## 特性

通用：双低端、双高端或半桥模式栅极驱动器

工作温度范围：-40°C 至 +125°C

开关参数：

- 最大传输失配 5ns

- 最大脉宽失真 8ns

Pai8233B/C/E, Pai8253B/C/E：

- 典型传输延时 19ns

- 最小脉冲宽度 10ns

Pai8233A/D/F, Pai8253A/D/F：

- 典型传输延时 90ns

- 最小脉冲宽度 50ns

共模传输抑制比(CMTI)：

- Pai8233B/C/E, Pai8253B/C/E: 100kV/us

- Pai8233A/D/F, Pai8253A/D/F: 300kV/us

隔离栅寿命 >40 年

4A 峰值源电流, 8A 峰值灌电流

TTL 和 CMOS 兼容输入

3V~5.5V 输入 VCCI 范围可与数字和模拟控制器接口

输出驱动电源 VDD 高达 25V

- 6V、9V 和 12V VDD UVLO 版本可选

可编程的重叠和死区时间

抑制小于 5ns 的输入脉冲和噪声瞬态

满足电源时序的快速 Disable 功能

安全相关认证：

- 符合 DIN EN IEC 60747-17 (VDE 0884-17) :2021-10 的 3535V<sub>pk</sub> 基本绝缘

- 符合 UL 1577 的 1 分钟 2.5kV<sub>RMS</sub> 隔离电压

- 符合 IEC 60950-1, IEC 62368-1, IEC 61010-1 和 IEC 60601-1 终端设备标准的 CSA 认证

- 符合 GB4943.1-2022 的 CQC 认证

标准 LGA13 封装

## 应用

DC-DC 和 AC-DC 电源中的隔离转换器

服务器、电信、IT 和工业基础设施

电机驱动器和 DC-AC 太阳能逆变器

HEV 和 BEV 电池充电器

不间断电源(UPS)

感应加热

LED 照明

## 特性

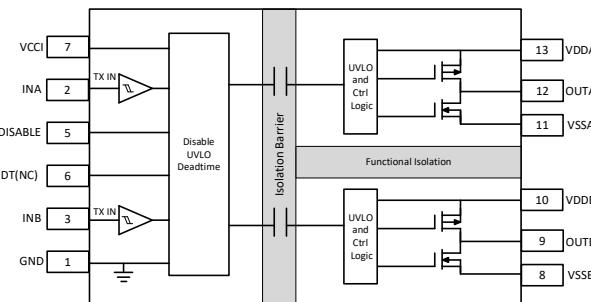

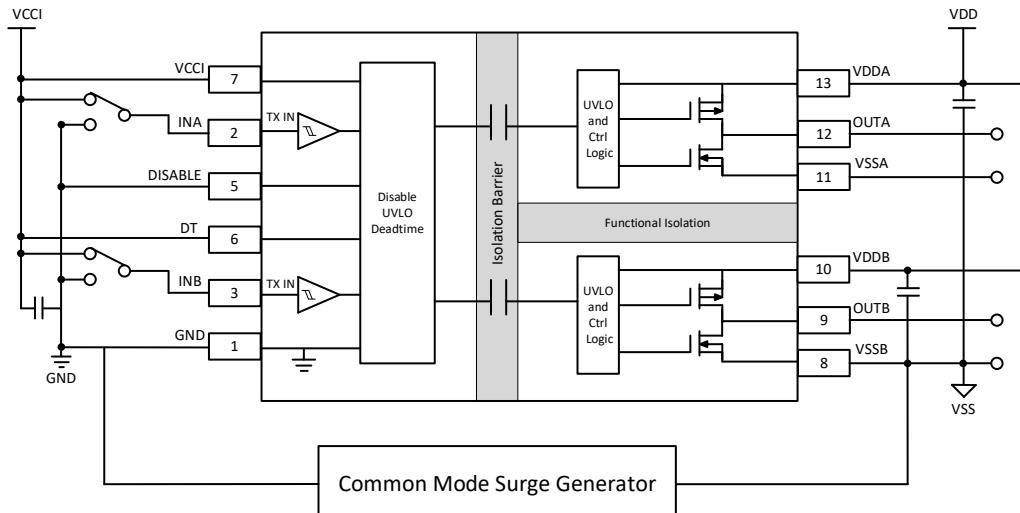

Pai8233X/Pai8253X 是基于荣湃 iDivider® 技术开发的双通道隔离栅极驱动器，具有 4A 的峰值源电流和 8A 的峰值灌电流。该系列器件的最高开关频率可达 5MHz，适用于 MOSFET、IGBT 和 SiC MOSFET 的栅极驱动。

输入端通过一个能承受 2.5kV<sub>RMS</sub> 隔离电压的隔离栅与两个输出驱动器隔离，典型的共模瞬变抗扰度(CMTI)能力包含 100kV/us 和 300kV/us 两个版本。两个次级侧驱动器之间的内部功能隔离允许最高 700V<sub>DC</sub> 的工作电压。

每个驱动器都可以作为两个低端驱动器、两个高端驱动器或一个可编程死区时间(DT)的半桥驱动器使用。Disable 引脚在设为高电平时会同时关闭两个输出，并在断开或接地时允许正常运行。作为故障安全措施，初级侧逻辑故障会将两个输出均设为低电平。

每个器件都支持高达 25V 的 VDD 电源电压。3V 至 5.5V 的输入 VCCI 范围使该驱动器适合与模拟和数字控制器接口。所有电源电压引脚均具有欠压锁定(UVLO)保护。

## 产品信息

| 型号       | 隔离耐压                 | 可编程死区时间 | 封装    |

|----------|----------------------|---------|-------|

| Pai8253X | 2.5kV <sub>RMS</sub> | 不支持     | LGA13 |

| Pai8233X | 2.5kV <sub>RMS</sub> | 支持      | LGA13 |

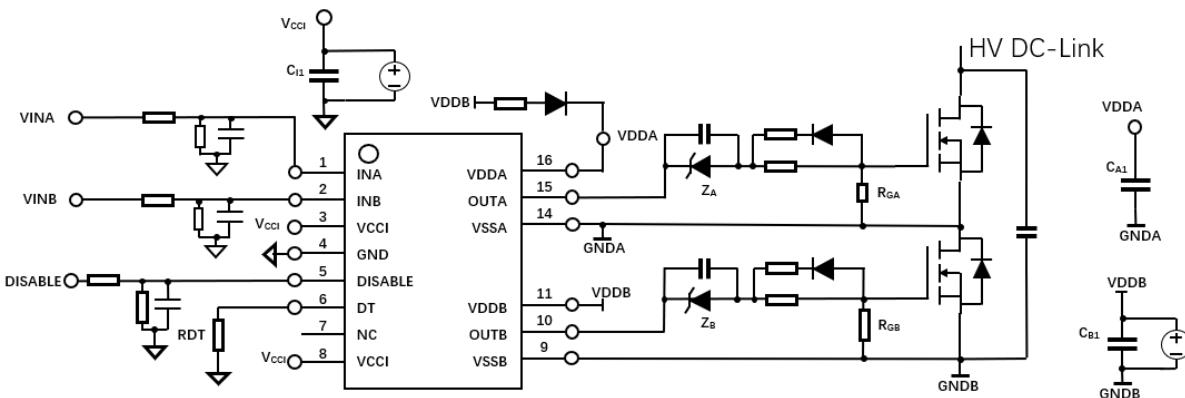

## 功能框图

图 1. 功能框图

Rev. 1.1

荣湃半导体提供的信息被认为是准确和可靠的。但荣湃半导体对使用它或因使用它可能导致的任何专利侵权或第三方其他权利不承担任何责任。规格如有更改，恕不另行通知。荣湃半导体的任何专利或专利权均不以暗示或其他方式授予任何许可。商标和注册商标是其各自所有者的财产。

上海市浦东新区博霞路 22 号 307-309 室, 201203

021-50850681

荣湃半导体(上海)有限公司, 版权所有。

<http://www.rpsemi.com/>

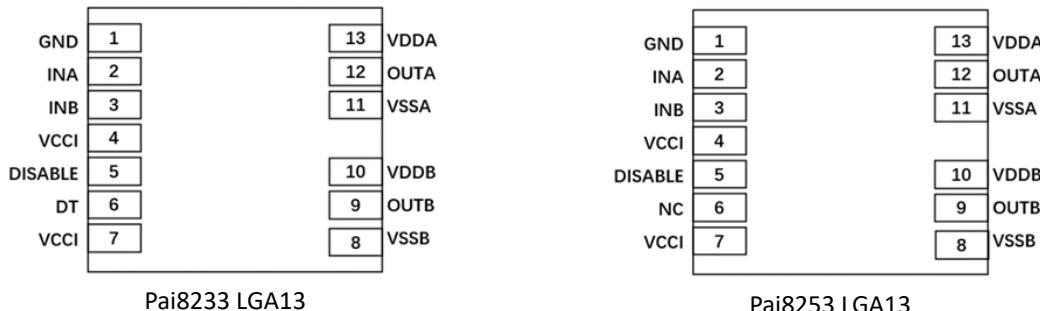

## 1 引脚定义和功能描述

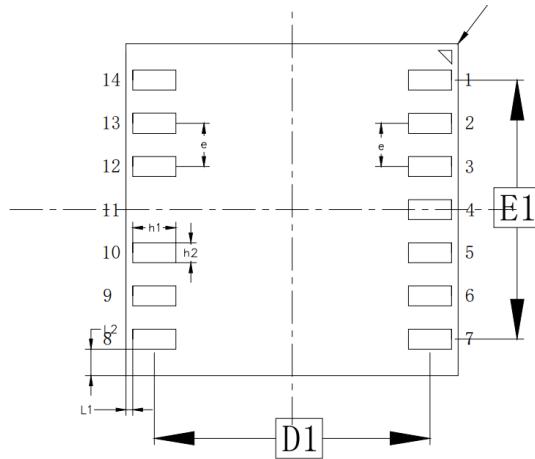

图 2. 引脚定义

表 1. Pai8233X/Pai8253X 引脚定义和功能描述

| 引脚名称    | PIN NO.  |          | 描述                                                                                                                                                                                                                                 |

|---------|----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Pai8233X | Pai8253X |                                                                                                                                                                                                                                    |

| INA     | 2        | 2        | A 通道的输入信号。<br>INA 输入具有 TTL / CMOS 兼容输入阈值。引脚在内部具备下拉电路，当引脚悬空时，默认为低电平输入。<br>如果不使用该引脚，则建议将该引脚接地，以获得更好的抗噪能力。                                                                                                                            |

| INB     | 3        | 3        | B 通道的输入信号。<br>INB 输入具有 TTL / CMOS 兼容输入阈值。引脚在内部具备下拉电路，当引脚悬空时，默认为低电平输入。<br>如果不使用该引脚，则建议将该引脚接地，以获得更好的抗噪能力。                                                                                                                            |

| VCCI    | 4,7      | 4,7      | 原边供电电源引脚。                                                                                                                                                                                                                          |

| GND     | 1        | 1        | 原边供电电源地引脚。<br>也是所有原边信号的参考地。                                                                                                                                                                                                        |

| DISABLE | 5        | 5        | 关闭输出引脚。此引脚在内部被下拉。<br>如果置为高电平，则两个驱动器停止输出；如果置为低电平或悬空，则允许驱动器输出。如果不使用该引脚，则建议将该引脚接地，以获得更好的抗噪能力。与微控制器连接时，在 DIS 引脚附近使用一个约 $1nF$ 的低 ESR / ESL 电容旁路。                                                                                        |

| DT      | 6        | /        | 死区时间设置引脚。<br>将 DT 引脚连接到 VCCI 时，允许输出 VOA 和 VOB 同时为高电平。DT 引脚开路时，则默认死区时间设置为 $<15\text{ ns}$ 。在 DT 和 GND 之间放置一个 $500\Omega$ 至 $500k\Omega$ 的电阻(RDT)时，死区时间为 $\text{DT(ns)} \approx 10 \times \text{RDT(k}\Omega)$ 。死区设置电阻 RDT 靠近 DT 引脚。 |

| VSSB    | 8        | 8        | 次边侧驱动器 B 的参考地。<br>次边侧 B 通道信号的参考地。                                                                                                                                                                                                  |

| OUTB    | 9        | 9        | 驱动器 B 的输出。连接到 B 通道 FET 或 IGBT 的栅极。                                                                                                                                                                                                 |

| VDBB    | 10       | 10       | 驱动器 B 的次级侧电源。<br>该 Pin 脚和 VSSB 之间需要放置低 ESR/ESL 的去耦电容，去耦电容尽可能靠近该 Pin 脚。                                                                                                                                                             |

| VSSA    | 11       | 11       | 次边侧驱动器 A 的参考地。<br>次边侧 A 侧通道信号的参考地。                                                                                                                                                                                                 |

| OUTA    | 12       | 12       | 驱动器 A 的输出。<br>连接到 A 沟道 FET 或 IGBT 的栅极。                                                                                                                                                                                             |

| VDDA    | 13       | 13       | 驱动器 A 的次级侧电源。<br>该 Pin 脚和 VSSA 之间需要放置低 ESR/ESL 的去耦电容，去耦电容尽可能靠近该 Pin 脚。                                                                                                                                                             |

## 2 技术指标

### 2.1 绝对最大额定值

表 2. 绝对最大额定值<sup>1</sup>

| 参数              | 符号                             | 最小值  | 最大值                | 单位 |

|-----------------|--------------------------------|------|--------------------|----|

| 输入电源电压          | VCCI-GND                       | -0.6 | 7                  | V  |

| 驱动器电源           | VDDA-VSSA, VDDB-VSSB           | -0.4 | 30                 | V  |

| 输入信号电压          | INA, INB, DIS, DT-GND          | -0.6 | VCCI+0.5           | V  |

| 输入信号电压          | INA, INB, 50ns 瞬态              | -5   | VCCI+0.5           | V  |

| 输出信号电压          | OUTA-VSSA, OUTB-VSSB           | -0.4 | VDDA+0.5, VDDB+0.5 | V  |

| 输出信号电压          | OUTA-VSSA, OUTB-VSSB, 200ns 瞬态 | -2   | VDDA+0.5, VDDB+0.5 | V  |

| 通道间电压           | VSSA-VSSB, VSSB-VSSA           | -700 | 700                | V  |

| 结温, $T_J$       | $T_J$                          | -40  | 150                | °C |

| 储存温度, $T_{stg}$ | $T_{stg}$                      | -65  | 150                | °C |

- 1) 超出上表中列出的绝对最大额定值可能会导致器件永久损坏。这些仅是绝对最大额定值，并不意味着器件在这些或任何其他超出“推荐工作条件”的条件下功能正常。长时间处于绝对最大额定条件下可能会影响器件的可靠性。

### 2.2 ESD 能力

| 描述                                  |                                                                   | 数值    | 单位 |

|-------------------------------------|-------------------------------------------------------------------|-------|----|

| $V_{(ESD)}$ Electrostatic discharge | ESD(HBM - 人体模型), 适用标 ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>        | ±4000 | V  |

|                                     | 组件充电模式 (CDM), 适用标准 JEDEC specification JESD22-C101 <sup>(2)</sup> | ±2000 |    |

- 1) JEDEC 文件 JEP155 规定, 500V HBM 允许通过标准 ESD 控制过程进行安全制造。

2) JEDEC 文件 JEP157 规定, 250V CDM 允许通过标准 ESD 控制过程进行安全制造。

### 2.3 推荐工作条件

表 3. 无风环境(除非另有说明)

| 符号                            | 描述            | 最小值  | 最大值       | 单位 |

|-------------------------------|---------------|------|-----------|----|

| VCCI                          | VCCI 输入电源电压   | 3    | 5.5       | V  |

| VDDA-VSSA, VDDB-VSSB          | 输出侧电源 -6V 版本  | 6.5  | 25        | V  |

|                               | 输出侧电源 -9V 版本  | 9.2  | 25        | V  |

|                               | 输出侧电源 -12V 版本 | 13.5 | 25        | V  |

| INA-GND, INB-GND, DISABLE-GND | 输入信号电压        | 0    | $V_{CCI}$ | V  |

| VOA-VSSA, VOB-VSSB            | 驱动输出电压        | 0    | VDDA/VDDB | V  |

| $t_{INA}, t_{INB}$            | 有效脉冲宽度        | 10   | /         | ns |

| $T_A$                         | 环境温度          | -40  | 125       | °C |

| $T_J$                         | 结温            | -40  | 130       | °C |

## 2.4 热信息

表 4. 热阻信息

| 符号              | 参数      | 典型值 | 单位   |

|-----------------|---------|-----|------|

| $R_{\theta JA}$ | 结到空气的热阻 | 207 | °C/W |

## 2.5 额定功率

表 5. 额定功率

测试条件:  $V_{CC1} = 3.3V$ ,  $V_{DDA/B} = 12 V$ ,  $INA/B = 3.3 V$ , 2MHz, 50%占空比方波 1nF 负载

| 符号       | 参数         | 数值    | 单位 |

|----------|------------|-------|----|

| PD       | 功耗         | 0.603 | W  |

| PDI      | 发射侧功耗      | 0.003 | W  |

| PDA, PDB | 每个驱动输出侧的功耗 | 0.30  | W  |

## 3 绝缘规格

表 6. 电气间隙、爬电距离、材料组别及过电压等级

| 参数                                 | 描述     | 测试条件                                 | 数值    | 单位 |

|------------------------------------|--------|--------------------------------------|-------|----|

| CLR                                | 外部电气间隙 | 空气中最短的引脚距离                           | > 3.2 | mm |

| CPG                                | 外部爬电距离 | 整个封装表面上最短的引脚到引脚距离                    | > 3.2 | mm |

| CTI                                | 相对电痕指数 | IEC 60112; DIN EN 60112(VDE 0303-11) | > 400 | V  |

| 材料组别                               | 材料组别   | IEC 60664-1                          | II    |    |

| 符合 GB/T 16935.1、IEC 60664-1 的过电压类别 |        | 额定电源电压≤600 V <sub>RMS</sub>          | I-II  |    |

|                                    |        | 额定电源电压≤1000 V <sub>RMS</sub>         | I     |    |

表 7. DIN EN IEC 60747-17 (VDE 0884-17):2021-10

| 参数         | 描述         | 测试条件                                                                                                                                  | 数值   | 单位               |

|------------|------------|---------------------------------------------------------------------------------------------------------------------------------------|------|------------------|

| $V_{IORM}$ | 最大重复峰值隔离电压 | 交流电压(双极性)                                                                                                                             | 792  | V <sub>PK</sub>  |

| $V_{IOWM}$ | 最大工作隔离电压   | 交流电压(正弦波)                                                                                                                             | 560  | V <sub>RMS</sub> |

|            |            | 直流电压                                                                                                                                  | 792  | V <sub>DC</sub>  |

| $V_{IOTM}$ | 最大瞬态隔离电压   | $V_{TEST} = V_{IOTM}$ , t = 60 秒(认证)<br>$V_{TEST} = 1.2 \times V_{IOTM}$ , t = 1s(100%生产)                                             | 3535 | V <sub>PK</sub>  |

| $V_{IOSM}$ | 最大浪涌隔离电压   | 根据 IEC 62368-1 的测试方法, 1.2/50 μs 波形, $V_{TEST} = 1.3 \times V_{IOSM}$ (认证)                                                             | 3500 | V <sub>PK</sub>  |

| $q_{pd}$   | 视在放电       | 输入/输出安全测试子组 2/3 之后,采用方法 a)。<br>$V_{ini} = V_{IOTM}$ , $t_{ini} = 60s$ ; $V_{pd(m)} = 1.2 \times V_{IORM}$ , $t_m = 10s$               | <5   | pC               |

|            |            | 经过子组 1 环境测试后,采用方法 a)。<br>$V_{ini} = V_{IOTM}$ , $t_{ini} = 60s$ ; $V_{pd(m)} = 1.3 \times V_{IORM}$ , $t_m = 10$ 秒                    | <5   | pC               |

|            |            | 方法 b1; 在常规测试(100%生产)和预处理(类型测试)时;<br>$V_{ini} = 1.2 \times V_{IOTM}$ , $t_{ini} = 1s$ ; $V_{pd(m)} = 1.5 \times V_{IORM}$ , $t_m = 1s$ | <5   | pC               |

| 参数       | 描述          | 测试条件                                                                            | 数值          | 单位       |

|----------|-------------|---------------------------------------------------------------------------------|-------------|----------|

| $C_{IO}$ | 隔离电容, 输入对输出 | $V_{IO} = 0.4 \sin(2\pi ft)$ , $f = 1 \text{ MHz}$                              | 1.2         | pF       |

| $R_{IO}$ | 隔离电阻, 输入对输出 | $T_A = 25^\circ\text{C}$ 时, $V_{IO} = 500 \text{ V}$                            | $> 10^{12}$ | $\Omega$ |

|          |             | $100^\circ\text{C} \leq T_A \leq 125^\circ\text{C}$ 时, $V_{IO} = 500 \text{ V}$ | $> 10^{11}$ | $\Omega$ |

|          |             | $T_S = 150^\circ\text{C}$ 时, $V_{IO} = 500 \text{ V}$                           | $> 10^9$    | $\Omega$ |

| 污染等级     |             |                                                                                 | 2           |          |

| 气候类别     |             |                                                                                 | 40/125/21   |          |

表 8. UL 1577

| 参数        | 描述   | 测试条件                                                                                                                                             | 数值   | 单位                      |

|-----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------|

| $V_{ISO}$ | 隔离电压 | $V_{TEST} = V_{ISO}$ , $t = 60\text{s}$ . (认证测试),<br>$V_{TEST} = 1.2 \times V_{ISO} = 6000 \text{ V}_{\text{RMS}}$ , $t = 1\text{s}$ (100% 生产测试) | 2500 | $\text{V}_{\text{RMS}}$ |

### 3.1 安全相关认证

表 9. 认证

| 认证标准       | 描述信息                                                                                                                                                                                                                                        |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>CQC</b> | 通过 GB 4943.1-2022 认证<br>基本绝缘, 海拔≤5000 m, 热带气候, 额定 557 VRMS(峰值 636V)工作电压<br>证书编号: CQC23001407489                                                                                                                                             |

| <b>UL</b>  | 根据 UL 1577 器件认可计划认可<br>单一保护, 2500 $\text{V}_{\text{RMS}}$<br>证书编号: E494497                                                                                                                                                                  |

| <b>VDE</b> | 通过 DIN EN IEC 60747-17 (VDE 0884-17) :2021-10, and EN IEC 60747-17: 2020+AC:<br>2021 认证<br>基本绝缘最大瞬态隔离电压, 3535 $\text{V}_{\text{PK}}$ ;<br>最大重复峰值隔离电压 792 $\text{V}_{\text{PK}}$ ;<br>最大浪涌隔离电压 3500 $\text{V}_{\text{PK}}$<br>证书编号: 40052896 |

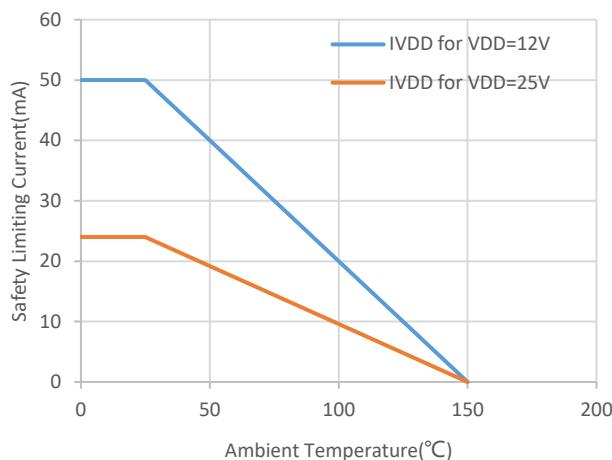

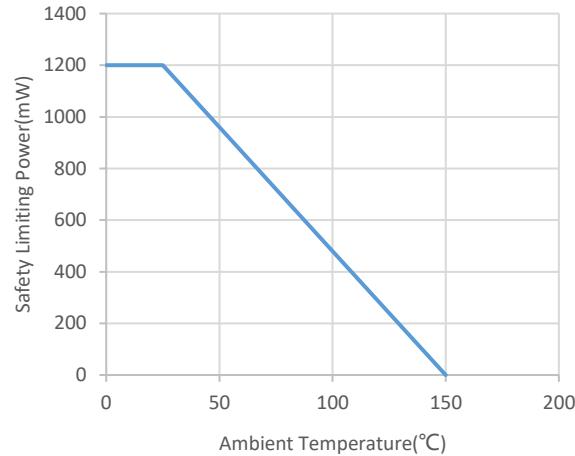

### 3.2 安全工作区

安全限值旨在最大程度地减少输入或输出电路出现故障时对隔离栅的潜在损坏。

表 10. 安全限值

| 符号    | 参数                | 测试条件                                                                                                                            | SIDE               | 最大值 | 单位 |

|-------|-------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|----|

| $I_S$ | 安全输出电源电流          | $R_{\theta JA} = 101^\circ\text{C} / \text{W}$ , $VDDA/B = 12 \text{ V}$ , $T_A = 25^\circ\text{C}$ , $T_J = 150^\circ\text{C}$ | Driver A, Driver B | 25  | mA |

|       |                   | $R_{\theta JA} = 101^\circ\text{C} / \text{W}$ , $VDDA/B = 25 \text{ V}$ , $T_A = 25^\circ\text{C}$ , $T_J = 150^\circ\text{C}$ | Driver A, Driver B | 12  | mA |

| $P_S$ | 安全功率              | $R_{\theta JA}=101^\circ\text{C} / \text{W}$ , $T_A = 25^\circ\text{C}$ , $T_J = 150^\circ\text{C}$ ;                           | TOTAL              | 600 | mW |

| $T_S$ | 安全温度 <sup>1</sup> |                                                                                                                                 |                    | 150 | °C |

- 1) 最高安全温度  $T_S$  与器件规定的最高结温  $T_J$  相同。  $I_S$  和  $P_S$  分别代表安全电流和安全功率。 不得超过  $I_S$  和  $P_S$  的最大限值。 这些限值随环境温度  $T_A$  而变化。

热性能信息表中的结对空气的热阻  $R_{\theta JA}$  是指安装在高 K 测试板上贴片封装的器件热阻。用以下公式来计算每个参数的值：

$T_J = T_A + R_{\theta JA} \times P$ , 其中  $P$  是器件中的功耗。

$T_{J(max)} = T_S = T_A + R_{\theta JA} \times P_S$ , 其中  $T_{J(max)}$  是允许的最大结温。  $P_S = I_S \times V_I$ , 其中  $V_I$  是最大输入电压。

## 4 真值表

表 11.真值表

| 输入             |                | DISABLE | VCCI/VDDA/VDDB 状态 |        |        | 输出             |                | 注意事项                                   |

|----------------|----------------|---------|-------------------|--------|--------|----------------|----------------|----------------------------------------|

| INA            | INB            |         | VCCI              | VDDA   | VDDB   | VOA            | VOB            |                                        |

| L              | L              | L 或 悬空  | 供电                | 供电     | 供电     | L              | L              | 如果使能了死区功能，则输出状态在死区延时后才变更。 <sup>2</sup> |

| L              | H              | L 或 悬空  | 供电                | 供电/未供电 | 供电     | L              | H <sup>2</sup> |                                        |

| H              | L              | L 或 悬空  | 供电                | 供电     | 供电/未供电 | H <sup>2</sup> | L              | DT 引脚悬空或者连接 R <sub>DT</sub> 电阻。        |

| H              | H              | L 或 悬空  | 供电                | 供电     | 供电     | L              | L              |                                        |

| H              | H              | L 或 悬空  | 供电                | 供电     | 供电     | H <sup>2</sup> | H <sup>2</sup> | DT 引脚连接到 VCCI。                         |

| X <sup>1</sup> | X <sup>1</sup> | H       | 供电                | 供电     | 供电     | L              | L              |                                        |

| L              | L              | L 或 悬空  | 未供电               | 供电     | 供电     | L              | L              |                                        |

注意：

1) “X”表示低电平、高电平或悬空。

2) VOA / VOB 输出仅在这种情况下为高。如果有其他情况，VOA / VOB 输出为低电平。

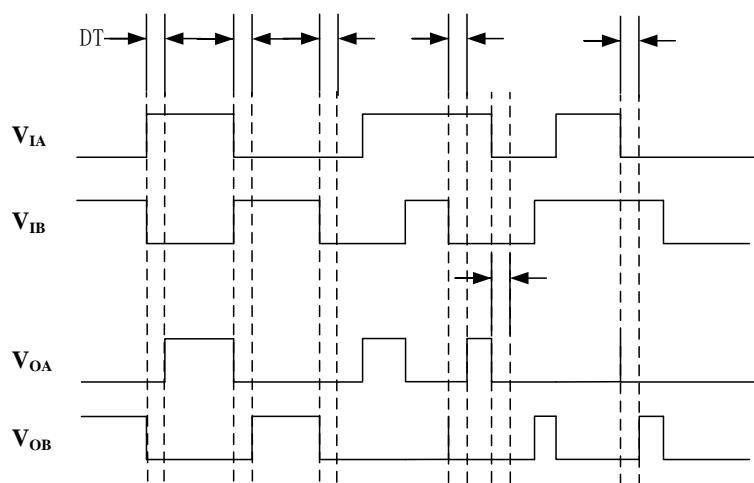

$T_{DT} \approx 10 \times R_{DT}$  ( $T_{DT}$  以 ns 为单位,  $R_{DT}$  以 kΩ 为单位)。将 DT 连接到 VCCI 可以使输出重叠。保持 DT 开路，死区时间设置 < 15ns。在 DT 和 GND 之间放置一个 500Ω 至 500kΩ 的电阻( $R_{DT}$ )，可以根据以下条件调整死区时间： $DT(ns) \approx 10 \times R_{DT}(k\Omega)$ 。

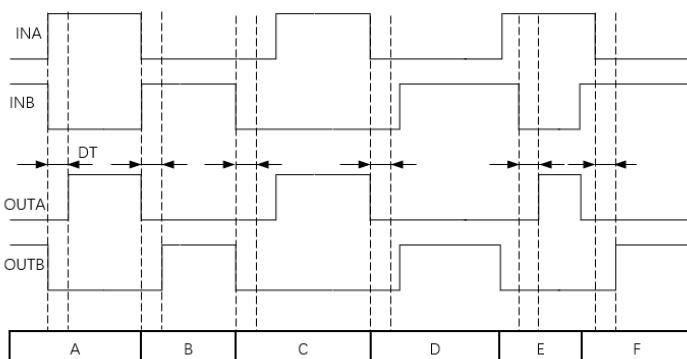

图 3.死区设置与输入输出信号逻辑关系图

## 5 规格

### 5.1 电气特性

表 12. 电气特性

V<sub>VCCI</sub> = 3.3 V 或 5 V, V<sub>VCCI</sub> 与 GND 之间的电容为 0.1  $\mu$ F, Pai823(5)3A/B/C/D VDDA = VDDB = 12 V, Pai823(5)3E/F VDDA = VDDB = 15V, VDDA 与 VSSA 之间的电容为 1  $\mu$ F, VDDB 与 VSSB 之间的电容为 1  $\mu$ F, T<sub>A</sub> = -40°C ~+ 125°C。 (除非另有说明)

| 符号                                                                   | 描述                                             | 测试条件                                                                                           | 最小值                       | 典型值   | 最大值  | 单位       |

|----------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------|-------|------|----------|

| I <sub>VCCI</sub>                                                    | V <sub>VCCI</sub> 静态电流                         | V <sub>INA</sub> = 0 V, V <sub>INB</sub> = 0 V                                                 |                           | 0.5   | 1.1  | mA       |

| I <sub>VDDA</sub> , I <sub>VDDB</sub>                                | VDDA 和 VDDB 静态电流                               | V <sub>INA</sub> = 0 V, V <sub>INB</sub> = 0 V                                                 |                           | 0.9   | 1.5  | mA       |

| I <sub>VCCI</sub>                                                    | V <sub>VCCI</sub> 工作电流                         | V <sub>INA</sub> , V <sub>INB</sub> 输入信号 f = 500 kHz, 50% 占空比, 每通道负载电容 100 pF±20%, 包含测量仪器输入电容。 |                           | 0.9   |      | mA       |

| I <sub>VDDA</sub> , I <sub>VDDB</sub>                                | VDDA 和 VDDB 工作电流                               |                                                                                                |                           | 2.2   |      | mA       |

|                                                                      |                                                |                                                                                                |                           |       |      |          |

| V <sub>VCCI_ON</sub>                                                 | V <sub>VCCI</sub> 开机阈值                         |                                                                                                | 2.55                      | 2.7   | 2.85 | V        |

| V <sub>VCCI_OFF</sub>                                                | V <sub>VCCI</sub> 关机阈值                         |                                                                                                | 2.35                      | 2.5   | 2.65 | V        |

| V <sub>VCCI_HYS</sub>                                                | V <sub>VCCI</sub> 欠压回滞                         |                                                                                                |                           | 0.2   |      | V        |

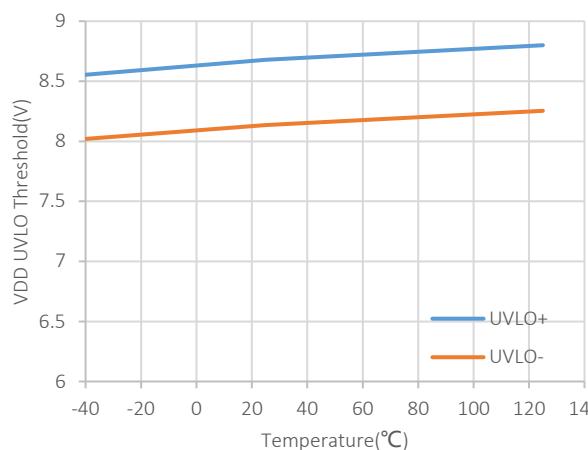

| V <sub>VDDA_ON'</sub><br>V <sub>VDDB_ON'</sub>                       | VDDx 开机阈值 - 6V 版本<br>(Pai8233B/D, Pai8253B/D)  |                                                                                                | 5.7                       | 6.1   | 6.5  | V        |

| V <sub>VDDA_OFF'</sub><br>V <sub>VDDB_OFF'</sub>                     | VDDx 关机阈值 - 6V 版本<br>(Pai8233B/D, Pai8253B/D)  |                                                                                                | 5.4                       | 5.8   | 6.2  | V        |

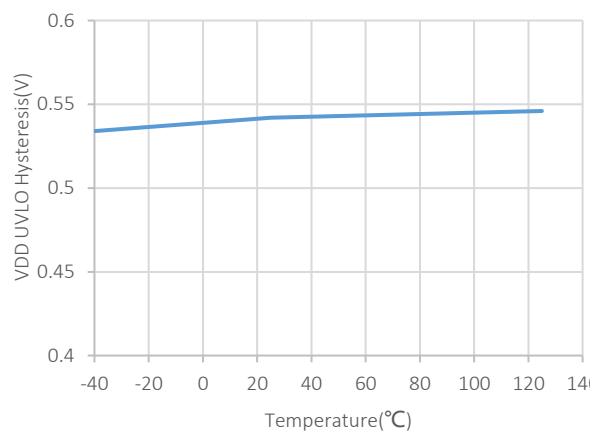

| V <sub>VDDA_HYS'</sub><br>V <sub>VDDB_HYS'</sub>                     | VDDx 欠压回滞 - 6V 版本<br>(Pai8233B/D, Pai8253B/D)  |                                                                                                |                           | 0.3   |      | V        |

| V <sub>VDDA_ON'</sub><br>V <sub>VDDB_ON'</sub>                       | VDDx 开机阈值 - 9V 版本<br>(Pai8233A/C, Pai8253A/C)  |                                                                                                | 8.3                       | 8.7   | 9.2  | V        |

| V <sub>VDDA_OFF'</sub><br>V <sub>VDDB_OFF'</sub>                     | VDDx 关机阈值 - 9V 版本<br>(Pai8233A/C, Pai8253A/C)  |                                                                                                | 7.8                       | 8.2   | 8.7  | V        |

| V <sub>VDDA_HYS'</sub><br>V <sub>VDDB_HYS'</sub>                     | VDDx 欠压回滞 - 9V 版本<br>(Pai8233A/C, Pai8253A/C)  |                                                                                                |                           | 0.5   |      | V        |

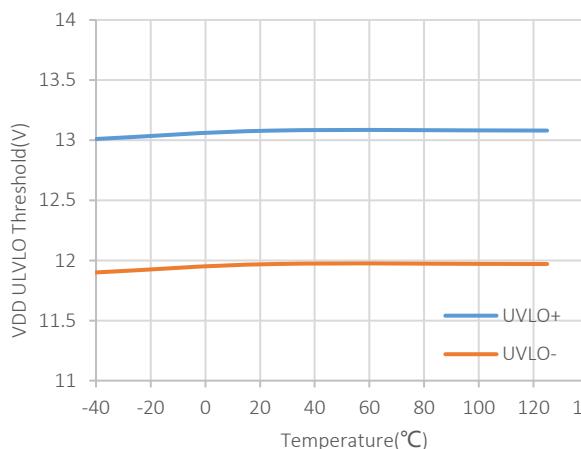

| V <sub>VDDA_ON'</sub><br>V <sub>VDDB_ON'</sub>                       | VDDx 开机阈值 - 12V 版本<br>(Pai8233E/F, Pai8253E/F) |                                                                                                | 11.9                      | 12.8  | 13.7 | V        |

| V <sub>VDDA_OFF'</sub><br>V <sub>VDDB_OFF'</sub>                     | VDDx 关机阈值 - 12V 版本<br>(Pai8233E/F, Pai8253E/F) |                                                                                                | 10.9                      | 11.8  | 12.7 | V        |

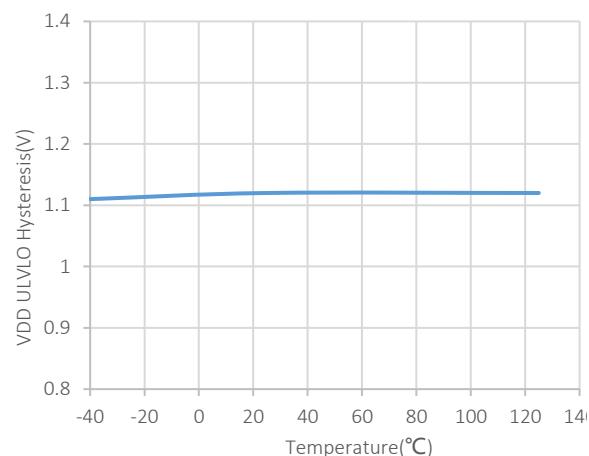

| V <sub>VDDA_HYS'</sub><br>V <sub>VDDB_HYS'</sub>                     | VDDx 欠压回滞 - 12V 版本<br>(Pai8233E/F, Pai8253E/F) |                                                                                                |                           | 1     |      | V        |

| V <sub>INAH</sub> , V <sub>INBH</sub> ,<br>V <sub>DISH</sub>         | 输入高电平阈值                                        |                                                                                                | 1.6                       | 1.8   | 2    | V        |

| V <sub>INAL</sub> , V <sub>INBL</sub> , V <sub>DISL</sub>            | 输入低电平阈值                                        |                                                                                                | 0.8                       | 1     | 1.2  | V        |

| V <sub>INA_HYS'</sub><br>V <sub>INB_HYS'</sub> V <sub>DIS_HYS'</sub> | 输入信号回滞                                         |                                                                                                |                           | 0.8   |      | V        |

| V <sub>INA</sub> , V <sub>INB</sub>                                  | 参考到 GND, 50ns 瞬态负脉冲                            | 仅实验室测试                                                                                         | -5                        |       |      | V        |

| I <sub>OA+</sub> , I <sub>OB+</sub>                                  | Pai8233X/Pai8253X 峰值输出源电流                      | C <sub>LOAD</sub> = 10 $\mu$ F, C <sub>LOAD</sub> = 0.68 $\mu$ F, f= 100Hz, 仅实验室测试             |                           | 4     |      | A        |

| I <sub>OA-</sub> , I <sub>OB-</sub>                                  | Pai8233X/Pai8253X 峰值输出灌电流                      |                                                                                                |                           | 8     |      | A        |

| R <sub>ROHA</sub> , R <sub>ROHB</sub>                                | 输出高电平状态下的输出内阻                                  | I <sub>OUT</sub> = -10 mA, TA = 25°C, ROHA, ROHB 不代表驱动器上拉性能。                                   |                           | 1     |      | $\Omega$ |

| R <sub>ROLA</sub> , R <sub>ROLB</sub>                                | 输出低电平状态下的输出内阻                                  | I <sub>OUT</sub> = 10 mA, TA = 25°C                                                            |                           | 0.4   |      | $\Omega$ |

| V <sub>ROHA</sub> , V <sub>ROHB</sub>                                | 高输出时的输出电压                                      | VDDA, VDDB = 12 V, I <sub>OUT</sub> = -10 mA, TA = 25°C                                        |                           | 11.99 |      | V        |

| V <sub>ROLA</sub> , V <sub>ROLB</sub>                                | 低输出时的输出电压                                      | VDDA, VDDB = 12 V, I <sub>OUT</sub> = 10 mA, TA = 25°C                                         |                           | 4     |      | mV       |

| DT                                                                   | 死区时间(仅 Pai8233X)                               | DT 引脚连接到 V <sub>VCCI</sub>                                                                     | 输出高电平重叠时间取决于 INA 与 INB 信号 |       |      | ns       |

|                                                                      |                                                | DT 引脚悬空                                                                                        | 0                         | 8     | 15   | ns       |

|                                                                      |                                                | R <sub>DT</sub> = 20 k $\Omega$                                                                | 150                       | 200   | 250  | ns       |

| 符号              | 描述               | 测试条件 | 最小值                              | 典型值 | 最大值 | 单位 |

|-----------------|------------------|------|----------------------------------|-----|-----|----|

| DT              | 死区时间(仅 Pai8253X) |      | 无死区限制, 输出高电平重叠时间取决于 INA 与 INB 信号 |     | ns  |    |

| T <sub>JF</sub> | 过温保护恢复           |      |                                  | 140 |     | °C |

| T <sub>JR</sub> | 过温保护             |      |                                  | 150 |     | °C |

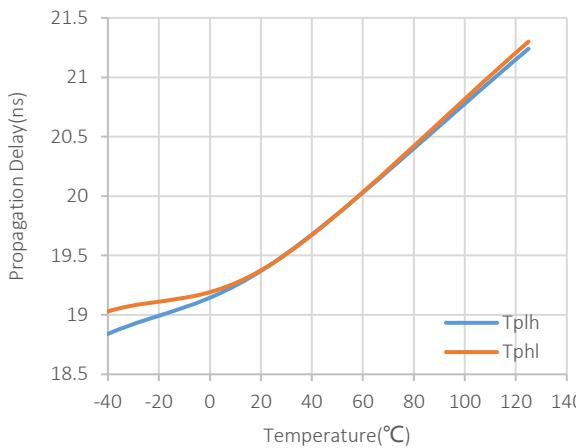

## 5.2 开关特性

表 13.开关特性

VCCI = 3.3 V 或 5 V, VCCI 与 GND 之间的电容为 0.1  $\mu$ F, Pai823(5)3A/B/C/D VDDA = VDDB = 12 V, Pai823(5)3E/F VDDA = VDDB = 15V, VDDA 与 VSSA 之间的电容为 1  $\mu$ F, VDDB 与 VSSB 之间的电容为 1  $\mu$ F, T<sub>A</sub> = -40°C ~ +125°C。(除非另有说明)

| 参数                   | 描述                                                              | 测试条件                                           | 最小值 | 典型值 | 最大值 | 单位      |

|----------------------|-----------------------------------------------------------------|------------------------------------------------|-----|-----|-----|---------|

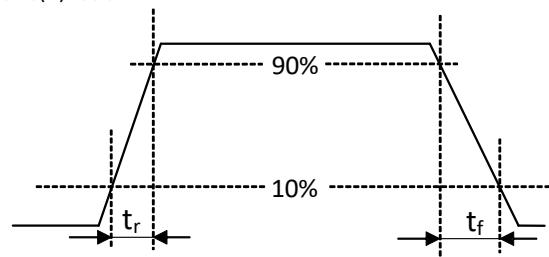

| t <sub>r</sub>       | 输出上升时间, 测量点为 10%至 90%                                           | C <sub>OUT</sub> = 1.8 nF                      |     | 7   | 18  | ns      |

| t <sub>f</sub>       | 输出下降时间, 测量点的 90%至 10%                                           | C <sub>OUT</sub> = 1.8 nF                      |     | 8   | 12  | ns      |

| t <sub>PWmin</sub>   | 最小脉冲宽度                                                          | C <sub>OUT</sub> = 0 pF                        |     | 10  | 20  | ns      |

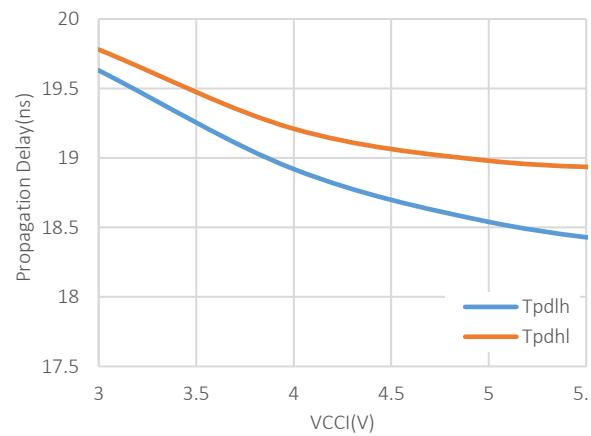

| t <sub>PDHL</sub>    | Pai823(5)3B/C/E: INx 下降沿到 OUTx 下降沿的传播延迟                         |                                                | 14  | 19  | 30  | ns      |

| t <sub>PDLH</sub>    | Pai823(5)3B/C/E: INx 上升沿到 OUTx 上升沿的传播延迟                         |                                                | 14  | 19  | 30  | ns      |

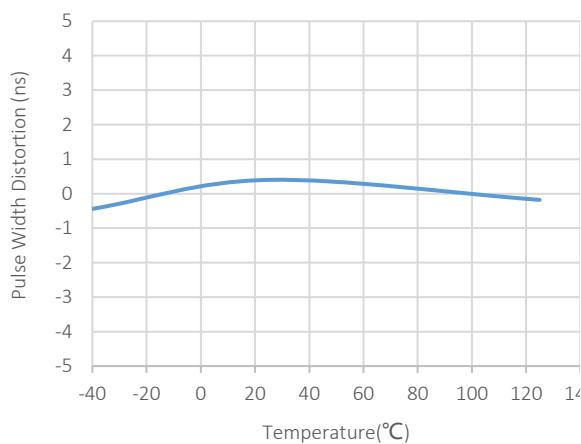

| t <sub>PWD</sub>     | Pai823(5)3B/C/E: 脉冲宽度失真   t <sub>PDLH</sub> - t <sub>PDHL</sub> |                                                |     |     | 5   | ns      |

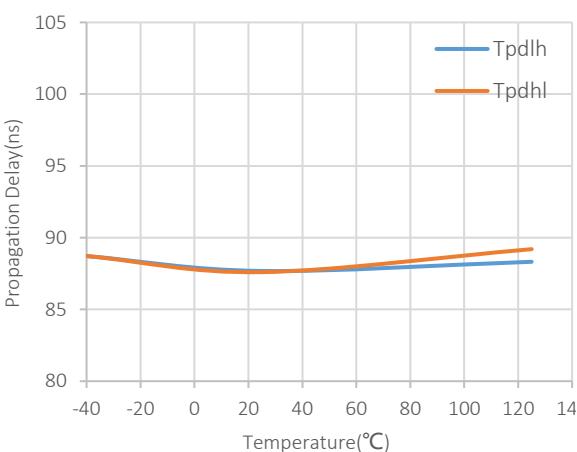

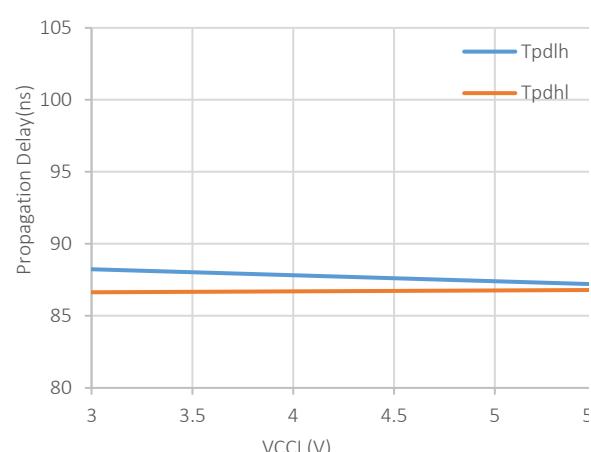

| t <sub>PDHL</sub>    | Pai823(5)3A/D/F: INx 下降沿到 OUTx 下降沿的传播延迟                         |                                                | 60  | 90  | 150 | ns      |

| t <sub>PDLH</sub>    | Pai823(5)3A/D/F: INx 上升沿到 OUTx 上升沿的传播延迟                         |                                                | 60  | 90  | 150 | ns      |

| t <sub>PWD</sub>     | Pai823(5)3A/D/F: 脉冲宽度失真   t <sub>PDLH</sub> - t <sub>PDHL</sub> |                                                |     |     | 8   | ns      |

| t <sub>DM</sub>      | VOUTA, VOUTB 之间的传播延迟差异                                          | f = 100 kHz                                    |     |     | 5   | ns      |

| CM <sub>H</sub>      | Pai823(5)3B/C/E: 输出高电平时的共模瞬变抗扰度                                 | INA 和 INB 均连接到 VCCI 上; V <sub>CM</sub> =1000V; |     | 100 |     | kV/us   |

| CM <sub>L</sub>      | Pai823(5)3B/C/E: 输出低电平时的共模瞬变抗扰度                                 | INA 和 INB 均连接到 GND 上; V <sub>CM</sub> =1000V;  |     | 100 |     | kV/us   |

| CM <sub>H</sub>      | Pai823(5)3A/D/F: 输出高电平时的共模瞬变抗扰度                                 | INA 和 INB 均连接到 VCCI 上; V <sub>CM</sub> =1000V; |     | 300 |     | kV/us   |

| CM <sub>L</sub>      | Pai823(5)3A/D/F: 输出低电平时的共模瞬变抗扰度                                 | INA 和 INB 均连接到 GND 上; V <sub>CM</sub> =1000V;  |     | 300 |     | kV/us   |

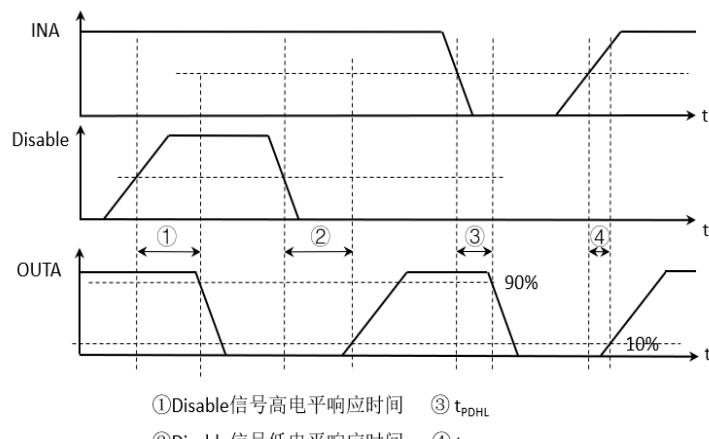

| t <sub>SD</sub>      | Pai823(5)3B/C/E: DISABLE 关断响应时间                                 |                                                |     |     | 40  | ns      |

| t <sub>RESTART</sub> | Pai823(5)3B/C/E: DISABLE 重新启动时间                                 |                                                |     |     | 40  | ns      |

| t <sub>SD</sub>      | Pai823(5)3A/D/F: DISABLE 关断响应时间                                 |                                                |     |     | 150 | ns      |

| t <sub>RESTART</sub> | Pai823(5)3A/D/F: DISABLE 重新启动时间                                 |                                                |     |     | 150 | ns      |

| t <sub>START</sub>   | 芯片启动时间                                                          | 从 VDD = VDD_UV+ 到 VOA, VOB = INA, INB          |     |     | 100 | $\mu$ s |

### 5.3 绝缘特性曲线

图 4. 极限电流的热降额曲线

图 5. 极限功率的热降额曲线

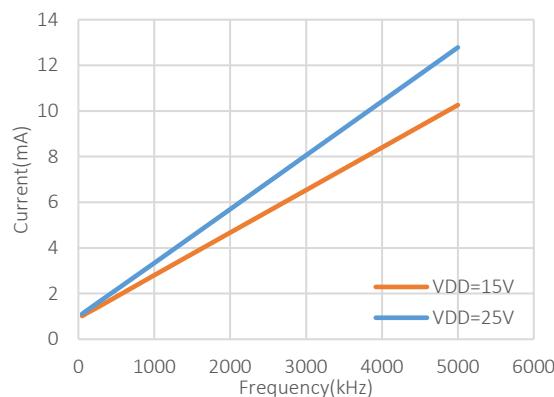

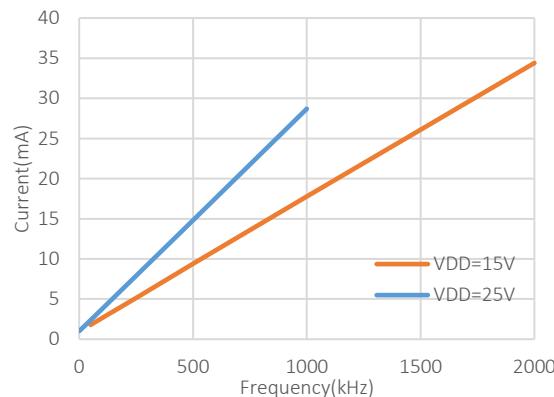

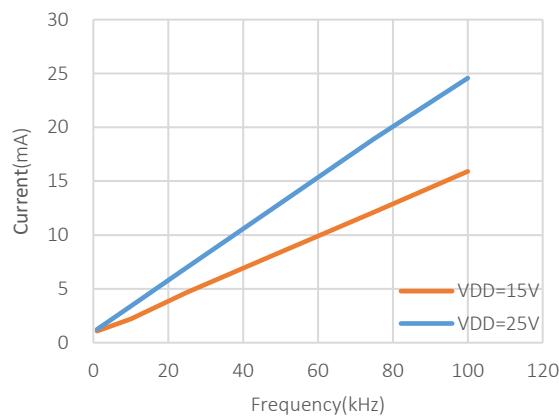

### 5.4 典型特性曲线

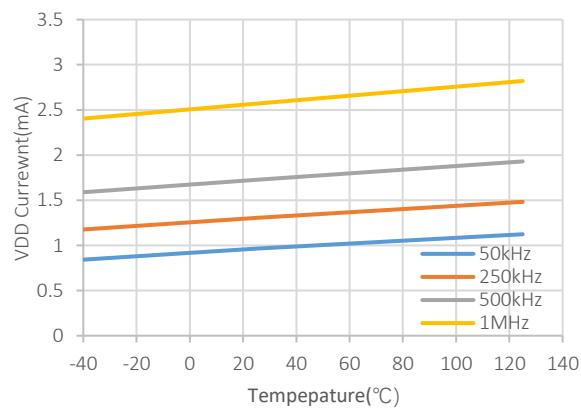

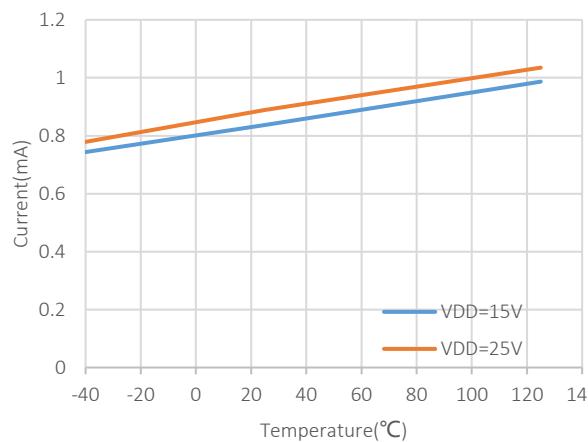

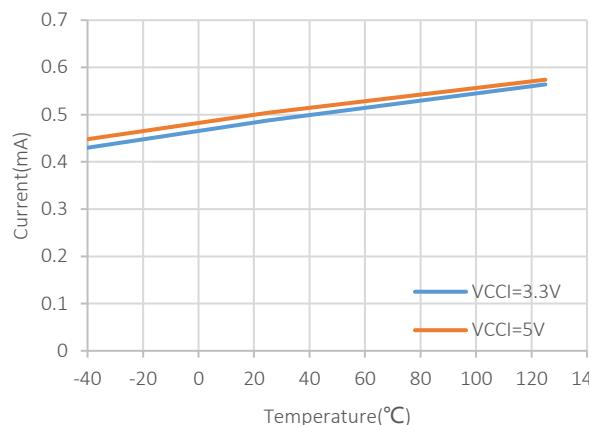

VDDA = VDBB = 12 V, VCCI = 3.3 V, TA = 25°C, 空载 (除非另有说明).

图 6. Per Channel Current ( $I_{VDDA/B}$ ) (No load)

图 7. Per Channel Current ( $I_{VDDA/B}$ ) (1nF Load)

图 8. Per Channel Current ( $I_{VDDA/B}$ ) (10nF Load)

图 9. Per Channel Current ( $I_{VDDA/B}$ ) (No Load)

图 10.Per Channel Quiescent Current ( $I_{VDDA/B}$ )

图 11. $I_{VCCI}$  Quiescent Current

图 12.Pai823(5)3B/C/E Propagation Delay

图 13.Pai823(5)3B/C/E Propagation Delay

图 14.Pai823(5)3A/D/F Propagation Delay

图 15. Pai823(5)3A/D/F Propagation Delay

图 16.Pulse Width Distortion

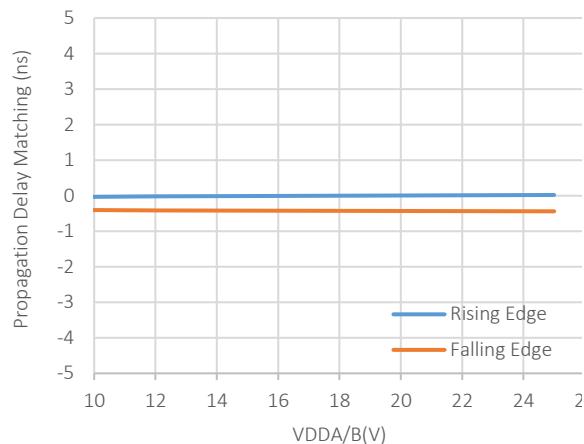

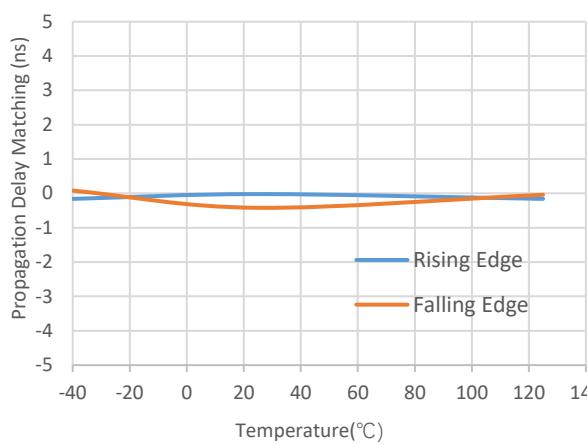

图 17.Propagation Delay Matching ( $t_{\text{DM}}$ )

图 18.Propagation Delay Matching ( $t_{\text{DM}}$ )

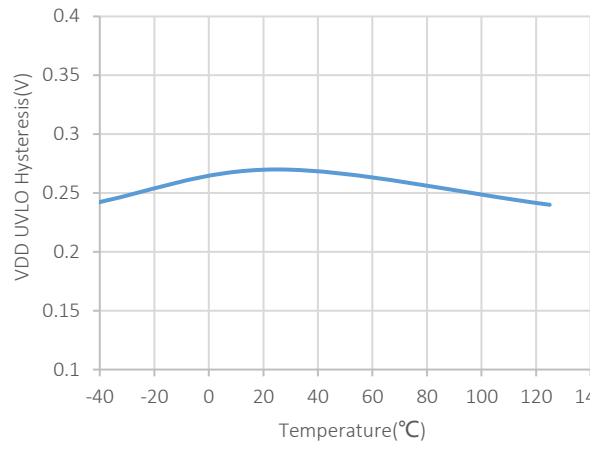

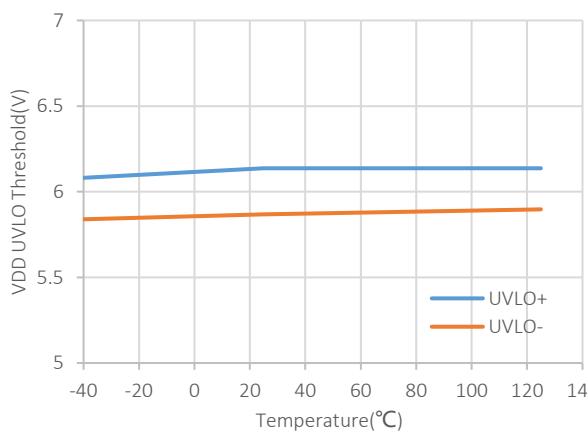

图 19.VDD 6-V UVLO Hysteresis

图 20.VDD 6-V UVLO Threshold vs. Temperature

图 21.VDD 9-V UVLO Hysteresis

图 22.VDD 9-V UVLO Threshold vs. Temperature

图 23.VDD 12-V UVLO Hysteresis

图 24.VDD 12-V UVLO Threshold vs. Temperature

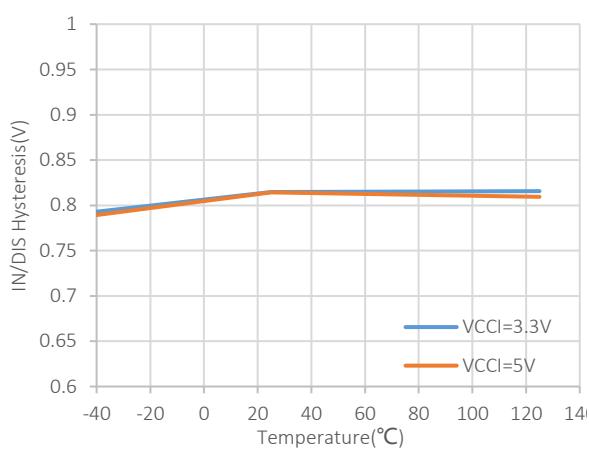

图 25.IN/DIS Hysteresis

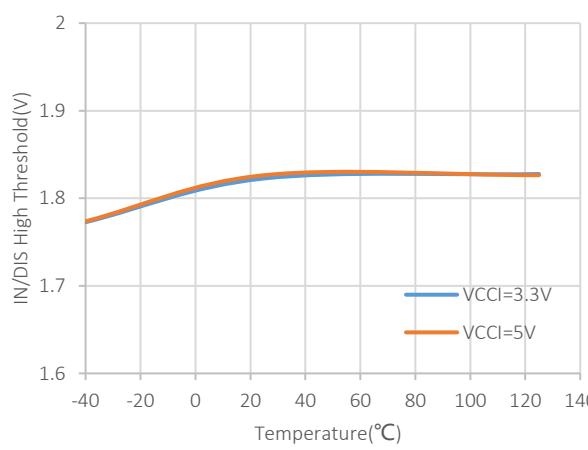

图 26.IN/DIS High Threshold (rise)

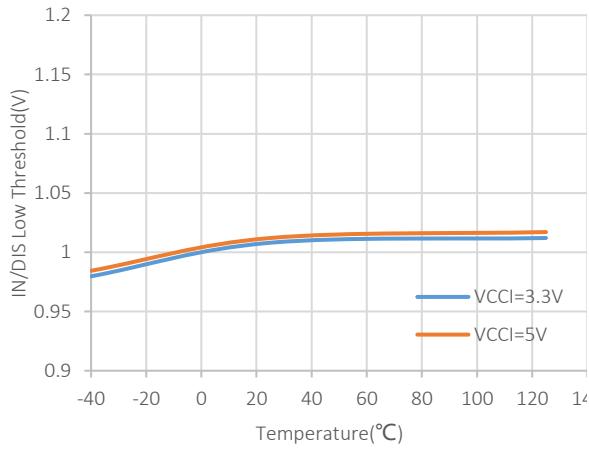

图 27.IN/DIS Low Threshold (fall)

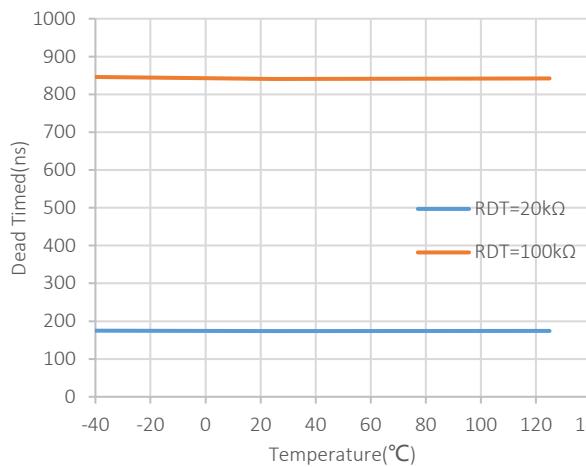

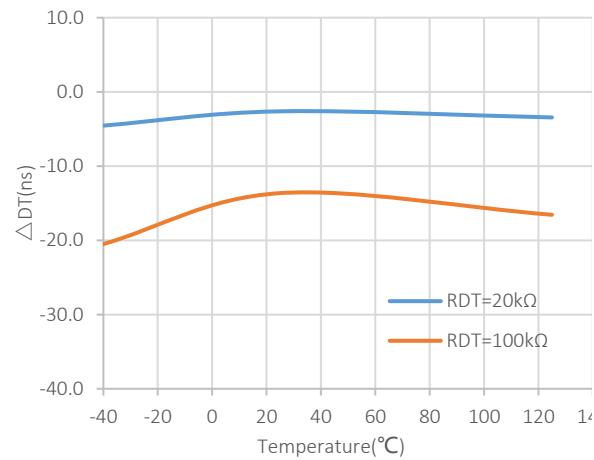

图 28.Dead Time

图 29.Dead Time Matching

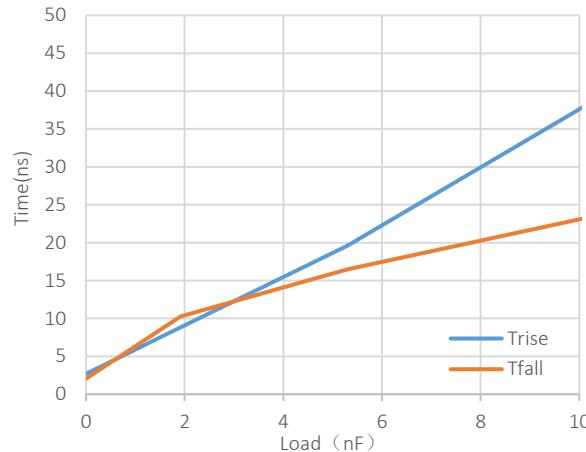

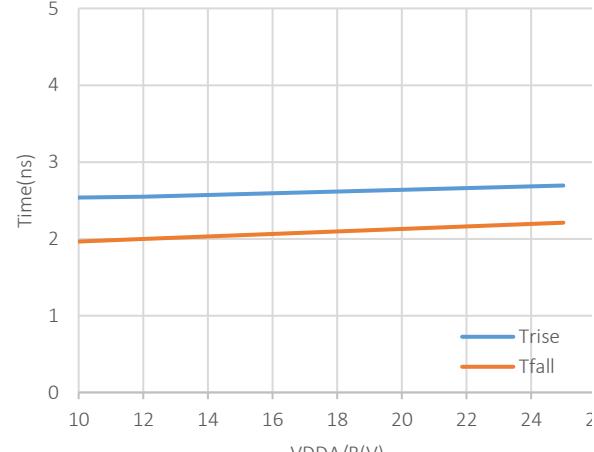

图 30.Rising and Falling Time

图 31.Rise/Fall Time

## 6 参数测量方法

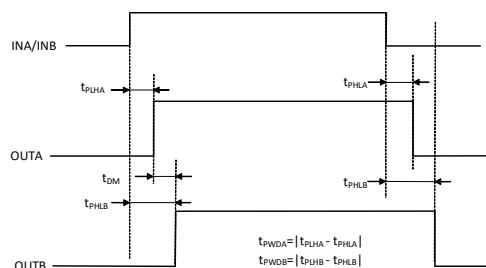

### 6.1 传播延迟和脉宽失真

图 32 显示了如何根据通道 A 和 B 的传播延迟来计算脉冲宽度失真( $t_{PWD}$ )和延迟匹配( $t_{DM}$ )。可以通过将 DT 引脚连接到 VCCI 屏蔽死区功能以确保两个输入同相来进行测量。

图 32.重叠输入，屏蔽死区

## 6.2 上升和下降时间

图 33 显示了上升时间( $t_r$ )和下降时间( $t_f$ )的测量。

图 33. 上升和下降时间的测量

## 6.3 输入和关闭响应时间

图 34 显示了关闭功能的响应时间。将 DISABLE 引脚与控制器连接时，建议在 DISABLE 引脚附近并联一个低 ESR / ESL 的  $1\text{nF}$  电容。

图 34. Disable 信号响应时序

## 6.4 可编程死区时间

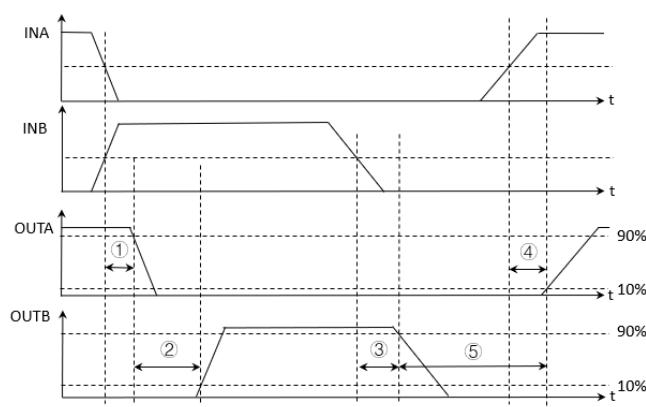

保持 DT 引脚开路或通过适当的电阻( $R_{DT}$ )连接到 GND 可以设置合适的死区时间。

①tPDHL    ②死区时间(通过RDT设定)

③tPDHL    ④tPDLH

⑤死区时间(由输入信号决定, 如果死区时间比设定时间长)

图 35. 死区时间

## 6.5 供电开机延时

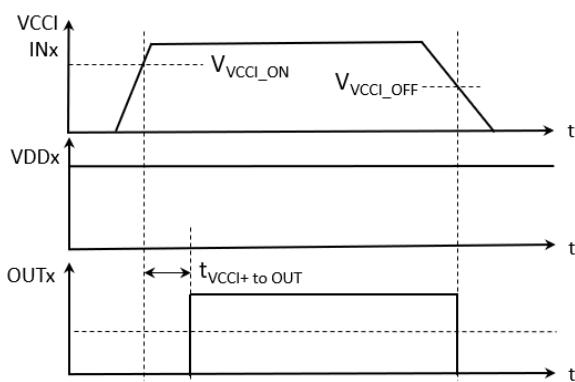

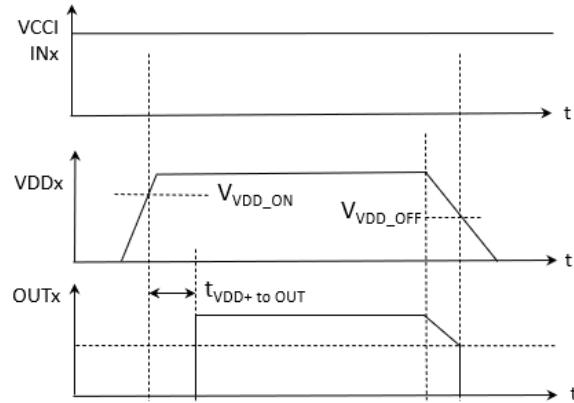

隔离驱动器从供电正常到输出正常建立存在一个上电延时，当 VCCI 达到开机电压后的上电延时定义为  $t_{VCCI+ to OUT}$ ；当 VDD 达到开机电压后的上电延时定义为  $t_{VDD+ to OUT}$ 。建议系统在隔离驱动器的 VCCI 和 VDD 上电准备就绪后，再发送 PWM 信号。图 36 和图 37 给出了 VCCI 和 VDD 的上电延时时序图。

当 INA 或 INB 输入正常的 PWM 信号时，如果 VCCI 或 VDD 电压从低电压上升大于到其开机电压阈值，隔离驱动器建立时间不足，输出将保持为低，直到经过  $t_{VCCI+ to OUT}$  或  $t_{VDD+ to OUT}$  时间后，输出才会跟随输入信号变化。但是，如果 VCCI 或 VDD 电压下降到小于其各自的关断阈值电压，输出将被拉低，在输出被拉低之前会有 $<1\mu s$  的延迟，这主要取决于电源引脚上的电压下降斜率。这种非对称延时旨在确保 VCCI 或 VDD 电压不足时的安全运行。

图 36.VCCI 上电传输延迟

图 37.VDDA/B 上电传输延迟

## 6.6 CMTI 测试

图 38 是简化的 CMTI 测试框图。

图 38.CMTI 测试方法

## 7 详细说明

### 7.1 概述

Pai8233X/Pai8253X 是双通道栅极隔离驱动器系列产品。该系列产品功能丰富，可使其与控制电路很好的集成并保护其驱动的器件，例如可编程的死区时间(DT)控制(Pai8233X)、DISABLE 功能和欠压保护(UVLO)功能。

当输入保持开路或输入脉冲宽度不足时，Pai8233X/Pai8253X 将保持低电平输出。

### 7.2 供电与欠压保护(UVLO)

Pai8233X/Pai8253X 的一次侧和二次侧具有供电欠压保护功能(UVLO)。在开机时，当 VDD 电压低于  $V_{VDD\_ON}$  或启动后低于  $V_{VDD\_OFF}$  时，无论输入引脚(INA 和 INB)的状态如何，输出将保持为低电平。

表 14. Pai8233X/Pai8253X 一次侧欠压保护特性逻辑表

| 条件                                    | 输入  |     | 输出   |      |

|---------------------------------------|-----|-----|------|------|

|                                       | INA | INB | OUTA | OUTB |

| 器件上电过程中 $V_{CCI\_GND} < V_{VCCI\_ON}$ | H   | L   | L    | L    |

|                                       | L   | H   | L    | L    |

|                                       | H   | H   | L    | L    |

|                                       | L   | L   | L    | L    |

| 器件上电后 $V_{CCI\_GND} < V_{VCCI\_OFF}$  | H   | L   | L    | L    |

|                                       | L   | H   | L    | L    |

|                                       | H   | H   | L    | L    |

|                                       | L   | L   | L    | L    |

表 15. Pai8233X/Pai8253X 二次侧欠压保护特性逻辑表

| CONDITION                          | 输入  |     | 输出   |      |

|------------------------------------|-----|-----|------|------|

|                                    | INA | INB | OUTA | OUTB |

| 器件上电过程中 $V_{DD-VSS} < V_{VDD\_ON}$ | H   | L   | L    | L    |

|                                    | L   | H   | L    | L    |

|                                    | H   | H   | L    | L    |

|                                    | L   | L   | L    | L    |

| 器件上电后 $V_{DD-VSS} < V_{VDD\_OFF}$  | H   | L   | L    | L    |

|                                    | L   | H   | L    | L    |

|                                    | H   | H   | L    | L    |

|                                    | L   | L   | L    | L    |

## 7.3 DISABLE 功能

将 DISABLE 引脚设置为高电平会同时关闭两个输出。将 DISABLE 引脚接地(或保持开路)可以使 Pai8233X/Pai8253X 正常运行。DISABLE 功能的响应时间在 20ns 范围内，与传播延迟一样快。仅当 VCCI 保持高于 UVLO 阈值时，DISABLE 功能才起作用(并且是必需的)。

如果不使用 DISABLE 引脚，建议将该引脚接地。在 DIS 引脚与控制器连接使用时，建议在 DIS 引脚对地并联 1nF 的低 ESR / ESL 电容。

## 7.4 可编程死区时间(DT)引脚

Pai8233X/Pai8253X 允许用户通过以下方式设置死区时间(DT):

### 7.4.1 DT 引脚连接到 VCC

没有死区时间，输出完全匹配输入，两路输出信号可以同时为高。

### 7.4.2 DT 引脚悬空或通过编程电阻连接到 GND

如果 DT 引脚保持开路，则死区时间( $t_{DT}$ )设置为<15 ns。死区时间  $t_{DT}$  可以通过 DT 引脚和 GND 之间的电阻  $R_{DT}$  来设置。死区时间的可以用公式 1 来计算。

$$t_{DT} \approx 10 \times R_{DT} \quad (1)$$

电阻  $R_{DT}$  的单位 kΩ，死区时间  $t_{DT}$  的单位 ns。

一个输入信号的下降沿将为另一个信号激活设定的死区时间。如果两个输入同时为高，则两个输出将立即变为低。此功能可以防止直通，并且不会影响正常工作时的死区时间。各种输入输出情况下死区逻辑关系如下图。

图 39. 输入、输出、死区逻辑关系

表 16. 输入、输出、死区逻辑关系

| 工况 | INB | INA | 输出                                                                                                                           |

|----|-----|-----|------------------------------------------------------------------------------------------------------------------------------|

| A  | 下降沿 | 上升沿 | INB 立即将 OUTB 设为低，并将已设定的死区时间分配给 OUTA。在设定的死区时间后，OUTA 将变为高。                                                                     |

| B  | 上升沿 | 下降沿 | INA 立即将 OUTA 设为低，并将已设定的死区时间分配给 OUTB。在设定的死区时间后，OUTB 将变高。                                                                      |

| C  | 下降沿 | 低电平 | INB 立即将 OUTB 设置为低，并将已设定的死区时间分配给 OUTA。在这种情况下，输入信号自身的死区时间比设定的死区时间长。因此，当 INA 变为高电平时，OUTA 立即变为高。                                 |

| D  | 低电平 | 下降沿 | INA 立即将 OUTA 设置为低，并将已设定的死区时间分配给 OUTB。INB 自身的死区时间比设定的死区时间长。因此，当 INB 变为高电平时，OUTB 立即变为高。                                        |

| E  | 高电平 | 上升沿 | 当 INA 变为高，INB 和 OUTB 仍为高时，为避免过冲，INA 立即将 OUTB 拉低并保持 OUTA 低。一段时间后，INB 变为低并将已设定的死区时间分配给 OUTA。这时 OUTB 已经很低，在设定的死区时间之后，OUTA 将变为高。 |

| F  | 上升沿 | 高电平 | 当 INB 变为高，INA 和 OUTA 仍为高时，为避免过冲，INB 立即将 OUTA 拉低并保持 OUTB 低。一段时间后，INA 变为低并将已设定的死区时间分配给 OUTB。这时 OUTA 已经很低，在设定的死区时间之后，OUTB 将变为高。 |

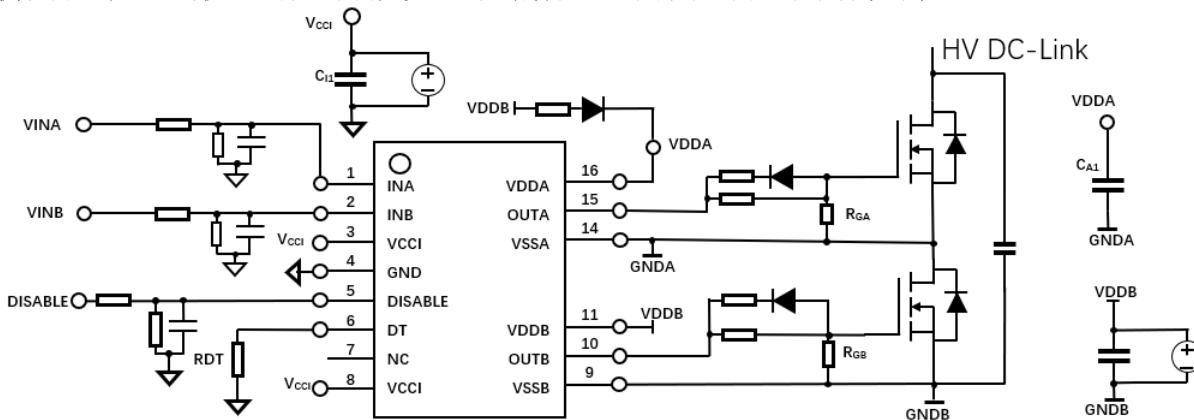

## 8 典型应用

注意：本章节的信息仅供参考，荣湃不保证其准确性或完整性。

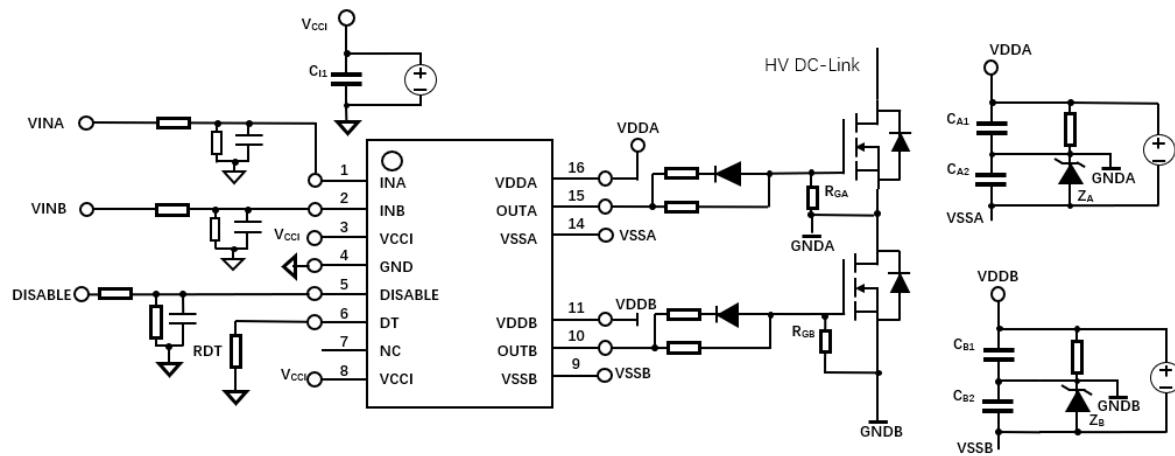

### 8.1 二次侧上管自举供电解决方案一

图 40 中的电路显示了一个参考设计，其中 Pai8233X/Pai8253X 设置为典型的半桥驱动应用。在这种设计方案中，二次侧仅需一个独立的供电电源，不需要负电压关断特性。此种方案适用于中小功率场景。

图 40. 二次侧上管自举供电解决方案一

### 8.2 二次侧上管自举供电解决方案二

图 41. 二次侧上管自举供电解决方案二

如图 41 所示的方案是一种改进型的方案，二次侧只需要使用一路独立的供电电源，通过在栅极驱动回路中增加一个齐纳二极管来构建负压关断，增强栅极的抗干扰能力。

此解决方案有以下局限性：

- 1) 负栅极驱动偏置不仅由齐纳二极管决定，而且还取决于占空比，这意味着负偏置占空比变化时，关断时的电压也会变化。

- 2) V<sub>DDA</sub>-V<sub>SSA</sub> 必须保持足够的电压以保持在推荐的工作电压范围内，这意味着下管在每个开关周期内必须开通足够的时间，给自举电容器充电。

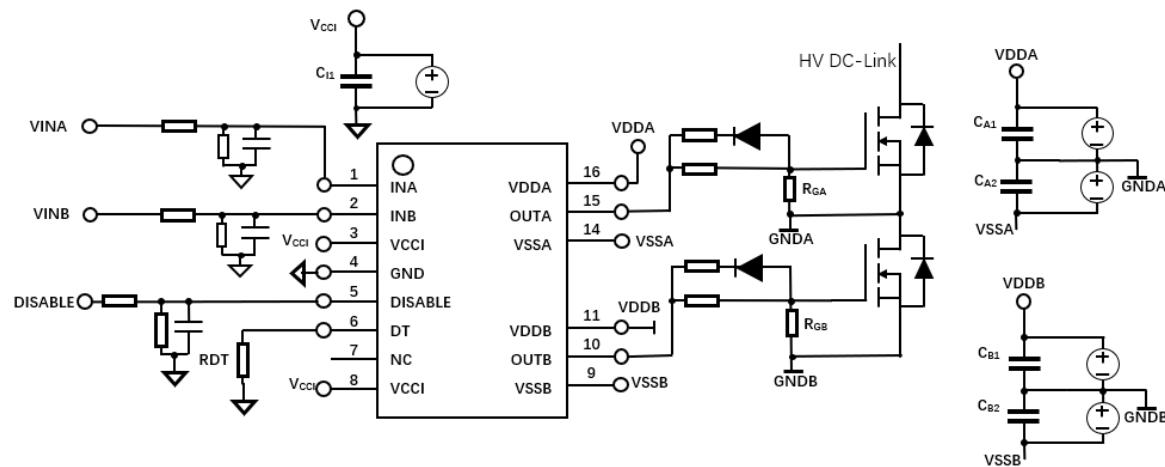

### 8.3 二次侧两路独立电源供电解决方案

图 42. 二次侧两路独立电源供电解决方案

当非理想的 PCB 布局和长封装引线引入寄生电感时，开关期间开关管的栅-源极电压会因为高  $di/dt$  和  $dv/dt$  而产生高振铃。如果振铃超过开关管的栅极阈值电压，则存在意外接通和直通的风险。在开关管上施加负压是一种将振铃保持在阈值以下的常用方法。以下是实现栅极负压关断的一个示例。

图 42 显示了一个示例，在二次侧隔离电源上使用齐纳二极管构造一个负电源电压，为驱动器输出提供负压，让开关管实现负压关断。

负压由齐纳二极管电压设置，如果隔离电源 VDDA 等于 25V，关断电压为 -5.1V，开通电压为  $25V - 5.1V \approx 20V$ 。

### 8.4 二次侧两组独立/四路电源供电解决方案

图 43 显示了一个使用两组独立 / 四路电源的解决方案。

图 43. 二次侧两组独立/四路电源供电解决方案

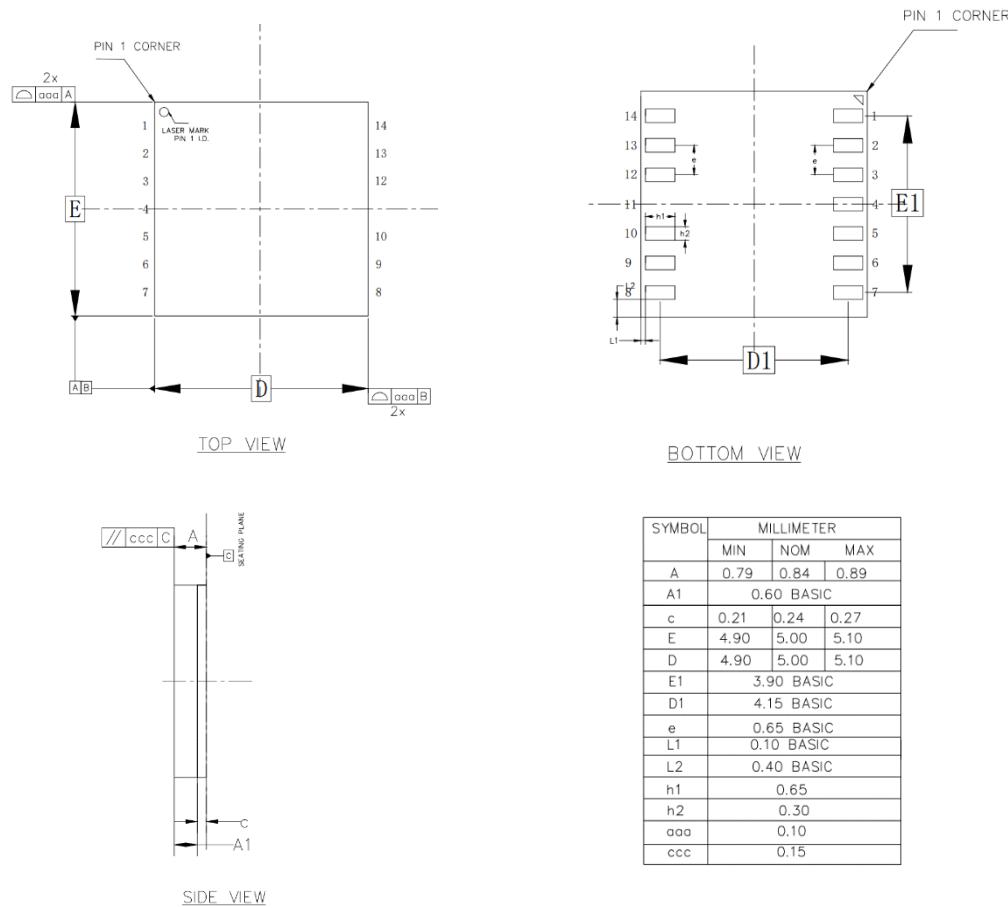

## 9 芯片外形尺寸

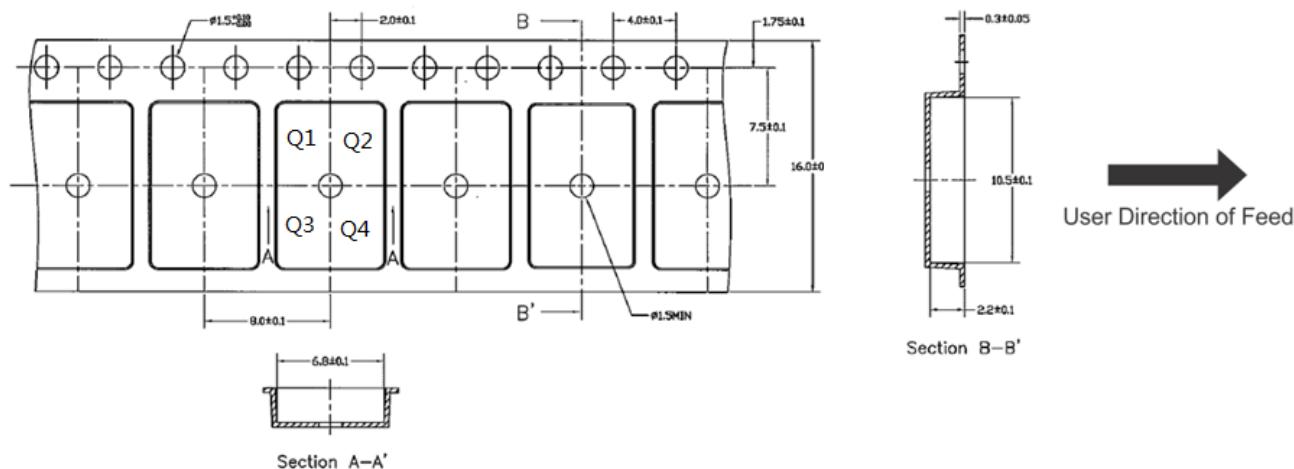

图 44. LGA13 外形尺寸

## 10 焊盘图案

图 45 显示了 LGA 封装中 Pai8233X/Pai8253X 的焊盘细节。下表列出了焊盘中所示的尺寸值。

图 45. LGA13 焊盘图案

表 17.LGA13 焊盘尺寸

| 标识 | 特征                 | 参数   | 单位 |

|----|--------------------|------|----|

| D1 | Pad column spacing | 4.15 | mm |

| e  | Pad row pitch      | 0.65 | mm |

| h2 | Pad width          | 0.30 | mm |

| h1 | Pad length         | 0.65 | mm |

说明：推荐的焊盘尺寸是基于 IPC-7351 设计的

## 11 顶层丝印图

图 46 顶层丝印图

|        |                              |

|--------|------------------------------|

| Line 1 | PaiXXXXXX=产品名称               |

| Line 2 | YY = 年份<br>WW = 周<br>ZZ=工厂代码 |

| Line 3 | XXXXX, 暂无特殊含义                |

## 12 包装信息

图 47.LG13 包装示意图

说明：芯片的 Pin1 在 Q1 区域。

## 13 订购指南

表 18.订购型号

| 型号           | 工作温度范围    | 峰值电流  | 最小工作电压 | 绝缘耐压 (kV rms) | 封装描述  | 潮敏等级,最高焊接温度 <sup>1</sup> | 每卷数量 |

|--------------|-----------|-------|--------|---------------|-------|--------------------------|------|

| Pai8233A- LR | -40~125°C | 4A/8A | 9.2V   | 2.5kVrms      | LGA13 | Level-3-260°C            | 3000 |

| Pai8233B- LR | -40~125°C | 4A/8A | 6.5V   | 2.5kVrms      | LGA13 | Level-3-260°C            | 3000 |

| Pai8233C- LR | -40~125°C | 4A/8A | 9.2V   | 2.5kVrms      | LGA13 | Level-3-260°C            | 3000 |

| Pai8233D- LR | -40~125°C | 4A/8A | 6.5V   | 2.5kVrms      | LGA13 | Level-3-260°C            | 3000 |

| Pai8233E- LR | -40~125°C | 4A/8A | 13.7V  | 2.5kVrms      | LGA13 | Level-3-260°C            | 3000 |

| Pai8233F- LR | -40~125°C | 4A/8A | 13.7V  | 2.5kVrms      | LGA13 | Level-3-260°C            | 3000 |

| Pai8253A- LR | -40~125°C | 4A/8A | 9.2V   | 2.5kVrms      | LGA13 | Level-3-260°C            | 3000 |

| Pai8253B- LR | -40~125°C | 4A/8A | 6.5V   | 2.5kVrms      | LGA13 | Level-3-260°C            | 3000 |

| Pai8253C- LR | -40~125°C | 4A/8A | 9.2V   | 2.5kVrms      | LGA13 | Level-3-260°C            | 3000 |

| Pai8253D- LR | -40~125°C | 4A/8A | 6.5V   | 2.5kVrms      | LGA13 | Level-3-260°C            | 3000 |

| Pai8253E- LR | -40~125°C | 4A/8A | 13.7V  | 2.5kVrms      | LGA13 | Level-3-260°C            | 3000 |

| Pai8253F- LR | -40~125°C | 4A/8A | 13.7V  | 2.5kVrms      | LGA13 | Level-3-260°C            | 3000 |

说明：

- 1) 潮敏等级,允许最高焊接温度 - 根据 JEDEC 行业标准分类的湿度敏感度等级, 以及允许最高焊接温度。

## 14 免责声明

荣湃半导体尽量为客户提供最新、准确和深入的文档。但是，荣湃半导体对使用它或因使用它可能导致的任何专利侵权或第三方其他权利不承担任何责任。特征数据, 可用型号和提供的“典型”参数在不同的应用中可能并且确实有所不同。本文描述的应用示例仅用于说明目的。荣湃半导体保留进行更改的权利, 恕不另行通知, 并且不对此处的产品信息, 规格和说明进行任何限制, 并且对所包含信息的准确性或完整性不做任何保证。荣湃半导体不对使用此处提供的信息的后果承担任何责任。

商标和注册商标是其各自所有者的财产。本文档并不暗示或明示授予其设计或制造任何集成电路的版权许可。

201203 上海市浦东新区博霞路 22 号 307-309 室 021-50850681

荣湃半导体(上海)有限公司, 版权所有。

<http://www.rpssemi.com/>

## 15 版本历史

| 版本      | 日期         | 页面   | 变更记录                    |

|---------|------------|------|-------------------------|

| Rev0.1  | 2022-04-08 | 所有   | 首次发布                    |

| Rev0.2  | 2023-03-10 | 所有   | 更新 Pai8253X 信息          |

| Rev0.3  | 2023-11-29 | 4 页  | 表 6 CLR>3.2mm CPG>3.2mm |

| Rev0.4  | 2023-03-25 | 5 页  | 更新安全相关认证                |

| Rev 0.5 | 2024-07-17 | 23 页 | 更新订购指南                  |

| Rev0.6  | 2024-08-01 | 4 页  | 更新绝缘规格                  |

|         |            | 5 页  | 更新安全相关认证                |

| Rev1.0  | 2024.10.25 | 3 页  | 添加 ESD 信息               |

| Rev1.1  | 2025.01.25 | 3 页  | 更新推荐工作条件                |

|         |            | 8 页  | 增加 Pai8253X 死区时间描述      |

单击下面可查看定价，库存，交付和生命周期等信息

[>>2pai\\_semi\(荣湃半导体\)](#)