#### **Features**

Input Voltage Range: 2.2 V to 6.5 V

Output Voltage Options:

- Fixed Output: 1.2 V, 1.8 V, 3.3 V and 5 V

Adjustable Output: 0.8 V to 6 V

±3% Accuracy over Line Regulation, Load Regulation, and Operating Temperature Range

1 A Maximum Output Current

· Low Dropout Voltage: 500 mV Maximum at 1 A

· High PSRR:

80 dB at 1 kHz

- 50 dB at 1 MHz

4.5 μV<sub>RMS</sub> Output Voltage Noise (100 Hz to 100 kHz)

· Excellent Transient Response

Stable with a 4.7 μF or Larger Ceramic Output Capacitor

Over-Current Protection and Over-Temperature Protection

Package: 3×3 DFN-8

#### **Applications**

Communication: CPU, ASIC, FPGA, CPLD, DSP

High-Performance Analog: ADC, DAC, LVDS, VCO

Noise-Sensitive Imaging: CMOS Sensors, Video ASICs

#### **Description**

The TPL910A series are 1-A high-current,  $4.5-\mu V_{RMS}$  low-noise, high-PSRR, high-accuracy linear regulators with only 500-mV maximum ultra-low dropout voltage at 1-A load current. The TPL910A series support both fixed output voltage ranges from 1.2 V to 5 V and adjustable output voltage ranges from 0.8 V to 6 V with external resistor divider.

Ultra-low noise, high PSRR, and high output current capability makes the TPL910A series as the ideal power supply for noise-sensitive applications, such as high-speed communication facilities, and high-definition imaging equipment. Accurate output voltage tolerance, excellent transient response, and adjustable soft-start control ensures the TPL910A series products optimal power supply for the large-scale processors or digital loads, such as such as ASIC, FPGA, CPLD and DSP.

The TPL910A series provide small 3×3 DFN-8 package with guaranteed operating temperature ranges from –40°C to +125°C.

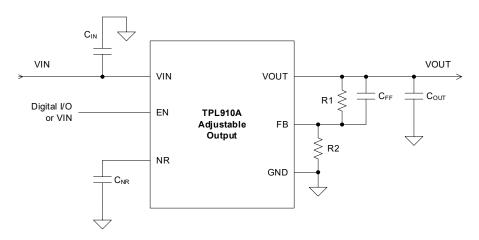

### **Typical Application Circuit**

## **Product Family Table**

| Part Number Order Number |                 | Output Voltage (V) | Package   |  |

|--------------------------|-----------------|--------------------|-----------|--|

| TPL910A                  | TPL910ADJA-DF6R | Adjustable         | 3×3 DFN-8 |  |

#### **Table of Contents**

| Features                                |          |

|-----------------------------------------|----------|

| Applications                            |          |

| Description                             |          |

| Typical Application Circuit             |          |

| Product Family Table                    | 2        |

| Revision History                        | 4        |

| Pin Configuration and Functions         | 5        |

| Pin Functions                           | 5        |

| Specifications                          | 6        |

| Absolute Maximum Ratings                | 6        |

| ESD, Electrostatic Discharge Protection | 6        |

| Recommended Operating Conditions        | 6        |

| Thermal Information                     | 6        |

| Electrical Characteristics              |          |

| Typical Performance Characteristics     | <u>C</u> |

| Detailed Description                    | 11       |

| Overview                                | 11       |

| Functional Block Diagram                | 11       |

| Feature Description                     | 11       |

| Application and Implementation          | 14       |

| Application Information                 | 14       |

| Typical Application                     | 14       |

| Layout                                  | 15       |

| Layout Guideline                        | 15       |

| Tape and Reel Information               |          |

| Package Outline Dimensions              | 17       |

| 3×3 DFN-8                               |          |

| Ouden Information                       | 4.0      |

## **Revision History**

| Date       | Revision  | Notes               |

|------------|-----------|---------------------|

| 2020-12-31 | Rev.Pre.0 | Preliminary Version |

| 2021-08-31 | Rev.A.0   | Initial Release     |

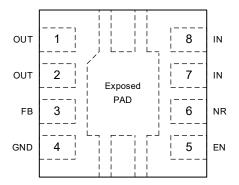

### **Pin Configuration and Functions**

#### **TPL910A Series**

DFN-8 Package Top View

#### **Pin Functions**

| Р    | Pin            |     | Pin                                                                                                                                                                                                                                    |  | Donastintias. |

|------|----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|---------------|

| No.  | Name           | I/O | Description                                                                                                                                                                                                                            |  |               |

| 5    | EN             | I   | Regulator enable pin. Drive EN high to turn on the regulator; drive EN low to turn off the regulator. For automatic startup, connect EN to IN directly. The EN pin must not be left floating.                                          |  |               |

| 3    | FB             | I   | Output voltage feedback pin. Connect to an external resistor divider to adjust the output voltage. A 10-nF feed-forward capacitor from FB to OUT (as close as possible to FB pin) is recommended to maximize regulator ac performance. |  |               |

| 4    | GND            | -   | Ground reference pin. Connect GND pin to PCB ground plane directly.                                                                                                                                                                    |  |               |

| 7, 8 | IN             | I   | Input voltage pin. Suggest connecting a 10-µF or larger ceramic capacitor from IN to ground (as close as possible to IN pin) to reduce the jitter from previous-stage power supply.                                                    |  |               |

| 6    | NR/SS          | I   | Noise-reduction and soft-start pin. A 10-nF or larger capacitor from NR/SS to GND (as close as possible to NR/SS pin) is recommended to maximize ac performance.                                                                       |  |               |

| 1, 2 | OUT            | 0   | Regulated output voltage pin. A 4.7-µF or larger ceramic capacitor from OUT to ground (as close as possible to OUT pin) is required to ensure regulator stability.                                                                     |  |               |

| _    | Exposed<br>Pad | _   | Exposed PAD must be connected to a large-area ground plane to maximum the thermal performance.                                                                                                                                         |  |               |

### **Specifications**

#### **Absolute Maximum Ratings**

|                  | Parameter                           | Min  | Max                   | Unit |

|------------------|-------------------------------------|------|-----------------------|------|

| IN, EN OUT       |                                     | -0.3 | 7                     | V    |

|                  |                                     | -0.3 | V <sub>IN</sub> + 0.3 | V    |

| FB, NR           | FB, NR                              |      | 3.6                   | V    |

| TJ               | Junction Temperature Range          | -40  | 150                   | °C   |

| T <sub>STG</sub> | Storage Temperature Range           | -65  | 150                   | °C   |

| TL               | Lead Temperature (Soldering 10 sec) |      | 260                   | °C   |

<sup>(1)</sup> Stresses beyond the Absolute Maximum Ratings may permanently damage the device.

#### **ESD, Electrostatic Discharge Protection**

| Symbol | Parameter                | Condition                             | Minimum Level | Unit |

|--------|--------------------------|---------------------------------------|---------------|------|

| НВМ    | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±4000         | V    |

| CDM    | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±1500         | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### **Recommended Operating Conditions**

| Parameter       |                            | Min | Тур | Max | Unit |

|-----------------|----------------------------|-----|-----|-----|------|

| IN              | Input voltage              | 2.2 |     | 6.5 | V    |

| EN              | Enable voltage             | 0   |     | 6.5 | V    |

| OUT             | Output voltage             | 0.8 |     | 6   | V    |

| OUT             | Output current             | 0   |     | 1   | Α    |

| Соит            | Output capacitor           | 4.7 |     |     | μF   |

| C <sub>FF</sub> | Feed-forward capacitor     |     | 10  |     | nF   |

| C <sub>NR</sub> | NR capacitor               |     | 10  |     | nF   |

| TJ              | Junction Temperature Range | -40 |     | 125 | °C   |

#### **Thermal Information**

| Package Type | θ <sub>JA</sub> | <b>Ө</b> лс | Unit |  |

|--------------|-----------------|-------------|------|--|

| 3×3 DFN-8    | 69.3            | 8.16        | °C/W |  |

<sup>(2)</sup> All voltage values are with respect to GND.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### **Electrical Characteristics**

All test conditions:  $T_J = -40^{\circ}\text{C}$  to +125°C (typical value at  $T_J = +25^{\circ}\text{C}$ ),  $V_{IN} = V_{OUT(NOM)} + 0.5 \text{ V}$  or 2.2 V, whichever is greater;  $V_{EN} = 2.2 \text{ V}$ ,  $I_{OUT} = 1 \text{ mA}$ ,  $C_{IN} = 4.7 \mu\text{F}$ ,  $C_{OUT} = 4.7 \mu\text{F}$ ,  $C_{NR} = 10 \text{ nF}$ ,  $C_{FF} = \text{open}$ , unless otherwise noted.

| Parameter           |                              | Conditions                                                                                                                                    | Min | Тур  | Max | Unit |

|---------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Supply              | Input Voltage and Current    |                                                                                                                                               |     |      |     |      |

| VIN                 | Supply voltage range (1)     |                                                                                                                                               | 2.2 |      | 6.5 | V    |

| 10/10               | Input supply UVLO            | $V_{IN}$ rising, $R_L = 1 \text{ k}\Omega$                                                                                                    |     |      | 2.1 | V    |

| UVLO                | Hysteresis                   |                                                                                                                                               |     | 70   |     | mV   |

|                     | CNID min augment             | V <sub>IN</sub> = 6.5 V, I <sub>OUT</sub> = 1 mA                                                                                              |     | 130  | 190 | μA   |

| IGND                | GND pin current              | V <sub>IN</sub> = 6.5 V, I <sub>OUT</sub> = 1 A                                                                                               |     | 5.4  | 8   | mA   |

| I <sub>SD</sub>     | Shutdown current             | V <sub>IN</sub> = 6.5 V, V <sub>EN</sub> = 0 V                                                                                                |     | 2.2  | 10  | μA   |

| Device I            | Enable                       |                                                                                                                                               |     |      |     |      |

| V <sub>IH(EN)</sub> | EN high-level input voltage  | Device enable                                                                                                                                 | 1.2 |      | 6.5 | V    |

| V <sub>IL(EN)</sub> | EN low-level input voltage   | Device disable                                                                                                                                | 0   |      | 0.4 | V    |

| I <sub>EN</sub>     | EN leakage current           | V <sub>IN</sub> = 6.5 V, V <sub>EN</sub> = 0 V to 6.5 V                                                                                       |     | 0.1  | 1   | μA   |

| Regulat             | ed Output Voltage and Curren |                                                                                                                                               |     |      |     |      |

| $V_{FB}$            | Feedback voltage (2)         |                                                                                                                                               |     | 0.8  |     | V    |

| I <sub>FB</sub>     | FB pin leakage current (2)   | V <sub>IN</sub> = 6.5 V, stress V <sub>FB</sub> = 0.8V                                                                                        |     | 0.1  | 1   | μA   |

| V <sub>NR/SS</sub>  | NR/SS pin voltage            |                                                                                                                                               |     | 0.8  |     | V    |

| I <sub>NR/SS</sub>  | NR/SS pin charging current   | V <sub>IN</sub> = 6.5 V, V <sub>NR</sub> = GND                                                                                                |     | 6.2  | 9   | μA   |

| Vоит                | Output accuracy (3)          | V <sub>IN</sub> = V <sub>OUT(NOM)</sub> + 0.5 V or 2.2 V to 6.5 V,<br>V <sub>OUT</sub> = 0.8 V to 6 V, I <sub>OUT</sub> = 100 mA to 500<br>mA | -2% |      | 2%  |      |

|                     |                              | V <sub>IN</sub> = V <sub>OUT(NOM)</sub> + 0.5 V or 2.2 V to 6.5 V,<br>V <sub>OUT</sub> = 0.8 V to 6 V, I <sub>OUT</sub> = 100 mA to 1 A       | -3% |      | 3%  |      |

| $\Delta V_{OUT}$    | Line regulation              | tion $V_{IN} = V_{OUT(NOM)} + 0.5 \text{ V or } 2.2 \text{ V to } 6.5 \text{ V},$ $I_{OUT} = 100 \text{ mA}$                                  |     | 0.03 |     | mV/V |

|                     | Load regulation              | I <sub>OUT</sub> = 100 mA to 1 A                                                                                                              |     | 2    |     | mV/A |

<sup>(1)</sup> Minimum  $V_{IN} = V_{OUT(NOM)} + V_{DO}$  or 2.2 V, whichever is greater.

<sup>(2)</sup> For adjustable output voltage version only.

<sup>(3)</sup> Resistor tolerance is not included. Output accuracy is not tested at this condition:  $V_{OUT} = 0.8 \text{ V}$ ,  $4.5 \text{ V} \le V_{IN} \le 5.5 \text{ V}$ , and  $750 \text{ mA} \le I_{OUT} \le 1 \text{ A}$ , because the power dissipation is out of package limitation.

#### **Electrical Characteristics (continued)**

All test conditions:  $T_J = -40^{\circ}C$  to +125°C (typical value at  $T_J = +25^{\circ}C$ ),  $V_{IN} = V_{OUT(NOM)} + 0.5$  V or 2.2 V, whichever is greater;  $V_{EN} = 2.2$  V,  $I_{OUT} = 1$  mA,  $C_{IN} = 4.7$   $\mu$ F,  $C_{OUT} = 4.7$   $\mu$ F,  $C_{NR} = 10$  nF,  $C_{FF} = open$ , unless otherwise noted.

| Parameter        |                                       | Conditions                                                                                                                                  |                                                                         |      | Тур | Max | Unit              |

|------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------|-----|-----|-------------------|

| Regulat          | ed Output Voltage and Cu              | rrent                                                                                                                                       |                                                                         |      |     |     |                   |

|                  |                                       | $V_{IN} = V_{OUT(NOM)} + 0.5 V_{OUT(NOM)}$<br>500 mA, $V_{FB} = GND$ or                                                                     | or 2.2 V to 6.5 V, I <sub>OUT</sub> = rV <sub>SNS</sub> = GND           |      |     | 250 | mV                |

| $V_{DO}$         | Dropout voltage (4)                   | $V_{IN} = V_{OUT(NOM)} + 0.5 V_{OUT(NOM)}$<br>750 mA, $V_{FB} = GND$ of                                                                     | or 2.2 V to 6.5 V, I <sub>OUT</sub> = V <sub>SNS</sub> = GND            |      |     | 350 | mV                |

|                  |                                       | $V_{IN} = V_{OUT(NOM)} + 0.5 V$<br>1 A, $V_{FB} = GND$ or $V_{SN}$                                                                          | or 2.2 V to 6.5 V, I <sub>OUT</sub> = I <sub>S</sub> = GND              |      |     | 500 | mV                |

| I <sub>LIM</sub> | Output current limit                  | V <sub>OUT</sub> is forced at 0.9 ×                                                                                                         | $V_{OUT(NOM)}, V_{IN} \ge 3.3 V$                                        | 1.1. | 1.6 |     | Α                 |

| I <sub>SC</sub>  | Short circuit to ground current limit | V <sub>OUT</sub> is forced to ground, T <sub>A</sub> = 25°C                                                                                 |                                                                         |      | 0.6 |     | А                 |

| tstr             | Start-up time                         | $V_{OUT(NOM)} = 3.3 \text{ V, } V_{OU}$<br>$R_L = 3.3 \text{ k}\Omega, C_{OUT} = 10$                                                        | r = 0% to 90% V <sub>OUT(NOM)</sub> ,<br>) μF, C <sub>NR</sub> = 470 nF |      | 80  |     | ms                |

| PSRR a           | nd Noise                              |                                                                                                                                             |                                                                         |      |     |     |                   |

|                  | Power supply ripple                   | V <sub>IN</sub> = 4.3 V, V <sub>OUT</sub> =                                                                                                 | f = 1 kHz                                                               |      | 80  |     | dB                |

| PSRR             |                                       | 3.3 V, I <sub>OUT</sub> = 1 A,<br>C <sub>OUT</sub> = 4.7µF, C <sub>NR</sub> =<br>470 nF, C <sub>FF</sub> = 470 nF                           | f = 10 kHz                                                              |      | 65  |     | dB                |

| PORK             | rejection                             |                                                                                                                                             | f = 100 kHz                                                             |      | 54  |     | dB                |

|                  |                                       |                                                                                                                                             | f = 1 MHz                                                               |      | 45  |     | dB                |

| V <sub>N</sub>   | Output noise voltage                  | BW = 100 Hz to 100 kHz, $V_{IN}$ = 3.8 V, $V_{OUT}$ = 3.3 V, $I_{OUT}$ = 1 A, $C_{OUT}$ = 4.7 $\mu$ F, $C_{NR}$ = 470 nF, $C_{FF}$ = 470 nF |                                                                         |      | 4.5 |     | μV <sub>RMS</sub> |

| Temper           | ature Range                           |                                                                                                                                             |                                                                         |      |     |     |                   |

| T <sub>SD</sub>  | Thermal shutdown threshold            | Temperature increasing                                                                                                                      |                                                                         |      | 165 |     | °C                |

|                  | Hysteresis                            |                                                                                                                                             |                                                                         |      | 20  |     | °C                |

<sup>(4)</sup> Dropout voltage is the minimum input to output voltage differential needed to maintain regulation at a specified output current and measure for V<sub>OUT(NOM)</sub>≥ 2.2 V. In dropout mode, the output voltage will be equal to: V<sub>IN</sub> − V<sub>DO</sub>.

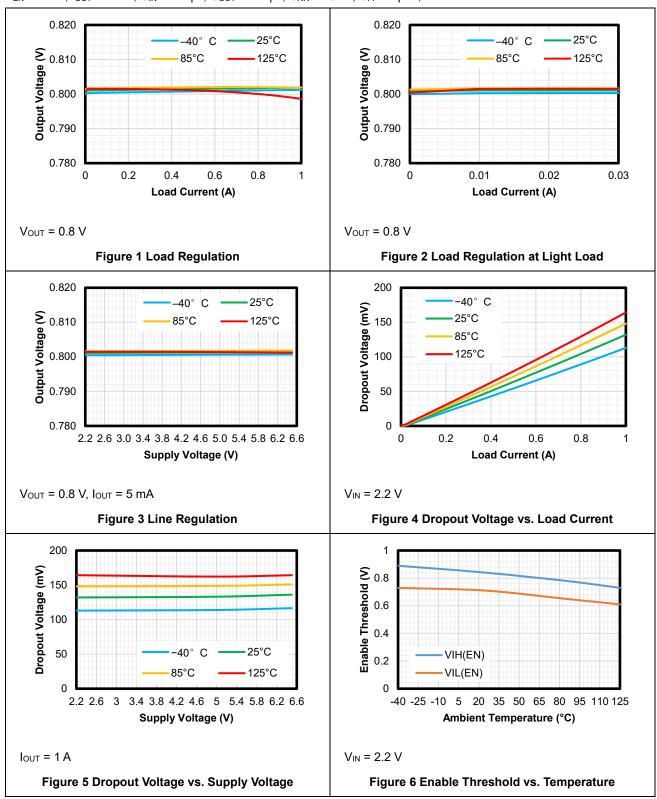

#### **Typical Performance Characteristics**

All test conditions:  $T_J = -40$ °C to +125°C (typical value at  $T_J = +25$ °C),  $V_{IN} = V_{OUT(NOM)} + 0.5$  V or 2.2 V, whichever is greater;  $V_{EN} = 2.2$  V,  $I_{OUT} = 1$  mA,  $C_{IN} = 4.7$   $\mu$ F,  $C_{OUT} = 4.7$   $\mu$ F,  $C_{NR} = 10$  nF,  $C_{FF} = 0$  open, unless otherwise noted.

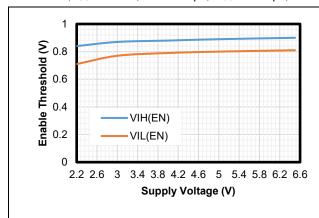

#### **Typical Performance Characteristics (Continued)**

All test conditions:  $T_J = -40$ °C to +125°C (typical value at  $T_J = +25$ °C),  $V_{IN} = V_{OUT(NOM)} + 0.5$  V or 2.2 V, whichever is greater;  $V_{EN}$  = 2.2 V,  $I_{OUT}$  = 1 mA,  $C_{IN}$  = 4.7  $\mu$ F,  $C_{OUT}$  = 4.7  $\mu$ F,  $C_{NR}$  = 10 nF,  $C_{FF}$  = open, unless otherwise noted.

$T_A = 25^{\circ}C$

Figure 7 Enable Threshold vs. Supply Voltage

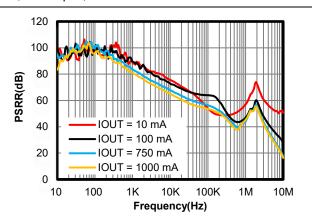

$V_{IN}$  = 4.3 V,  $V_{OUT}$  = 3.3 V,  $C_{OUT}$  = 10  $\mu$ F,  $C_{NR/SS}$  = 470 nF,  $C_{FF} = 470 \text{ nF}$

#### Figure 8 PSRR

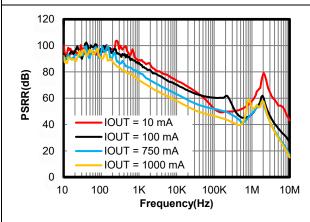

$V_{IN} = 3.8 \text{ V}, V_{OUT} = 3.3 \text{ V}, C_{OUT} = 4.7 \mu\text{F}, C_{NR/SS} = 470 \text{ nF},$ C<sub>FF</sub> = 470 nF

Figure 9 PSRR

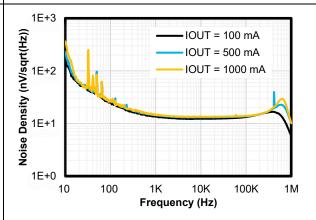

$V_{IN} = 3.8 \text{ V}, V_{OUT} = 3.3 \text{ V}, C_{OUT} = 4.7 \mu\text{F}, C_{NR/SS} = 470 \text{ nF},$  $C_{FF} = 470 \text{ nF}$

Figure 10 Noise

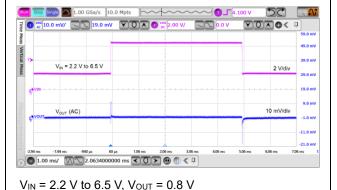

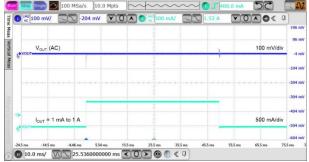

Figure 11 Line Transient

$I_{OUT} = 1 \text{ mA to } 1 \text{ A}, V_{OUT} = 0.8 \text{ V}$

Figure 12 Load Transient

#### **Detailed Description**

#### Overview

The TPL910A series are 1-A high-current,  $4.5-\mu V_{RMS}$  low-noise, high-PSRR, high-accuracy linear regulators with only 500-mV maximum ultra-low dropout voltage at 1-A load current. The TPL910A series support both fixed output voltage ranges from 1.2 V to 5 V and adjustable output voltage ranges from 0.8 V to 6 V with external resistor divider.

Ultra-low noise, high PSRR, and high output current capability makes the TPL910A series as the ideal power supply for noise-sensitive applications, such as high-speed communication facilities, and high-definition imaging equipment. Accurate output voltage tolerance, excellent transient response, and adjustable soft-start control ensures the TPL910A series products optimal power supply for the large-scale processors or digital loads, such as such as ASIC, FPGA, CPLD and DSP.

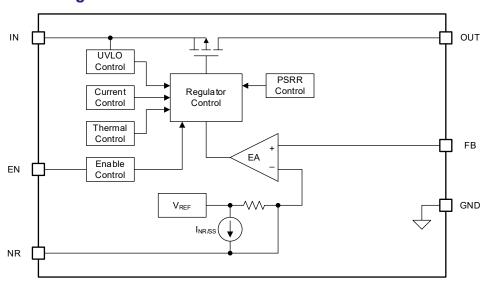

#### **Functional Block Diagram**

Figure 13 Functional Block Diagram

#### **Feature Description**

#### **Enable (EN)**

The TPL910A series provide a device enable pin (EN) to enable or disable the device. Connect this pin to the GPIO of an external digital logic control circuit to control the device. When the V<sub>EN</sub> voltage falls below V<sub>IL(EN)</sub>, the LDO device turns off, and when the V<sub>EN</sub> ramps above V<sub>IH(EN)</sub>, the LDO device turns on.

#### **Under-Voltage Lockout (IN and UVLO)**

The TPL910A series use an under-voltage lockout circuit to keep the output shut off until the internal circuitry operates properly. Refer to the Electrical Characteristics table for UVLO threshold and hysteresis.

#### **Fixed Output Voltage (OUT)**

The TPL910A series are available in fixed voltage versions of 1.2 V, 1.8 V, 3.3 V and 5 V. When the input voltage is higher than  $V_{\text{OUT(NOM)}} + V_{\text{DO}}$  or 2.2V, whichever is greater, OUT pin is regulated with fixed voltage. When the input voltage falls below  $V_{\text{OUT(NOM)}} + V_{\text{DO}}$  and greater than UVLO threshold, OUT pin tracks the input voltage, and the output voltage value equals to  $V_{\text{IN}} - V_{\text{DO}}$ .

#### Adjustable Output Voltage (OUT and FB)

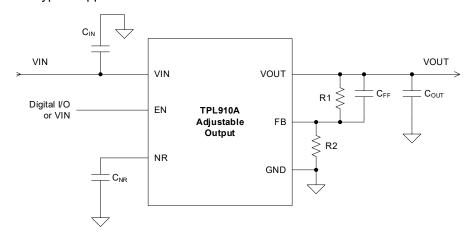

The TPL910A series are also available in adjustable voltage versions of 0.8 V to 5 V. Using external resistors divider, the output voltage of TPL910A series is determined by the value of the resistor R1 and R2 in Figure 15. Use Equation 1 to calculate the output voltage.

$$V_{OUT} = V_{FB} \times \left(1 + \frac{R1}{R2}\right) \tag{1}$$

Where the feedback voltage V<sub>FB</sub> is 0.8 V.

Table 1 provides a list of recommended resistor combinations to achieve the common output voltage values.

**External Resistors Divider Target Output Voltage (V)** Calculated Output Voltage (V) R1 (kΩ) R2 (kΩ) 0.80 0 10 0.800 0.85 0.62 10 0.850 0.90 1.24 10 0.899 0.95 1.87 10 0.950 1.00 2.49 10 0.999 1.20 4.99 10 1.199 1.50 8.75 10 1.500 12.5 1.80 10 1.800 2.50 21.3 10 2.504 25 10 2.80 2.800 3.00 27.5 10 3.000 3.30 31.3 10 3.304 3.60 35 10 3.600 4.50 46.3 10 4.504 10 5.00 52.5 5.000

**Table 1 External Resistor Combinations**

#### **Programmable Soft Start**

The TPL910A series integrate a programmable soft-start function to control the output voltage ramp-up slew rate and start-up time. By selecting the external capacitor at the NR/SS pin, the output start-up time can be calculated with Equation 2.

$$t_{Start-up} = 1.25 \times \frac{V_{NR/SS} \times C_{NR/SS}}{I_{NR/SS}}$$

(2)

Where, the typical value of  $V_{NR/SS}$  is 0.8 V, the typical value of  $I_{NR/SS}$  is 6.2  $\mu$ A,  $C_{NR/SS}$  is the external capacitor at the NR/SS pin.

#### **Over-Current Protection**

The TPL910A series integrate an internal current limit that helps to protect the regulator during fault conditions.

- When the output voltage is pulled down below the regulated voltage, over-current protection starts to work and limit the output current to I<sub>LIM</sub>

- When the output voltage is pulled down below the short-to-ground threshold (about 140 mV), or shorted to ground directly, short-to-ground protection starts to work and limit the output current to Isc.

- During startup, the output current is limited to I<sub>SC</sub> before the output voltage ramps higher than the short-to-ground threshold.

Under the over-current conditions, the internal junction temperature ramps up quickly. When the junction temperature is high enough, it will cause the over temperature protection.

#### **Over-Temperature Protection**

The over-temperature protection starts to work when the junction temperature exceeds the thermal shutdown (TSD) threshold, which turns off the regulator immediately. Until when the device cools down and the junction temperature falls below the thermal shutdown threshold minus thermal shutdown hysteresis, the regulator turns on again.

The junction temperature range should be limited according to the Recommended Operating Conditions table, continuously operating above the junction temperature range will reduce the device lifetime.

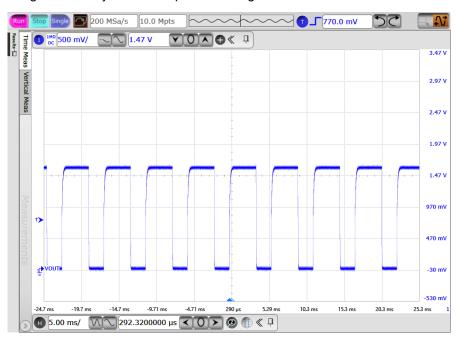

**Figure 14 Over-Temperature Protection**

#### **Application and Implementation**

#### NOTE

Information in the following applications sections is not part of the 3PEAK's component specification and 3PEAK does not warrant its accuracy or completeness. 3PEAK's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### **Application Information**

The TPL910A series products are 1-A high-current,  $4.5-\mu V_{RMS}$  low-noise, high-PSRR, high-accuracy linear regulators with only 500-mV maximum ultra-low dropout voltage. The following application schematic shows a typical usage of the TPL910A series.

#### **Typical Application**

Figure 15 shows the typical application schematic of the TPL910A series.

Figure 15 Adjustable Output Operation

#### **Input Capacitor and Output Capacitor**

The TPL910A series is designed to be stable with low equivalent series resistance (ESR) ceramic capacitors at the input, output, and noise-reduction pin (NR/SS). It is recommended to use ceramic capacitors with X7R-, X5R-, and COG-rated dielectric materials to get good capacitive stability across temperature.

3PEAK recommends adding a 10  $\mu$ F or greater capacitor with a 0.1  $\mu$ F bypass capacitor in parallel at IN pin to keep the input voltage stable. The voltage rating of the capacitors must be greater than the maximum input voltage.

To ensure loop stability, the TPL910A series requires a minimum 4.7  $\mu$ F low ESR output capacitor. 3PEAK recommends selecting a X7R-type 10- $\mu$ F ceramic capacitor with low ESR over temperature.

Both input capacitors and output capacitors must be placed as close to the device pins as possible.

#### **Power Dissipation**

During normal operation, LDO junction temperature should meet the requirement in the Recommended Operating Conditions table. Using below equations to calculate the power dissipation and estimate the junction temperature.

The power dissipation can be calculated using Equation 3.

$$P_{D} = (V_{IN} - V_{OUT}) \times I_{OUT} + V_{IN} \times I_{GND}$$

(3)

The junction temperature can be estimated using Equation 4.  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

$$\mathsf{T}_{\mathsf{J}} = \mathsf{T}_{\mathsf{A}} + \mathsf{P}_{\mathsf{D}} \times \theta_{\mathsf{J}\mathsf{A}} \tag{4}$$

#### Layout

#### **Layout Guideline**

Both input capacitors and output capacitors must be placed as close to the device pins as possible, and vias between capacitors and device power pins must be avoid.

It is recommended to bypass the input pin to ground with a  $0.1~\mu F$  bypass capacitor. The loop area formed by the bypass capacitor connection, IN pin and the GND pin of the system must be as small as possible.

It is recommended to use wide trace lengths or thick copper weight to minimize I×R drop and heat dissipation.

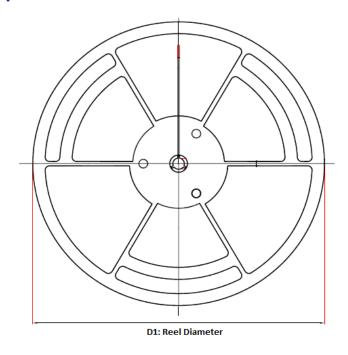

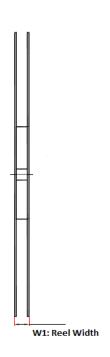

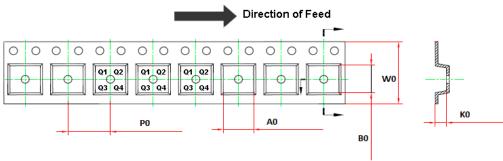

### **Tape and Reel Information**

| Order Number    | Package   | D1<br>(mm) | W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | W0<br>(mm) | Pin1<br>Quadrant |

|-----------------|-----------|------------|------------|------------|------------|------------|------------|------------|------------------|

| TPL910ADJA-DF6R | 3×3 DFN-8 | 330.0      | 17.6       | 3.4        | 3.4        | 1.1        | 8.0        | 12.0       | Q2               |

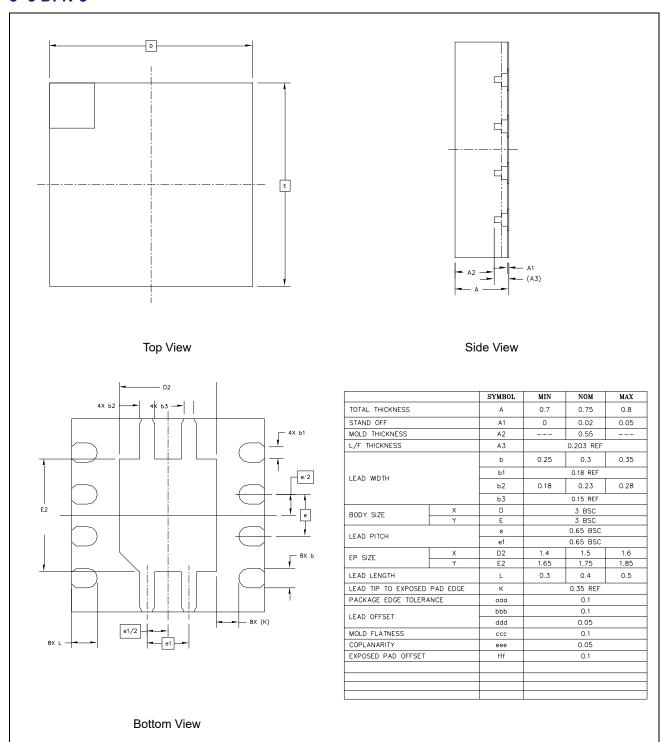

### **Package Outline Dimensions**

#### 3×3 DFN-8

#### **Order Information**

| Order Number    | Operating Temperature<br>Range | Package   | Package Marking MSL Information |      | Transport Media,<br>Quantity | Eco Plan |

|-----------------|--------------------------------|-----------|---------------------------------|------|------------------------------|----------|

| TPL910ADJA-DF6R | –40°C to +125°C                | 3×3 DFN-8 | L910A                           | MSL3 | Tape and Reel, 4,000         | Green    |

Green: 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

3PEAK and the 3PEAK logo are registered trademarks of 3PEAK INCORPORATED. All other trademarks are the property of their respective owners.

### 单击下面可查看定价,库存,交付和生命周期等信息

### >>3PEAK(思瑞浦)