## Features

- Meet the ISO 11898-2:2016 and SAE J2284-1 to SAE J2284-5 Physical Layer Standards

- Supports CAN FD and Data Rating up to 5 Mbps

- Short Propagation Delay Times and Fast Loop Times

- 5-V Power Supply, I/O Voltage Range Supports 2.8-V to 5.5-V MCU Interface

- Support Partial Networking by Means of Selective Wake Up/Wake-Up Frame with INH Output

- SPI for Device Configuration and Status Retrieving

- Ideal Passive Behavior to CAN Bus when Unpowered

- Common-Mode Input Voltage: ±30 V

- Protection Feature:

- IEC 61000-4-2 ESD Protection up to ±10 kV

- Bus Fault Protection: ±70 V

- VCC Undervoltage Protection

- TXD Dominant Time-Out Function and Bus-Dominant Time-Out Function

- Thermal Shutdown Protection

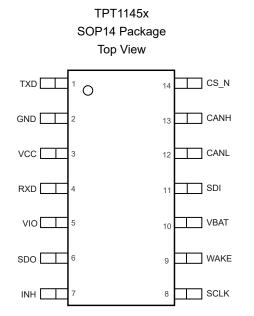

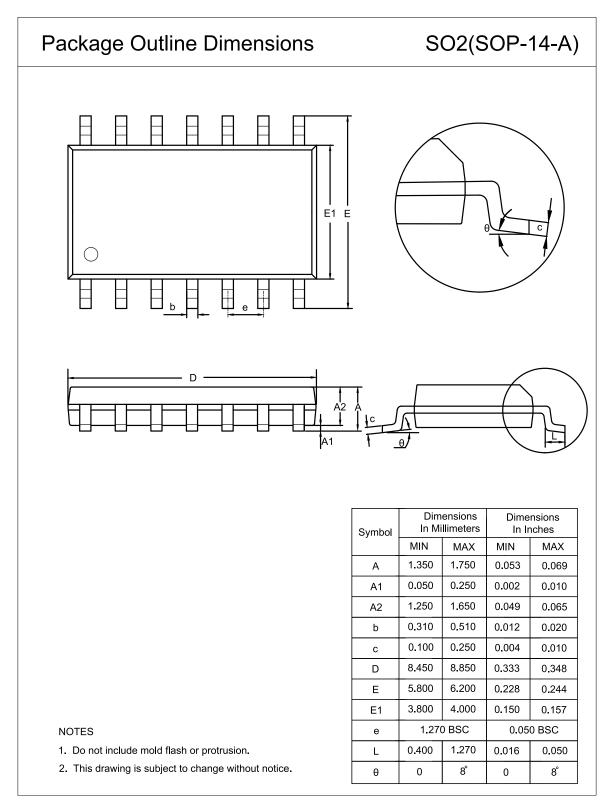

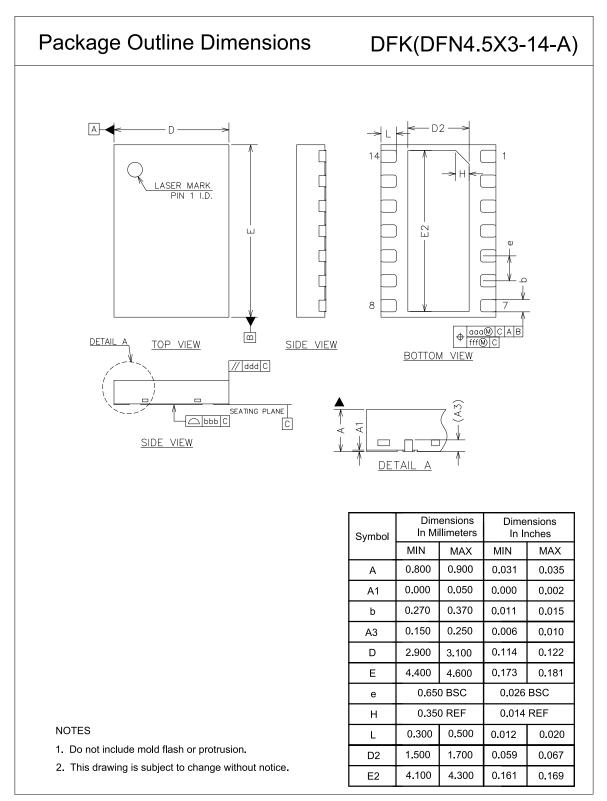

- Available in SOP14 Package and Leadless DFN4.5X3-14L Package

- AEC-Q100 Qualified for Automotive Application, Grade 1

## Applications

- All Devices Supporting Highly Loaded CAN Networks

- Automotive and Transportation

- Body Electronics / Lighting

- Power Train / Chassis

- Infotainment / Cluster

- ADAS / Safety

### Description

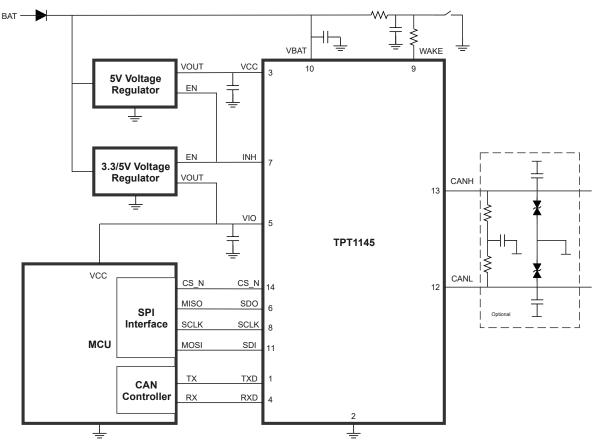

The TPT1145 is a CAN transceiver that meets the ISO11898 high-speed CAN (Controller Area Network) physical layer standard. The device is designed to be used in CAN FD networks up to 5 Mbps, with enhanced timing margin and higher data rates in long and highly loaded networks. As designed, the device features crosswire, overvoltage, and loss of ground protection from -70 V to +70 V, over-temperature shutdown, and a -30-V to +30-V common-mode input voltage range. The TPT1145 has a secondary power supply input for I/O level shifting the input pin thresholds and RXD output level. A serial peripheral interface (SPI) is provided for configuration and status retrieve. TPT1145 supports selective wake up and enables the Electronic Control Unit (ECU) to implement the partial networking function which is operating in an active state while it is in a low-power sleep mode. The device comes with the standby mode, which can be waked up from the CAN bus, and ultra-low power management controls the ECU in standby and sleep modes, then enable the power supply by inhibit output through the local or remote wake-up via wake-up pattern or wake-up frame identification. TPT1145 includes many protection features to enhance device and network robustness. There are two versions of the device, TPT1145Q and TPT1145NQ, the difference between the two versions is that the Device ID is different.

TPT1145 is available in SOP14 and DFN4.5X3.0-14L packages, and is characterized from  $-40^{\circ}$ C to  $+125^{\circ}$ C.

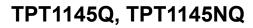

## **Typical Application Circuit**

# Automotive Fault Protected High-Speed CAN FD Transceiver for Partial Networking

## **Table of Contents**

| Features                                 | 1  |

|------------------------------------------|----|

| Applications                             | 1  |

| Description                              | 1  |

| Typical Application Circuit              | 1  |

| Product Family Table                     | 3  |

| Revision History                         | 3  |

| Pin Configuration and Functions          | 4  |

| Specifications                           | 6  |

| Absolute Maximum Ratings                 | 6  |

| ESD (Electrostatic Discharge Protection) | 7  |

| Recommended Operating Conditions         | 7  |

| Thermal Information                      | 7  |

| Electrical Characteristics               | 8  |

| AC Timing Requirements                   | 13 |

| Parameter Measurement Information        | 16 |

| Test Circuit                             | 16 |

| Parameter Diagram                        | 17 |

| Detailed Description                     |    |

| Overview                                 | 19 |

| Functional Block Diagram                 | 19 |

| Feature Description                      |    |

| System Controller Operating Modes        | 20 |

| Device Local Faults                      |    |

| Register Map                             |    |

| Application and Implementation           | 35 |

| Application Information                  |    |

| Typical Application                      | 35 |

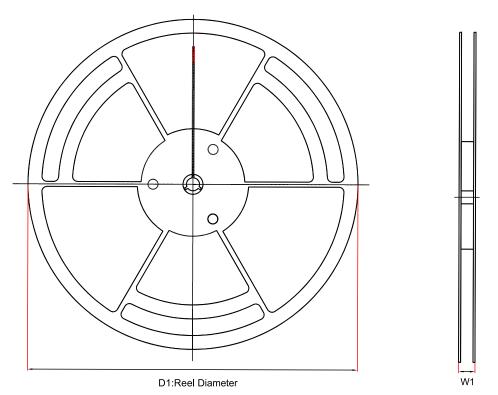

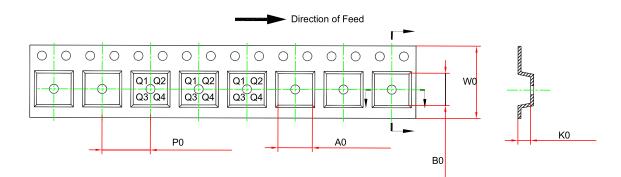

| Tape and Reel Information                |    |

| Package Outline Dimensions               | 37 |

| SOP14                                    |    |

| DFN4.5X3-14                              |    |

| Order Information                        |    |

| IMPORTANT NOTICE AND DISCLAIMER          |    |

|                                          |    |

## **Product Family Table**

| Order Number     | VCC (V)    | VIO (V)    | BUS Protection (V) | Package      |

|------------------|------------|------------|--------------------|--------------|

| TPT1145Q-SO2R-S  | 4.5 to 5.5 | 2.8 to 5.5 | ±70                | SOP14        |

| TPT1145Q-DFKR-S  | 4.5 to 5.5 | 2.8 to 5.5 | ±70                | DFN4.5X3-14L |

| TPT1145NQ-SO2R-S | 4.5 to 5.5 | 2.8 to 5.5 | ±70                | SOP14        |

| TPT1145NQ-DFKR-S | 4.5 to 5.5 | 2.8 to 5.5 | ±70                | DFN4.5X3-14L |

## **Revision History**

| Date       | Revision  | Notes             |

|------------|-----------|-------------------|

| 2021-08-12 | Rev.Pre.0 | Initial Version.  |

| 2022-12-20 | Rev.A.0   | Released Version. |

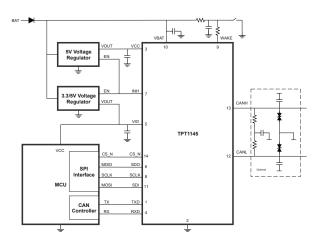

## **Pin Configuration and Functions**

#### Table 1. Pin Functions: TPT1145x

| Р   | Pin  |                           | Description                                                                                                                    |

|-----|------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| No. | Name | I/O                       | Description                                                                                                                    |

| 1   | TXD  | Digital<br>input          | CAN transmit data input (low to drive dominant state and high to drive recessive state on CAN bus).                            |

| 2   | GND  | GND                       | Ground, must be soldered to board ground.                                                                                      |

| 3   | VCC  | Power                     | 5-V CAN transceiver supply voltage.                                                                                            |

| 4   | RXD  | Digital<br>output         | CAN receive data output (low for dominant and high for recessive bus states), output voltage adapted to the VIO input voltage. |

| 5   | VIO  | Power                     | Supply voltage for Digital I/O level adaptor.                                                                                  |

| 6   | SDO  | Digital<br>output         | SPI Serial data output, tri-state when CS_N is high.                                                                           |

| 7   | INH  | High<br>voltage<br>output | Inhibit pin to control external system voltage supplies.                                                                       |

| 8   | SCLK | Digital<br>input          | SPI clock input.                                                                                                               |

| 9   | WAKE | High<br>voltage<br>input  | Local wake-up input.                                                                                                           |

| Р   | in             | 1/0                      | Description                                                                                                                      |

|-----|----------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| No. | Name           | I/O                      | Description                                                                                                                      |

| 10  | VBAT           | High<br>voltage<br>Power | High-voltage battery supply.                                                                                                     |

| 11  | SDI            | Digital<br>input         | SPI Serial data input.                                                                                                           |

| 12  | CANL           | Bus I/O                  | Low-level CAN bus line.                                                                                                          |

| 13  | CANH           | Bus I/O                  | High-level CAN bus line.                                                                                                         |

| 14  | CS_N           | Digital<br>input         | SPI Chip select input, active low.                                                                                               |

|     | Exposed<br>pad | GND                      | Thermal pad of DFN package, for enhanced thermal and electrical performance, it is required to solder the exposed pad to Ground. |

## **Specifications**

### **Absolute Maximum Ratings**

|                     | Parameter                                                                     | Min  | Мах | Unit |

|---------------------|-------------------------------------------------------------------------------|------|-----|------|

| V <sub>BAT</sub>    | Battery Supply Voltage Range                                                  | -0.3 | 60  | V    |

| Vcc                 | Power Supply Voltage Range                                                    | -0.3 | 7   | V    |

| VIO                 | I/O Level-Shifting Voltage Range                                              | -0.3 | 7   | V    |

| V <sub>BUS</sub>    | CAN Bus I/O Voltage Range (CANH, CANL)                                        | -70  | 70  | V    |

| VBUS_DIFF           | Differential Voltage of CAN Bus (CANH - CANL)                                 | -70  | 70  | V    |

| VLOGIC              | Logic Input and Output Terminal Voltage Range (TXD, RXD, SDI, SDO, SCK, CS_N) | -0.3 | 7   | V    |

| VWAKE               | WAKE Input Pin Voltage Range                                                  | -40  | 40  | V    |

| VINH                | INH Output Pin Voltage Range                                                  | -40  | 40  | V    |

|                     | RXD Output Current                                                            | -8   | 8   | mA   |

| I <sub>O_INH_</sub> | INH Output Current                                                            | -4   | 4   | mA   |

| IO_WAKE             | WAKE Output Current                                                           | -4   | 4   | mA   |

| TJ                  | Maximum Junction Temperature                                                  | -40  | 150 | °C   |

| T <sub>STG</sub>    | Storage Temperature Range                                                     | -65  | 150 | °C   |

| Тотw                | Over-Temperature Warning Junction Temperature                                 | -    | 135 | °C   |

| TOTP                | Over-Temperature Protection Junction Temperature                              | -    | 170 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

(2) This data was taken with the JEDEC low effective thermal conductivity test board.

(3) This data was taken with the JEDEC standard multilayer test boards.

### ESD (Electrostatic Discharge Protection)

|       | Parameter                          | Condition                            | Minimum Level | Unit |

|-------|------------------------------------|--------------------------------------|---------------|------|

|       | IEC Contact Discharge              | IEC-61000-4-2, Bus Pin               | ±10           | kV   |

| IEC   | IEC Air-Gap Discharge              | IEC-61000-4-2, Bus Pin               | ±15           | kV   |

| НВМ   | Human Body Model ESD               | ANSI/ESDA/JEDEC JS-001, All Pin      | ±8            | kV   |

| CDM   | Charged Device Model ESD           | ANSI/ESDA/JEDEC JS-002, All Pin      | ±1.5          | kV   |

|       |                                    | Latch up, per JESD78, All Pin, 25°C  | ±500          | mA   |

| LU    | Latch Up                           | Latch up, per JESD78, All Pin, 125°C | ±100          | mA   |

|       |                                    | Pulse 1                              | -100          | V    |

|       | ISO7637-2 transients per IEC       | Pulse 2a                             | 75            | V    |

| Vtran | 62228-3, CANH, CANL, WAKE,<br>VBAT | Pulse 3a                             | -150          | V    |

|       |                                    | Pulse 3b                             | 100           | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions**

|                     | Description                            |      |     | Unit |

|---------------------|----------------------------------------|------|-----|------|

| VBAT                | Battery Supply Voltage Range           | 4.65 | 28  | V    |

| VIO                 | Input/output voltage (TXD, RXD, SPI)   | 2.8  | 5.5 | V    |

| Vcc                 | CAN transceiver power supply           | 4.5  | 5.5 | V    |

| IOH_RXD             | RXD terminal HIGH level output current | -4   | -   | mA   |

| I <sub>OL_RXD</sub> | RXD terminal LOW level output current  | -    | 4   | mA   |

| I <sub>O_INH</sub>  | INH output current                     | -    | 1   | mA   |

| TA                  | Operating ambient temperature          | -40  | 125 | °C   |

### **Thermal Information**

| Package Type | θյΑ  | θις  | Unit |

|--------------|------|------|------|

| SOP14        | 65.2 | 34.1 | °C/W |

| DFN4.5x3-14  | 38.4 | 33.2 | °C/W |

## Automotive Fault Protected High-Speed CAN FD Transceiver for Partial Networking

### **Electrical Characteristics**

All test conditions:  $V_{CC}$  = 4.5 V to 5.5 V,  $V_{IO}$  = 2.8 V to 5.5 V,  $V_{BAT}$  = 4.5 V to 28 V,  $R_L$  = 60  $\Omega$ ,  $T_A$  = -40°C to 125°C, unless otherwise noted.

| Symbol                     | Parameter                                              | Test Conditions                                                                                                       | Min  | Тур | Max  | Unit |

|----------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| Pin VBAT                   | (Supply from battery)                                  |                                                                                                                       |      | 1   |      | I    |

| V <sub>BAT_R</sub>         | Power-on Detection on VBAT for<br>Protected Mode       | V <sub>BAT</sub> rising                                                                                               | 4.15 | -   | 4.65 | V    |

| V <sub>BAT_F</sub>         | Power-off Detection on VBAT for<br>Protected Mode      | V <sub>BAT</sub> falling                                                                                              | 2.7  | -   | 3.15 | V    |

| UV <sub>BAT_R</sub>        | Undervoltage Recovery on VBAT for<br>Protected Mode    | V <sub>BAT</sub> rising                                                                                               | 4.5  | -   | 5    | V    |

| $UV_{BAT_F}$               | Undervoltage Detection on VBAT for<br>Protected Mode   | V <sub>BAT</sub> falling                                                                                              | 4.15 | -   | 4.65 | V    |

| V <sub>HYS_UVBA</sub><br>t | Hysteresis Voltage on $U_{VBAT}$ <sup>(1)</sup>        |                                                                                                                       | -    | 350 | -    | mV   |

|                            |                                                        | Normal mode                                                                                                           | -    | 1   | 1.5  | mA   |

|                            | Battery Supply Current                                 | Sleep mode, CAN Offline<br>Mode, $4.5V \le V_{BAT} \le 28V$                                                           | -    | 45  | 70   | μA   |

|                            |                                                        | Standby mode, CAN Offline Mode, $4.5V \le V_{BAT} \le 28V$                                                            | -    | 50  | 73   | μA   |

| Іват                       |                                                        | Additional current in CAN<br>Offline Bias Mode, CAN bus<br>is connected to 2.5V                                       | -    | 40  | 70   | μΑ   |

|                            |                                                        | Additional current in CAN<br>Offline Bias Mode when<br>selective wake is enabled and<br>CAN bus active <sup>(1)</sup> | -    | 0.4 | 0.55 | mA   |

|                            |                                                        | Additional current from WAKE input                                                                                    | -    | 1   | 2    | μA   |

| Pin VCC (                  | Power Supply)                                          |                                                                                                                       |      |     |      |      |

| Vcc                        | Supply Voltage                                         |                                                                                                                       | 4.5  | -   | 5.5  | V    |

| UV <sub>VCC_R</sub>        | Undervoltage Recovery on $V_{CC}$ for Protected Mode   | Vcc Rising                                                                                                            | -    | 4.6 | 4.8  | V    |

| UV <sub>VCC_F</sub>        | Undervoltage Detection on $V_{CC}$ for Protected Mode  | V <sub>cc</sub> Falling                                                                                               | 4.25 | 4.4 | -    | V    |

| V <sub>HYS_UVVC</sub>      | Hysteresis Voltage on U <sub>VVCC</sub> <sup>(1)</sup> |                                                                                                                       | -    | 200 | -    | mV   |

| lcc                        | Supply Current                                         | Normal mode (recessive),<br>$V_{TXD} = V_{IO}, R_L = 50 \Omega, C_L =$<br>open                                        | -    | 3   | 6    | mA   |

| Symbol                     | Parameter                                                                    | Test Conditions                                                                                                                                | Min                       | Тур | Max          | Unit |

|----------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----|--------------|------|

|                            |                                                                              | Normal mode (dominant),<br>$V_{TXD} = 0 V, R_L = 50 \Omega, C_L =$<br>open                                                                     | -                         | 40  | 70           | mA   |

|                            |                                                                              | Standby/Normal mode, CAN inactive, $V_{TXD}$ = $V_{CC}$ , selective wake off, $R_L$ = 50 $\Omega$ , $C_L$ = open                               | -                         | 4   | 8.5          | μΑ   |

|                            |                                                                              | Sleep mode, CAN inactive,<br>TXD = $V_{CC}$ , $R_L$ = 50 $\Omega$ , $C_L$ =<br>open                                                            | -                         | 1.2 | 6            | μA   |

|                            |                                                                              | Dominant with bus fault, short<br>circuit on bus line, $V_{TXD} = 0$<br>V, $-3V < (V_{CANH} = V_{CANL}) <$<br>+18V, $R_L$ = Open, $C_L$ = open | -                         | 50  | 70           | mA   |

| Pin VIO (I                 | /O Supply)                                                                   |                                                                                                                                                |                           |     |              |      |

| V <sub>IO</sub>            | Supply Voltage on $V_{IO}$ Pin                                               |                                                                                                                                                | 2.8                       | -   | 5.5          | V    |

| $UV_{VIO_{R}}$             | Undervoltage Recovery on V <sub>IO</sub> for Protected Mode                  | V <sub>IO</sub> Rising                                                                                                                         | -                         | 2.8 | 2.85         | V    |

| $UV_{VIO_{F}}$             | Undervoltage Detection on V <sub>IO</sub> for Protected Mode                 | V <sub>IO</sub> Falling                                                                                                                        | 2.45                      | 2.6 | -            | V    |

| V <sub>HYS_UVVI</sub><br>0 | Hysteresis Voltage on U <sub>VVIO</sub> for<br>Protected Mode <sup>(1)</sup> |                                                                                                                                                | -                         | 200 | -            | mV   |

| l <sub>io</sub>            | Supply Current from VIO                                                      | Normal and Standby mode,<br>V <sub>TXD</sub> = V <sub>IO</sub>                                                                                 | -                         | 7   | 11           | μΑ   |

|                            |                                                                              | Sleep mode                                                                                                                                     | -                         | 3   | 8            | μA   |

| Pin SDI, S                 | SCK, CS_N (Serial Peripheral Interface                                       | Inputs)                                                                                                                                        |                           |     |              |      |

| V <sub>IH_SPI</sub>        | High-Level Input Voltage                                                     | $3 \text{ V} \leq \text{V}_{10} \leq 5.5 \text{ V}$                                                                                            | 0.7 х<br>V <sub>ю</sub>   | -   | -            | N    |

| VIL_SPI                    | Low-Level Input Voltage                                                      | $3 \text{ V} \leq \text{V}_{10} \leq 5.5 \text{ V}$                                                                                            | -                         | -   | 0.3 x<br>Vio | V    |

| V <sub>HYS_SPI</sub>       | Hysteresis Voltage on SPI Inputs <sup>(1)</sup>                              | $3 \text{ V} \leq \text{V}_{10} \leq 5.5 \text{ V}$                                                                                            | 0.05 x<br>V <sub>IO</sub> | -   | -            | V    |

| lін                        | High-Level Input Leakage Current <sup>(1)</sup>                              | $3 \text{ V} \leq \text{V}_{10} \leq 5.5 \text{ V}$                                                                                            | -1                        | -   | 1            | μA   |

| lı∟                        | Low-Level Input Leakage Current <sup>(1)</sup>                               | Input = 0 V, 3 V ≤ V <sub>IO</sub> ≤ 5.5 V                                                                                                     | -30                       | -   | -2           | μA   |

| I <sub>IL_CSN</sub>        | Low-Level Input Leakage Current for CS_N <sup>(1)</sup>                      | Input = 0 V, 3 V $\leq$ V <sub>IO</sub> $\leq$ 5.5 V                                                                                           | -50                       | -   | -2           | μA   |

| I <sub>LKG_OFF</sub>       | Unpowered Leakage Current                                                    | $V_{BAT} = V_{CC} = V_{IO} = 0 V$                                                                                                              | -1                        | -   | 1            | μA   |

| CIN                        | Input Capacitance <sup>(1)</sup>                                             | At 20MHz                                                                                                                                       | 4                         | -   | 15           | pF   |

| R <sub>PD_SCK</sub>        | SCK Pin Pull-Down Resistance                                                 |                                                                                                                                                | 40                        | 60  | 80           | kΩ   |

| R <sub>PU_CSN</sub>        | CS_N Pin Pull-Up Resistance                                                  |                                                                                                                                                | 40                        | 60  | 80           | kΩ   |

| RPD_SDI                    | SDI Pin Pull-Down Resistance                                                 |                                                                                                                                                | 40                        | 60  | 80           | kΩ   |

| Symbol                    | Parameter                                                                                                                       |                     | Test Conditions                                                                                                                        | Min                       | Тур | Max                      | Unit |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----|--------------------------|------|

| R <sub>PU_SDI</sub>       | SDI Pin Pull-Up Resistance                                                                                                      |                     |                                                                                                                                        | 40                        | 60  | 80                       | kΩ   |

| Pin SDO (                 | Serial Peripheral Interface Outp                                                                                                | outs)               | -                                                                                                                                      |                           |     |                          |      |

| Voh_spi                   | High-Level Output Voltage                                                                                                       |                     | I <sub>ОН</sub> = -4 mA                                                                                                                | V <sub>IO</sub> –<br>0.4  | -   | -                        | V    |

| V <sub>OL_SPI</sub>       | Low-Level Output Voltage                                                                                                        |                     | I <sub>OH</sub> = 4 mA                                                                                                                 | -                         | -   | 0.4                      | V    |

| I <sub>LKG_OFF</sub>      | FF Unpowered Leakage Current                                                                                                    |                     | $V_{CSN} = V_{IO}, \ 0V \le V_O \le V_{IO}$                                                                                            | -5                        | -   | 5                        | μA   |

| Pin INH (I                | nhibit high voltage output)                                                                                                     |                     |                                                                                                                                        |                           |     |                          |      |

| Vo_inh                    | High-Level Output Voltage                                                                                                       |                     | I <sub>INH</sub> = -180 μΑ                                                                                                             | V <sub>BAT</sub> –<br>0.8 | -   | VBAT                     | V    |

| R <sub>PD_INH</sub>       | INH Pin Pull-Down Resistance                                                                                                    |                     | Sleep mode                                                                                                                             | 3                         | 4   | 5                        | MΩ   |

| Pin TXD (                 | CAN transmit data input)                                                                                                        |                     |                                                                                                                                        |                           |     |                          |      |

| VIH_TXD                   | High-Level Input Voltage                                                                                                        |                     | $3 \text{ V} \leq \text{V}_{10} \leq 5.5 \text{ V}$                                                                                    | 0.7 x<br>V <sub>IO</sub>  | -   | -                        | V    |

| VIL_TXD                   | Low-Level Input Voltage                                                                                                         |                     | $3 \text{ V} \leq \text{V}_{10} \leq 5.5 \text{ V}$                                                                                    | -                         | -   | 0.3 x<br>V <sub>IO</sub> | V    |

| Vhys_txd                  | Hysteresis Voltage on TXD Inputs                                                                                                |                     | $3 \text{ V} \leq \text{V}_{10} \leq 5.5 \text{ V}$                                                                                    | 0.05 x<br>Vю              | -   | -                        | V    |

| R <sub>PU_TXD</sub>       | TXD Pin Pull-Up Resistance                                                                                                      |                     | V <sub>TXD</sub> =V <sub>IO</sub> -1.8V                                                                                                | 40                        | 60  | 80                       | kΩ   |

| Pin RXD (                 | CAN Receive Data Output)                                                                                                        |                     | _                                                                                                                                      |                           |     |                          |      |

| V <sub>OH_RXD</sub>       | High-Level Output Voltage                                                                                                       |                     | IO = -4 mA                                                                                                                             | VIO –<br>0.4              | -   | -                        | V    |

| Vol_rxd                   | Low-Level Output Voltage                                                                                                        |                     | IO = 4 mA                                                                                                                              | -                         | -   | 0.4                      | V    |

| Pin WAKE                  | E (Local wake-up pin)                                                                                                           |                     |                                                                                                                                        |                           |     |                          |      |

| VIH_WAKE                  | High-Level Input Voltage                                                                                                        |                     |                                                                                                                                        | 3                         | -   | 3.8                      | V    |

| VIL_WAKE                  | Low-Level Input Voltage                                                                                                         |                     |                                                                                                                                        | 2.5                       | -   | 3.4                      | V    |

| V <sub>HYS_WAK</sub><br>E | Hysteresis Voltage on WAKE Inp                                                                                                  | outs <sup>(1)</sup> |                                                                                                                                        | 250                       | 325 | 400                      | mV   |

| IIL                       | Low-Level Input Current                                                                                                         |                     | WAKE = 1 V                                                                                                                             | -                         | -   | 1.5                      | μA   |

| Pin CANH                  | , CANL (CAN Bus lines)                                                                                                          |                     |                                                                                                                                        |                           |     |                          |      |

|                           |                                                                                                                                 | CANH                | CAN active mode, VTXD = 0                                                                                                              | 2.75                      | 3.5 | 4.5                      | V    |

| V <sub>O(DOM)</sub>       | Dominant Bus Output Voltage                                                                                                     | CANL                | V, 50 $\Omega \le RL \le 65 \Omega$ , CL = open, t < t <sub>to(dom)TXD</sub>                                                           | 0.5                       | 1.5 | 2.25                     | V    |

| Vsym_dc                   | DC Output Symmetry (dominant or recessive)<br>(V <sub>CC</sub> – V <sub>O(CANH)</sub> – V <sub>O(CANL)</sub> )                  |                     | VCC = 5 V, RL = 60 Ω, CL =<br>open,                                                                                                    | -0.4                      | -   | 0.84                     | V    |

| V <sub>SYM</sub>          | Transient Symmetry (dominant c<br>recessive)<br>(V <sub>O(CANH)</sub> + V <sub>O(CANL)</sub> ) / V <sub>CC</sub> <sup>(1)</sup> | Dr                  | 4.75 V $\leq$ VCC $\leq$ 5.25 V, RL =<br>60 Ω, CL = open, C <sub>SPLIT</sub> = 4.7<br>nF, T <sub>XD</sub> = 250 kHz, 1 MHz, 2.5<br>MHz | 0.9                       | 1.0 | 1.1                      | V/V  |

| Symbol                 | Parameter                                                 |                                                                                                                                                                               | Test Conditions                                                                                                                                                                         | Min  | Тур          | Мах  | Unit |

|------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------|------|------|

|                        |                                                           | CAN active mode, t < $t_{t_0(dom)TXD}, 4.75 \text{ V} \le \text{V}_{CC} \le 5.25$ V, $\text{V}_{TXD}$ = 0 V, 45 $\Omega \le \text{R}_L < 50$ $\Omega$ , C <sub>L</sub> = open | 1.5                                                                                                                                                                                     | -    | 3            | V    |      |

|                        | Differential Output Valtage (dam                          | in ont)                                                                                                                                                                       | CAN active mode, t < $t_{to(dom)TXD}$ , 4.75 V ≤ V <sub>CC</sub> ≤ 5.25 V, V <sub>TXD</sub> = 0 V, 50 $\Omega$ ≤ R <sub>L</sub> < 65 $\Omega$ , C <sub>L</sub> = open                   | 1.5  | -            | 3    | V    |

| Vod_dom                | Differential Output Voltage (dom                          | mant <i>)</i>                                                                                                                                                                 | CAN active mode, t < $t_{to(dom)TXD}$ , 4.75 V $\leq$ V <sub>CC</sub> $\leq$ 5.25 V, V <sub>TXD</sub> = 0 V, 65 $\Omega \leq$ R <sub>L</sub> $\leq$ 70 $\Omega$ , C <sub>L</sub> = open | 1.5  | -            | 3.3  | V    |

|                        |                                                           |                                                                                                                                                                               | CAN active mode, t < $t_{t_0(dom)TXD}, 4.75 \text{ V} \le \text{V}_{CC} \le 5.25$ V, V <sub>TXD</sub> = 0 V, R <sub>L</sub> = 2240 $\Omega$ , C <sub>L</sub> = open                     | 1.5  | -            | 5.5  | V    |

| Vod_rec                | VoD_REC Differential Output Voltage (recessive)           |                                                                                                                                                                               | CAN active mode, $V_{TXD} = V_{IO}$ , no load                                                                                                                                           | -50  | -            | 50   | mV   |

|                        |                                                           |                                                                                                                                                                               | CAN Offline mode, no load                                                                                                                                                               | -0.2 | -            | 0.2  | V    |

|                        | Recessive Output Voltage                                  |                                                                                                                                                                               | CAN Active mode, V <sub>TXD</sub> = V <sub>IO</sub><br>= V <sub>CC</sub> , no load                                                                                                      | 2    | 0.5 x<br>VCC | 3    | V    |

| $V_{O\_REC}$           |                                                           |                                                                                                                                                                               | CAN Offline mode; no load                                                                                                                                                               | -0.1 | -            | 0.1  | V    |

|                        |                                                           |                                                                                                                                                                               | CAN Offline Bias and Silent modes; no load; $V_{CC}$ = 0 V                                                                                                                              | 2    | 2.5          | 3    | V    |

|                        | Dominant Short-Circuit Output                             | CANH                                                                                                                                                                          | CAN active mode, −15 V<br>≤V <sub>CANH</sub> ≤ 18 V, CANL = open,<br>V <sub>TXD</sub> = 0 V                                                                                             | -115 | -            | -    | mA   |

| Io_sc_dom              | Current                                                   |                                                                                                                                                                               | CAN active mode, −15 V<br>≤V <sub>CANL</sub> ≤ 18 V CANH = open,<br>V <sub>TXD</sub> = 0 V                                                                                              | -    | -            | 115  | mA   |

| IO_SC_REC              | Recessive Short-Circuit Output (                          | Current                                                                                                                                                                       | $\label{eq:Variation} \begin{array}{l} -27 \mbox{ V} \leq \!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$                                                         | -5   | -            | 5    | mA   |

| V <sub>TH_RX_DIF</sub> | <sub>RX_DIF</sub> Differential Receiver Threshold Voltage |                                                                                                                                                                               | CAN active mode or Silent mode $-12 \text{ V} \le \text{V}_{CANH} / \text{V}_{CANL} \le 12 \text{ V}$                                                                                   | 0.5  | 0.7          | 0.9  | V    |

|                        |                                                           |                                                                                                                                                                               | CAN offline mode,<br>−12 V ≤ V <sub>CANH</sub> / V <sub>CANL</sub> ≤ 12 V                                                                                                               | 0.4  | 0.7          | 1.15 | V    |

| V <sub>REC_RX</sub>    | Receiver Recessive Voltage                                |                                                                                                                                                                               | CAN active mode or Silent<br>mode, Bus bias active<br>−12 V ≤V <sub>CANH</sub> / V <sub>CANL</sub> ≤ 12 V                                                                               | -3   | -            | 0.5  | V    |

|                        |                                                           |                                                                                                                                                                               | CAN offline mode, Bus bias inactive                                                                                                                                                     | -3   | -            | 0.4  | V    |

# Automotive Fault Protected High-Speed CAN FD Transceiver for

### **Partial Networking**

| Symbol            | Parameter                                                                                 | Test Conditions                                                                                                                       | Min  | Тур | Max | Unit |

|-------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

|                   |                                                                                           | $-12 \text{ V} \leq V_{\text{CANH}} / V_{\text{CANL}} \leq 12 \text{ V}$                                                              |      |     |     |      |

| V                 |                                                                                           | CAN active mode or Silent<br>mode, Bus bias active<br>$-12 V \le V_{CANH} / V_{CANL} \le 12 V$                                        | 0.9  | -   | 8   | V    |

| Vdom_rx           | Receiver Dominant Voltage                                                                 | CAN offline mode, Bus bias<br>inactive<br>−12 V ≤V <sub>CANH</sub> / V <sub>CANL</sub> ≤ 12 V                                         | 1.15 | -   | 8   | V    |

| Vhys_rx_d<br>if   | Differential Receiver Hysteresis<br>Voltage <sup>(1)</sup>                                | CAN active mode or Silent<br>mode,<br>−12 V ≤V <sub>CANH</sub> / V <sub>CANL</sub> ≤ 12 V                                             | 1    | 30  | 100 | mV   |

| R <sub>IN</sub>   | Input Resistance (CANH or CANL)                                                           | $V_{TXD} = V_{CC} = V_{IO} = 5 \text{ V}, -2 \text{ V}$ $\leq V_{CANH} / V_{CANL} \leq 7 \text{ V}$                                   | 10   | 23  | 35  | kΩ   |

| R <sub>IN_M</sub> | Input Resistance Matching: [1 –<br>R <sub>IN(CANH)</sub> / R <sub>IN(CANL)</sub> ] × 100% | $V_{TXD} = V_{CC} = V_{IO} = 5 V$                                                                                                     | -2   | -   | +2  | %    |

| RID               | Differential Input Resistance                                                             | $V_{TXD} = V_{CC} = V_{IO} = 5 \text{ V}, -2 \text{ V}$ $\leq V_{CANH} / V_{CANL} \leq 7 \text{ V}$                                   | 30   | 47  | 60  | kΩ   |

| Cı                | Input Capacitance to Ground (CANH or CANL) $^{(1)}$                                       |                                                                                                                                       | -    | -   | 20  | pF   |

| CID               | Differential Input Capacitance <sup>(1)</sup>                                             |                                                                                                                                       | -    | -   | 10  | pF   |

| ۱L                | Leakage Current                                                                           | $V_{BAT} = V_{CC} = 0 V \text{ or } V_{BAT} = V_{CC}$<br>shorted to ground via 47 k $\Omega$ ;<br>$V_{CANH} = 5 V$ , $V_{CANL} = 5 V$ | -5   | -   | 5   | μA   |

(1) The typical data is based on bench test and design simulation. V<sub>sym</sub> =  $0.9 \sim 1.1$  V/V at 250 kbps.

### **AC Timing Requirements**

All test conditions:  $V_{CC}$  = 4.5 V to 5.5 V,  $V_{IO}$  = 2.8 V to 5.5 V,  $V_{BAT}$  = 4.5 V to 28 V,  $R_L$  = 60  $\Omega$ ,  $T_A$  = -40°C to 125°C, unless otherwise noted.

| Symbol                   | Parameter                                                         | Test Conditions                                                                                         | Min | Тур | Мах | Unit |

|--------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Pin BAT, V               | CC, VIO (Power supply)                                            |                                                                                                         |     |     |     |      |

| tpwrup                   | Power-up Time                                                     | Time from $V_{BAT}$ exceeding<br>the power-on detection<br>threshold( $V_{BAT_R}$ ) until INH<br>active | -   | 2.8 | 4.7 | ms   |

| $t_{d\_UV}$              | Under Voltage Detection Delay<br>Time                             |                                                                                                         | 20  | -   | 60  | μs   |

| t <sub>d_UVSLP</sub>     | Delay from Undervoltage<br>Detection to Sleep Mode <sup>(1)</sup> | Time from $U_{VCC}$ and/or $U_{VIO}$ event until transition to Sleep mode                               | 200 | -   | 400 | ms   |

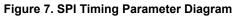

| Pin CS_N,                | SCLK, SDI, SDO (SPI timing)                                       |                                                                                                         |     |     |     |      |

| f <sub>SCLK</sub>        | SPI Clock Frequency <sup>(1)</sup>                                | Normal, Standby mode, Sleep mode                                                                        | -   | -   | 4   | MHz  |

| t <sub>SCLK</sub>        | SPI Clock Period <sup>(1)</sup>                                   | Normal, Standby mode, Sleep mode                                                                        | 250 | -   | -   | ns   |

|                          | CDI Chin Colort Coture Time (1)                                   | Normal and Standby mode                                                                                 | 100 | -   | -   | ns   |

| tcss                     | SPI Chip Select Setup Time <sup>(1)</sup>                         | Sleep mode                                                                                              | 500 | -   | -   | ns   |

| t <sub>CSH</sub> SPI     | SPI Chip Select Hold Time <sup>(1)</sup>                          | Normal and Standby mode                                                                                 | 100 | -   | -   | ns   |

|                          |                                                                   | Sleep mode                                                                                              | 500 | -   | -   | ns   |

| t <sub>clк_н</sub>       | SPI Clock High Time <sup>(1)</sup>                                | Normal and Standby mode                                                                                 | 100 | -   | -   | ns   |

|                          |                                                                   | Sleep mode                                                                                              | 500 | -   | -   | ns   |

| t <sub>CLK L</sub>       | SPI Clock Low Time <sup>(1)</sup>                                 | Normal and Standby mode                                                                                 | 100 | -   | -   | ns   |

|                          |                                                                   | Sleep mode                                                                                              | 500 | -   | -   | ns   |

| t <sub>DI_SU</sub>       | SPI Data Input Setup Time <sup>(1)</sup>                          | Normal and Standby mode                                                                                 | 50  | -   | -   | ns   |

|                          |                                                                   | Sleep mode                                                                                              | 200 | -   | -   | ns   |

| t <sub>DI_H</sub>        | SPI Data Input Hold Time <sup>(1)</sup>                           | Normal and Standby mode                                                                                 | 50  | -   | -   | ns   |

| -51_11                   |                                                                   | Sleep mode                                                                                              | 200 | -   | -   | ns   |

| <b>+</b>                 | SPI Data Output Valid Time                                        | pin SDO; C <sub>L</sub> = 20 pF; Normal and Standby modes                                               | -   | -   | 100 | ns   |

| t <sub>DO_V</sub> SPI Da | SPI Data Output Valid Time                                        | pin SDO; C <sub>L</sub> = 20 pF; Sleep<br>modes                                                         | -   | -   | 100 | ns   |

| t <sub>d_SDI-SDO</sub>   | SDI to SDO Delay Time                                             | SPI address bits and read-only bit; $C_L = 20 \text{ pF}^{(1)}$                                         | -   | -   | 50  | ns   |

| t <sub>cs_wн</sub>       | SPI Chip Select Pulse Width                                       | pin SDO; Normal and Standby modes                                                                       | 250 | -   |     | ns   |

|                          | High <sup>(1)</sup>                                               | pin SDO; Sleep mode                                                                                     | 1   | -   |     | μs   |

| Symbol                           | Parameter                                                                                                              | Test Conditions                                                                                                                                    | Min | Тур | Max | Unit |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>d_SCLKL-CSL</sub>         | Delay Time from SCLK Low to CS_N Low <sup>(1)</sup>                                                                    |                                                                                                                                                    | 50  | -   | -   | ns   |

| Transceive                       | er Switching Characteristics                                                                                           |                                                                                                                                                    |     |     |     | 1    |

| t <sub>pLD</sub>                 | Propagation Delay Time, Low<br>TXD to Driver Dominant<br>(recessive to dominant) <sup>(1)</sup>                        |                                                                                                                                                    | -   | 60  | 100 | ns   |

| t <sub>pHR</sub>                 | Propagation Delay Time, High<br>TXD to Driver Recessive<br>(dominant to recessive) <sup>(1)</sup>                      | Normal mode, $R_L$ = 60 $\Omega$ , $C_L$ =                                                                                                         | -   | 60  | 100 | ns   |

| t <sub>sk_P</sub>                | Pulse Skew ( t <sub>pHR</sub> - t <sub>pLD</sub>  ) <sup>(1)</sup>                                                     | 100 pF                                                                                                                                             | -   | 10  | 35  | ns   |

| t <sub>R</sub>                   | Differential Output Signal Rise<br>Time <sup>(1)</sup>                                                                 |                                                                                                                                                    | -   | 45  | -   | ns   |

| t <sub>F</sub>                   | Differential Output Signal Fall<br>Time <sup>(1)</sup>                                                                 |                                                                                                                                                    | -   | 45  | -   | ns   |

| t <sub>pRH</sub>                 | Propagation Delay Time, Bus<br>Recessive Input to RXD High<br>Output (Dominant to Recessive) <sup>(1)</sup>            |                                                                                                                                                    | -   | 90  | 120 | ns   |

| t <sub>pDL</sub>                 | Propagation Delay Time, Bus<br>Dominant Input to RXD Low<br>Output (Recessive to Dominant) <sup>(1)</sup>              | $V_{STB}$ = 0 V, $C_{L(RXD)}$ = 15 pF                                                                                                              | -   | 90  | 120 | ns   |

| t <sub>R_R</sub>                 | RXD Output Signal Rise Time <sup>(1)</sup>                                                                             |                                                                                                                                                    | -   | 20  | -   | ns   |

| t <sub>R_F</sub>                 | RXD Output Signal Fall Time <sup>(1)</sup>                                                                             |                                                                                                                                                    | -   | 20  | -   | ns   |

| t <sub>PROP_TXDL</sub> -<br>RXDL | Total loop delay, driver input<br>(TXD) low to receiver output<br>(RXD) low, recessive to<br>dominant <sup>(1)</sup>   | Normal mode, $R_L$ = 60 $\Omega$ , $C_L$ =                                                                                                         | -   | 110 | 220 | ns   |

| tprop_txdh-<br>rxdh)             | Total loop delay, driver input<br>(TXD) high to receiver output<br>(RXD) high, dominant to<br>recessive <sup>(1)</sup> | 100 pF, C <sub>L(RXD)</sub> = 15 pF,                                                                                                               | -   | 140 | 220 | ns   |

| FD Timing                        | Parameters                                                                                                             |                                                                                                                                                    |     |     |     | 1    |

| tour ours                        | Bit time on CAN bus output pins with $t_{BIT_TXD}$ = 500 ns <sup>(1)</sup>                                             |                                                                                                                                                    | 435 | -   | 530 | ns   |

| t <sub>BIT_BUS</sub>             | Bit time on CAN bus output pins with $t_{BIT_TXD}$ = 200 ns <sup>(1)</sup>                                             |                                                                                                                                                    | 155 | -   | 210 | ns   |

|                                  | Bit time on RXD output pins with $t_{B T_TXD} = 500 \text{ ns}$                                                        | R <sub>L</sub> = 60 Ω, C <sub>L</sub> = 100 pF,<br>C <sub>L(RXD)</sub> = 15 pF,<br>Δt <sub>REC</sub> = t <sub>BIT_RXD</sub> - t <sub>BIT_BUS</sub> | 400 | -   | 550 | ns   |

| t <sub>BIT_RXD</sub>             | Bit time on RXD output pins with $t_{BIT_TXD}$ = 200 ns                                                                | LAIKEC- USII_KXD- USII_BUS                                                                                                                         | 120 | -   | 220 | ns   |

| $\Delta t_{\text{REC}}$          | Receiver timing symmetry with $t_{BIT_TXD} = 500 \text{ ns}^{(1)}$                                                     |                                                                                                                                                    | -65 | -   | 40  | ns   |

| Symbol                  | Parameter                                                            | Test Conditions                                                                                                              | Min  | Тур | Max  | Unit |

|-------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

|                         | Receiver timing symmetry with $t_{BIT(TXD)}$ = 200 ns <sup>(1)</sup> |                                                                                                                              | -45  | -   | 15   | ns   |

| Device Tin              | ning Parameters                                                      |                                                                                                                              |      |     |      |      |

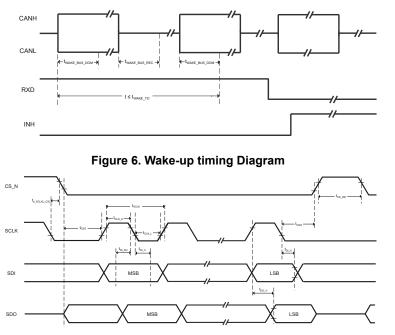

| twake_filt              | Bus time to meet filtered bus requirement for wake-up request        | Pulse for wake-up on pins<br>CANH and CANL                                                                                   | 0.5  | -   | 1.8  | μs   |

| twake_to                | Bus wake-up time out-time                                            | Between first and second<br>dominant pulses; CAN Offline<br>mode                                                             | 0.8  | -   | 10   | ms   |

| t <sub>TXD_DTO</sub>    | TXD dominant time-out time                                           | normal mode, R <sub>L</sub> = 60 Ω, C <sub>L</sub> = open, V <sub>TXD</sub> = 0V                                             | 2.7  | -   | 3.3  | ms   |

| tsilence                | Bus Silence time-out time <sup>(1)</sup>                             | Timeout for bus inactivity. Timer<br>is reset and restarted when<br>bus changes from dominant to<br>recessive or vice versa. | 0.95 | -   | 1.2  | S    |

| t <sub>d_ACT-BIAS</sub> | Delay time form bus active to bias                                   |                                                                                                                              | -    | -   | 200  | μs   |

| t <sub>SU_CAN</sub>     | CAN start-up time                                                    | When switching to Active mode                                                                                                | -    | -   | 220  | μs   |

| CAN Parti               | al Networking                                                        |                                                                                                                              |      |     |      |      |

| N <sub>idle_bits</sub>  | Number of idle bits <sup>(1)</sup>                                   | Before a new SOF is accepted                                                                                                 | 6    | -   | 10   |      |

| t <sub>fltr_dom</sub>   | Dominant bit filter time <sup>(1)</sup>                              | arbitration data rate ≤ 500 kbps                                                                                             | 5    | -   | 8.75 | %    |

| Pin RXD Ir              | nterrupt/wake-up Timing                                              |                                                                                                                              |      |     |      |      |

| t <sub>d_event</sub>    | Event capture delay time                                             | CAN offline mode                                                                                                             | 0.9  | -   | 1.1  | ms   |

| t <sub>blank</sub>      | Blanking time                                                        | Switching from Offline mode to Active or Silent mode                                                                         | -    | -   | 30   | μs   |

| Pin WAKE                | ·                                                                    |                                                                                                                              |      |     |      |      |

| t <sub>WAKE</sub>       | Wake up time                                                         |                                                                                                                              | 50   | -   | -    | μs   |

| Pin INH                 |                                                                      |                                                                                                                              |      |     |      |      |

| t <sub>d_BW-INH</sub>   | Delay time from bus wake-up to INH high                              |                                                                                                                              | -    | -   | 100  | μs   |

(1) The test data is based on bench test and design simulation.

Automotive Fault Protected High-Speed CAN FD Transceiver for Partial Networking

### **Parameter Measurement Information**

**Test Circuit**

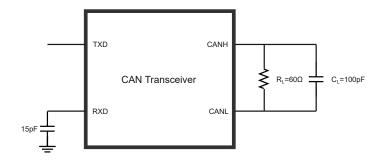

Figure 1. CAN Transceiver Timing Parameter Test Circuit

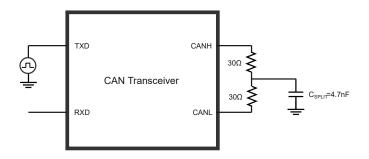

Figure 2. CAN Transceiver Driver Symmetry Test Circuit

### **Parameter Diagram**

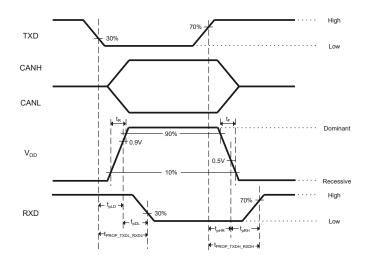

Figure 3. CAN Transceiver Timing Diagram

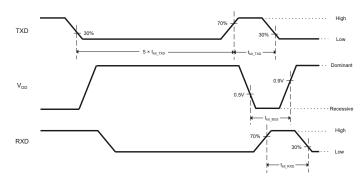

Figure 4. CAN FD Timing Parameter Diagram

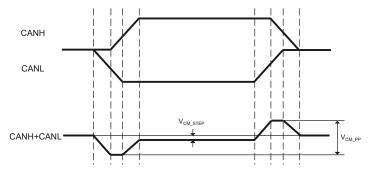

Figure 5. CAN Bus Common-Mode Voltage

## **Detailed Description**

### Overview

The TPT1145 is a CAN transceiver which meets the ISO11898 High Speed CAN (Controller Area Network) physical layer standard. The device is designed to be used in CAN FD networks up to 5 Mbps, with enhanced timing margin and higher data rates in long and highly loaded networks. As designed, the device features crosswire, overvoltage and loss of ground protection from -70 V to +70 V, overtemperature shutdown, and a -30 V to +30 V common-mode input voltage range. The TPT1145 has a secondary power supply input for I/O level shifting the input pin thresholds and the RXD output level. A serial peripheral interface (SPI) is provided for configuration and status retrieve. TPT1145 supports selective wake up and enables the Electronic Control Unit (ECU) to implement the Partial Networking function which is operating in an active state while it is in a low-power sleep mode. The device comes with the standby mode, which can be waked up from CAN BUS, and ultra-low power management controls the ECU in standby and sleep modes, then enables the power supply by inhibit output through the local or remote wake-up via wake-up pattern or wake-up frame identification. TPT1145 includes many protection features to enhance device and network robustness. There are two versions of the device, TPT1145Q and TPT1145NQ, the difference between the two versions is that the Device ID is different.

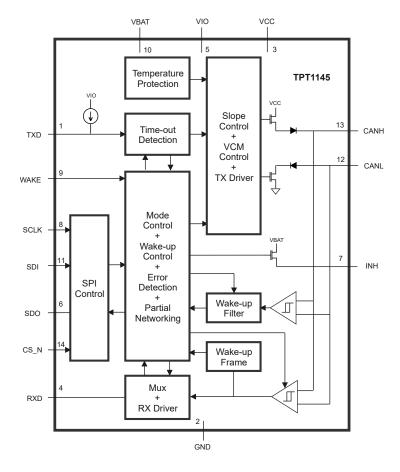

### Functional Block Diagram

Figure 8. Functional Block Diagram

# Automotive Fault Protected High-Speed CAN FD Transceiver for Partial Networking

### **Feature Description**

#### Table 2. Driver Function Table

| Device Made | Inputs    | Out  | Driver DUC State |                  |  |

|-------------|-----------|------|------------------|------------------|--|

| Device Mode | TXD       | CANH | CANL             | Driven BUS State |  |

| Normal      | L         | Н    | L                | Dominant         |  |

| Normal      | H or Open | Z    | Z                | Biased Recessive |  |

| Standby     | X         | Z    | Z                | Biased to GND    |  |

| Silent      | Х         | Z    | Z                | Biased to 2.5V   |  |

| Sleep       | Х         | Z    | Z                | Biased to GND    |  |

#### Table 3. Receiver Function Table

| Device Mode         | CAN Differential Inputs<br>VID = VCANH – VCANL | BUS State     | RXD Terminal  |

|---------------------|------------------------------------------------|---------------|---------------|

|                     | $V_{\text{ID}} \ge V_{\text{IT+(MAX)}}$        | Dominant      | L             |

| Normal or Standby   | $V_{IT - (MIN)} \le V_{ID} \le V_{IT + (MAX)}$ | Indeterminate | Indeterminate |

| Normal or Standby - | $V_{ID} \leq V_{IT - (MIN)}$                   | Recessive     | Н             |

|                     | Open (V <sub>ID</sub> ≈ 0 V)                   | Open          | Н             |

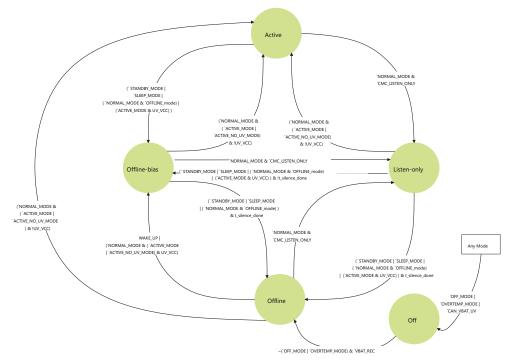

### System Controller Operating Modes

The device system controller has 5 operating modes: normal mode, standby mode, sleep mode, off mode, and over-temperature mode.

Figure 9. Mode Transition State Diagram

#### Normal Mode

This is the normal operating mode of the device. In the normal mode, the device is fully operational, and all block is available.

#### Standby Mode

This is the first level of the low-power mode. In the standby mode, the driver and receiver of the CAN transceiver are disabled, and the device is unable to transmit or receive data. The low-power receiver is monitoring bus activity for valid wake-up requirements. The CAN bus pin is biased to the ground. The INH pin is active to enable the voltage regulator controlled by the INH pin. The pins RXD will reflect active wake-up requests as that  $V_{IO}$  and  $V_{BAT}$  are powered.

#### Sleep Mode

This is the second level of low-power mode as well as the lowest power mode. In the sleep mode, the driver and receiver of the CAN transceiver are disabled, and the device is unable to transmit or receive data, the low-power receiver is monitoring bus activity for valid wake-up requirements. The CAN bus pin is biased to the ground. The INH pin is floating to disable the voltage regulator controlled by the INH pin for additional system-level power saving.

#### Off Mode

This is the default mode when  $V_{BAT}$  is first powered, and the device will switch to the off mode if  $V_{BAT}$  drops below the power off threshold  $V_{BAT_F}$ . The CAN bus pins and INH pin are in High-Z state in off mode. When  $V_{BAT}$  rises above the power on the threshold  $V_{BAT_R}$ , the device will re-boot and will switch to standby mode after  $t_{SU_CAN}$ .

#### **Over-Temperature Mode**

Over-temperature mode will prevent the device from over-heated induced damage. The device will switch to over-temperature mode as soon as the junction temperature rises above the over-temperature warning threshold  $T_{OTW}$ . The CAN driver and receiver are disabled, and CAN bus pins are High-Z state in over-temperature mode.

#### High-Speed CAN Transceiver Operating Mode

The high-speed CAN transceiver has 4 operating modes: active mode, silent mode, offline mode, and Offline bias mode. Operating mode selection is made via register setting of bits CMC.The CAN transceiver operating mode can be selected

among the offline mode, active mode, and silent mode via register setting in the normal mode. The CAN transceiver is forced to go into the offline mode or offline bias mode when the device is in the standby mode or sleep mode.

#### Active Mode

In the active mode, the CAN driver and receiver block are fully operational, the transceiver will transmit and receive data via the bus lines CANH and CANL. The driver translates the digital input data on the TXD pin to differential analog output on the CAN bus. The receiver translates the differential analog data on the CAN bus to digital data output to the RXD pin. The slopes of the CAN bus output signals are controlled by the internal circuit that optimized the Electro Magnetic Emission (EME) performance.

#### Silent Mode

This is the listen-only mode and receive-only mode of the device. In the silent mode, the driver is disabled, releasing the bus pins to a recessive state. All other blocks, including the receiver, continue to operate in the normal mode. The silent mode can be used to prevent a faulty CAN controller from disrupting CAN bus network communications.

#### Offline Mode and Offline Bias Mode

The transceiver monitors the CAN bus for wake-up event in the offline mode if the CAN wake-up detection function is enabled. The CAN bus are biased to ground. The transceiver monitors the CAN bus for wake-up event in the offline mode if the CAN wake-up detection function is enabled. The CAN bus are biased to 2.5 V. The offline bias mode is activated automatically when the activity is detected on the CAN bus while the transceiver in the CAN offline mode. The transceiver will return to the offline mode if there is no edges on the CAN bus for longer than  $t_{SILENCE}$ .

### **Device Local Faults**

#### TXD Dominant Time-out

The device is featured with the TXD dominant time-out detection function. This function prevents a permanent low on the TXD pin, resulting in the CAN bus being driven into permanent dominant, which will cause the CAN bus network communication blocked. If the TXD remains low for longer than  $t_{TXD_DTO}$ , the transmitter will be disabled until the fault flag has been cleared.

#### TXD Shorted to RXD Detection

The device is featured with the function of a short circuit between TXD and RXD detection. This function prevents the CAN bus from being locked in permanent dominance, which will result in the CAN bus network communication blocked. The transmitter will be disabled until the fault flag has been cleared.

#### Under-Voltage Lockout (UVLO)

The device integrates an under-voltage detect and lockout circuit of the supply terminal to keep the device in the protected mode if the supply voltage drops below the threshold until the supply voltage is higher than the UVLO threshold. This protects the device and system during under-voltage events on supply terminals.

#### **Over-Temperature Protection (OTP)**

The device integrates over-temperature protection circuit to prevent the device from over-heated induced damage. When the junction temperature is higher than the over-temperature protection threshold  $T_{OTP}$ , the device will shut down until the junction temperature  $T_J$  drops below  $T_{OTW}$ .

#### **CAN Partial Networking Configuration Registers**

Dedicated registers are provided for configuring CAN partial networking.

#### Table 4. Data rate register (address 26h)

| Bit | Symbol   | Access | Value | Description                                                      |

|-----|----------|--------|-------|------------------------------------------------------------------|

| 7:3 | reserved | R      | -     |                                                                  |

|     |          |        |       | CAN data rate selection:                                         |