# Ultra Low Noise, 3.5MHz, RRIO Zero-Drift Op-amps Description

#### **Features**

Low Offset Voltage: 5 µV (Max)

Zero Drift: 0.05 µV/°C (Max)

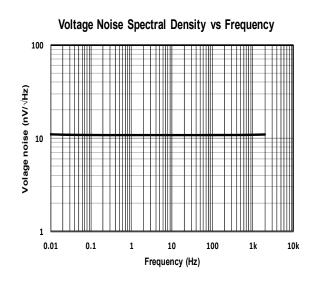

1/f Noise Corner Down to 0.1Hz:

15 nV/√Hz Input Noise Voltage @1kHz

- 350 nV<sub>P-P</sub> Noise Voltage @0.1Hz to 10Hz

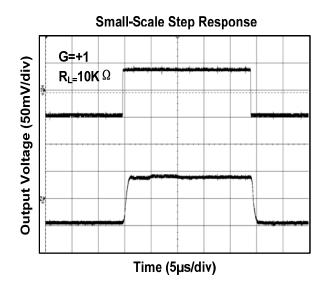

■ Slew Rate: 2.5 V/µs ■ Bandwidth: 3.5 MHz

Low Supply Current: 500 µA per Amplifier

Low Input Bias Current: 50 pA Typical

Rail-to-Rail Output Voltage Range

High Gain, CMRR, PSRR: 130 dB

■ 7 kV HBM ESD Rating

■ -40°C to 125°C Operation Range

### **Applications**

- Medical Instrumentation

- Temperature Measurements

- Precision Current Sensing

- ADC Drivers

- Process Control Systems

- Precision Voltage Reference Buffers

The TP555x op-amps are single/dual/quad chopper stabilized zero-drift operational amplifier optimized for single or dual supply operation from 1.8V to 5.5V and  $\pm 0.9$ V to  $\pm 2.75$ V. The TP555x features very low input offset voltage and low noise with 1/f noise corner down to 0.1Hz. The TP555x is designed to have ultra low offset voltage and offset temperature drift, wide gain bandwidth and rail-to-rail input/output swing while minimizing power consumption.

The TP555x family can provide very low offset voltage  $(5\mu V \text{ Max.})$  and near-zero drift over time and temperature with excellent CMRR and PSRR.

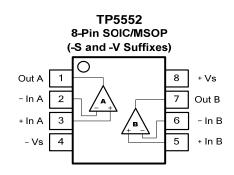

The TP5551 (single version) is available in SOT23, SC70 and SO-8 packages. The TP5552 (dual version) is offered in MSOP-8 and SO-8 packages. The TP5554 (quad version) is available in TSSOP-14 and SO-14 packages. All versions are specified for operation from -40°C to 125°C.

4 3PEAK and the 3PEAK logo are registered trademarks of 3PEAK INCORPORATED. All other trademarks are the property of their respective owners.

#### Related Zero-Drift RRO Op-amps

| Vos (Max.)              | 10 μV     | 5 μV      | 5 μV      |

|-------------------------|-----------|-----------|-----------|

| GBWP                    | 350 kHz   | 1.5 MHz   | 3.5 MHz   |

| Supply Current          | 34 μΑ     | 220 μΑ    | 500 μΑ    |

| e <sub>N</sub> at 1 kHz | 55 nV/√Hz | 25 nV/√Hz | 15 nV/√Hz |

| Single                  | TP5531    | TP5541    | TP5551    |

| Dual                    | TP5532    | TP5542    | TP5552    |

| Quad                    | TP5534    | TP5544    | TP5554    |

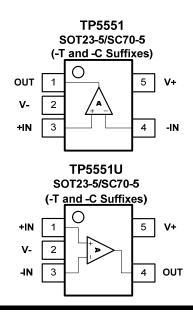

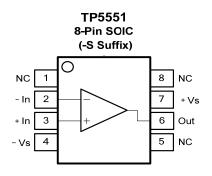

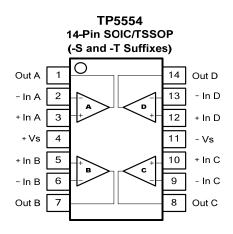

### **Pin Configuration (Top View)**

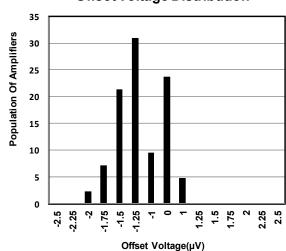

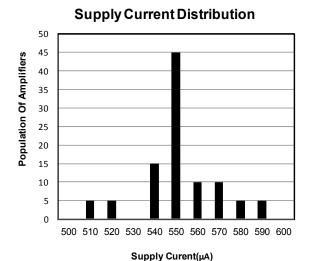

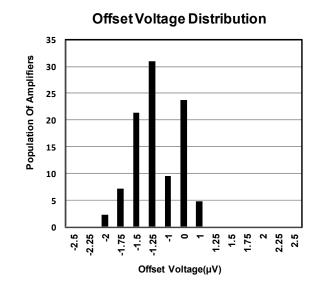

#### Offset Voltage Distribution

#### **Pin Configuration (Top View)**

#### **Order Information**

| Model Name | Order Number | Package  | Transport Media, Quantity | Marking<br>Information |

|------------|--------------|----------|---------------------------|------------------------|

|            | TP5551-TR    | SOT23-5  | Tape and Reel, 3000       | E51T                   |

| TP5551     | TP5551-CR    | SC70-5   | Tape and Reel, 3000       | E51C                   |

|            | TP5551-SR    | SO-8     | Tape and Reel, 4000       | E51S                   |

| TP5551U    | TP5551U-TR   | SOT23-5  | Tape and Reel, 3000       | E51U                   |

|            | TP5551U-CR   | SC70-5   | Tape and Reel, 3000       | E51V                   |

| TP5552     | TP5552-SR    | SO-8     | Tape and Reel, 4000       | E52S                   |

| 173332     | TP5552-VR    | MSOP-8   | Tape and Reel, 3000       | E52V                   |

| TP5554     | TP5554-SR    | SO-14    | Tape and Reel, 2500       | E54S                   |

|            | TP5552-TR    | TSSOP-14 | Tape and Reel, 3000       | E54T                   |

#### **Absolute Maximum Ratings Note 1**

| Supply Voltage:                      | 7V                             |

|--------------------------------------|--------------------------------|

| Input Voltage:V                      | $^{-}$ - 0.3 to V $^{+}$ + 0.3 |

| Input Current: +IN, -IN Note 2       | ±20mA                          |

| Output Current: OUT                  | ±60mA                          |

| Output Short-Circuit Duration Note 3 | Indefinite                     |

| Current at Supply Pins ±             | 50mA  |

|--------------------------------------|-------|

| Operating Temperature Range40°C to   | 125°C |

| Maximum Junction Temperature         | 150°C |

| Storage Temperature Range65°C to     | 150°C |

| Lead Temperature (Soldering, 10 sec) | 260°C |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

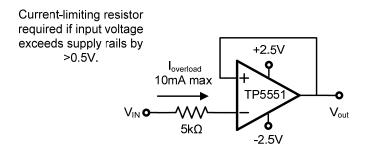

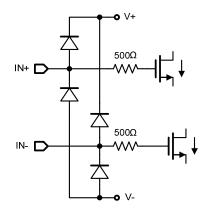

**Note 2:** The inputs are protected by ESD protection diodes to each power supply. If the input extends more than 500mV beyond the power supply, the input current should be limited to less than 10mA.

**Note 3**: A heat sink may be required to keep the junction temperature below the absolute maximum. This depends on the power supply voltage and how many amplifiers are shorted. Thermal resistance varies with the amount of PC board metal connected to the package. The specified values are for short traces connected to the leads.

## **ESD, Electrostatic Discharge Protection**

| Symbol | Parameter                | Condition                  | Minimum Level | Unit |

|--------|--------------------------|----------------------------|---------------|------|

| HBM    | Human Body Model ESD     | MIL-STD-883H Method 3015.8 | 7             | kV   |

| CDM    | Charged Device Model ESD | JEDEC-EIA/JESD22-C101E     | 2             | kV   |

#### **Electrical Characteristics**

The denotes the specifications which apply over the full operating temperature range,  $T_A$  = -40°C to +125°C . At  $T_A$  = 27°C,  $V_{DD}$ =5V,  $R_L$ =10K,  $V_{CM}$ = $V_{DD}$ /2, unless otherwise noted.

| VDD=5V,<br>SYMBOL    | PARAMETER                                         | CONDITIONS                                           | MIN      | ТҮР               | MAX                | UNITS            |

|----------------------|---------------------------------------------------|------------------------------------------------------|----------|-------------------|--------------------|------------------|

| $V_{DD}$             | Supply Voltage Range                              |                                                      | 1.8      | •                 | 5.5                | V                |

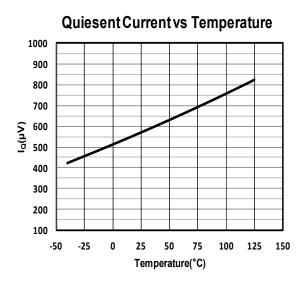

| IQ                   | Quiescent current per amplifier  Over temperature | I <sub>O</sub> = 0                                   |          | 500               | 590<br><b>820</b>  | μА               |

| $V_{OS}$             | Input Offset Voltage                              | Input grounded, unity gain.                          |          | ±1                | ±5                 | μV               |

| dV <sub>OS</sub> /dT | vs. Temperature                                   |                                                      |          | 0.008             | 0.05               | μV/°C            |

| PSRR                 | vs. Power Supply                                  | $V_S = +1.8V \text{ to } +5.5V$                      |          | 0.5               |                    | μV/V             |

| $V_{N(P-P)}$         | Input Voltage Noise                               | f = 0.01Hz to 1Hz<br>f = 0.1Hz to 10Hz               |          | 0.1<br>0.35       |                    | μV <sub>PP</sub> |

| V <sub>N</sub>       | Input Voltage Noise Density                       | f = 1kHz                                             |          | 15                |                    | nV/√Hz           |

| C <sub>IN</sub>      | Input Capacitor                                   | Differential<br>Common-Mode                          |          | 3<br>2            |                    | pF               |

| I <sub>B</sub>       | Input Current Over temperature                    |                                                      |          | ±50               | ±200<br><b>800</b> | рА               |

| los                  | Input Offset Current                              |                                                      |          | ±100              | ±400               | pА               |

| V <sub>CM</sub>      | Common-mode Voltage Range                         |                                                      | (V-)-0.1 |                   | (V+)+0.1           | V                |

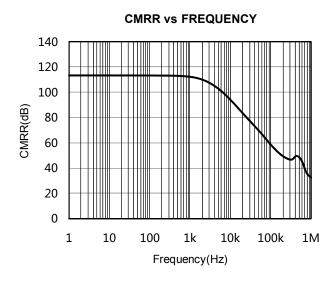

| CMRR                 | Common-mode Rejection Ratio                       |                                                      | 110      | 130               |                    | dB               |

| $V_{O}$              | Output Voltage Swing from Rail  Over temperature  | $R_L = 10k\Omega$<br>$R_L = 10k\Omega$               |          | 5                 | 10<br><b>10</b>    | mV               |

| Isc                  | Short-circuit Current                             |                                                      |          |                   | ±60                | mA               |

| CL                   | Maximum Capacitive Load                           |                                                      |          | 1000              |                    | pF               |

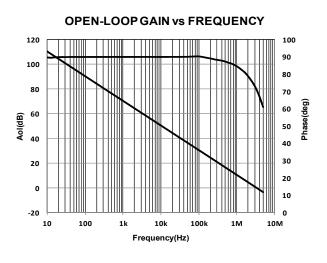

| GBW                  | Unity Gain Bandwidth                              | C <sub>L</sub> = 100pF                               |          | 3.5               |                    | MHz              |

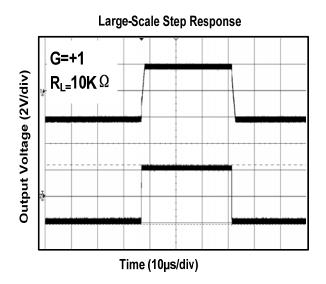

| SR                   | Slew Rate                                         | G = +1, C <sub>L</sub> = 100pF                       |          | 2.5               |                    | V/µs             |

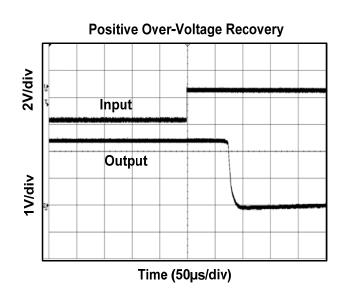

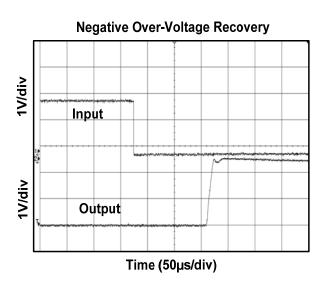

| tor                  | Overload Recovery Time                            | G = -10                                              |          | 35                |                    | μs               |

| ts                   | Settling Time to 0.01%                            | C <sub>L</sub> = 100pF                               |          | 20                |                    | μs               |

| $A_{VO}$             | Open-Loop Voltage Gain                            | $(V-)+0.1V < V_O < (V+)-0.1V,$<br>$R_L = 100k\Omega$ | 100      | 120               |                    | dB               |

|                      | Thermal Resistance Junction to Ambient            | SOT23-5<br>MSOP-8<br>SO-8                            |          | 200<br>210<br>158 |                    | °C/W             |

| $\theta_{JA}$        |                                                   | SC70-5                                               |          | 250               |                    |                  |

|                      |                                                   | SO-14<br>TSSOP-14                                    |          | 83<br>100         |                    |                  |

## **Typical Performance Characteristics**

## **Typical Performance Characteristics**(continue)

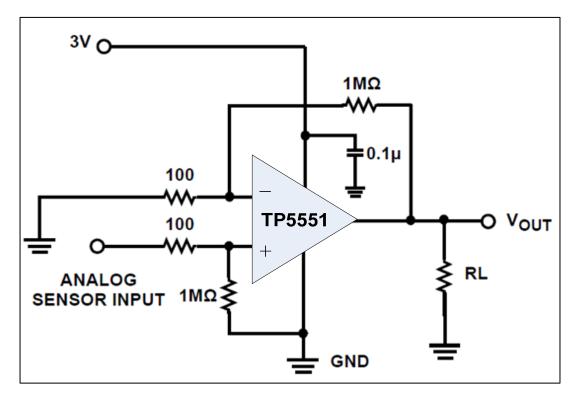

# **TYPICAL APPLICATIONS**

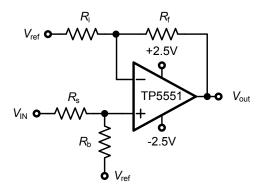

Single Supply, High Gain Amplifier, AV = 10,000 V/V

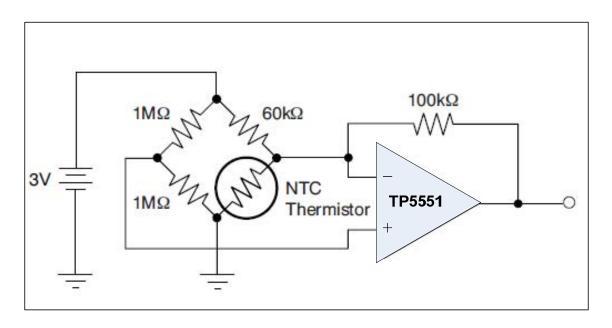

**Thermistor Measurement**

**6** REV1.0 www.3peakic.com

#### **Pin Functions**

-IN: Inverting Input of the Amplifier.

+IN: Non-Inverting Input of Amplifier.

**OUT:** Amplifier Output. The voltage range extends to within mV of each supply rail.

V+ or +V<sub>s</sub>: Positive Power Supply. Typically the voltage is from 1.8V to 5.5V. Split supplies are possible as long as the voltage between V+ and V- is between 1.8V and

5.5V. A bypass capacitor of  $0.1\mu F$  as close to the part as possible should be used between power supply pins or between supply pins and ground.

**V- or -V<sub>s</sub>:** Negative Power Supply. It is normally tied to ground. It can also be tied to a voltage other than ground as long as the voltage between V<sup>+</sup> and V<sup>-</sup> is from 1.8V to 5.5V. If it is not connected to ground, bypass it with a capacitor of  $0.1\mu F$  as close to the part as possible.

#### **Operation**

The TP5551/2/4 op amps are zero drift, rail-to-rail operation amplifiers that can be run from a single-supply voltage. They use an auto-calibration technique with a time-continuous 3.5MHz op amp in the signal path while consuming only 550µA of supply current per channel. This amplifier is zero-corrected with an 150kHz clock. Upon power-up, the amplifier requires approximately 100µs to achieve specified Vos accuracy. This design has no aliasing or flicker noise.

#### **Applications Information**

#### Rail-To-Rail Input And Output

The TP5551/2/4 feature rail-to-rail input and output with a supply voltage from 1.8V to 5.5 V. This allows the amplifier inputs to have a wide common mode range(50mV beyond supply rails)while maintaining high CMRR(120dB) and maximizes the signal to noise ratio of the amplifier by having the  $V_{OH}$  and  $V_{OL}$  levels be at the V+ and V- rails, respectively.

#### **Input Protection**

The TP5551/2/4 have internal ESD protection diodes that are connect between the inputs and supply rail. When either input exceeds one of the supply rails by more than 300mV, the ESD diodes become forward biased and large amounts of current begin to flow through them. Without current limiting, this excessive fault current causes permanent damage to the device. Thus an external series resistor must be used to ensure the input currents never exceed 10mA (see Figure xx).

INPUT ESD DIODE CURRENT LIMITING-UNITY GAIN

www.3peakic.com REV1.0

#### TP5551/TP5552/TP5554

## Ultra Low Noise, 3.5MHz, RRIO Zero-Drift Op-amps

#### **Low Input Referred Noise**

Flicker noise, as known as 1/f noise, is inherent in semiconductor devices and increases as frequency decreases. So at lower frequencies, flicker noise dominates, causing higher degrees of error for sub-Hertz frequencies or dc precision application.

The TP5551/2/4 amplifiers are chopper stabilized amplifiers, the flicker noise is reduced greatly because of this technique. This reduction in 1/f noise allows the TP5551/2/4 to have much lower noise at dc and low frequency compared to standard low noise amplifier.

#### Residual voltage ripple

The chopping technique can be used in amplifier design due to the internal notch filter. Although the chopping related voltage ripple is suppressed, higher noise spectrum exists at the chopping frequency and its harmonics due to residual ripple.

So if the frequency of input signal is nearby the chopping frequency, the signal maybe interfered by the residue ripple. To further suppress the noise at the chopping frequency, it is recommended that a post filter be placed at the output of the amplifier.

#### **Broad Band And External Resistor Noise Considerations**

The total broadband noise output from any amplifier is primarily a function of three types of noise: input voltage noise from the amplifier, input current noise from the amplifier, and thermal (Johnson) noise from the external resistors used around the amplifier. These noise sources are not correlated with each other and their combined noise can be summed in a root sum squared manner. The full equation is given as:

$$e_n total = [e_n^2 + 4kTR_s + (i_n \times R_s)^2]^{1/2}$$

Where:

$e_n$ = the input voltage noise density of the amplifier.

$i_0$ = the input current noise of the amplifier.

$R_{\rm S}$ = source resistance connected to the noninverting terminal.

k= Boltzmann' s constant (1.38x10<sup>-23</sup>J/K). T= ambient temperature in Kelvin (K).

The total equivalent rms noise over a specific bandwidth is expressed as:

$$e_{n,rms} = e_n \ total \times \sqrt{BW}$$

The input voltage noise density (en) of the TP555x is 55 nV/ $\sqrt{\text{Hz}}$ , and the input current noise can be neglected. When the source resistance is 190 k $\Omega$ , the voltage noise contribution from the source resistor and the amplifier are equal. With source resistance greater than 190 k $\Omega$ , the overall noise of the system is dominated by the Johnson noise of the resistor itself.

#### **High Source Impedance Application**

The TP5551/2/4 uses switches at the chopper amplifier input, the input signal is chopped at 125kHz to reduce input offset voltage down to  $10\mu V$ . The dynamic behavior of these switches induces a charge injection current to the input terminals of the amplifier. The charge injection current has a DC path to ground through the resistances seen at the input terminals of the amplifier. Higher input impedance cause an apparent shift in the input bias current of the amplifier.

Because the chopper amplifier has charge injection currents at each terminal, the input offset current will be larger than standard amplifiers. The los of TP5551/2/4 are 150pA under the typical condition. So the input impedance should be balanced across each input(see Figure xx). The input impedance of the amplifier should be matched between the IN+ and IN- terminals to minimize total input offset current. Input offset currents show up as an additional output offset voltage, as shown in the following equation:

**8** REV1.0 www.3peakic.com

$$v_{os,total} = v_{os} - R_f \times I_{os}$$

For a gain configure using  $1M\Omega$  feedback resistor, a 150pA total input offset current will have an additional output offset voltage of 0.15mV. By keeping the input impedance low and balanced across the amplifier inputs, the input offset current effect will be suppress efficiently.

Figxx Circuit Implication for reducing Input offset current effect

#### **PCB Surface Leakage**

In applications where low input bias current is critical, Printed Circuit Board (PCB) surface leakage effects need to be considered. Surface leakage is caused by humidity, dust or other contamination on the board. It is recommended to use multi-layer PCB layout and route the OPA's -IN and +IN signal under the PCB surface.

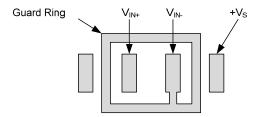

The effective way to reduce surface leakage is to use a guard ring around sensitive pins (or traces). The guard ring is biased at the same voltage as the sensitive pin. An example of this type of layout is shown in Figure 2 for Inverting Gain application.

- 1. For Non-Inverting Gain and Unity-Gain Buffer:

- a) Connect the non-inverting pin  $(V_{IN}+)$  to the input with a wire that does not touch the PCB surface.

- b) Connect the guard ring to the inverting input pin (V<sub>IN</sub>-). This biases the guard ring to the Common Mode input voltage.

- 2. For Inverting Gain and Trans-impedance Gain Amplifiers (convert current to voltage, such as photo detectors):

- a) Connect the guard ring to the non-inverting input pin  $(V_{IN}+)$ . This biases the guard ring to the same reference voltage as the op-amp (e.g.,  $V_{DD}/2$  or ground).

- b) Connect the inverting pin (V<sub>IN</sub>-) to the input with a wire that does not touch the PCB surface.

Figure The Layout of Guard Ring

## **Package Outline Dimensions**

SOT23-5 / SOT23-6

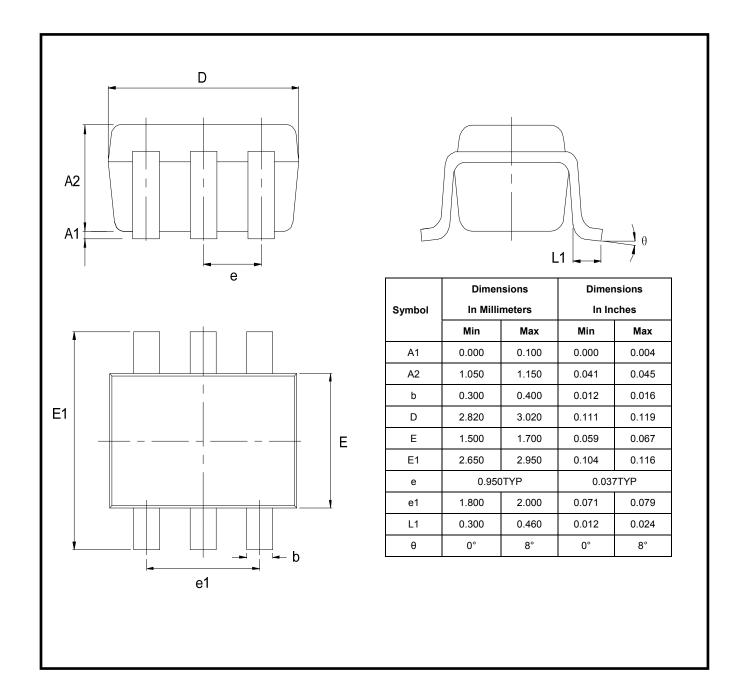

## **Package Outline Dimensions**

SC-70-6 (SOT363)

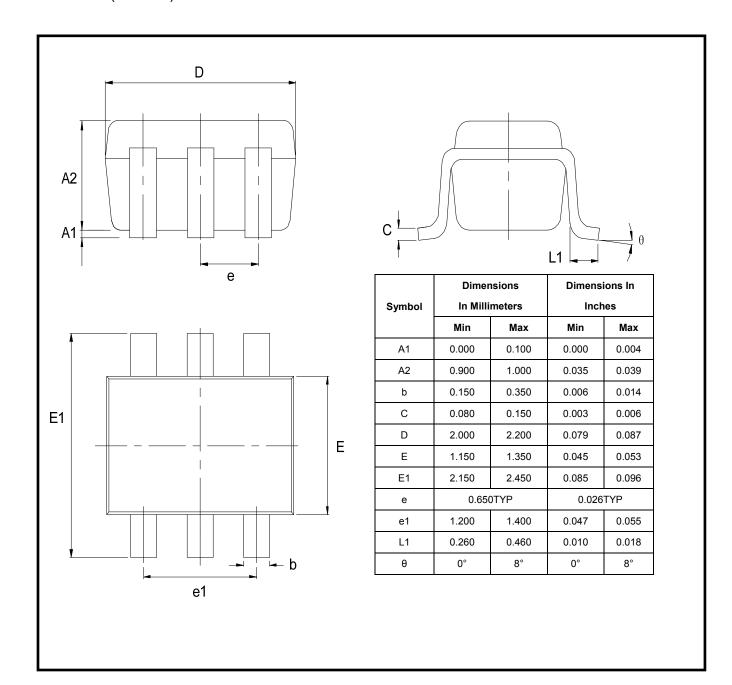

# Ultra Low Noise, 3.5MHz, RRIO Zero-Drift Op-amps Package Outline Dimensions

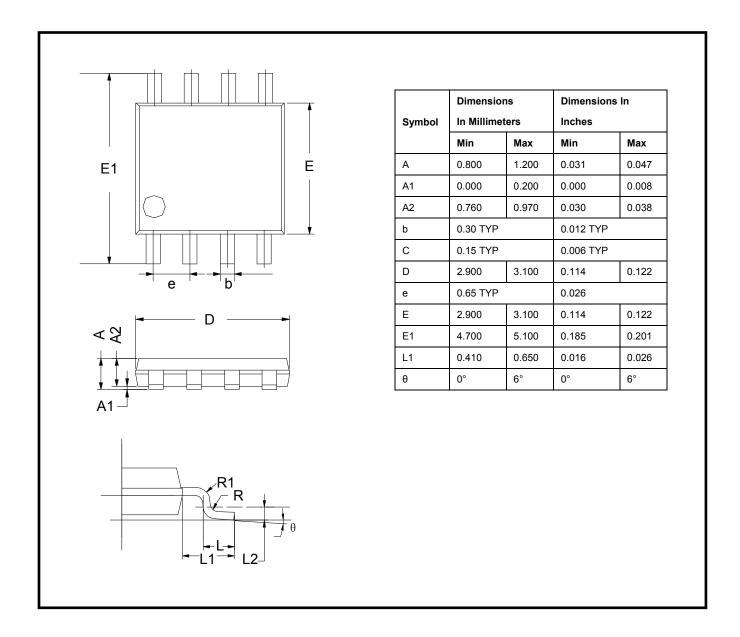

SO-8 (SOIC-8)

## **Package Outline Dimensions**

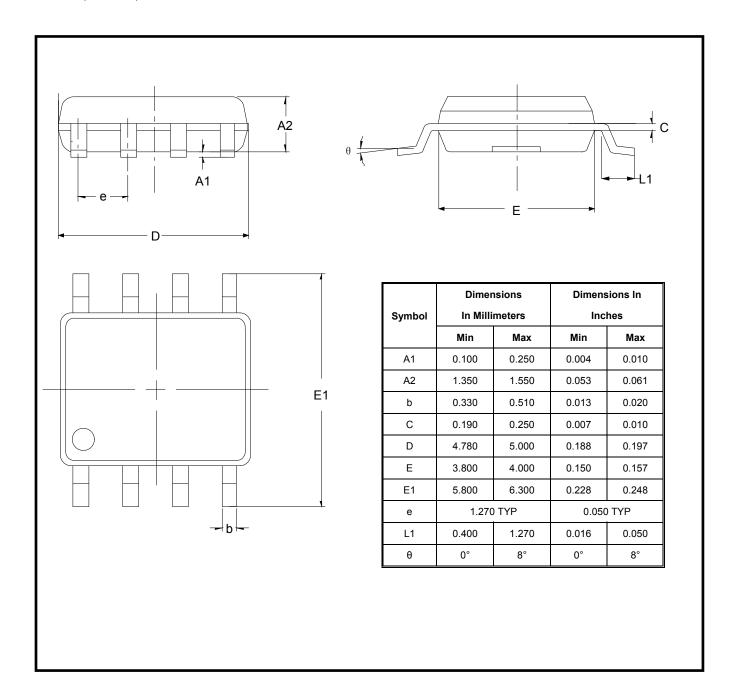

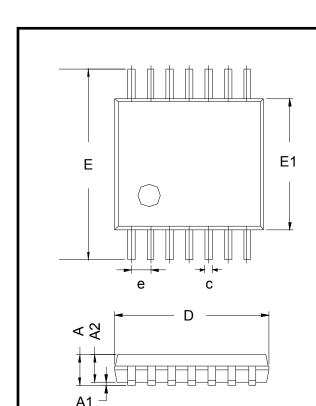

MSOP-8

# **Package Outline Dimensions**

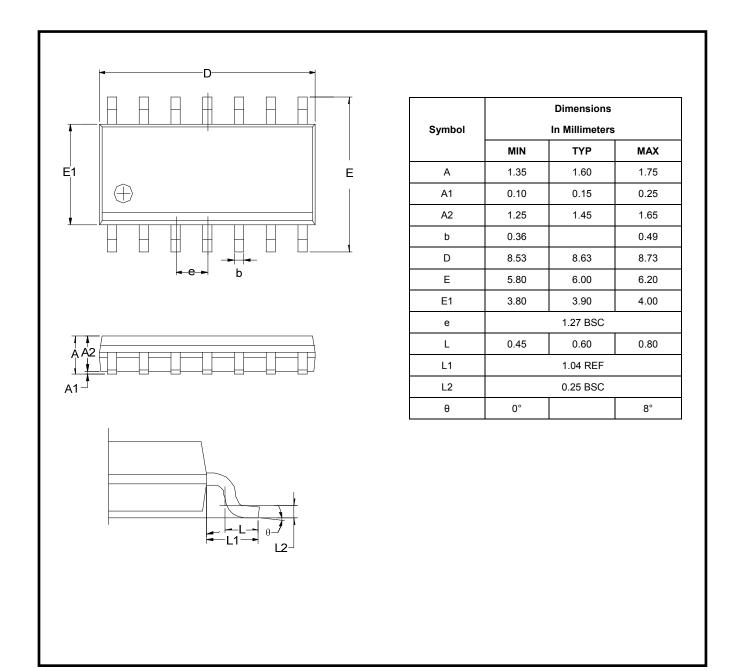

TSSPO-14

|        | Dimensions     |      |      |

|--------|----------------|------|------|

| Symbol | In Millimeters |      |      |

| Symbol | MIN            | TYP  | MAX  |

| Α      | =              | -    | 1.20 |

| A1     | 0.05           | -    | 0.15 |

| A2     | 0.90           | 1.00 | 1.05 |

| b      | 0.20           | -    | 0.28 |

| С      | 0.10           | -    | 0.19 |

| D      | 4.86           | 4.96 | 5.06 |

| E      | 6.20           | 6.40 | 6.60 |

| E1     | 4.30           | 4.40 | 4.50 |

| е      | 0.65 BSC       |      |      |

| L      | 0.45           | 0.60 | 0.75 |

| L1     | 1.00 REF       |      |      |

| L2     | 0.25 BSC       |      |      |

| R      | 0.09           |      | -    |

| θ      | 0°             | -    | 8°   |

www.3peakic.com

## **Package Outline Dimensions**

SO-14 (SOIC-14)

# 单击下面可查看定价,库存,交付和生命周期等信息

# >>3PEAK(思瑞浦)