# ANSILIC

### Table of Contents

| 1 | Features                                   | 2  |

|---|--------------------------------------------|----|

| 2 | Product Description                        | 4  |

| 3 | Pin definition                             | 6  |

| 4 | Internal circuit structure diagram         | 7  |

| 5 | Bus transceiver electrical characteristics | 8  |

| 6 | Test circuit waveform timing diagram       | 11 |

|   | Note                                       |    |

|   |                                            |    |

### 1 Features

- AEC-Q100 (Level 1) support: Meets automotive application requirements

- Complies with ISO 11898-2:2016 and ISO 11898-5:2007 Physical layer standards,

- Provide functional safety

- Documentation to help with functional safety system design

- Support 5Mbps

- With a short symmetric propagation delay time and a fast number of cycles, the timing margin can be increased

- Faster data rates in loaded CAN networks

- EMC Performance: Support SAE J2962-2 and IEC 62228-3 (up to 500kbps) without a common mode choke

- The I/O voltage range supports 3.3V and 5V MCUS

- Ideal passive behavior when unpowered

- Bus and logic pins in high resistance (no load)

- Uninterrupted operation and protection on/off bus and RXD outputs

- Protection features

- IEC ESD protection up to ±15kV

- Bus fault protection: ±58V (non-H model) and ±70V (H model)

- VCC and VIO (V models only) power terminals have undervoltage protection

- Drive Explicit Timeout (TXD DTO) Data rates as low as 10kbps

- Thermal shutdown Protection (TSD)

- Receiver common-mode input voltage: ±30V

- Typical loop delay: 110ns

- SEU: ≥75Mev.cm2/mg or 10<sup>(-5)</sup> times/device.day (Commercial aerospace grade)

- SEL: ≥75Mev.cm2/mg (Commercial aerospace grade)

### 2 **Product Description**

This CAN transceiver family complies with the ISO1189-2 (2016) High Speed CAN (Controller Local Area Network) physical layer standard. All devices are designed for CAN FD networks with data rates up to 2Mbps (megabits per second). The transceiver supports a data rate of 5Mbps and provides an auxiliary power input for I/O levels to set input pin thresholds and RXD output levels. The series features low power standby mode and remote wake request. In addition, the device offers a variety of protection features to improve the durability of the device and network.

Chip models are as follows:

| Chip type                    | Chip Model | Grade                   | Package |

|------------------------------|------------|-------------------------|---------|

| Communication interface chip | ASM1042I6S | Industrial              | SOIC8   |

| Communication interface chip | ASM1042A3S | Automotive              | SOIC8   |

| Communication interface chip | ASM1042S8S | Commercial<br>aerospace | SOIC8   |

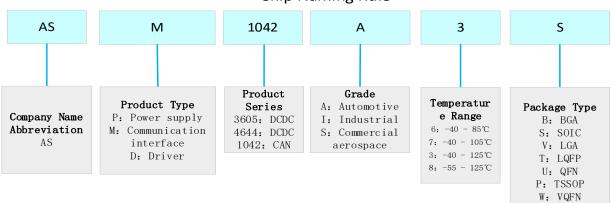

#### Chip Naming Rule

| Parameters                                     | Symbol  | Min. | Max. | Unit |

|------------------------------------------------|---------|------|------|------|

| Bus supply voltage                             | VCC     | -0.3 | 7    | V    |

| Supply voltage of the I/O port                 | VIO     | -0.3 | 7    | V    |

| CAN bus I/O voltage range                      | VBUS    | -70  | 70   | V    |

| Max. pressure difference between CANH and CANL | V(Diff) | -70  | 70   | V    |

| Voltage range of the logical port | VTXD、VSTB、VRXD | -0.3 | 7   | V  |

|-----------------------------------|----------------|------|-----|----|

| RXD Output current                | IO(RXD)        | -8   | 8   | mA |

| Junction temperature              | TJ             | -55  | 150 | °C |

# 3 Pin definition

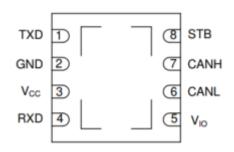

### Figure 1 Pin distribution of FD CAN chip

| Pin number | Pin name | Pin function                                                      |

|------------|----------|-------------------------------------------------------------------|

| 1          | TXD      | Transmitter data input side                                       |

| 2          | GND      | Ground                                                            |

| 3          | VCC      | Receiver power supply                                             |

| 4          | RXD      | Receiver input                                                    |

| 5          | VIO      | Receiver I/O power supply                                         |

| 6          | CANL     | Low potential CAN input and output                                |

| 7          | CANH     | High potential CAN input and output                               |

| 8          | STB      | Standby mode the control terminal, high level are in standby mode |

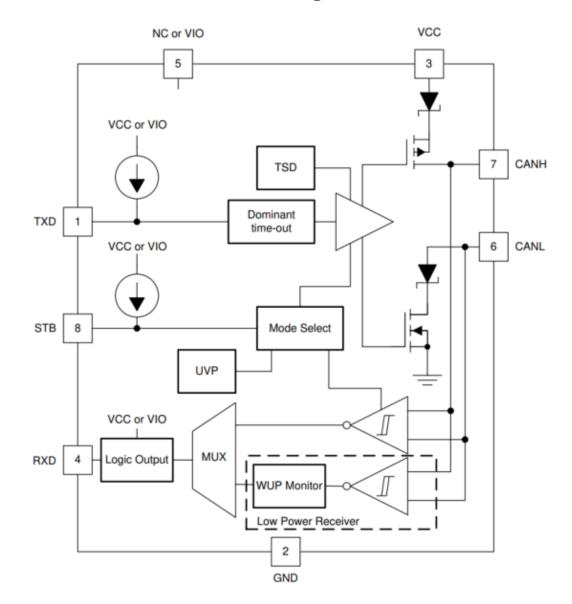

# 4 Internal circuit structure diagram

Figure 2 Block diagram of internal circuit structure

### 5 **Bus transceiver electrical characteristics**

| Characteristics                                                                                                                                                                                                            | Symbol          | Limit/standard value |         | Limit/standard value |      |  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------|---------|----------------------|------|--|------|

|                                                                                                                                                                                                                            | Symbol          | Min.                 | Typical | Max.                 | Cint |  |      |

| Dominant power<br>consumption (Normal<br>mode), TXD=0V,<br>R <sub>L</sub> =60Ω, C <sub>L</sub> =open,<br>R <sub>CM</sub> =open, STB=0V,<br>The load conditions are<br>shown in Figure 3.                                   |                 |                      | 40      | 70                   |      |  |      |

| Bus fault explicit power<br>consumption (Normal<br>mode), TXD=0, V <sub>CANH</sub> =-<br>12V, R <sub>L</sub> =open,<br>C <sub>L</sub> =open, R <sub>CM</sub> =open,<br>The load conditions are<br>shown in Figure 3.       |                 |                      |         | 110                  | mA   |  |      |

| Recessive power<br>consumption (Normal<br>mode), TXD=V <sub>CC</sub> or V <sub>IO</sub> ,<br>R <sub>L</sub> =50Ω, C <sub>L</sub> =open,<br>R <sub>CM</sub> =open, STB=0V,<br>The load conditions are<br>shown in Figure 3. | Icc             |                      | 1.5     | 2.5                  |      |  |      |

| Power consumption when<br>the load is a V device<br>(Standby mode),<br>$TXD=V_{IO}$ , $R_L=50\Omega$ ,<br>$C_L=open$ , $R_{CM}=open$ ,<br>$STB=V_{IO}$ , The load<br>conditions are shown in<br>Figure 3.                  |                 |                      | 0.5     | 5                    |      |  |      |

| Power consumption of a<br>device without a V model<br>(Standby mode),<br>$TXD=V_{CC}$ , $R_L=50\Omega$ ,<br>$C_L=open$ , $R_{CM}=open$ ,<br>STB=VCC, The load<br>conditions are shown in<br>Figure 3.                      |                 |                      |         | 22                   | μA   |  |      |

| I/O Power consumption<br>(Normal mode)                                                                                                                                                                                     | l <sub>io</sub> |                      | 90      | 300                  |      |  |      |

#### **Basic parameters**

| I/O Power consumption<br>(Standby mode)                                                                                                                                                               |                                      |      | 12      | 17   |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------|---------|------|-----|

| V <sub>CC</sub> Undervoltage<br>protection rise threshold<br>voltage                                                                                                                                  | UVcc                                 |      | 4.2     | 4.4  | V   |

| V <sub>CC</sub> Undervoltage<br>protection drop threshold<br>voltage                                                                                                                                  | UVCC                                 | 3.8  | 4.0     | 4.25 | v   |

| U <sub>VCC</sub> Hysteretic voltage                                                                                                                                                                   | V <sub>HYS(UVVCC)</sub>              |      | 200     |      | mV  |

| V <sub>IO</sub> Undervoltage protection threshold                                                                                                                                                     | UV <sub>VIO</sub>                    | 1.3  |         | 2.75 | V   |

| U <sub>VVIO</sub> Hysteretic voltage                                                                                                                                                                  | V <sub>HYS(UVVIO)</sub>              |      | 80      |      | mV  |

| Dominant output voltage<br>(Normal mode)                                                                                                                                                              | V <sub>CANH</sub>                    | 2.75 |         | 4.5  |     |

| 50Ω≤R <sub>L</sub> ≤65Ω, C <sub>L</sub> =open,<br>R <sub>CM</sub> =open, The load                                                                                                                     | Vcanl                                | 0.5  |         | 2.25 |     |

| conditions are shown in<br>Figure 3.                                                                                                                                                                  | V <sub>CANH</sub> -V <sub>CANL</sub> | 1.5  |         | 3    | V   |

| Recessive output voltage<br>(Normal mode)                                                                                                                                                             | $V_{CANH}$ and $V_{CANL}$            | 2    | 0.5×VCC | 3    |     |

| $\begin{array}{c} TXD{=}V_{CC} \text{ or } V_{IO},\\ V_{IO}{=}V_{CC}, \ STB{=}0V,\\ R_{L}{=}open(no \ load),\\ R_{CM}{=}open, \ The \ load\\ conditions \ are \ shown \ in\\ Figure \ 3. \end{array}$ | V <sub>CANH</sub> -V <sub>CANL</sub> | -50  |         | 50   | mV  |

| Output voltage (Standby mode)                                                                                                                                                                         | V <sub>CANH</sub>                    | -0.1 | 0       | 0.1  |     |

| STB=V <sub>IO</sub> , R <sub>L</sub> =open(no<br>load), R <sub>CM</sub> =open, The                                                                                                                    | V <sub>CANL</sub>                    | -0.1 | 0       | 0.1  | V   |

| load conditions are shown<br>in Figure 3.                                                                                                                                                             | V <sub>CANH</sub> -V <sub>CANL</sub> | -0.2 | 0       | 0.2  |     |

| Output level matching                                                                                                                                                                                 | V <sub>SYM</sub>                     | 0.9  |         | 1.1  | V/V |

| Dc output level matching                                                                                                                                                                              | V <sub>SYM_DC</sub>                  | -0.4 |         | 0.4  | V   |

| Dominant short-circuit<br>output current (Normal<br>mode), VCANH=-<br>5V~40V, CANL=open                                                                                                               |                                      | -100 |         |      |     |

| Dominant short-circuit<br>output current (Normal<br>mode), V <sub>CANH</sub> =-5V~40V,<br>CANL=open                                                                                                   | Ios(ss_dom)                          |      |         | 100  | mA  |

| Recessive short-circuit output current (Normal                                                                                                                                                        | I <sub>OS(SS_REC)</sub>              | -5   |         | 5    |     |

| mode),<br>V <sub>BUS</sub> =V <sub>CANH</sub> =V <sub>CANL</sub> ,<br>-27V≪VBUS≪32V                                                                              |                               |     |       |     |             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----|-------|-----|-------------|

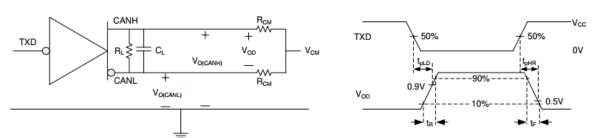

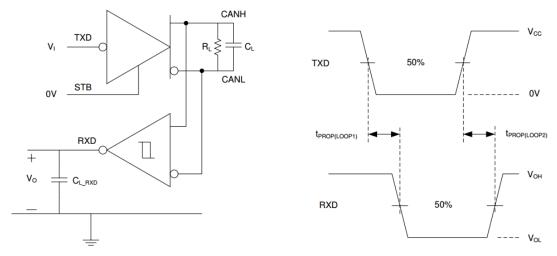

| Loop delay (recessive to<br>dominant), the load<br>conditions are shown in<br>Figure 5.                                                                          | tprop(loop1)                  |     | 100   | 160 | ns          |

| Loop delay (recessive to<br>dominant), the load<br>conditions are shown in<br>Figure 5.                                                                          | tprop(loop2)                  |     | 110   | 175 | ns          |

| Mode switching time from<br>Normal to Standby                                                                                                                    | t <sub>MODE</sub>             |     | 9     | 45  | μs          |

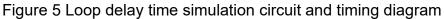

| Filter mode wakeup time                                                                                                                                          | t <sub>wk_filter</sub>        | 0.5 |       | 1.8 | <b>P</b> .0 |

| Transmission<br>delay(recessive to<br>dominant), the load<br>conditions are shown in<br>Figure 3. R <sub>L</sub> =60Ω,<br>CL=100pF,<br>CL(RXD)=15pF <sub>°</sub> | t <sub>pHR</sub>              |     | 55    |     |             |

| Transmission<br>delay(dominant to<br>recessive), the load<br>conditions are shown in<br>Figure 3. R <sub>L</sub> =60Ω,<br>CL=100pF,<br>CL(RXD)=15pF <sub>°</sub> | t <sub>pLD</sub>              |     | 75    |     | ns          |

| Dominant Timeout                                                                                                                                                 | t <sub>txd_dto</sub>          | 1.2 |       | 3.8 | ms          |

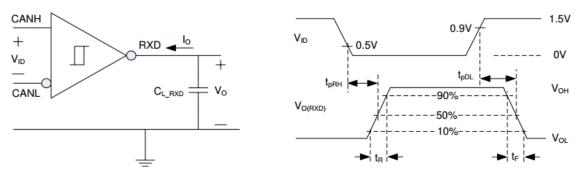

| Transmission<br>delay(recessive to<br>dominant), the load<br>conditions are shown in<br>Figure 4. C <sub>L(RXD)</sub> =15pF。                                     | t <sub>pRH</sub>              |     | 65    |     |             |

| Transmission<br>delay(dominant to<br>recessive), the load<br>conditions are shown in<br>Figure 4. C <sub>L(RXD)</sub> =15pF。                                     | t <sub>pDL</sub>              |     | 50    |     | ns          |

| CAN bus pin human body discharge model (HBM)                                                                                                                     | $V_{\text{ESD}_{\text{HBM}}}$ |     | ±6000 |     |             |

| Module charging model<br>(CDM)                                                                                                                                   | $V_{ESD_{CDM}}$               |     | ±1500 |     | V           |

| Mechanical model (MM)                                                                                                                                            | $V_{\text{ESD}\_\text{MM}}$   |     | ±200  |     |             |

# 6 Test circuit waveform timing diagram

Figure 3 FDCAN transmit test circuit and timing diagram

Figure 4 FDCAN receiving test circuit and timing diagram

### 7 Note

#### 1 Over-temperature protection

The transceiver chip has the function of overtemperature protection. When the overtemperature protection is triggered, the drive circuit will be closed, the drive current will be reduced, and the chip temperature will be reduced.

#### 2 Under voltage protection

The transceiver chip VCC and VIO power pins both feature undervoltage protection to protect the bus when the VCC and VIO voltages fall below the threshold voltage.

#### 3 Standby mode

Standby mode can be activated when STB is set to high power level. Both the CAN driver and receiver are turned off at this time to save power. The STB high level signal activates the low power receiver and wake filter, and when the bus detects a primary bus level that exceeds the tWK\_FILTER, the pin RXD changes to low.

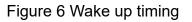

#### 4 Explicit timeout function

When the low-level duration on pin TXD exceeds tTXD\_DTO, the transmitter is disabled and the CAN bus enters a hidden state to prevent network congestion caused by application failure on pin TXD. The TXD rising edge signal resets the dominant timeout protection.

Figure 7 Sequence of explicit timeout protection

单击下面可查看定价,库存,交付和生命周期等信息

>>ANSILIC(国科安芯)