# AOZ5049QI-02

High-Current, High-Performance DrMOS Power Module

#### **General Description**

The AOZ5049QI-02 is a high efficiency synchronous buck power stage module consisting of two asymmetrical MOSFETs and an integrated driver. The MOSFETs are individually optimized for operation in the synchronous buck configuration. The High Side (HS) MOSFET is optimized to achieve low capacitance and gate charge for fast switching with low duty cycle operation. The Low Side (LS) MOSFET has ultra low on-resistance to minimize conduction loss. The compact 3.5mm x 5mm QFN package is optimally chosen and designed to minimize parasitic inductance for minimal EMI signature.

The AOZ5049QI-02 is intended to be used for 5V PWM Logic with Tri-state compatibility. The 5V FCCM input pin also has Tri-State Level compatibility to fascilitate the different modes for step-down operation.

The bootstrap diode is integrated in the driver. The low side MOSFET can be driven into diode emulation mode to provide asynchronous operation when required. The pin-out is optimized for low inductance routing of the converter, keeping the parasitics and their effects to a minimum.

#### **Features**

- 4.5V to 25V power supply range

- 4.5V to 5.5V driver supply range

- Up to 35A output current

- Integrated bootstrap Schottky diode

- Up to 2MHz switching operation

- Tri-state FCCM/PWM input compatible

- Under-voltage lockout protection

- Single pin control for shutdown/diode emulation/CCM operation

- Small 3.5mm x 5mm QFN-24L package

### **Applications**

- Servers

- Notebook computers

- VRMs for motherboards

- Point-of-load DC/DC converters

- Memory and graphic cards

- Video gaming consoles

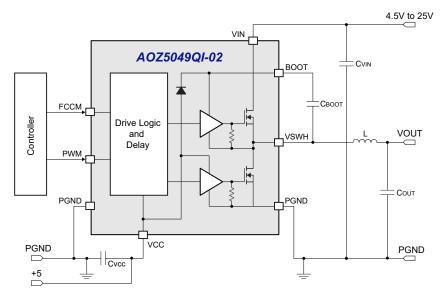

### **Typical Application Circuit**

## **Ordering Information**

| Part Number  | Ambient Temperature Range | Package             | Environmental |

|--------------|---------------------------|---------------------|---------------|

| AOZ5049QI-02 | -40°C to +85°C            | 3.5mm x 5mm QFN-24L | RoHS          |

AOS Green Products use reduced levels of Halogens, and are also RoHS compliant. Please visit www.aosmd.com/media/AOSGreenPolicy.pdf for additional information.

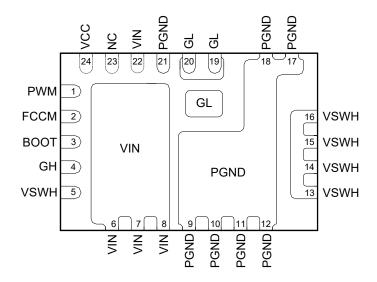

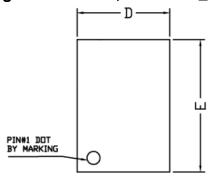

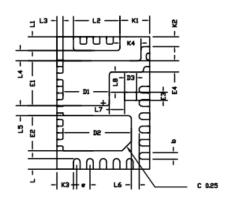

## **Pin Configuration**

## **Pin Description**

| Pin Number               | Pin Name | Pin Function                                                                                                                                                                                                                       |

|--------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                        | PWM      | PWM input signal from the controller IC. This input is compatible with 5V and Tri-State logic level Low Side.                                                                                                                      |

| 2                        | FCCM     | Continuous conduction mode of operation is allowed when FCCM = High.  Discontinuous mode is allowed and diode emulation mode is active when FCCM = Low.  High impedance on the input of FCCM will shutdown both HS and LS MOSFETs. |

| 3                        | воот     | HS MOSFET Gate Driver supply rail (5V wrt VSWH). Connect a 100nF ceramic capacitor between BOOT and the VSWH (Pin 5).                                                                                                              |

| 4                        | GH       | HS MOSFET Gate pin.                                                                                                                                                                                                                |

| 5                        | VSWH     | Switching node connected to the source of HS MOSFET and the drain of LS MOSFET. This pin is dedicated for bootstrap capacitor connection to the BOOT pin. It is optional to connect to Pin 13 externally on PCB.                   |

| 6, 7, 8                  | VIN      | Power stage high voltage input pin.                                                                                                                                                                                                |

| 9, 10, 11, 12,<br>17, 18 | PGND     | Power Ground pin for power stage.                                                                                                                                                                                                  |

| 13, 14, 15, 16           | VSWH     | Switching node connected to the source of HS MOSFET and the drain of LS MOSFET. These pins are being used for Zero Cross Detect, Bootstrap UVLO and Anti-Overlap Control.                                                          |

| 19, 20                   | GL       | LS MOSFET Gate pin.                                                                                                                                                                                                                |

| 21                       | PGND     | Power Ground pin for LS MOSFET Gate Driver.                                                                                                                                                                                        |

| 22                       | VIN      | Power stage high voltage input pin.                                                                                                                                                                                                |

| 23                       | NC       | No Connect. Optional connection to Pin 24 rendering no effect in performance and operation.                                                                                                                                        |

| 24                       | VCC      | Serves as Input Bias and LS MOSFET Gate Driver Rail. Connect a 2.2µF MLCC directly across to this pin and PGND (Pin 21).                                                                                                           |

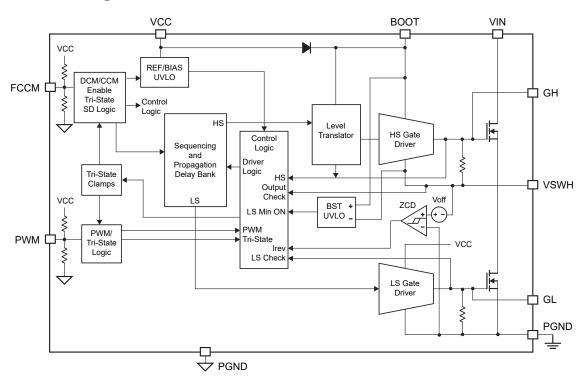

## **Functional Block Diagram**

#### **Absolute Maximum Ratings**

Exceeding the Absolute Maximum ratings may damage the device.

| Parameter                                               | Rating                       |

|---------------------------------------------------------|------------------------------|

| Low Voltage Supply (VCC)                                | -0.3V to 7V                  |

| High Voltage Supply (VIN)                               | -0.3V to 30V                 |

| Control Inputs (PWM, FCCM)                              | -0.3V to (VCC+0.3V)          |

| Bootstrap Voltage DC (BOOT-PGND)                        | -0.3V to 33V                 |

| Bootstrap Voltage DC (BOOT-VSWH)                        | -0.3V to 7V                  |

| BOOT Voltage Transient (1)<br>(BOOT-VSWH)               | -0.3V to 9V                  |

| Switch Node Voltage DC (VSWH)                           | -0.3V to 30V                 |

| Switch Node Voltage Transient <sup>(1)</sup> (VSWH)     | -0.3V to 38V                 |

| High Side Gate Voltage DC (GH)                          | (VSWH-0.3V) to BOOT          |

| High Side Gate Voltage<br>Transient <sup>(2)</sup> (GH) | (VSWH-5V) to BOOT            |

| Low Side Gate Voltage DC (GL)                           | (PGND-0.3V) to<br>(VCC+0.3V) |

| Low Side Gate Voltage<br>Transient <sup>(2)</sup> (GL)  | (PGND-2.5V) to<br>(VCC+0.3V) |

| Storage Temperature (T <sub>S</sub> )                   | -65°C to +150°C              |

| Max Junction Temperature (T <sub>J</sub> )              | 125°C                        |

| ESD Rating <sup>(3)</sup>                               | 2kV                          |

#### Notes:

- 1. Peak voltages can be applied for 10ns per switching cycle.

- 2. Peak voltages can be applied for 20ns per switching cycle.

- 3. Devices are inherently ESD sensitive, handling precautions are required. Human body model rating: 1.5k $\Omega$  in series with 100pF.

## **Recommended Operating Conditions**

The device is not guaranteed to operate beyond the Maximum Recommended Operating Conditions.

| Parameter                                | Rating           |

|------------------------------------------|------------------|

| High Voltage Supply (VIN)                | 4.5V to 25V      |

| Low Voltage Supply<br>{VCC, (BOOT-VSWH)} | 4.5V to 5.5V     |

| Control Inputs (PWM, FCCM)               | 0V to (VCC-0.3V) |

| Operating Frequency                      | 200kHz to 2MHz   |

Electrical Characteristics<sup>(4)</sup>  $T_A = 25$ °C,  $V_{IN} = 12$ V,  $V_{CC} = 5$ V unless otherwise specified.

| Symbol                | Parameter                              | Conditions                                                                                                                         | Min. | Тур. | Max. | Units          |

|-----------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----------------|

| V <sub>IN</sub>       | Power Stage Power Supply               |                                                                                                                                    | 4.5  |      | 25   | V              |

| V <sub>CC</sub>       | Driver Power Supply                    | VCC = 5V                                                                                                                           | 4.5  |      | 5.5  | V              |

| $R_{\theta JC}$       |                                        | PCB Temp = 100°C                                                                                                                   |      | 3    |      | °C / W         |

| $R_{\theta JA}$       | Thermal Resistance                     | AOS Demo Board                                                                                                                     |      | 18.5 |      | °C / W         |

|                       | PLY AND UVLO                           |                                                                                                                                    |      |      |      |                |

| V <sub>CC</sub>       |                                        | VCC Rising                                                                                                                         |      | 3.4  | 3.9  | V              |

| V <sub>CC_HYST</sub>  | Under-Voltage Lockout                  | VCC Falling                                                                                                                        |      | 500  |      | mV             |

| I <sub>VCC_SD</sub>   | Shutdown Bias Supply Current           | FCCM = Floating (Shutdown) VPWM = Internally Pulled Low                                                                            |      | 3    |      | μΑ             |

|                       | 0 1 10: "5: 0 1                        | FCCM = 5V (CCM), VPWM = Floating                                                                                                   |      | 80   |      | μΑ             |

|                       | Control Circuit Bias Current           | FCCM = 0V (DCM), VPWM = Floating                                                                                                   |      | 120  |      | μΑ             |

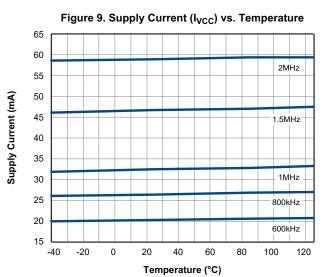

| I <sub>VCC</sub>      |                                        | FCCM = 5V, VPWM = 800kHz                                                                                                           |      | 27   |      | mA             |

| PWM INPU              | Switching Current (I <sub>BIAS</sub> + | FCCM = 5V, VPWM = 1MHz                                                                                                             |      | 34   |      | mA             |

|                       | I <sub>DRV</sub> )                     | FCCM = 5V, VPWM = 1.5MHz                                                                                                           |      | 48   |      | mA             |

| PWM INPU              | Т                                      |                                                                                                                                    |      |      |      |                |

| V <sub>PWMH</sub>     | PWM Input High Threshold               | V <sub>PWM</sub> Rising, VCC = 5V                                                                                                  | 4.1  |      |      | V              |

| V <sub>PWML</sub>     | PWM Input Low Threshold                | V <sub>PWM</sub> Falling, VCC = 5V                                                                                                 |      |      | 0.7  | V              |

| 1 771112              |                                        | Source, PWM = 5V                                                                                                                   |      | +250 |      | μΑ             |

| $I_{PWM}$             | PWM Pin Input Current                  | Sink, PWM = 0V                                                                                                                     |      | -250 |      | <u>.</u><br>μΑ |

| V <sub>TRI</sub>      | PWM Input Tri-State Threshold Window   | PWM = High Impedance                                                                                                               | 1.5  |      | 3.3  | ·<br>V         |

| FCCM INPL             |                                        |                                                                                                                                    |      |      |      |                |

| V <sub>FCCMH</sub>    | 50045 11 71 111                        | FCCM Rising, VCC = 5V<br>Shutdown → CCM                                                                                            | 3.8  |      |      | V              |

| V <sub>FCCML</sub>    | FCCM Enable Threshold                  | FCCM Falling, VCC = 5V<br>Shutdown → DCM                                                                                           |      |      | 1.2  | V              |

|                       | 500MB: 1 10 1                          | Source, FCCM = 5V                                                                                                                  |      | +50  |      | μΑ             |

| I <sub>FCCM</sub>     | FCCM Pin Input Current                 | Sink, FCCM = 0V                                                                                                                    |      | -50  |      | μΑ             |

| V <sub>TRI</sub>      | FCCM Input Tri-State Threshold Window  | FCCM = High Impedance                                                                                                              | 2.1  |      | 2.9  | V              |

| V <sub>TRI_HYST</sub> | FCCM Input Threshold<br>Hysteresis     | $\begin{array}{c} \text{Shutdown} \to \text{CCM} \to \text{Shutdown} \\ \text{DCM} \to \text{Shutdown} \to \text{DCM} \end{array}$ |      | 300  |      | mV             |

| $t_{PTS}$             | PS4 Exit Latency                       | VCC = 5V                                                                                                                           |      |      | 15   | μS             |

| GATE DRIV             | ER TIMING                              |                                                                                                                                    |      |      |      |                |

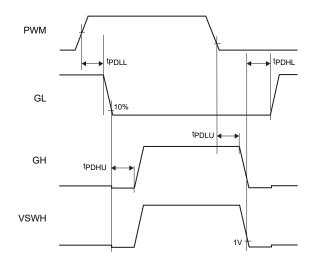

| t <sub>PDLU</sub>     | PWM Falling to GH Turn-Off             | PWM 10%, GH 90%                                                                                                                    |      | 18   |      | ns             |

| t <sub>PDLL</sub>     | PWM Raising to GL Turn-Off             | PWM 90%, GL 90%                                                                                                                    |      | 25   |      | ns             |

| t <sub>PDHU</sub>     | GL Falling to GH Rising<br>Deadtime    | GL 10%, GH 10%                                                                                                                     |      | 20   |      | ns             |

| t <sub>PDHL</sub>     | GH/VSWH Falling to GL Rising Deadtime  | VSWH @ 1V, GL 10%                                                                                                                  |      | 20   |      | ns             |

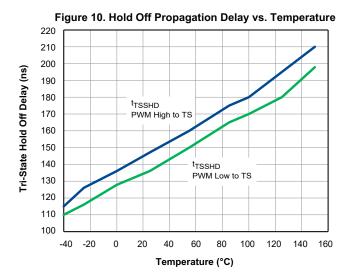

| t <sub>TSSHD</sub>    | Tri-State Shutdown Delay               | TS to GH Falling, TS to GL Falling                                                                                                 |      | 175  |      | ns             |

| t <sub>PTS</sub>      | Tri-State Propagation Delay            | GH = GL = 0V<br>PWM: Tri-State to Rising →GH Rising<br>PWM: Tri-State to FallingGL Rising                                          |      | 35   |      | ns             |

| t <sub>LGMIN</sub>    | Low-Side Minimum On-Time               | FCCM = 0V                                                                                                                          |      | 350  |      | ns             |

#### Note:

4. All voltages are specified with respect to the corresponding PGND pin

Rev. 1.0 July 2017 Page 5 of 15 www.aosmd.com

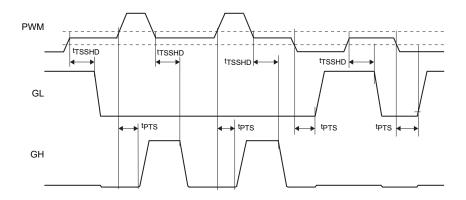

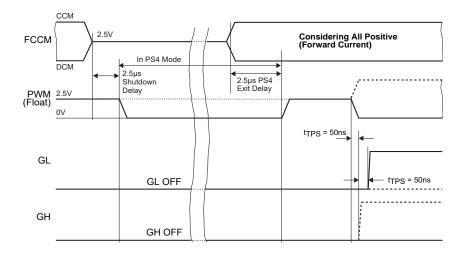

## **Timing Diagram**

Figure 1. PWM Logic Input Timing Diagram

Figure 2. PWM Tri-State Input Logic Timing Diagram

Figure 3. FCCM Logic During High Impedance at PWM Input

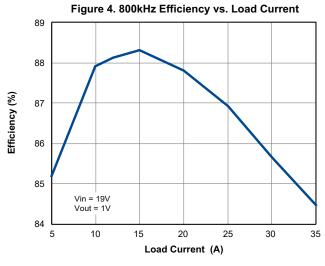

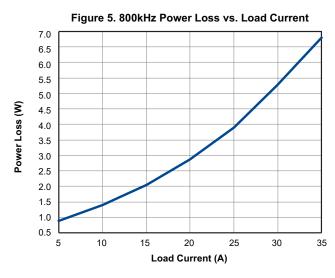

## **Typical Performance Characteristics**

$T_A$  = 25°C,  $V_{IN}$  = 19V, VCC = 5V, L = 220nH, unless otherwise specified.

## **Typical Performance Characteristics** (Continued)

#### **Application Information**

AOZ5049QI-02 is a fully integrated power module designed to work over an input voltage range of 4.5V to 25V with a separate 5V supply for gate drive and internal control circuits. A number of features make AOZ5049QI-02 a highly versatile power module. The MOSFETs are individually optimized on either HS or LS switches in a low duty cycle synchronous buck converter. A high current driver is also included in the package which minimizes the gate drive loop and results in extremely fast switching. The modules are fully compatible with Intel DrMOS specification IMVP8 in form fit and function.

#### **Powering the Module and the Gate Drives**

An external supply VCC of 5V is required for driving the MOSFETs. The MOSFETs are designed with low gate thresholds so that lower drive voltage can be used to reduce the switching and drive losses without compromising switching speed. The integrated gate driver is capable of supplying large peak currents into the Low Side MOSFET's input capacitance. A ceramic bypass capacitor of  $1\mu$ F or higher is recommended from VCC to PGND. For effective filtering it is strongly recommended to directly connect this capacitor to PGND (pin 21).

The Boot Strapped supply for driving the High Side MOSFET is generated by connecting a small capacitor between BOOT pin and the switching node VSWH. It is recommended that this capacitor Cboot be connected as close as possible to the device across pins 2 and 5. A boot diode is integrated into the package. A resistor in series with Cboot can be optionally used by designers to slow down the turn on speed of the high side MOSFET. Typical values between  $1\Omega$  to  $5\Omega$  is a compromise between the need to keep both the switching time and VSWH node spikes as low as possible.

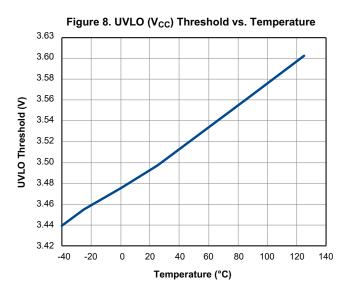

#### **Undervoltage Lockout**

In a UVLO event, both GH and GL outputs are actively held low until adequate gate supply becomes available. The under-voltage lockout is set to 3.4V with a 500mV hysteresis. The AOZ5049QI-02 must be powered up before the PWM input is applied.

Since the PWM control signals are provided typically from an external controller or a digital processor, extra care must be taken during start up. It should be ensured that PWM signal goes through a proper soft start sequence to minimize in-rush current through the converter during start up. Powering the module with a full duty cycle PWM signal may lead to a number of undesirable consequences as explained below. In general it should be noted that AOZ5049QI-02 is a combination of two MOSFETs with an IMVP8 compliant driver, all of which are optimized for switching at the highest efficiency. Other

than UVLO and thermal protection, it does not have any monitoring or protection functions built in. The PWM controller should be designed in to perform these functions under all possible operating and transient conditions.

#### **Input Voltage VIN**

AOZ5049QI-02 is rated to operate over a wide input range of 4.5V to 25V. As with any other synchronous buck converter, large pulse currents at high frequency and extremely high dI/dt rates will be drawn by the module during normal operation. It is strongly recommended to bypass the input supply very closely to package leads with X7R or X5R quality surface mount ceramic capacitors.

The high side MOSFET in AOZ5049QI-02 is optimized for fast switching with low duty ratios. It has ultra low gate charges which have been achieved as a trade off with higher RDS(ON) value. When the module is operated at low VIN the duty ratio will be higher and conduction losses in the HS FET will also be correspondingly higher. This will be compensated to some extent by reduced switching losses. The total power loss in the module may appear to be low even though in reality the HS MOSFET losses may be disproportionately high. Since the two MOSFETs have their own exposed pads and PCB copper areas for heat dissipation, the HS MOSFET may be much hotter than the LS MOSFET. It is recommended that worst case junction temperature be measured and ensured to be within safe limits when the module is operated with high duty ratios.

#### **PWM Input**

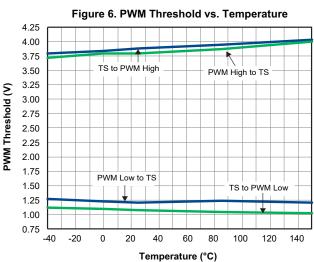

AOZ5049QI-02 is offered to be interfaced with 5V (TTL) PWM logic. Refer to Figure 1 for timing and propagation delays diagram between PWM input and the MOSFET Gate drives.

The PWM is also a tri-state compatible input. When the input is high impedance or unconnected both the gate drives will turn off and the gates are held active low. The PWM Threshold Table in Table 1 lists the thresholds for high and low level transitions as well as tri-state operation window. As shown in Figure 2, there is a hold off delay between the corresponding PWM tri-state signal and the output gate drive being pulled low. This delay is typically 175ns and intended to prevent spurious triggering caused by tri-state mode entrance

Table 1. PWM Input and Tri-State Thresholds

| $Thresholds \to$ | V <sub>PWMH</sub> | V <sub>PWML</sub> | V <sub>TRIH</sub> | V <sub>TRIL</sub> |

|------------------|-------------------|-------------------|-------------------|-------------------|

| AOZ5049QI-02     | 4.1 V             | 0.7 V             | 1.1 V             | 3.9 V             |

Note: See Figure 2 for propagation delays and tri-state window.

#### **Diode Mode Emulation of Low Side MOSFET (FCCM)**

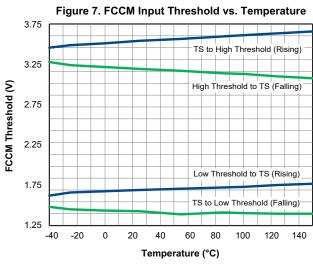

AOZ5049QI-02 can be operated in the diode emulation or skip mode using the FCCM pin. This is useful if the converter has to operate in asynchronous mode during start up, light load or under pre bias conditions. If FCCM is taken high, the controller will use the PWM signal as reference and generate both the high and low side complementary gate drive outputs with minimal antioverlap delays necessary to avoid cross conduction. When the pin is taken low the HS MOSFET drive is not affected but diode emulation mode is activated for the LS MOSFET. See Table 2 for all possible logic inputs and corresponding output drive conditions. A high impedance state at the FCCM pin shuts down the AOZ5049QI-02. The FCCM Threshold Table in Table 3 lists the thresholds for high and low level transitions as well as tri- state threshold window. The FCCM / PWM Timing diagram in Figure 3 illustrates the sequential timing involved when the PWM pin is left at a high impedance state by the master controller. During a shutdown event (FCCM entering Tri-State), the PWM will be actively pulled low by an internal sink circuit ensuring that GH is asserted Low as well as asserting GL low since the I.C. is in shutdown mode. Nevertheless, the ultimate goal is to ensure that the GH and GL are held at low states.

**Table 2. Control Logic Truth Table**

| FCCM      | PWM                            | GH | GL |

|-----------|--------------------------------|----|----|

| L         | L                              | L  | L  |

| L         | Н                              | Н  | L  |

| Н         | H L L                          |    | Н  |

| Н         | Н                              | Н  | L  |

| L         | Tri-State                      | L  | L  |

| Н         | Tri-State                      | L  | L  |

| Tri-State | Pulled Low if<br>Left Floating | L  | L  |

Table 3. FCCM Input and Tri-State Thresholds

| $Thresholds \to$ | V <sub>PWMH</sub> | V <sub>PWML</sub> | V <sub>TRIH</sub> | $V_{TRIL}$ |  |

|------------------|-------------------|-------------------|-------------------|------------|--|

| AOZ5049QI-02     | 3.8 V             | 1.2 V             | 1.4 V             | 3.4 V      |  |

Note: Diode emulation mode is activated when FCCM pin is held low.

#### **Gate Drives**

AOZ5049QI-02 has an internal high current, high speed driver that generates the floating gate drive for the HS MOSFET and a complementary drive for the LS MOSFET. Propagation delays between transitions of the PWM waveform and corresponding gate drives are kept to the minimum. An internal shoot through protection scheme ensures that neither MOSFET turns on while the other one is still conducting, thereby preventing shoot through condition of the input current. When the PWM signal makes a transition from H to L or L to H, the corresponding gate drive GH or GL begins to turn off. The adaptive timing circuit monitors the falling edge of the gate voltage and when the level goes below 1V, the complementary gate driver is turned on. The dead time between the two switches is minimized, at the same time preventing cross conduction across the input bus. The adaptive circuit also monitors the switching node VSWH and ensures that transition from one MOSFET to another always takes place without cross conduction, even under transient and abnormal conditions of operation.

The gate pins GH and GL are brought out on pins 4 and 19 respectively. However these connections are not made directly to MOSFET gate pads and their voltage measurement may not reflect the actual gate voltage applied inside the package. The gate connections are primarily for functional tests during manufacturing and no connections should be made to them in the application.

#### **PCB Layout Guidelines**

AOZ5049QI-02 is a high current module rated for operation up to 2MHz. This requires extremely fast switching speeds to keep the switching losses and device temperatures within limits. Having a robust gate driver integrated in the package eliminates driver-to-MOSFET gate pad parasitics of the package or PCB.

While excellent switching speeds are achieved, correspondingly high levels of dV/dt and di/dt will be observed throughout the power train which requires careful attention to PCB layout to minimize voltage spikes and other transients. As with any synchronous buck converter layout, the critical requirement is to minimize the area of the primary switching current loop, formed by the HS MOSFET, LS MOSFET and the input bypass capacitor Cin. The PCB design is somewhat simplified because of the optimized pin out in AOZ5049QI-02. The bulk of VIN and PGND pins are located adjacent to each other and the input bypass capacitors should be placed as close as possible to these pins. The area of the secondary switching loop, formed by LS MOSFET, output inductor and output capacitor Cout is the next critical parameter, this requires second layer or "Inner 1" should always be an uninterrupted GND plane with sufficient GND vias placed as close as possible to by-pass capacitors GND pads.

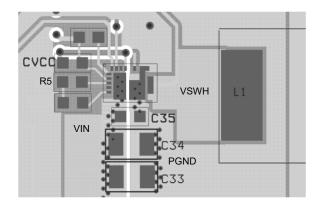

Figure 11. Top Layer of PCB Layout (VIN, VSWH and PGND Copper Planes)

As shown in Figure 11, the top most layer of the PCB should comprise of uninterrupted copper flooding for the primary AC current loop which runs along the VIN copper plane originating from the bypass capacitors C33, C34 and C35 which are mounted to a large PGND copper plane, also on the top most layer of the PCB. These copper planes also serve as heat dissipating elements as heat simply flows down to the VIN exposed pad and onto the top layer VIN copper plane which fans out to a wider area moving away from the 3.5x5 QFN package. Adding vias will only help transfer heat to

cooler regions of the PCB board through the other 3 layers (if 4 layer PCB is used) beneath but serve no purpose to AC activity as all the AC current sees the lowest impedance on the top layer only.

Due to the optimized bonding technique used on the AOZ5049QI-02 internal package, the VIN input capacitors are optimally placed for AC current activities on both the primary and complimentary current loops. The return path of the current during the complimentary period flows through a non interrupted PGND copper plane that is symmetrically proportional to the VIN copper plane.

Due to the PGND exposed pad, heat is optimally dissipated simply by flowing down through the vertically structured lower MOSFET, through the exposed PGND pad and down to the PCB top layer PGND copper plane that also fans outward, moving away from the package.

As the primary and secondary (complimentary) AC current loops move through VIN to VSWH and through PGND to VSWH, large positive and negative voltage spikes appear at the VSWH terminal which are caused by the large internal di/dts produced through the in package parastics. To minimize the effects of this interference, the VSWH terminal at which the main inductor L1 is mounted to, is sized just so the inductor can physically fit. The goal is to employ the least amount of copper area for this VSWH terminal just enough so the inductor can be securely mounted.

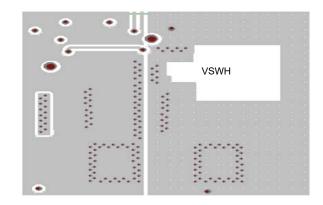

To minimize the effects of switching noise coupling to the rest of the sensitive areas of the PCB, the area directly underneath the designated VSWH copper plane on the top layer is voided and the shape of this void is replicated descending down through the rest of the layers as shown on Figure 12 which is the bottom layer of the PCB as an example.

Figure 12. Bottom Layer PCB Layout (VSWH Copper Plane Voided on Descending Layers)

## Adding Vias Through Exposed Pads Landing Pattern

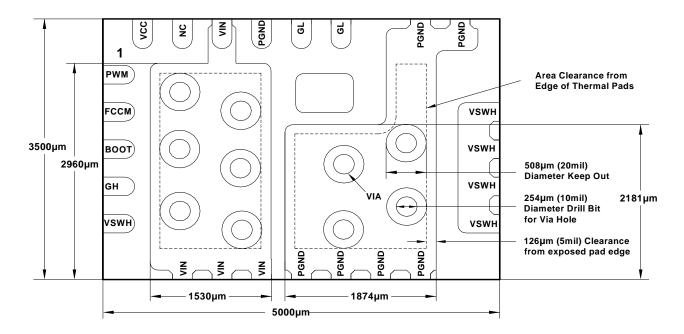

The AOZ5049QI-02 can be operated at a switching frequency of up to 2MHz. This implies that the inherent capacitive parameters of the HS and LS MOSFETs need to be charged and discharge on each and every cycle. Due to the back and forth conduction of these AC currents flowing in and out of the input capacitors, the exposed pads (VIN and PGND) would tend to heat up, hence requiring thermal venting. Positioning vias through the landing pattern of the VIN and PGND thermal pads will help quickly facilitate the thermal build up and spread the heat much more quickly towards the surrounding copper layers descending from the top layer.

The exposed pads dimensional footprint of the 3.5x5 QFN package is shown on Figure 13. For optimal thermal relief, it is recommended to fill the PGND and VIN exposed landing pattern with 10mil diameter vias. 10mil via diameter is a commonly used as it is optimally cost effective based on the tooling bit used in manufacturing. Each via is associated with a 20mil diameter keep out. Maintain a 5mil clearance (127µm) around the inside edge of each exposed pad in an event of solder overflow, potentially shorting with the adjacent expose thermal pad.

Figure 13. Exposed Pad Land Pattern and Recommended Via Placements

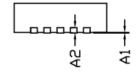

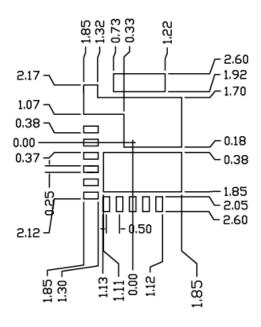

## Package Dimensions, QFN3.5x5\_24L EP2\_S

TOP VIEW

SIDE VIEW

**BOTTOM VIEW**

SIDE VIEW

#### RECOMMENDED LAND PATTERN

| 0.44001.0 | DIM           | ENSION IN | MM   | DIMEN | DIMENSION IN INCHES |       |  |  |

|-----------|---------------|-----------|------|-------|---------------------|-------|--|--|

| SYMBOLS   | MIN           | NOM       | MAX  | MIN   | MAX                 |       |  |  |

| Α         | 1.00          | 1.10      | 1.20 | 0.039 | 0.043               | 0.047 |  |  |

| A1        | 0.00          | -         | 0.05 | 0.000 | -                   | 0.002 |  |  |

| A2        |               | 0.2REF    |      |       | 0.008REF            |       |  |  |

| E         | 4.90          | 5.00      | 5.10 | 0.193 | 0.197               | 0.201 |  |  |

| E1        | 1.66          | 1.71      | 1.76 | 0.065 | 0.067               | 0.069 |  |  |

| E2        | 1.27          | 1.32      | 1.37 | 0.050 | 0.052               | 0.054 |  |  |

| E3        | 0.25          | 0.30      | 0.35 | 0.010 | 0.012               | 0.014 |  |  |

| E4        | 0.38          | 0.43      | 0.48 | 0.015 | 0.017               | 0.019 |  |  |

| D         | 3.40          | 3.50      | 3.60 | 0.134 | 0.138               | 0.142 |  |  |

| D1        | 1.70          | 1.75      | 1.80 | 0.067 | 0.069               | 0.071 |  |  |

| D2        | 2 2.53 2      |           | 2.63 | 0.100 | 0.102               | 0.104 |  |  |

| D3        | 0.40          | 0.45      | 0.50 | 0.016 | 0.018               | 0.020 |  |  |

| L         | 0.35          | 0.40      | 0.45 | 0.014 | 0.016               | 0.018 |  |  |

| L1        | 0.48          | 0.53      | 0.58 | 0.019 | 0.021               | 0.023 |  |  |

| L2        | 1.70 1.75 1.8 |           | 1.80 | 0.067 | 0.069               | 0.071 |  |  |

| L3        | 0.18          | 0.23      | 0.28 | 0.007 | 0.009               | 0.011 |  |  |

| L4        | 0.32          | 0.37      | 0.42 | 0.013 | 0.015               | 0.017 |  |  |

| L5        | 0.33          | 0.38      | 0.43 | 0.013 | 0.015               | 0.017 |  |  |

| L6        | 0.25          | 0.30      | 0.35 | 0.010 | 0.012               | 0.014 |  |  |

| L7        | 0.53          | 0.58      | 0.63 | 0.021 | 0.023               | 0.025 |  |  |

| L8        | 0.72          | 0.77      | 0.82 | 0.028 | 0.030               | 0.032 |  |  |

| K1        | 1.08          | 1.13      | 1.18 | 0.042 | 0.044               | 0.046 |  |  |

| K2        | 0.33          | 0.38      | 0.43 | 0.013 | 0.015               | 0.017 |  |  |

| K3        | 0.58          | 0.63      | 0.68 | 0.023 | 0.025               | 0.027 |  |  |

| K4        | 0.75          | 0.80      | 0.85 | 0.030 | 0.031               | 0.033 |  |  |

| b         | 0.20          | 0.25      | 0.30 | 0.008 | 0.010               | 0.012 |  |  |

| е         |               | 0.50BSC   |      |       | 0.02BSC             |       |  |  |

UNIT: mm

NOTE CONTROLLING DIMENSION IS MILLIMETER. CONVERTED INCH DIMENSIONS ARE NOT NECESSARILY EXACT.

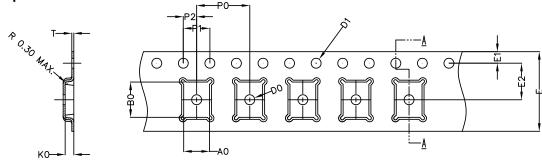

## Tape and Reel Dimensions, QFN\_3.5x5\_24L\_EPS\_2

## **Carrier Tape**

FEEDING DIRECTION

UNIT: MM

| PACKAGE             | AO            | В0            | КО            | DO           | D1                    | Е              | E1            | E2            | P0            | P1            | P2            | Т             |

|---------------------|---------------|---------------|---------------|--------------|-----------------------|----------------|---------------|---------------|---------------|---------------|---------------|---------------|

| QFN3.5x5<br>(12 mm) | 3.89<br>±0.10 | 5.31<br>±0.10 | 1.30<br>±0.10 | 1.50<br>MIN. | 1.50<br>+0.10<br>0.00 | 12.00<br>±0.30 | 1.75<br>±0.10 | 5.50<br>±0.05 | 8.00<br>±0.10 | 4.00<br>±0.10 | 2.00<br>±0.05 | 0.30<br>±0.05 |

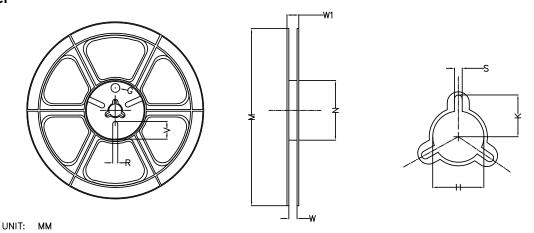

#### Reel

| TAPE SIZE | REEL SIZE | М                | N               | W                       | W1                      | Н               | S         | К | G | R | ٧ |

|-----------|-----------|------------------|-----------------|-------------------------|-------------------------|-----------------|-----------|---|---|---|---|

| 12 mm     | ø330      | ø330.00<br>±2.00 | ø101.6<br>±2.00 | 12.40<br>+2.00<br>-0.00 | 12.40<br>+3.00<br>-0.20 | ø13.20<br>±0.30 | 1.70-2.60 |   |   |   |   |

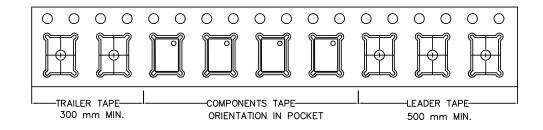

#### **Leader / Trailer & Orientation**

Unit Per Reel: 3000pcs

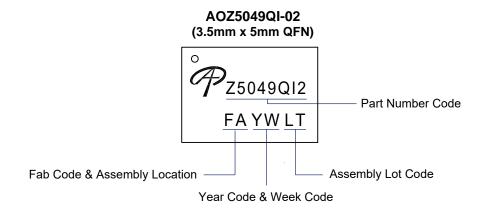

#### **Part Marking**

#### **LEGAL DISCLAIMER**

Applications or uses as critical components in life support devices or systems are not authorized. AOS does not assume any liability arising out of such applications or uses of its products. AOS reserves the right to make changes to product specifications without notice. It is the responsibility of the customer to evaluate suitability of the product for their intended application. Customer shall comply with applicable legal requirements, including all applicable export control rules, regulations and limitations.

AOS' products are provided subject to AOS' terms and conditions of sale which are set forth at: <a href="http://www.aosmd.com/terms">http://www.aosmd.com/terms</a> and conditions of sale

#### LIFE SUPPORT POLICY

ALPHA AND OMEGA SEMICONDUCTOR PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS.

As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Rev. 1.0 July 2017 **www.aosmd.com** Page 15 of 15

## 单击下面可查看定价,库存,交付和生命周期等信息

## >>AOS(万代)