# **Over-Voltage Protection Load Switch with Surge Protection**

#### **FEATURES**

- Surge protection

- IEC 61000-4-5: > 100V

- Integrated low R<sub>dson</sub> nFET switch: typical 24mΩ

- 5A continuous current capability

- Default Over-Voltage Protection (OVP) threshold

- > AW32705: 6.8V

- > AW32710: 10.5V

- OVP threshold adjustable range: 4V to 20V

- Input system ESD protection

- IEC 61000-4-2 Contact discharge: ±8kV

- IEC 61000-4-2 Air gap discharge: ±15kV

- Input maximum voltage rating: 35V<sub>DC</sub>

- Fast turn-off response: typical 50ns

- Over-Temperature Protection (OTP)

**TYPICAL APPLICATION CIRCUIT**

- Under-Voltage Lockout (UVLO)

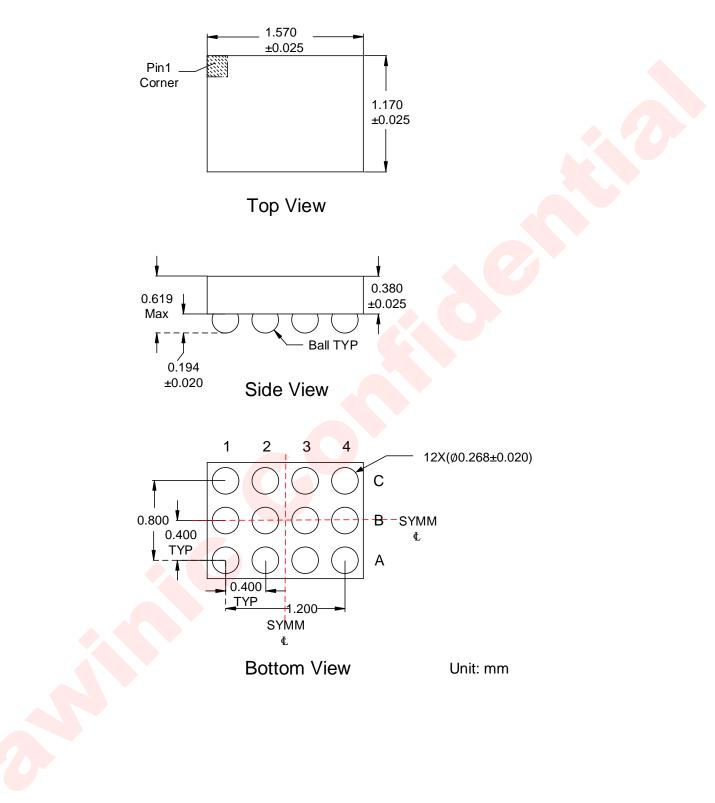

- WLCSP 1.17×1.57-12B package

## **APPLICATIONS**

- Smartphones

- Tablets

- Charging Ports

## **GENERAL DESCRIPTION**

The AW327XX family OVP load switch features surge protection, an internal clamp circuit protects the device from surge voltages up to 100V.

The AW327XX features an ultra-low  $24m\Omega$  (typ.) R<sub>dson</sub> nFET load switch. When input voltage exceeds the OVP threshold, the switch is turned off very fast to prevent damage to the protected downstream devices. The IN pin is capable of withstanding fault voltages up to  $35V_{DC}$ .

The default OVP threshold is 6.8V (AW32705) and 10.5V (AW32710), the OVP threshold can be adjusted from 4V to 20V through external OVLO pin.

The device features an open-drain output  $\overline{\text{ACOK}}$ , when  $V_{\text{IN}_{UVLO}} < V_{\text{IN}} < V_{\text{IN}_{OVLO}}$  and the switch is on,  $\overline{\text{ACOK}}$  will be driven low to indicate a good power input, otherwise it is high impedance.

This device features over-temperature protection that prevents itself from thermal damaging.

The AW327XX is available in a RoHS compliant WLCSP 1.17×1.57-12B package.

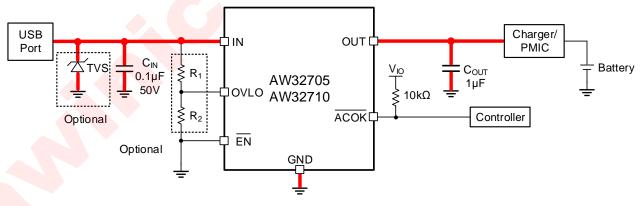

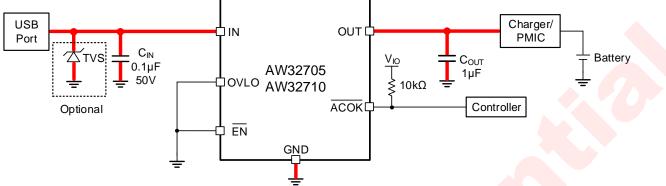

#### Figure 1 AW327XX typical application circuit

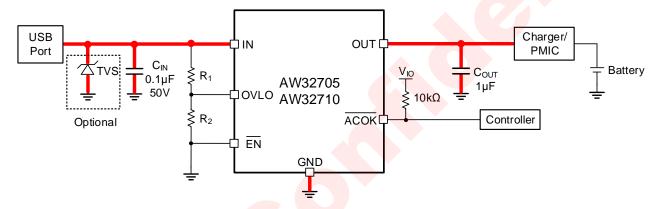

$R_1$  and  $R_2$  are used for OVP threshold adjustment, to use default OVP threshold, connect OVLO to ground.

All the trademarks mentioned in the document are the property of their owners.

### **DEVICE COMPARISON TABLE**

| Device  |                        |       | V <sub>IN_OVLO</sub> (V) |       |                                         |  |

|---------|------------------------|-------|--------------------------|-------|-----------------------------------------|--|

| Device  | Condition              | Min.  | Тур.                     | Max.  | V <sub>IN_OVLO</sub><br>hysteresis (mV) |  |

| AW32705 | V <sub>IN</sub> rising | 6.66  | 6.80                     | 6.94  | 140                                     |  |

| AW32710 | V <sub>IN</sub> rising | 10.29 | 10.50                    | 10.71 | 210                                     |  |

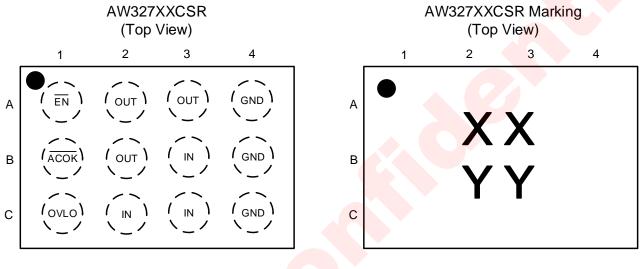

## **PIN CONFIGURATION AND TOP MARK**

XX – LT: AW32705CSR, TX: AW32710CSR YY – Production Tracing Code

#### Figure 2 Pin Configuration and Top Mark

#### **PIN DEFINITION**

| Pin        | Name | Description                             |

|------------|------|-----------------------------------------|

| A1         | ĒN   | Enable pin, active low                  |

| B1         | ACOK | Power good flag, active-low, open-drain |

| C1         | OVLO | OVP threshold adjustment pin            |

| C2, C3, B3 | IN   | Switch input and device power supply    |

| A2, A3, B2 | OUT  | Switch output                           |

| A4, B4, C4 | GND  | Device ground                           |

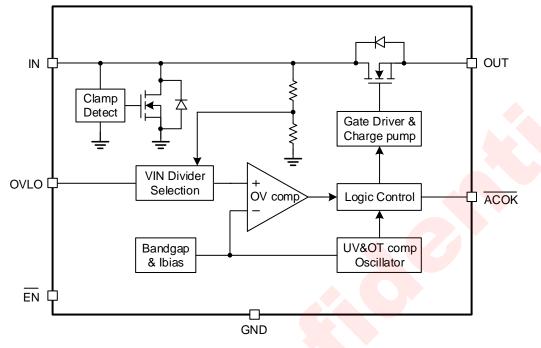

#### FUNCTIONAL BLOCK DIAGRAM

### **TYPICAL APPLICATION CIRCUITS**

Figure 4 AW327XX typical application circuit(using default OVP threshold)

Figure 5 AW327XX typical application circuit(using external resistors set OVP threshold)

#### Notice for Typical Application Circuits:

- 1. If VBUS is required to pass surge voltage greater than 100V, external TVS is needed, the maximum clamping voltage of the TVS should be below 37V.

- 2. When the default OVP threshold is used, connect OVLO pin to GND directly or through a 0Ω resistor. OVLO pin cannot be left floating.

- 3. If R<sub>1</sub> and R<sub>2</sub> are used to adjust the OVP threshold, it is better to use 1% precision resistors to improve the OVP threshold precision.

- 4. If ACOK is not used, it can be left floating, or short to GND.

- 5.  $C_{IN} = 0.1 \mu F$  is recommended for typical application, larger  $C_{IN}$  is also acceptable. The rated voltage of  $C_{IN}$  should be larger than the TVS maximum clamping voltage, if no TVS is applied and only AW327XX is used, the rated voltage of  $C_{IN}$  should be 50V.

- 6.  $C_{OUT} = 1\mu$ F is recommended for typical application, larger  $C_{OUT}$  is also acceptable. The rated voltage of  $C_{OUT}$  should be larger than the OVP threshold. For example, if the OVP threshold is 6.8V, the rated voltage of  $C_{OUT}$  should be 10V or higher.

#### **ORDERING INFORMATION**

| Part Number | Temperature | Package                        | Marking | Moisture<br>Sensitivity<br>Level | Environmental<br>Information | Delivery<br>Form                   |

|-------------|-------------|--------------------------------|---------|----------------------------------|------------------------------|------------------------------------|

| AW32705CSR  | -40°C~85°C  | WLCSP<br>1.17mm×1.57mm-<br>12B | LT      | MSL1                             | ROHS+HF                      | 3000<br>units/<br>Tape and<br>Reel |

| AW32710CSR  | -40°C~85°C  | WLCSP<br>1.17mm×1.57mm-<br>12B | тх      | MSL1                             | ROHS+HF                      | 3000<br>units/<br>Tape and<br>Reel |

## ABSOLUTE MAXIMUM RATINGS (NOTE 1)

| Symbol              | Parameter                                                  | Condition                                                     | Min. | Max.                    | Unit |

|---------------------|------------------------------------------------------------|---------------------------------------------------------------|------|-------------------------|------|

| VIN                 | Input voltage                                              |                                                               | -0.3 | 35                      | V    |

| Vout                | Output voltage                                             |                                                               | -0.3 | See <sup>(NOTE 2)</sup> | V    |

| Vovlo               | OVLO voltage                                               |                                                               | -0.3 | 6                       | V    |

| V <sub>ACOK</sub>   | ACOK voltage                                               |                                                               | -0.3 | 6                       | V    |

| $V_{\overline{EN}}$ | EN voltage                                                 |                                                               | -0.3 | 6                       | V    |

| Isw                 | Continuous current of switch<br>IN-OUT <sup>(NOTE 3)</sup> | Continuous current on IN and OUT pin                          |      | 5                       | A    |

| Іреак               | Peak current                                               | Peak input and output current on IN and OUT pin(10ms)         |      | 8                       | А    |

| IDIODE              | Continuous diode current                                   | Continuous forward current through the nFET body diode        |      | 1.5                     | A    |

| TA                  | Ambient temperature                                        |                                                               | -40  | 85                      | °C   |

| TJ                  | Junction temperature                                       |                                                               | -40  | 150                     | °C   |

| Тsтg                | Storage temperature                                        |                                                               | -65  | 150                     | °C   |

| TLEAD               | Soldering temperature                                      | At leads, 10 seconds                                          |      | 260                     | °C   |

| Surge               | Input surge protection                                     | IEC61000-4-5 test with $2\Omega$ equivalent series resistance | 100  |                         | V    |

NOTE1: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

NOTE2: 29V or  $V_{IN}$ +0.3V, whichever is smaller.

NOTE3: Limited by thermal design.

## THERMAL INFORMATION

| Symbol | Parameter                                            | Condition   | Value | Unit |

|--------|------------------------------------------------------|-------------|-------|------|

| Reja   | Thermal resistance from junction to ambient (NOTE 1) | In free air | 90    | °C/W |

NOTE1: Thermal resistance from junction to ambient is highly dependent on PCB layout.

## **ESD AND LATCH-UP RATINGS**

| Symbol                | Parameter                  | Condition              | Value | Unit |

|-----------------------|----------------------------|------------------------|-------|------|

|                       | IEC61000-4-2 system ESD on | Contact discharge      | ±8    | kV   |

|                       | IN pin                     | Air gap discharge      | ±15   | kV   |

| $V_{\text{ESD}}$      | Human Body Model           | ANSI/ESDA/JEDEC JS-001 | ±2    | kV   |

|                       | Charged Device Model       | JESD22-C101            | ±1.5  | kV   |

|                       | Machine Model              | JESD22-A115C           | ±200  | V    |

| I <sub>Latch-up</sub> | Latch-up                   | JEDEC78                | ±200  | mA   |

## **RECOMMENDED OPERATING CONDITIONS**

| Symbol          | Parameter               | Min. | Тур. | Max. | Unit |

|-----------------|-------------------------|------|------|------|------|

| V <sub>IN</sub> | Input DC voltage        | 3    |      | 30   | V    |

| CIN             | Input capacitance       |      | 0.1  |      | μF   |

| Cout            | Output load capacitance |      | 1    |      | μF   |

## **ELECTRICAL CHARACTERISTICS**

$T_A$  = -40°C to 85°C unless otherwise noted. Typical values are guaranteed for  $V_{IN}$  = 5V,  $C_{IN}$  = 0.1µF,  $I_{IN}$ ≤ 5A and  $T_A$  = 25°C.

| Symbol                        | Description                                 | Test Conditions                       |                               | Min.  | Тур.  | Max.  | Unit |

|-------------------------------|---------------------------------------------|---------------------------------------|-------------------------------|-------|-------|-------|------|

| $V_{\text{IN\_CLAMP}}$        | Input clamp voltage                         | I <sub>IN</sub> = 10mA                |                               |       | 36.3  |       | V    |

| Rdson                         | Switch on resistance                        | VIN = 5V, IOUT                        | r = 1A, T <sub>A</sub> = 25°C |       | 24    | 35    | mΩ   |

| lq                            | Input quiescent current                     | VIN = 5V, VOV                         | /LO=0V,IOUT = 0A              |       | 70    | 140   | μA   |

| Iin_ovlo                      | Input current at over-<br>voltage condition | V <sub>IN</sub> = 5V, V <sub>OV</sub> | /LO=3V,Vout = 0V              |       | 67    | 130   | μA   |

| Vovlo_th                      | OVLO set threshold                          |                                       |                               | 1.16  | 1.20  | 1.24  | V    |

| $V_{\text{OVLO}\_\text{RNG}}$ | OVP threshold adjustable range              |                                       |                               | 4     |       | 20    | v    |

|                               | External OVLO select                        | OVLO rising                           |                               | 0.19  | 0.26  | 0.33  | V    |

| Vovlo_sel                     | threshold                                   | Hysteresis                            | Hysteresis                    |       | 0.06  |       | V    |

| Iovlo                         | OVLO pin leakage<br>current                 | Vovlo=Vovlo                           | тн                            | -0.2  |       | 0.2   | μA   |

| Protection                    |                                             |                                       |                               |       |       |       |      |

|                               |                                             | A14/20705                             | V <sub>IN</sub> rising        | 6.66  | 6.80  | 6.94  |      |

| N/                            |                                             | AW32705                               | Hysteresis                    |       | 0.14  |       |      |

| Vin_ovlo                      | OVP trip level                              | 414/2074.0                            | V <sub>IN</sub> rising        | 10.29 | 10.50 | 10.71 | V    |

|                               |                                             | AW32710                               | Hysteresis                    |       | 0.21  |       |      |

| Valuera                       |                                             | V <sub>IN</sub> rising                |                               |       | 2.9   | 3.0   | v    |

| Vin_uvlo                      | UVLO trip level                             | Hysteresis                            | Hysteresis                    |       | 0.1   |       | V    |

| TSDN                          | Shutdown temperature                        |                                       |                               |       | 150   |       | °C   |

| Tsdn_hys                      | Shutdown temperature hysteresis             |                                       |                               |       | 20    |       | °C   |

| Rdchg                         | Output discharge resistance                 | Vout=7V,Vov                           | LO=3V                         |       | 50    |       | Ω    |

## **ELECTRICAL CHARACTERISTICS (CONTINUED)**

$T_A$  = -40°C to 85°C unless otherwise noted. Typical values are guaranteed for  $V_{IN}$  = 5V,  $C_{IN}$  = 0.1µF,  $I_{IN}$ ≤ 5A and  $T_A$  = 25°C.

| Symbol                 | Description             | Test Conditions                                                                                                                                                     | Min. | Тур. | Max. | Units |

|------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Digital Logi           | cal Interface           |                                                                                                                                                                     |      |      |      |       |

| Vol                    | ACOK output low voltage | Isink=1mA                                                                                                                                                           |      |      | 0.4  | V     |

| I <sub>LEAK_ACOK</sub> | ACOK leakage current    | $V_{IO}$ =5V, $\overline{ACOK}$ de-asserted                                                                                                                         | -0.5 |      | 0.5  | μA    |

| VIH                    | EN input high voltage   |                                                                                                                                                                     | 1.2  |      |      | V     |

| VIL                    | EN input low voltage    |                                                                                                                                                                     |      |      | 0.5  | V     |

| I <sub>LEAK_EN</sub>   | EN leakage current      | $V_{\overline{EN}} = 5V$                                                                                                                                            | 0    |      | 2    | μA    |

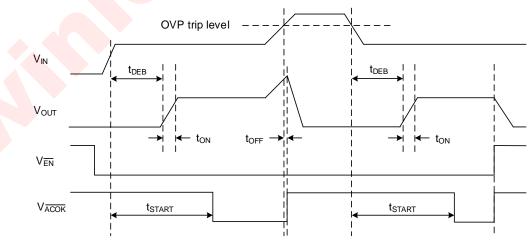

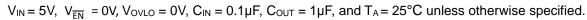

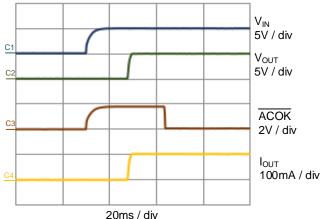

| Timing Cha             | racteristics (Figure 6) |                                                                                                                                                                     |      |      |      |       |

| tdeb                   | Debounce time           | From VIN > VIN_UVLO to 10%                                                                                                                                          |      | 15   |      | ms    |

| tstart                 | Start-up time           | From VIN > VIN_UVLO to ACOK<br>low                                                                                                                                  |      | 30   |      | ms    |

| ton                    | Switch turn-on time     | R <sub>L</sub> = 100Ω, C <sub>L</sub> = 22µF, V <sub>OUT</sub><br>from 10% V <sub>IN</sub> to 90% V <sub>IN</sub>                                                   |      | 2    |      | ms    |

| toff                   | Switch turn-off time    | $\begin{array}{l} C_L = 0 \mu F, \ R_L = 100 \Omega, \ V_{IN} > \\ V_{IN} \ ov_{LO} \ to \ V_{OUT} \ stop \ rising, \\ V_{IN} \ rise \ at \ 10 V/\mu s \end{array}$ |      | 50   |      | ns    |

## **TIMING DIAGRAM**

Figure 6 Timing diagram

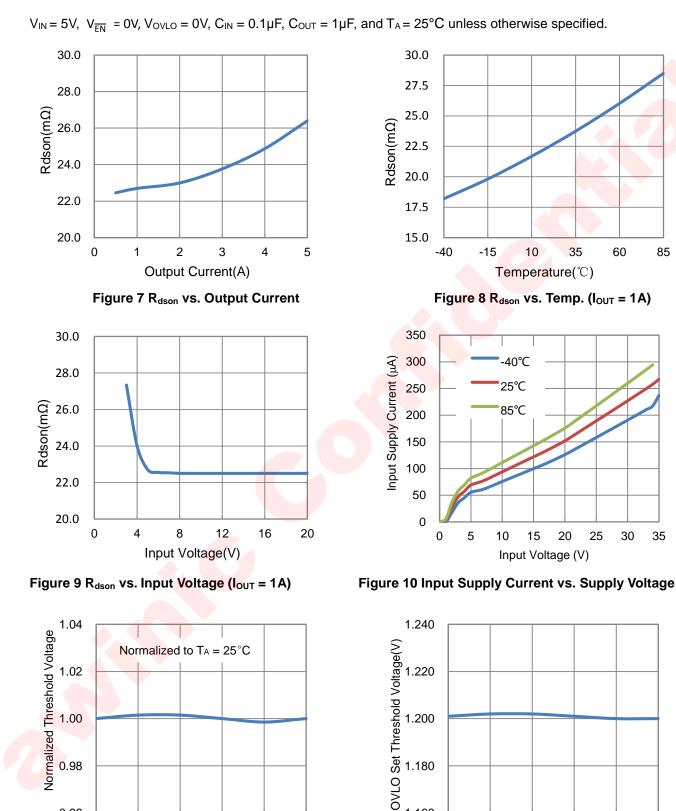

### **TYPICAL CHARACTERISTICS**

0.96 -40 -15 10 35 60 85 Temperature (°C)

www.awinic.com.cn

Figure 11 Normalized Internal OVP Threshold vs. Temp.

Copyright © 2018 SHANGHAI AWINIC TECHNOLOGY CO., LTD

10

Temperature (°C)

Figure 12 OVLO set threshold vs. Temp.

35

60

85

-15

9

1.160

-40

### **TYPICAL CHARACTERISTICS (CONTINUED)**

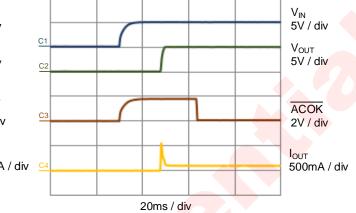

Figure 15 OVP Response (AW32705)

Figure 14 Power-up ( $C_{OUT} = 100 \mu$ F, 100mA load)

#### **DETAILED FUNCTIONAL DESCRIPTION**

#### **Device Operation**

If the AW327XX is enabled and the input voltage is between UVLO and OVP threshold, the internal charge pump begins to work after debounce time, the gate of the nFET switch will be slowly charged high till the switch is fully on.  $\overline{\text{ACOK}}$  will be driven low about 30ms after V<sub>IN</sub> valid, indicating the switch is on with a good power input. If the input voltage exceeds the OVP trip level, the switch will be turned off in about 50ns. If  $\overline{\text{EN}}$  is pulled high, or input voltage falls below UVLO threshold, or over-temperature happens, the switch will also be turned off.

#### **Surge Protection**

The AW327XX integrates a clamp circuit to suppress input surge voltage. For surge voltages between  $V_{IN_OVLO}$  and  $V_{IN_CLAMP}$ , the switch will be turned off but the clamp circuit will not work. For surge voltages greater than  $V_{IN_CLAMP}$ , the internal clamp circuit will detect surge voltage level and discharge the surge energy to ground. The device can suppress surge voltages up to 100V.

#### **Over-Voltage Protection**

If the input voltage exceeds the OVP rising trip level, the switch will be turned off in about 50ns. The switch will remain off until  $V_{IN}$  falls below the OVP falling trip level.

#### **OVP** Threshold Adjustment

If the default OVP threshold is used, OVLO pin must be grounded. If OVLO pin is not grounded, and by connecting external resistor divider to OVLO pin as shown in the typical application circuit, between IN and GND, the OVP threshold can be adjusted as following:

$$V_{\text{IN}_{\text{OVLO}}} = \frac{R_1 + R_2}{R_2} V_{\text{OVLO}_{\text{TH}}}$$

For example, if we select  $R_1 = 1M\Omega$  and  $R_2 = 100k\Omega$ , then the new OVP threshold calculated from the above formula is 13.2V. The OVP threshold adjustment range is from 4V to 20V. When the OVLO pin voltage  $V_{OVLO}$  exceeds  $V_{OVLO}_{SEL}$  (0.26V typical),  $V_{OVLO}$  is compared with the reference voltage  $V_{OVLO}_{TH}$  (1.2V typical) to judge whether input supply is over-voltage.

#### **ACOK** Output

The device features an open-drain output  $\overline{\text{ACOK}}$ , it should be connected to the system I/O rail through a pullup resistor. If the device is enabled and  $V_{IN_UVLO} < V_{IN} < V_{IN_OVLO}$ ,  $\overline{\text{ACOK}}$  will be driven low indicating the switch is on with a good power input. If OVP, UVLO, or OT occurs, or  $\overline{\text{EN}}$  is pulled high, the switch will be turned off and  $\overline{\text{ACOK}}$  will be pulled high.

#### USB On-The-Go (OTG) Operation

If  $V_{IN} = 0V$  and OUT is supplied by OTG voltage, the body diode of the load switch conducts current from OUT to IN and the voltage drop from OUT to IN is approximately 0.7V. When  $V_{IN} > V_{IN_UVLO}$ , internal charge pump begins to open the load switch after debounce time (about 15ms). After switch is fully on, current is supplied through switch channel and the voltage drop from OUT to IN is minimum.

### PCB LAYOUT CONSIDERATION

To obtain the optimal performance of AW327XX, PCB layout should be considered carefully. Here are some guidelines:

1. All the peripherals should be placed as close to the device as possible. Place the input capacitor  $C_{IN}$  on the top layer (same layer as the AW327XX) and close to IN pin, and place the output capacitor  $C_{OUT}$  on the top layer (same layer as the AW327XX) and close to OUT pin.

2. If external TVS is used, IN pin routing passes through the external TVS firstly, and then connect AW 327XX.

3. Red bold paths on figure 4 and 5 are power lines that will flow large current, please route them on PCB as straight, wide and short as possible.

4. The path from device ground pins to the system ground plane must be as short as possible.

5. If R1 and R2 are used, route OVLO line on PCB as short as possible to reduce parasitic capacitance.

6. The power trace from USB connector to AW327XX may suffer from ESD event, keep other traces away from it to minimize possible EMI and ESD coupling.

7. Use rounded corners on the power trace from USB connector to AW327XX to decrease EMI coupling.

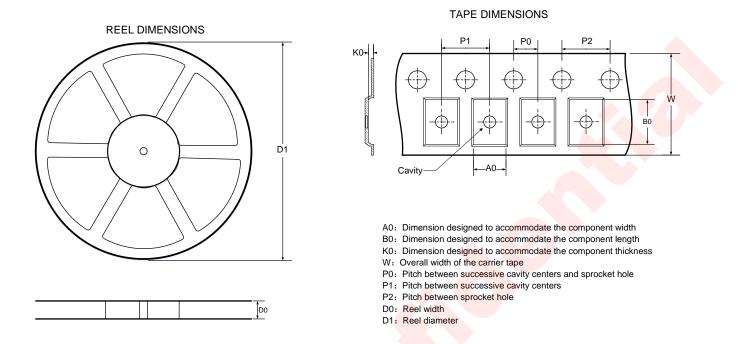

### **TAPE AND REEL INFORMATION**

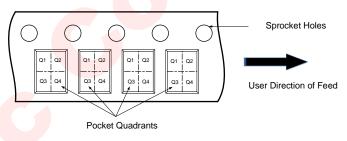

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### All dimensions are nominal

| D1     | D0   | A0   | B0   | K0   | P0   | P1   | P2   | W    | Pin1     |

|--------|------|------|------|------|------|------|------|------|----------|

| (mm)   | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) | Quadrant |

| 179.00 | 9.00 | 1.29 | 1.69 | 0.73 | 2.00 | 4.00 | 4.00 | 8.00 | Q2       |

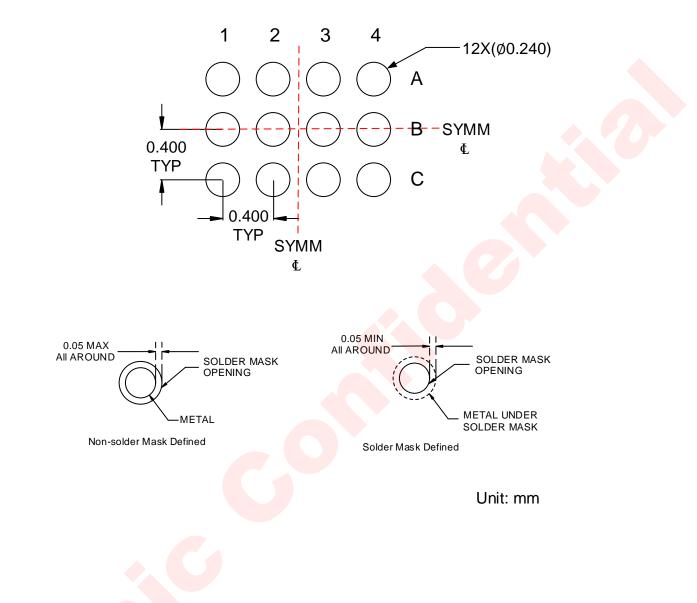

#### **PACKAGE DESCRIPTION**

#### LAND PATTERN DATA

| awinic | 上海艾为电子技术股份有限公司                                       |

|--------|------------------------------------------------------|

|        | 上海艾为电子技术股份有限公司<br>shanghai awinic technology co.,Itd |

## **REVISION HISTORY**

| Vision | Date         | Change Record           |

|--------|--------------|-------------------------|

| V1.0   | October 2018 | Datasheet V1.0 Released |

### DISCLAIMER

Information in this document is believed to be accurate and reliable. However, Shanghai AWINIC Technology Co., Ltd (AWINIC Technology) does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

AWINIC Technology reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. Customers shall obtain the latest relevant information before placing orders and shall verify that such information is current and complete. This document supersedes and replaces all information supplied prior to the publication hereof.

AWINIC Technology products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an AWINIC Technology product can reasonably be expected to result in personal injury, death or severe property or environmental damage. AWINIC Technology accepts no liability for inclusion and/or use of AWINIC Technology products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications that are described herein for any of these products are for illustrative purposes only. AWINIC Technology makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

All products are sold subject to the general terms and conditions of commercial sale supplied at the time of order acknowledgement.

Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

Reproduction of AWINIC information in AWINIC data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. AWINIC is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of AWINIC components or services with statements different from or beyond the parameters stated by AWINIC for that component or service voids all express and any implied warranties for the associated AWINIC component or service and is an unfair and deceptive business practice. AWINIC is not responsible or liable for any such statements.

单击下面可查看定价,库存,交付和生命周期等信息

>>AWINIC(艾为)