## 1A 充电 P-MOSFET 的锂离子电池充电器

## 特性

- 输入过压保护

- 输入限流保护

- 输出碰地保护

- 1A 充电 PMOSFET

- 内置专有的 K-CHARGE<sup>TM</sup> 技术,根据芯片温度智能调整输出电流

- 内置过温保护

- ESD 保护: **±8kV**(HBM)

- 纤小的 DFN3×3-10L

## 应用

手机 数码相机

## 概要

AW3210A 是一款高集成度的锂离子电池充电器。 AW3210A 持续检测输入电压,若输入电压超过保护 阈值电压且持续时间超过 100ns,则内部功率 P-MOSFET 关闭,CHRIN 电压拉低。AW3210A 内 置限流保护电路,充电电流会限制在安全的范围内。 AW3210A 内置专有的 K-Charge™ 技术,可根据芯 片温度智能调整输出电流,以保证在充电期间整个充 电系统的安全。

AW3210A 集成了充电 P-MOSFET,可省去手机充电系统中的外部充电 P-MOSFET 和肖特基二极管。AW3210A 具有防电流反灌功能,当 CHRIN 电压降至低于 OUT 电压,充电 P-MOSFET 关闭,防止电流从锂离子电池反灌至 AW3210A。

AW3210A 采用纤小的 DFN3×3-10L 封装, 额定工作 温度范围为-40~85℃。

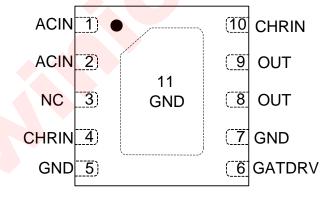

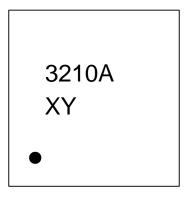

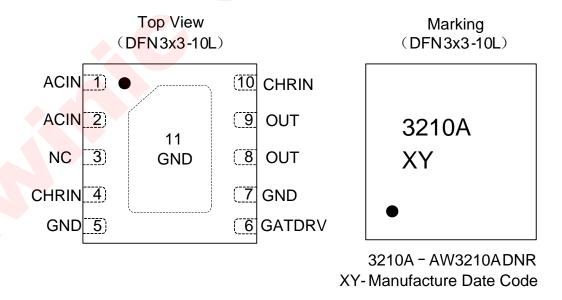

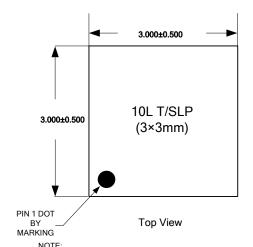

## 引脚分布及标记图

器件俯视图 (DFN3x3-10L封装)

器件标记 (DFN3x3-10L 封装)

3210A - AW3210ADNR

XY- 生产跟踪码

图 1 AW3210A 引脚分布(左)和标记图(右)

手册中提到的全部商标所有权归各自拥有者所有。

## 1A Li-ion Battery Charger Integrated with Protective PMOSFET

#### **FEATURES**

- Input Over-voltage Protection

- Input Current Limit Protection

- Output Short to Ground Protection

- 1A Charging PMOSFET

- Specific K-Charge<sup>™</sup>: Junction Temperature

Based Dynamic Output Current

- Over Temperature Protection

- ESD Protection: ±8kV(HBM)

- DFN3×3-10L Package

#### **APPLICATIONS**

Mobile Phones

Digital Camera

#### **GENERAL DESCRIPTION**

AW3210A is a highly integrated Li-Ion battery charger. AW3210A continuously detects the input voltage, if V<sub>IN</sub> exceeds the threshold voltage and lasts longer than 100ns, the internal power P-MOSFET turned off, CHRIN pulled down. AW3210A Built-in current limiting protection circuit, the charging current is limited to a safe range. AW3210A possesses the specific K-Charge™ technology, the output current can be adjusted smartly according to the chip temperature to ensure safety during the entire charging process.

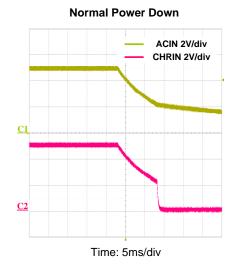

AW3210A integrates the charging P-MOSFET, eliminating the need for external charging P-MOSFET and Schottky Diode among a phone charging system. And the reverse current blocking function has been designed in AW3210A, when the CHRIN voltage drops below the OUT, charging P-MOSFET turned off, preventing current draining from the lithium-ion battery into AW3210A.

AW3210A is available in DFN 3x3-10L package.

## PIN CONFIGURATION AND TOP MARK

Figure 1 Pin configuration and marking

All trademarks are the property of their respective owners.

### **PIN DEFINITION**

| No. | NAME   | DESCRIPTION                                                     |  |

|-----|--------|-----------------------------------------------------------------|--|

| 1   | ACIN   | Charger input valtage, connected to AC adenter or LISP          |  |

| 2   | ACIN   | Charger input voltage, connected to AC adapter or USB.          |  |

| 3   | NC     |                                                                 |  |

| 4   | CHRIN  | Voltage output pin.                                             |  |

| 5   | GND    | Ground.                                                         |  |

| 6   | GATDRV | PMOSFET gate input, connected to PMU drive pin.                 |  |

| 7   | GND    | Ground.                                                         |  |

| 8   | OUT    | Charge current output, connected to battery via a current sense |  |

| 9   | OUT    | resistor.                                                       |  |

| 10  | CHRIN  | Voltage output pin, connected to PMU via resistor.              |  |

| 11  | GND    | Ground.                                                         |  |

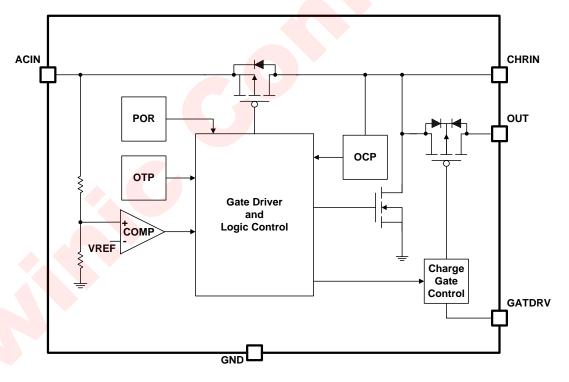

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 2 AW3210A FUNCTIONAL BLOCK DIAGRAM

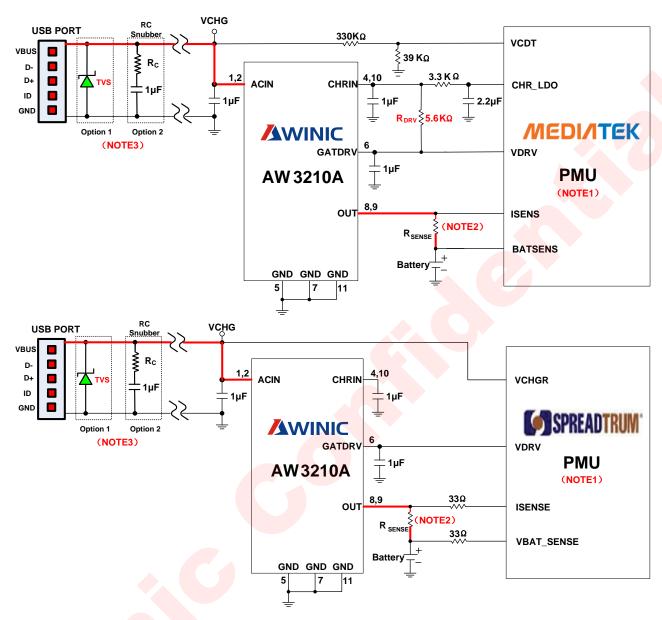

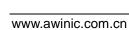

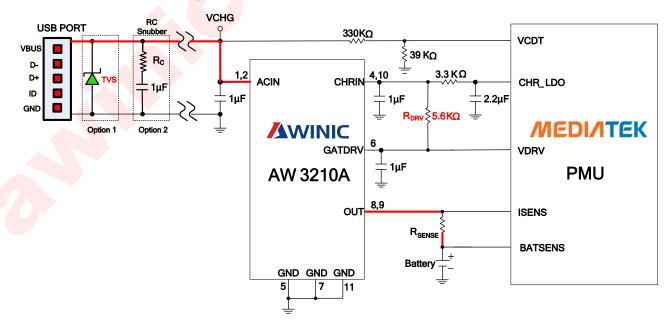

#### TYPICAL APPLICATION CIRCUITS

Figure 3 AW3210A Application Circuits with MTK or SPREADTRUM platform

NOTE1: The application circuits above corresponding to MTK current-driving PMUs and SPREADTRUM voltage-driving PMUs respectively, e.g. MT6320 MT6323 MT6329 and SC8825 SC8810 SC6820 SC6825.

NOTE2: The general default value of  $R_{SENSE}$  is  $200m\Omega$  for MTK and  $360m\Omega$  for SPREADTRUM, but please refer to the platform official documents for the resistor value of a specific PMU. When AICN voltage goes too low due to bad performance of AC adapter or USB cable, a decrease of  $R_{SENSE}$  would be proposed to increase the voltage drop space through AW3210A, enhancing the charging performance. And don't forget to adjust the PMU registers corresponding to  $R_{SENSE}$  at the same time, keeping the charging current unchanged.

NOTE3: Option1&2 are applied to increase the USB port robustness against surge voltage/current. A proposed TVS model is ESD9N5V-2/TR, while the proposed  $R_C$  value in option2 is  $1\Omega$ . For more details about the two options, please refer to the Application Information part below.

NOTE4: The red route in the figures above indicate the large current path for AW3210A application, please pay attention to the path width on PCB board. In general, a factor of 40mil/A between path width and current is suitable. For example, the set current is 1A, then the path width should not less than 40x1=40mil.

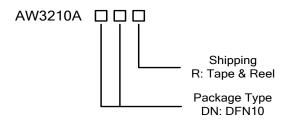

### **ORDERING INFORMATION**

| Part Number | Temperature | Package      | RoHS | Marking | Delivery Form                |

|-------------|-------------|--------------|------|---------|------------------------------|

| AW3210A DNR | -40℃~85℃    | DFN3×3mm-10L | Yes  | 3210A   | 6000 units/<br>Tape and Reel |

# **ABSOLUTE MAXIMUM RATINGS**(NOTE5)

| PARAMETERS                                                            | RANGE                     |  |  |  |

|-----------------------------------------------------------------------|---------------------------|--|--|--|

| ACIN voltage range                                                    | -0.3V to 15V              |  |  |  |

| CHRIN, OUT, GATEDRV voltage range                                     | -0.3V to 7V               |  |  |  |

| Maximum OUT current                                                   | 3A                        |  |  |  |

| Maximum power dissipation @T <sub>A</sub> =2 <mark>5</mark> ℃         | 1.48W                     |  |  |  |

| Junction-to-ambient thermal resistance θ <sub>JA</sub>                | 67.4℃/W                   |  |  |  |

| Operating free-air temp <mark>eratu</mark> re r <mark>ang</mark> e    | -40℃ to 85℃               |  |  |  |

| Maximum Junction temperature T <sub>JMAX</sub>                        | 150℃                      |  |  |  |

| Storage temperature T <sub>STG</sub>                                  | -65℃ to 150℃              |  |  |  |

| Lead Tem <mark>pe</mark> ratu <mark>re (Solde</mark> ring 10 Seconds) | 260℃                      |  |  |  |

| ESD <sup>(NOTE 6)</sup>                                               |                           |  |  |  |

| All pins, HBM (human body model)                                      | ±8kV                      |  |  |  |

| Latch-up                                                              |                           |  |  |  |

| Test Condition: JEDEC STANDARD NO.78B DECEMBER 2008                   | +IT: 450mA<br>-IT: -450mA |  |  |  |

NOTE5: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

NOTE6: The human body model is a 100pF capacitor discharged through a 1.5k $\Omega$  resistor into each pin. Test method: MIL-STD-883G Method 3015.7

### **ELECTRICAL CHARACTERISTICS**

ACIN=5V, VBAT=3.8V,  $T_A$ =25°C for typical values (unless otherwise noted)

|                              | PARAMETER                              | TEST CONDITION                                | MIN | TYP   | MAX | UNIT |  |

|------------------------------|----------------------------------------|-----------------------------------------------|-----|-------|-----|------|--|

| ACIN                         |                                        |                                               |     | 1     | •   |      |  |

| I <sub>ACIN</sub>            | ACIN supply current control            | I <sub>OUT</sub> =0A , I <sub>CHRIN</sub> =0A | 2.1 | 3     | 3.9 | mA   |  |

| V <sub>POR</sub>             | Power on reset voltage                 | ACIN rising from 0 to 3V                      |     | 2.6   | 3   | V    |  |

| V <sub>hys(POR)</sub>        | Power on reset hysteresis              | ACIN falling from 3V to 0                     |     | 300   |     | mV   |  |

| T <sub>BLK</sub>             | Power on reset delay                   |                                               |     | 3     |     | ms   |  |

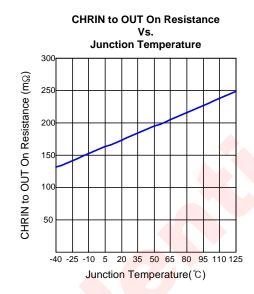

| R <sub>on</sub>              | •                                      |                                               |     |       |     |      |  |

| R <sub>DSON</sub>            | ACIN to OUT                            | I <sub>OUT</sub> =1A, ACIN=5.0V,<br>GATDRV=0V |     | 0.31  |     | Ω    |  |

|                              | CHRIN to OUT                           | I <sub>OUT</sub> =1A,ACIN=5.0V,<br>GATDRV=0V  |     | 0.155 |     | Ω    |  |

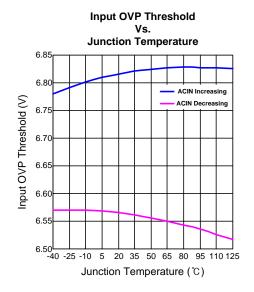

| INPUT OV                     | ERVOLTAGE PROTECTION                   |                                               |     |       |     |      |  |

| V <sub>OVP</sub>             | Input overvoltage threshold            | ACIN risi <mark>ng</mark>                     | 6.5 | 6.8   | 7.1 | V    |  |

| $V_{\text{hys}(\text{OVP})}$ | Input overvoltage hysteresis           |                                               | 250 | 300   | 350 | mV   |  |

| $T_{DGL(OVP)}$               | ACIN OVP deglitch time                 |                                               |     | 100   |     | ns   |  |

| $T_{REC(OVP)}$               | Release from OVP delay                 |                                               |     | 3     |     | ms   |  |

| CURRENT                      | LIMIT                                  |                                               |     |       |     |      |  |

| I <sub>OCP</sub>             | Input current limit threshold          |                                               |     | 1.8   |     | А    |  |

| I <sub>SHORT</sub>           | Current output when OUT to GND         |                                               |     | 110   |     | mA   |  |

| P-MOSFE                      | Т                                      |                                               |     |       |     |      |  |

|                              | V <sub>CHRIN</sub> -V <sub>OUT</sub> , | CHRIN rising,<br>PMOSFET released             |     | 160   |     | mV   |  |

|                              | PMOSFET lockout threshold              | CHRIN falling,<br>PMOSFET off                 |     | 40    |     | mV   |  |

| I <sub>OFF</sub>             | OUT current when P-MOSFET off          | ACIN=5V, CHRIN=<br>GATDRV, OUT=0V             |     |       | 1   | μΑ   |  |

| I <sub>GATDRV</sub>          | GATDRV leakage current                 |                                               |     |       | 1   | μA   |  |

| I <sub>LKG</sub>             | OUT leakage current                    | ACIN=0V, OUT=4.2V,<br>GATDRV=0V               |     |       | 1   | μΑ   |  |

| C <sub>G</sub>               | PMOSFET gate capacitor                 |                                               |     | 200   |     | pF   |  |

| $R_G$                        | PMOSFET gate resistor                  |                                               |     | 1000  |     | Ω    |  |

| OVER TEMPERATURE PROTECTION  |                                        |                                               |     |       |     |      |  |

| T <sub>OTP</sub>             | Overheat threshold                     |                                               |     | 160   |     | C    |  |

| T <sub>hys</sub>             | Overheat hysteresis                    |                                               |     | 25    |     | °C   |  |

### **TYPICAL CHARACTERISTICS**

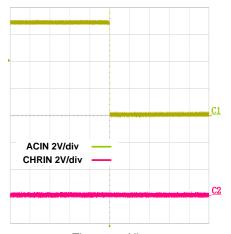

#### **OVP at Power On**

Time: 5ms/div

### **DETAILED FUNCTIONAL DESCRIPTION**

AW3210A is a highly integrated Li-Ion battery charger. AW3210A integrates the charging P-MOSFET, eliminating the need for external charging P-MOSFET and Schottky Diode among a phone charging system. And the reverse current blocking function has been designed in AW3210A, when the CHRIN voltage drops below the OUT, charging P-MOSFET turned off, preventing current draining from the lithium-ion battery into AW3210A.

AW3210A continuously detects the input voltage, if V<sub>IN</sub> exceeds the threshold voltage and lasts longer than 100ns, the internal power P-MOSFET turned off, CHRIN pulled down. AW3210A Built-in current limiting protection circuit, the charging current is limited to a safe range. AW3210A possesses the specific K-Charge<sup>TM</sup> technology, the output current can be adjusted smartly according to the chip temperature to ensure safety during the entire charging process.

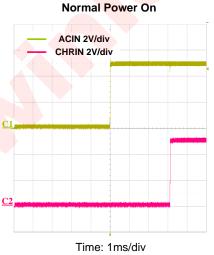

#### **Power On Reset**

AW3210A includes the power-on reset function. During power on process, if ACIN voltage is lower than the power-on reset voltage 2.6V (typ), the internal registers would be reset, and the chip hold in shutdown state. When ACIN voltage rises above the power-on reset voltage 2.6V and stays above 0.7ms, the chip would start, and CHRIN voltage gradually increase. Power-on reset function includes voltage hysteresis and reset delay, in order to avoid the interference of input voltage glitch.

#### **Input Overvoltage Protection**

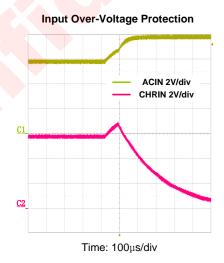

AW3210A continuously detects the input voltage, if  $V_{IN}$  exceeds the threshold voltage and lasts longer than 100ns, the internal power P-MOSFET turned off, CHRIN pulled down, protecting the devices connected to CHRIN and OUT. When ACIN voltage falls below  $V_{OVP}$ - $V_{hys(OVP)}$ , and stay above 2.2ms(typ), the internal power P-MOSFET would turn on. Hysteresis voltage and release delay time keep the system away from the disturbance of input voltage glitch.

#### Input Current Limit & Output Short to Ground Protection

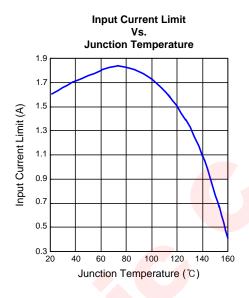

Input current limiting circuit samples output current. When the output current exceeds the limit current I<sub>OCP</sub>, the current limiting circuit limits the input current to protect the chip and the lithium-ion battery. AW3210A also set a specific K-Charge<sup>TM</sup> technology, the output current can be adjusted smartly according to the die temperature. When the temperature is lower than 80°C, the current limit keeps the same as the typical value of 1.8A; when the chip temperature exceeds 80°C, current limit would gradually decrease along with the temperature rising. If the chip temperature reaches 120°C, the current limit would reduce to 1.2A. Input current limit and K-Charge<sup>TM</sup> technology can protect the chip and lithium-ion battery during charging, meanwhile accelerate the charging process to the maximum extent.

AW3210A also possesses the output shorted to ground protection, when CHRIN voltage goes too low, the input current would be limited to 110mA.

#### Charging PMOSFET

AW3210A integrates the charging P-MOSFET, eliminating the need for external charging P-MOSFET and Schottky Diode among a phone charging system. When the chip powers on, the internal P-MOSFET only controlled by GATDRV pin when CHRIN voltage is higher than the OUT pin voltage +160mV (typ). And if CHRIN voltage drops below VOUT+40mV after power on, the charging P-MOSFET would be turned off, and GATDRV would be disconnected from the gate of PMOSFET. What's more, charging P-MOSFET would be closed once either input overvoltage or over temperature protection is triggered.

### **Overheat Protection**

The overheating protection of AW3210A would turn off the power P-MOSFET when the chip temperature exceeds 160  $^{\circ}$ C (typ). And the chip wouldn't recover to normal status, until the die temperature reduce to 135  $^{\circ}$ C (typ).

#### **APPLICATION INFORMATION**

#### CAPACITORS SELECTION

#### ACIN CAPACITOR CACIN

AW3210A advises to use a  $1\mu F$  ceramic capacitor at ACIN pin as shown in Figure 3, for decoupling as well as reducing input voltage overshoot. When AC adapter hot-plugging or a sudden drop in the charge current occurs, a transient overshoot arise at the input port, due to the impact of the parasitic inductance of input power traces. Increasing the input capacitance at ACIN pin can reduce the overshoot voltage, avoiding to affect the charging system. A  $1\mu F$  EYANG X5R/0402 ceramic capacitor is recommended here, whose rating voltage should no less than 16V, and location should be closed to ACIN pin.

#### CHRIN CAPACITOR CCHRIN

A  $1\mu F$  EYANG X5R/0402 ceramic capacitor is also recommended to be placed near CHRIN, whose rating voltage should no less than 10V.

#### PCB LAYOUT CONSIDERATION

To obtain the optimal performance of AW3210A, PCB layout should be considered carefully. Here are some guidelines:

- 1. The exposed plane of chip and GND pins must be connected to the large-area ground layer of PCB directly, meanwhile place sufficient vias below the exposed plane. Thus we can decrease the thermal resistor on the board to optimize heat-diffusion performance.

- 2. Large current charging application may cause a local temperature rise. Keep high-temp zone away from the parts user can easily touch like buttons and LCD would achieve better heat dissipation effect.

- 3. The connection lines between the planes of C<sub>ACIN</sub>, C<sub>CHRIN</sub> and respective chip pins should be as short and wide as possible.

- 4. To achieve optimal large-current performance, the power path shown in red as the figure below must be widen. Please routing according to a factor of 40mil/A between path width and current, for example, the set current is 1A, then the path width should not less than 40x1=40mil.

#### INCREASE SYSTEM ROBUSTNESS AGAINST HOT-PLUG

A surge voltage would arise when charger is hot-plugged into a USB interface. The over-shoot depends on the relative value of the route resistance and the USB cable parasitic inductance as well as the USB output capacitance. To reduce over-shoot effectively, a snubber  $R_{\rm C}$  or a TVS tube, or both of them is recommended to add to the USB power output port. Application circuit is shown below.

Figure 4 Application circuit of increasing robust against hot-plug for USB port

For the selection of TVS, a criterion as below can be used: the maximum clamp voltage of TVS when absorbs 1A peak-to-peak current should not exceed 8V, and a TVS of which part number is ESD9N5V-2/TR is recommended here.

The capacitor in series with  $R_{\text{C}}$  should not less than 1 $\mu$ F, and a X5R-0402 MLCC whose voltage rating no less than 16V is recommended.

For a typical RLC second-order system, if the resistance "R" across the USB cable to USB port capacitor satisfies a relationship of  $R>2\times\sqrt{\frac{L}{C}}$ , then the system would be over-damping, which makes the overshoot lower. Among the  $R>2\times\sqrt{\frac{L}{C}}$ , L represents the parasitic USB cable inductance, C represents the capacitance in series with  $R_C$ , and R consists of  $R_C+R_{ESR}$ , where  $R_{ESR}$  represents parasitic resistance from USB cable and the capacitor which is in series with  $R_C$ .

Whereas the system in the figure 4 has become a third-order system as the adding of  $C_{ACIN}$ , which is close to the input port of AW3210A. For the third-order system, the relationship between R and L/C for over-damping is not linear any more.  $1\Omega$  is recommended as the optimized value of  $R_C$ , for typical condition of the capacitance in series with  $R_C$  ranges from  $1\mu F$  and  $10\mu F$ .

Both the TVS and R<sub>C</sub> should be placed as close to the USB interface as possible.

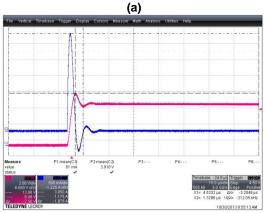

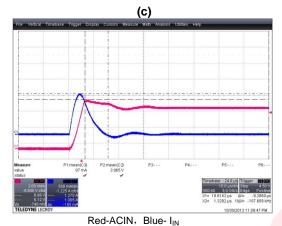

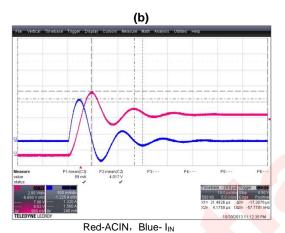

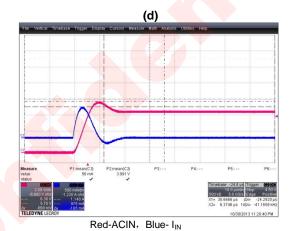

Detailed test waveforms are shown as below in figure 5, whose test condition is a 5V AC adapter with a 1-meter USB cable hot-plugged into the USB port. As the results contrast shown in table 1, a TVS tube or snubber  $R_{\rm C}$  added at the USB interface can reduce the ACIN overshoot effectively, as a consequence of which can increase the robustness of a system against hot-plug.

$\begin{array}{ccc} Red\text{-}ACIN, & Blue\text{-}I_{IN} \\ ACIN\_{PEAK} = 6.5V, \ 10\mu s/div \\ 5V & adapter with original cable plugged in \end{array}$

$ACIN\_{PEAK} = 6.12V, 10\mu s/div$  Two 4.7 $\mu$ H inductors in series among the USB cable, and a TVS(Vc=5.4V) added at the USB port, hot plug

$ACIN_{PEAK} = 8V, 10\mu s/div$  Two 4.7  $\mu$ H inductors in series among the USB cable, hot plug

ACIN\_PEAK = 6.36V,  $10\mu s/div$ Two  $4.7\mu H$  inductors in series among the USB cable, and a  $1\Omega$  R<sub>C</sub> in series with a  $1\mu F$  capacitor added at the USB port, hot plug

Figure 5 The overshoot at the AW3210A ACIN PIN when USB hot-plugged under different conditions

Table 1 Results contrast of Figure 5

| Waveform | Test condition                                                                                                                    | ACIN_PEAK |

|----------|-----------------------------------------------------------------------------------------------------------------------------------|-----------|

| (a)      | 5V adapter + original 1m USB cable                                                                                                | 6.5V      |

| (b)      | 5V adapter + 1m USB cable with two 4.7μH inductors in series                                                                      | 8V        |

| (c)      | 5V adapter + 1m USB cable with two 4.7μH inductors in series + TVS (V <sub>C</sub> =5.4V)                                         | 6.12V     |

| (d)      | 5V adapter + 1m USB cable with two 4.7 $\mu$ H inductors in series + 1 $\Omega$ R <sub>C</sub> in series with 1 $\mu$ F capacitor | 6.36V     |

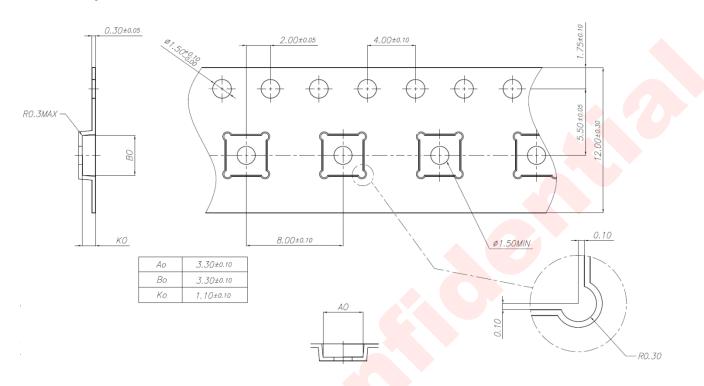

## **TAPE AND REEL INFORMATION**

## **Carrier Tape**

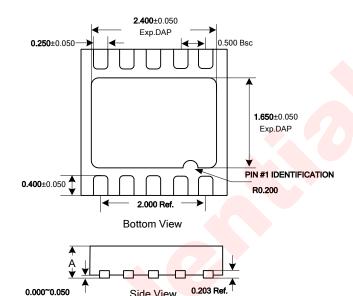

### **PACKAGE DESCRIPTION**

TSLP AND SLP SHARE THE SAME EXPOSE OUTLINE

BUT WITH DIFFERENT THICKNESS

|   |     | SLP   |

|---|-----|-------|

|   | MAX | 0.900 |

| A | NOM | 0.850 |

|   | MIN | 0.800 |

Side View

0.000~0.050

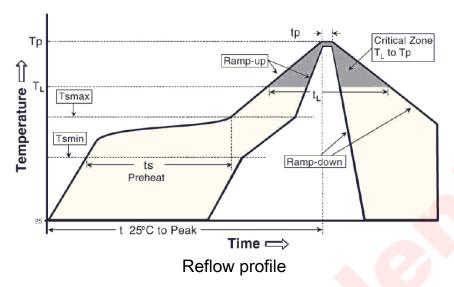

### **REFLOW**

Figure 5 Package Reflow Standard Profile

Table 2 Package Reflow Standard

|                                                                                                                                                                                                    | Sn-Pb eutec                                                  | tic assembly                                                              | Pb-Free assembly                                                         |                                                                           |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------|--|

| Reflow condition                                                                                                                                                                                   | Pkg. thickness ≥ 2.5 mm or Pkg. volume ≥ 350 mm <sup>3</sup> | Pkg.<br>thickness<br>< 2.5 mm and<br>Pkg. volume<br>< 350 mm <sup>3</sup> | Pkg.<br>thickness<br>≥ 2.5 mm or<br>Pkg. volume<br>≥ 350 mm <sup>3</sup> | Pkg.<br>thickness<br>< 2.5 mm and<br>Pkg. volume<br>< 350 mm <sup>3</sup> |  |

| Average ramp-up rate (Liquidus Temperature $(T_L)$ to Peak)                                                                                                                                        | 3 °C/second max.                                             |                                                                           | 3 °C/second max.                                                         |                                                                           |  |

| $\begin{split} & \text{Preheat} \\ & - & \text{Temperature Min } (T_{s(min)}) \\ & - & \text{Temperature Max } (T_{s(max)}) \\ & - & \text{Time } (\min \text{ to } \text{max}) (t_s) \end{split}$ | 100 °C<br>150 °C<br>60-120 seconds                           |                                                                           | 150 °C<br>200 °C<br>60-180 seconds                                       |                                                                           |  |

| $T_{s(max)}$ to $T_L$ - Ramp-up Rate                                                                                                                                                               |                                                              |                                                                           | 3 °C/sec                                                                 | ond max.                                                                  |  |

| Time maintained above:  - Temperature (T <sub>L</sub> )  - Time (t <sub>L</sub> )                                                                                                                  | 183 °C<br>60-150 seconds                                     |                                                                           | 217 °C<br>60-150 seconds                                                 |                                                                           |  |

| Peak Temperature (Tp)                                                                                                                                                                              | 225 +0/-5 °C 240 +0/-5 °C                                    |                                                                           | 245 +0/-5 °C                                                             | 250 +0/-5 °C                                                              |  |

| Time within 5 °C of actual Peak<br>Temperature (t <sub>p</sub> )                                                                                                                                   | 10-30 seconds 10-30 seconds                                  |                                                                           | 10-30 seconds                                                            | 20-40 seconds                                                             |  |

| Ramp-down Rate                                                                                                                                                                                     | 6 °C/second max.                                             |                                                                           | 6 °C/second max.                                                         |                                                                           |  |

| Time 25 °C to Peak Temperature                                                                                                                                                                     | 6 minutes max.                                               |                                                                           | 8 minutes max.                                                           |                                                                           |  |

NOTE 7: All data are compared with the package-top temperature, measured on the package surface;

NOTE 8: AW3210A adopted the Pb-Free assembly.

# **REVISION HISTORY**

| Version   | Date     | Change Record       |

|-----------|----------|---------------------|

| V1.0(CHN) | Nov 2013 | Officially Released |

| V1.0(ENG) | May 2015 | Officially Released |

## **RELATED PARTS**

| Part No.    | Description                                                                       | Comments                                                                                                                                              |

|-------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| AW3112 DNR  | 30V, 3A, PNP Low V <sub>CESAT</sub> BJT<br>Integration with 20V Trench<br>NMOSFET | Integrated with NMOS switch, 32V V <sub>CE</sub> Rating, 0.35V Max V <sub>CESAT</sub> , 1.5W Power Dissipation Rating, DFN2×2-6L                      |

| AW3206 DNR  | Li-ion Battery Charger Integrated with Protective PMOSFET                         | 15V Input Rating, K-Charge <sup>™</sup> Thermal Regulation, DFN2×2-8L                                                                                 |

| AW3208 DNR  | LDO mode Li-ion Battery<br>Charger Integrated with<br>Protective PMOSFET          | 10.5V OVP, 15V Input Rating, K-Charge <sup>™</sup> Thermal Regulation, LDO output mode, DFN2×2-8L                                                     |

| AW3282 DNR  | LDO mode Li-ion Battery Charge<br>Protector                                       | 15V Input Rating, K-Charge <sup>™</sup> Thermal Regulation, LDO output mode, DFN2×2-8L                                                                |

| AW3210A DNR | 1A Li-ion Battery Charger<br>Integrated with Protective<br>PMOSFET                | Up to 1A Charge Current, 15V Input Rating,<br>K-Charge <sup>™</sup> Thermal Regulation, DFN3x3-10L                                                    |

| AW3215A DNR | 1.5A Switch-mode Single Cell                                                      | Max 88% Efficient Switch-mode Conversion, 1.5A Max Charge Current, 18V Input Rating, K-DPM <sup>TM</sup> Maximizes Available Power from USB Port/Wall |

| AW3216 DNR  | Li-ion Battery Charger                                                            | Adapter, K-TEMP <sup>™</sup> Thermal Regulation, DFN3×3-12L                                                                                           |

#### **DISCLAIMER**

Information in this document is believed to be accurate and reliable. However, Shanghai AWINIC Technology Co., Ltd (AWINIC Technology) does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

AWINIC Technology reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. Customers shall obtain the latest relevant information before placing orders and shall verify that such information is current and complete. This document supersedes and replaces all information supplied prior to the publication hereof.

AWINIC Technology products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an AWINIC Technology product can reasonably be expected to result in personal injury, death or severe property or environmental damage. AWINIC Technology accepts no liability for inclusion and/or use of AWINIC Technology products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications that are described herein for any of these products are for illustrative purposes only. AWINIC Technology makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

All products are sold subject to the general terms and conditions of commercial sale supplied at the time of order acknowledgement.

Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

Reproduction of AWINIC information in AWINIC data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. AWINIC is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of AWINIC components or services with statements different from or beyond the parameters stated by AWINIC for that component or service voids all express and any implied warranties for the associated AWINIC component or service and is an unfair and deceptive business practice. AWINIC is not responsible or liable for any such statements.

# 单击下面可查看定价,库存,交付和生命周期等信息

# >>AWINIC(艾为)