# A Low Power One-key Capacitor Touch Sensor

## **Features**

awinic

- Sensitivity adjusted by the capacitance (0~50pF) outside (Refer to the DG\_AW93001\_Hardware\_Design\_Guide for details)

- Maximum response time

- Slow scan mode: 160ms(AW93001STR /BSTR/DNR/BDNR/CDNR/DDNR)

- Slow scan mode: 64ms(AW93001EDNR /FDNR)

- Fast scan mode: 48ms(AW93001STR /BSTR/DNR/BDNR/HDNR/GDNR/MDNR

/LDNR/CSTR/DSTR/CDNR/DDNR/EDNR

/FDNR)

- Push-pull output (AW93001STR/DSTR/DNR

/HDNR/MDNR)

- > Active high/low selected by pin AHLB

- Push-pull output, active high(AW93001CDNR /EDNR)

- Open-drain output, active low (AW93001BSTR /CSTR/BDNR/GDNR/LDNR/DDNR/FDNR)

- Toggle output selected by pin TOG

- Low power consumption

- Slow scan mode (128ms): 1.3µA

- Slow scan mode (32ms): 3.3µA

- Fast scan mode (16ms): 5.4µA

- 2.4V~5.5V power supply

- Operation temperature range: -40°C~85°C

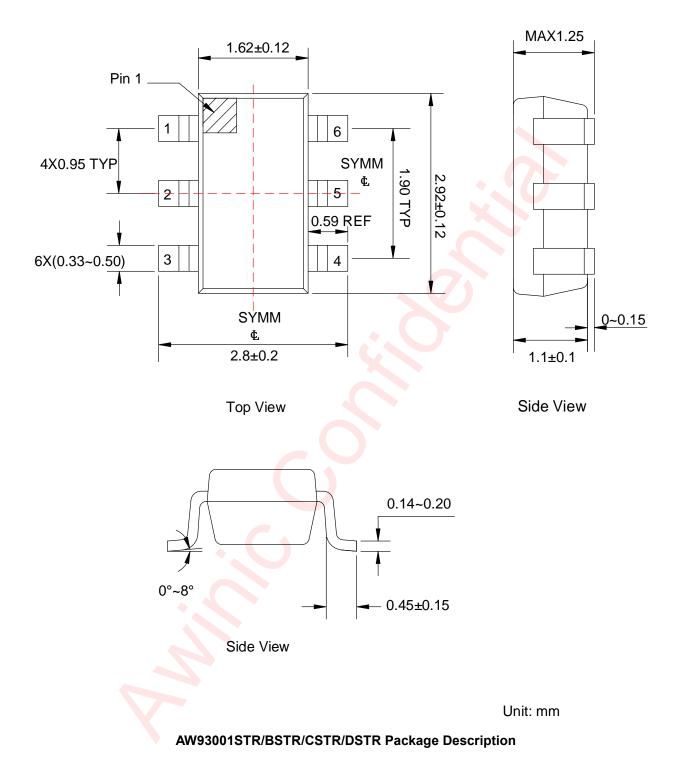

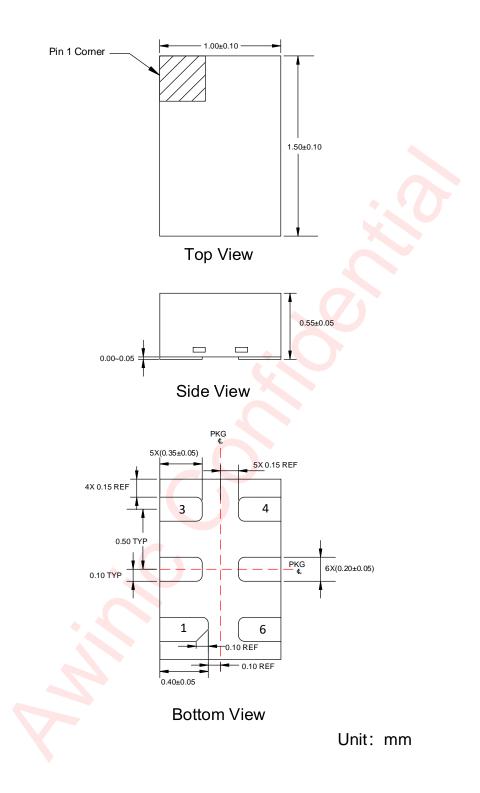

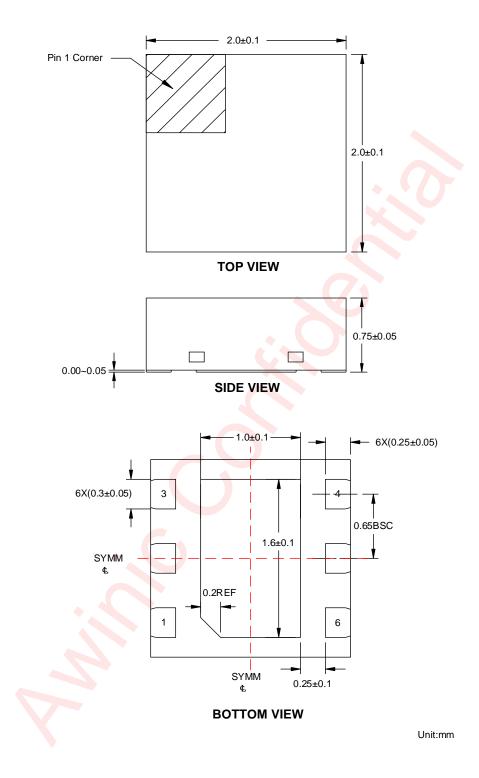

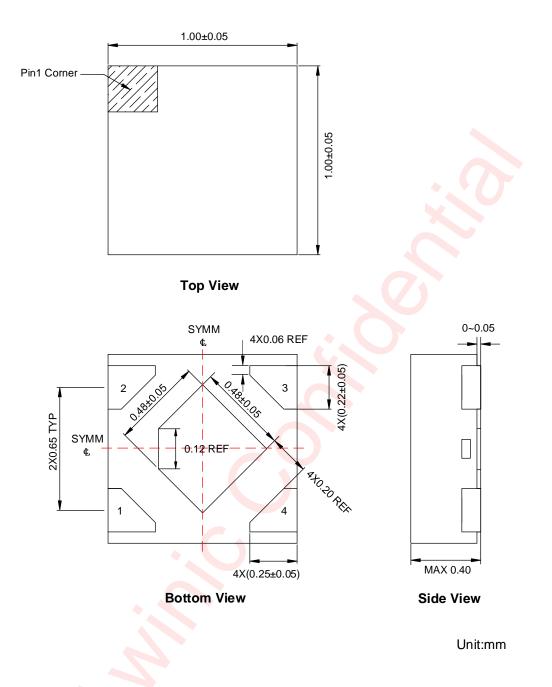

- Package

- SOT23-6L

- DFN 1.5mmx1.0mmx0.55mm-6L

- > DFN 2.0mmx2.0mmx0.75mm-6L

- DFN 1.0mmx1.0mmx0.37mm-4L

### **General Description**

AW93001 is a single channel capacitive touch controller with low power consumption and wide operation voltage range.

With the help of signal processing algorithms, the device is able to track slow environmental variations, and maintain high performance operation.

AW93001 is designed for replacing traditional mechanical button. It can be applied in many fields, such as consumer electronics, white goods and appliances, etc.

## Applications

Wearable device, White goods and appliances Replacing traditional mechanical button

1

# **Typical Application Circuit**

awinic

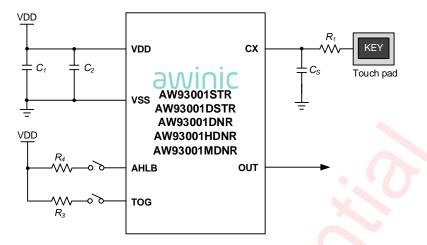

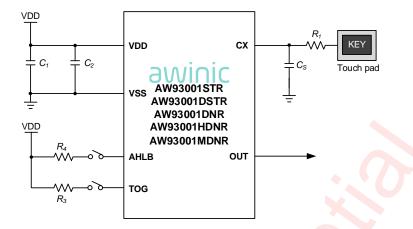

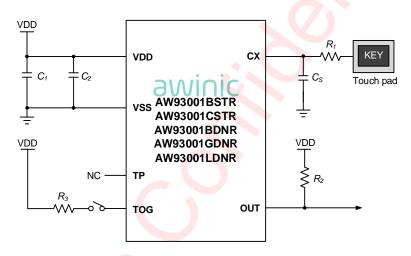

Figure 1 AW93001STR/DSTR/DNR/HDNR/MDNR Typical Application Circuit (push-pull output)

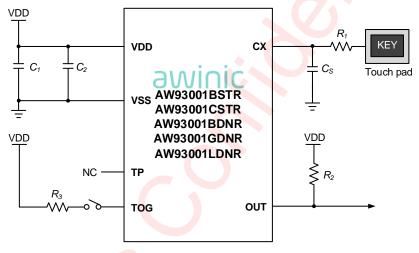

Figure 2 AW93001BSTR/CSTR/BDNR/GDNR/LDNR Typical Application Circuit (open-drain output)

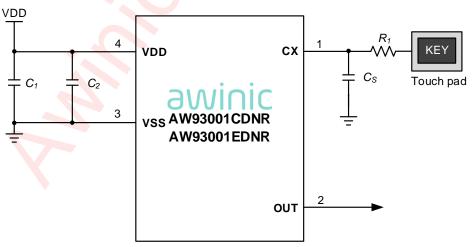

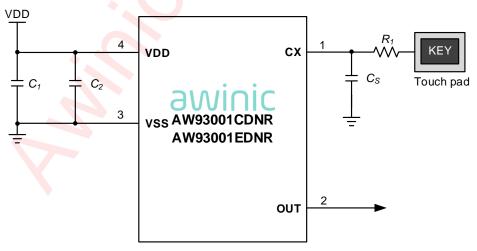

Figure 3 AW93001CDNR/EDNR Typical Application Circuit (push-pull output)

awini

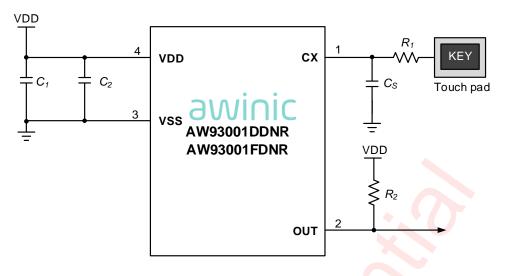

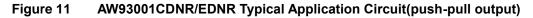

Figure 4 AW93001DDNR/FDNR Typical Application Circuit (open-drain output)

www.awinic.com

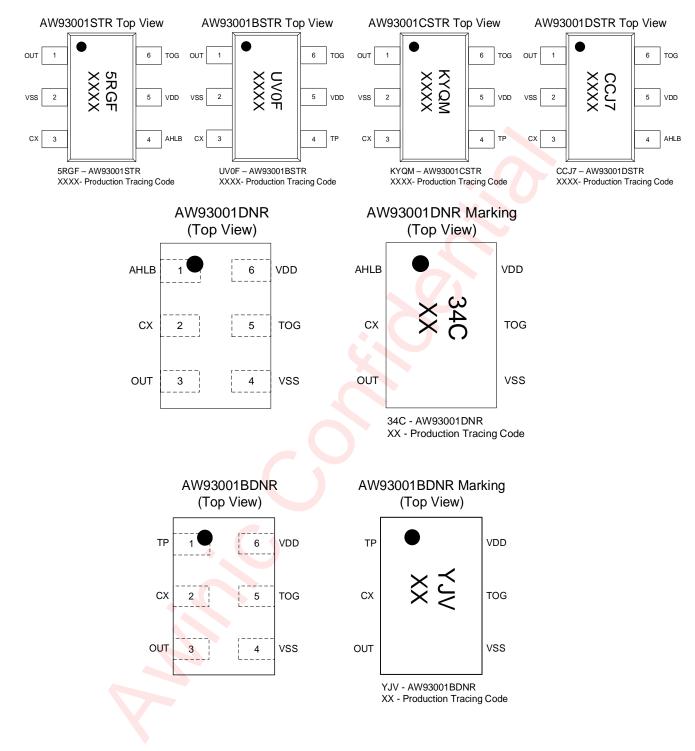

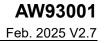

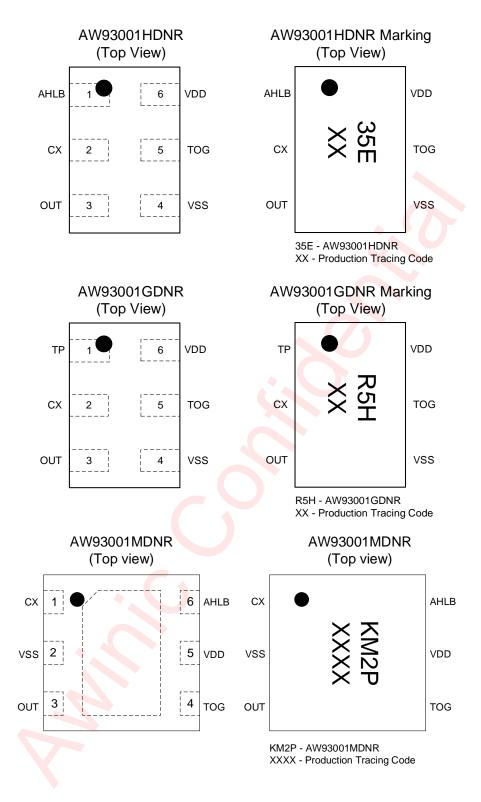

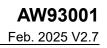

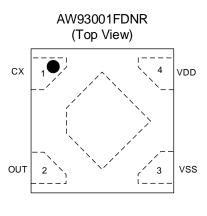

### **Pin Configuration And Top Mark**

4

awinic

AW93001 Feb. 2025 V2.7

## **Pin Definition**

awinio

### Table 1 AW93001STR/DSTR/DNR/HDNR/MDNR Pin Definition

|      |                     | Pin No.             |                 |                                                                                                                                     |

|------|---------------------|---------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------|

| NAME | AW93001<br>STR/DSTR | AW93001<br>DNR/HDNR | AW93001<br>MDNR | DESCRIPTION                                                                                                                         |

| OUT  | 1                   | 3                   | 3               | Push-pull output                                                                                                                    |

| VSS  | 2                   | 4                   | 2               | Ground                                                                                                                              |

| CX   | 3                   | 2                   | 1               | Capacitive detector input                                                                                                           |

| AHLB | 4                   | 1                   | 6               | Output active high or low selection, internal pull-down resistor of $50k\Omega$<br>Floating : Active high;<br>Tied high: Active low |

| VDD  | 5                   | 6                   | 5               | Power supply (2.4V~5.5V), requires decoupling capacitor                                                                             |

| TOG  | 6                   | 5                   | 4               | Output type option, internal pull-down resistor of $50k\Omega$<br>Floating : Direct output;<br>Tied high: Toggle output             |

### Table 2 AW93001BSTR/CSTR/BDNR/GDNR/LDNR Pin Definition

|      |                      | Pin No.              |                 |                                                                                                                         |

|------|----------------------|----------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------|

| NAME | AW93001<br>BSTR/CSTR | AW93001<br>BDNR/GDNR | AW93001<br>LDNR | DESCRIPTION                                                                                                             |

| OUT  | 1                    | 3                    | 3               | Open-drain output, requires pull-up resistor                                                                            |

| VSS  | 2                    | 4                    | 2               | Ground                                                                                                                  |

| CX   | 3                    | 2                    | 1               | Capacitive detector input                                                                                               |

| TP   | 4                    | 1                    | 6               | Test pin, typically floating                                                                                            |

| VDD  | 5                    | 6                    | 5               | Power supply (2.4V~5.5V), requires decoupling capacitor                                                                 |

| TOG  | 6                    | 5                    | 4               | Output type option, internal pull-down resistor of $50k\Omega$<br>Floating : Direct output;<br>Tied high: Toggle output |

| NAME | Pin No. | DESCRIPTION                                                                                           |

|------|---------|-------------------------------------------------------------------------------------------------------|

| СХ   | 1       | Capacitive detector input                                                                             |

| OUT  | 2       | Push-pull output (AW93001CDNR/EDNR)<br>Open-drain output (AW93001DDNR/FDNR), require pull-up resistor |

| VSS  | 3       | Ground                                                                                                |

| VDD  | 4       | Power supply (2.4V~5.5V), requires decoupling capacitor                                               |

#### Table 3 AW93001CDNR/DDNR/EDNR/FDNR Pin Definition

## **Device Comparison**

|             |            |                    | •                   |      |             |

|-------------|------------|--------------------|---------------------|------|-------------|

| Device      | Package    | Scan               | mode                | мот  | Output Mode |

| Device      | Гаскауе    | Fast scan          | Fast scan Slow scan |      | Output Mode |

| AW93001STR  | SOT23-6L   | 16ms               | 128ms               |      | Push-pull   |

| AW93001BSTR | SOT23-6L   | 16ms               | 128ms               |      | Open-drain  |

| AW93001DNR  | DFN1510-6L | 16ms               | 128ms               |      | Push-pull   |

| AW93001BDNR | DFN1510-6L | 16ms               | 128ms               | 16s  | Open-drain  |

| AW93001HDNR | DFN1510-6L | 16ms               |                     | 105  | Push-pull   |

| AW93001GDNR | DFN1510-6L | 16ms               |                     |      | Open-drain  |

| AW93001MDNR | DFN2x2-6L  | 16ms               |                     |      | Push-pull   |

| AW93001LDNR | DFN2x2-6L  | 16ms               | -                   |      | Open-drain  |

| AW93001CSTR | SOT23-6L   | 16ms               |                     | 100s | Open-drain  |

| AW93001DSTR | SOT23-6L   | 16ms               |                     | 1005 | Push-pull   |

| AW93001CDNR | DFN1x1-4L  | 16ms               | 128ms               |      | Push-pull   |

| AW93001DDNR | DFN1x1-4L  | 16 <mark>ms</mark> | 128ms               | 16s  | Open-drain  |

| AW93001EDNR | DFN1x1-4L  | 16ms               | 32ms                | 105  | Push-pull   |

| AW93001FDNR | DFN1x1-4L  | 16ms               | 32ms                |      | Open-drain  |

#### Table 4 Device Comparison

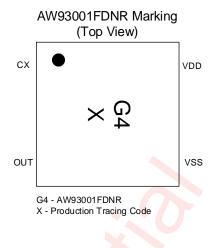

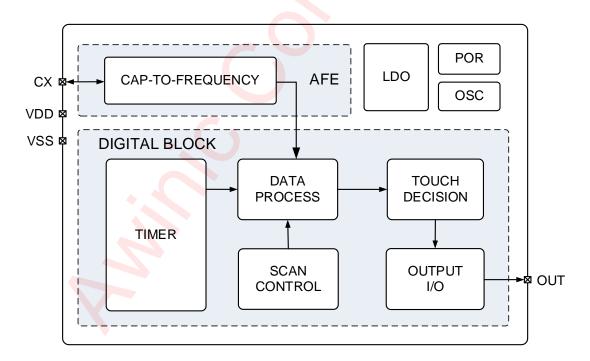

## **Functional Block Diagram**

Figure 5 AW93001STR/BSTR/CSTR/DSTR/DNR/BDNR/HDNR/GDNR/MDNR/LDNR Functional Block Diagram

### Figure 6 AW93001CDNR/DDNR/EDNR/FDNR Functional Block Diagram

## **Ordering Information**

| Part Number | Temperature | Package               | Marking | Moisture<br>Sensitivity Level | Environmental<br>Information | Delivery Form                |

|-------------|-------------|-----------------------|---------|-------------------------------|------------------------------|------------------------------|

| AW93001STR  | -40°C~85°C  | SOT23-6L              | 5RGF    | MSL3                          | ROHS+HF                      | 3000 units/<br>Tape and Reel |

| AW93001BSTR | -40°C~85°C  | SOT23-6L              | UV0F    | MSL3                          | ROHS+HF                      | 3000 units/<br>Tape and Reel |

| AW93001CSTR | -40°C~85°C  | SOT23-6L              | KYQM    | MSL3                          | ROHS+HF                      | 3000 units/<br>Tape and Reel |

| AW93001DSTR | -40°C~85°C  | SOT23-6L              | CCJ7    | MSL3                          | ROHS+HF                      | 3000 units/<br>Tape and Reel |

| AW93001DNR  | -40°C~85°C  | DFN<br>1.5mmx1.0mm-6L | 34C     | MSL1                          | ROHS+HF                      | 4500 units/<br>Tape and Reel |

| AW93001BDNR | -40°C~85°C  | DFN<br>1.5mmx1.0mm-6L | ΥJV     | MSL1                          | ROHS+HF                      | 4500 units/<br>Tape and Reel |

| AW93001HDNR | -40°C~85°C  | DFN<br>1.5mmx1.0mm-6L | 35E     | MSL1                          | ROHS+HF                      | 4500 units/<br>Tape and Reel |

| AW93001GDNR | -40°C~85°C  | DFN<br>1.5mmx1.0mm-6L | R5H     | MSL1                          | ROHS+HF                      | 4500 units/<br>Tape and Reel |

| AW93001MDNR | -40°C~85°C  | DFN<br>2.0mmx2.0mm-6L | KM2P    | MSL1                          | ROHS+HF                      | 3000 units/<br>Tape and Reel |

| AW93001LDNR | -40°C~85°C  | DFN<br>2.0mmx2.0mm-6L | нквв    | MSL1                          | ROHS+HF                      | 3000 units/<br>Tape and Reel |

| AW93001CDNR | -40°C~85°C  | DFN<br>1.0mmx1.0mm-4L | V2      | MSL1                          | ROHS+HF                      | 4500 units/<br>Tape and Reel |

| AW93001DDNR | -40°C~85°C  | DFN<br>1.0mmx1.0mm-4L | FD      | MSL1                          | ROHS+HF                      | 4500 units/<br>Tape and Reel |

| AW93001EDNR | -40°C~85°C  | DFN<br>1.0mmx1.0mm-4L | Z7      | MSL1                          | ROHS+HF                      | 4500 units/<br>Tape and Reel |

| AW93001FDNR | -40°C~85°C  | DFN<br>1.0mmx1.0mm-4L | G4      | MSL1                          | ROHS+HF                      | 4500 units/<br>Tape and Reel |

# Absolute Maximum Ratings<sup>(NOTE1)</sup>

| PARAMETER                    | PARAMETERS                                               |                               |  |  |  |

|------------------------------|----------------------------------------------------------|-------------------------------|--|--|--|

| Supply voltage rang          | ge VDD                                                   | -0.3V to 6.0V                 |  |  |  |

| Input voltage range          | CX, TP, AHLB, TOG                                        | -0.3V to 6.0V                 |  |  |  |

| Output voltage range         | OUT                                                      | -0.3V to 6.0V                 |  |  |  |

| Operating free-air tempe     | perating free-air temperature range -40°C to 85°C        |                               |  |  |  |

| Maximum operating junction t | Maximum operating junction temperature T <sub>JMAX</sub> |                               |  |  |  |

| Storage temperatur           | e T <sub>STG</sub>                                       | -6 <mark>5°C to 15</mark> 0°C |  |  |  |

| Lead temperature (solderin   | ng 10 seconds)                                           | 260°C                         |  |  |  |

| E                            | SD(Including CDM HBM ) <sup>(N</sup>                     | IOTE2)                        |  |  |  |

| НВМ                          |                                                          | ±6kV                          |  |  |  |

| CDM                          | CDM                                                      |                               |  |  |  |

|                              | Latch-Up                                                 |                               |  |  |  |

| Test condition: JES          | SD78E                                                    | +IT: 200mA, -IT: -200mA       |  |  |  |

NOTE1: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

NOTE2: The human body model is a 100pF capacitor discharged through a  $1.5k\Omega$  resistor into each pin. Test method: ESDA/JEDEC JS-001-2017(HBM) ESDA/JEDEC JS-002-2018(CDM).

## **Electrical Characteristics**

Note: Typical values are given for  $T_A = +25^{\circ}C$ , VDD=3.0V unless otherwise specified.

|       | PARAMETER                        | TEST CONDITION                    | MIN | TYP | MAX | UNIT |

|-------|----------------------------------|-----------------------------------|-----|-----|-----|------|

| VDD   | Operation voltage                | -                                 | 2.4 | 3.0 | 5.5 | V    |

| la.   | Current in slow scan             | Cs=20pF, scan period=128ms        | -   | 1.3 | -   | μA   |

| IsL   | mode                             | Cs=20pF, scan period=32ms         | -   | 3.3 | -   | μA   |

| IFS   | Current in fast scan mode        | Cs=20pF, scan period=16ms         | -   | 5.4 | -   | μA   |

| VIH   | Input high level                 | Pin AHLB, TOG                     | 1.4 | -   | -   | V    |

| VIL   | Input low level                  | Pin AHLB, TOG                     | -   | -   | 0.4 | V    |

| Іон   | Output high current              | VOH≥VDD-0.4V                      | -   | -   | -4  | mA   |

| lo∟   | Output low current               | VOL≤0.4V                          | 8   | -   | -   | mA   |

| Rpd   | Input pin pull-down<br>resistor  | Pin TOG, AHLB                     | -   | 50  | -   | kΩ   |

|       |                                  | Fast scan mode, scan period=16ms  | 34  | -   | 48  | ms   |

| TRESP | Response time <sup>(NOTE3)</sup> | Slow scan mode, scan period=32ms  | 34  | -   | 64  | ms   |

|       |                                  | Slow scan mode, scan period=128ms | 34  | -   | 160 | ms   |

NOTE3: It has an error of  $\pm$  10% according to the mass production test data.

### **Detailed Functional Description**

### **Power On Timing**

awinic

To ensure that the internal configuration parameters are correctly loaded during each power-on process of AW93001, the power design of AW93001 needs to follow the following power-on timing limit:

During the process of voltage rise or normal power supply, abnormal voltage fluctuations can not occur in the power supply. The peak to peak value of voltage fluctuation should below 200mV.

As the following timing figure:

Note: Especially during the battery welding process, abnormal voltage fluctuations may occur.

Figure 3 AW93001 Power on Timing

### Initialization

After power-on, the chip executes initialization process automatically, it lasts for about 500ms. During initialization, touch decision does not work, and no touch status can be reported.

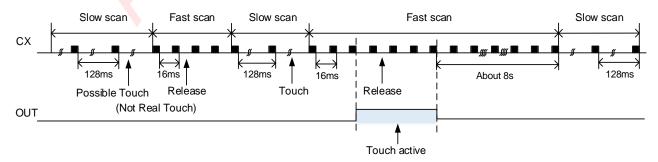

### Scan Mode

The AW93001STR/BSTR/DNR/BDNR/CDNR/DDNR have two scan modes, fast scan mode and slow scan mode, In fast scan mode, the scan period is about 16ms, and the maximum response time is about 48ms. In slow scan mode, the scan period is about 128ms with lower power consumption, and the maximum response time is about 160ms. For power saving, the device automatically switches scan mode between fast and slow mode according to touch detection status. After power-on, the device enters fast scan mode directly. In fast scan mode, if there is no touch detected for 8s continuously, the device switches to slow scan mode. In slow scan mode, if touch is detected, the device returns to fast scan mode at once.

### Figure 7 AW93001STR/BSTR/DNR/BDNR/CDNR/DDNR Scan Mode

**awi**

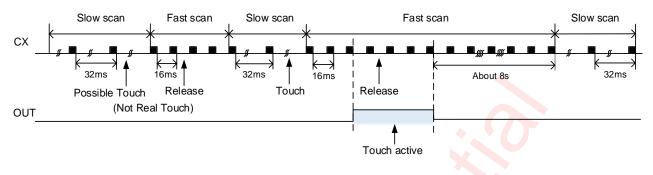

The AW93001EDNR/FDNR have two scan modes, fast scan mode and slow scan mode, In fast scan mode, the scan period is about 16ms, and the maximum response time is about 48ms. In slow scan mode, the scan period is about 32ms with lower power consumption, and the maximum response time is about 64ms.

Figure 8 AW93001EDNR/FDNR Scan Mode

The AW93001CSTR/DSTR/HDNR/GDNR/MDNR/LDNR only has fast scan mode. In fast scan mode, the scan period is about 16ms, and the maximum response time is about 48ms. After power-on, the device enters fast scan mode directly and keeps it all the time.

### **Output Mode**

For AW93001STR/DNR/HDNR/MDNR, pin OUT is a push-pull output, and the output mode depends on the initial power-on states of pin AHLB and pin TOG. Pin TOG selects direct output or toggle output, and pin AHLB selects active high or active low.

| Pin TOG   | Pin AHLB  | Pin OUT's output mode                |

|-----------|-----------|--------------------------------------|

| Floating  | Floating  | Direct output, active high           |

| Floating  | Tied high | Direct output, active low            |

| Tied high | Floating  | Toggle output, initial state is low  |

| Tied high | Tied high | Toggle output, initial state is high |

### Table 5 AW93001STR/DSTR/DNR/HDNR/MDNR Output Mode

For AW93001BSTR/CSTR/BDNR/GDNR/LDNR, pin OUT is an open-drain output, and the output mode only depends on the initial power-on state of pin TOG.

#### Table 6 AW93001BSTR/CSTR/BDNR/GDNR/LDNR Output Mode

| Pin TOG   | Pin OUT's output mode                  |  |  |  |  |  |

|-----------|----------------------------------------|--|--|--|--|--|

| Floating  | Direct output, active low              |  |  |  |  |  |

| Tied high | Toggle output, initial state is high-Z |  |  |  |  |  |

When pin AHLB or pin TOG is tied high, the internal pull-down function of these pin is closed, so no additional power consumption will be generated.

For AW93001CDNR/EDNR, pin OUT is a push-pull output, and the output is high level active.

For AW93001DDNR/FDNR, pin OUT is an open-drain output, and the output is low level active.

### Maximum Key-on Duration Time

In order to prevent the false touch detection caused by objects covering the touch pad, the chip sets maximum key-on duration time. For AW93001STR/BSTR/DNR/BDNR/HDNR/GDNR/MDNR/LDNR/CDNR/DDNR/EDNR/FDNR /FDNR/CDNR/DDNR/EDNR/FDNR, if the devices' touch status last over 16s, it will be released until a new touch action. For AW93001CSTR/DSTR, if the devices' touch status last over 100s, it will be released until a new touch action.

## **Application Information**

awinic

### Figure 9 AW93001STR/DSTR/DNR/HDNR/MDNR Typical Application Circuit (push-pull output)

Figure 10 AW93001BSTR/CSTR/BDNR/GDNR/LDNR Typical Application Circuit (open-drain output)

Figure 12 AW93001DDNR/FDNR Typical Application Circuit(open-drain output)

To obtain the optimal performance, the capacitive touch controller's application circuit should be considered carefully. Here are some guidelines:

- 1. The chip should be supplied by stable power, otherwise it may cause abnormal sensitivity or false detection.

- 2. Add a resistor R1 between Cs and Touch pad to improve ESD protection and reduce EMI.

- 3. Sensitivity can be adjusted by C<sub>s</sub>. The smaller the C<sub>s</sub>, the higher the sensitivity, the higher the power consumption. It is suggested to use temperature insensitive capacitors to adjust the sensitivity, such as NP0 capacitors.

- 4. Sensitivity can be adjusted by the electrode size. Using a larger electrode size can increase sensitivity, but the electrode size must be used in the effective scope.

- 5. Sensitivity can be adjusted by the panel thickness. Using a thinner panel can increase sensitivity, but the panel thickness must be used in the effective scope.

| Component | Name                         | Description                                  | Тур. | Unit |

|-----------|------------------------------|----------------------------------------------|------|------|

|           | <b>C</b> 1                   | -                                            | 1    | μF   |

| С         | C <sub>2</sub>               | -                                            | 0.1  | μF   |

| Ŭ         | Cs                           | 5% resolution<br>Low temperature coefficient | -    | pF   |

|           | R1                           | 5% resolution                                | 4.7  | kΩ   |

| R         | R <sub>2</sub>               | 5% resolution                                | 100  | kΩ   |

| ĸ         | R <sub>3</sub> 5% resolution |                                              | 4.7  | kΩ   |

|           | R <sub>4</sub>               | 5% resolution                                | 4.7  | kΩ   |

### Recommended Components List

awin

### **PCB Layout Consideration**

awini

To obtain the optimal performance, PCB layout should be considered carefully. Here are some guidelines:

- 1. The connections between the capacitors  $(C_1, C_2)$  and the IC as short as possible, to reduce noise and EMI.

- 2. The distance from the touch pad to the pin CX as short as possible, and the signal trace as thin as possible.

- 3. The IC and sensor traces surrounded by ground, both top and bottom layers filled with ground plane.

- 4. The sensor and traces away from mic, earphone line, because capacitive sensor will disturb audio line.

- 5. The sensor and traces away from interferences, such as communication lines.

- 6. The material of panel covering the PCB cannot contain metal or electric element, and the surface coating is the same.

www.awinic.com

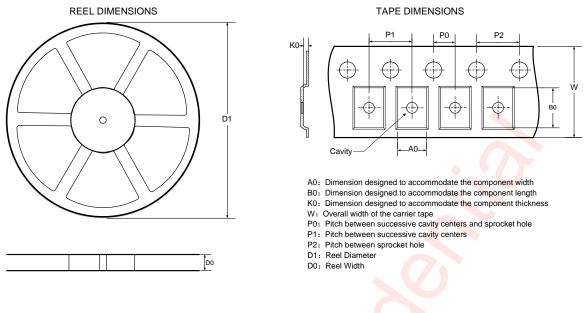

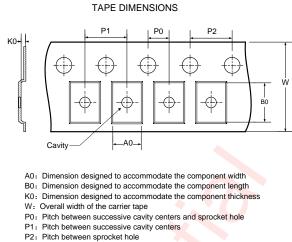

## **Tape And Reel Information**

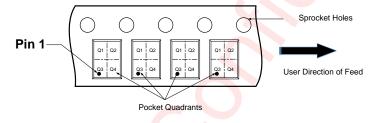

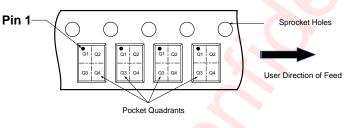

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

Note: The above picture is for reference only. Please refer to the value in the table below for the actual size

| DIMENSIONS AND PIN1 ORIENTATION |      |      |      |      |      |      |      |      |               |

|---------------------------------|------|------|------|------|------|------|------|------|---------------|

| D1                              | D0   | A0   | B0   | K0   | P0   | P1   | P2   | w    | Pin1 Quadrant |

| (mm)                            | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) |               |

| 178                             | 8.4  | 3.3  | 3.2  | 1.4  | 2    | 4    | 4    | 8    | Q3            |

| All dimensions are nominal      |      |      |      |      |      |      |      |      |               |

#### AW93001STR/BSTR/CSTR/DSTR Tape And Reel Information

awir

awir

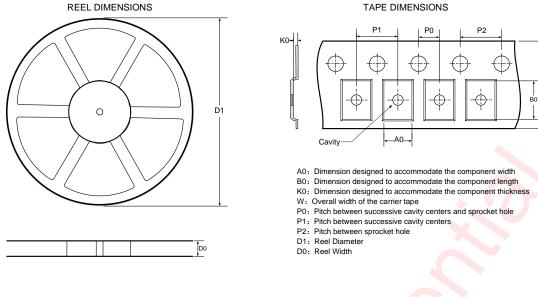

D0: Reel Width

Note: The above picture is for reference only. Please refer to the value in the table below for the actual size

#### DIMENSIONS AND PIN1 ORIENTATION

| DIMENC   |      |      |      |      |      |      |      |      |               |  |

|----------|------|------|------|------|------|------|------|------|---------------|--|

| D1       | D0   | A0   | B0   | K0   | P0   | P1   | P2   | w    | Pin1 Quadrant |  |

| (mm)     | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) |               |  |

| 178      | 8.4  | 2.3  | 2.3  | 1    | 2    | 4    | 4    | 8    | Q1            |  |

| All dime |      |      |      |      |      |      |      |      |               |  |

All dimensions are nominal

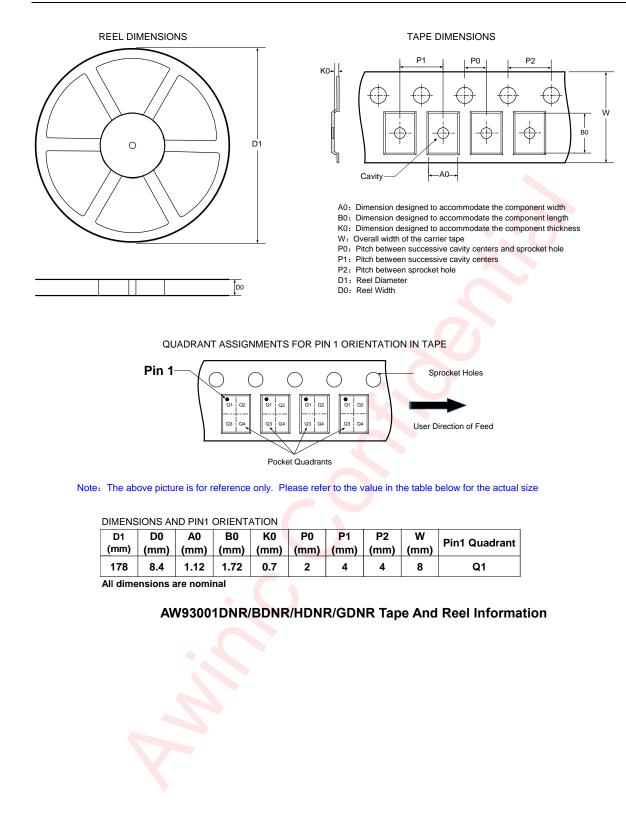

#### AW93001MDNR/LDNR Tape And Reel Information

Ŵ

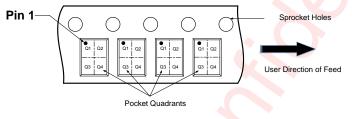

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

Note: The above picture is for reference only. Please refer to the value in the table below for the actual size

| DIMENSIONS AND PIN1 ORIENTATION |            |            |            |            |            |            |            |           |               |

|---------------------------------|------------|------------|------------|------------|------------|------------|------------|-----------|---------------|

| D1<br>(mm)                      | D0<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1 Quadrant |

| 178                             | 8.4        | 1.15       | 1.15       | 0.5        | 2          | 4          | 4          | 8         | Q1            |

All dimensions are nominal

awin

#### AW93001CDNR/DDNR/EDNR/FDNR Tape And Reel Information

## **Package Description**

awinic

#### AW93001DNR/BDNR/HDNR/GDNR Package Description

#### AW93001MDNR/LDNR Package Description

awinic

### AW93001CDNR/DDNR/EDNR/FDNR Package Description

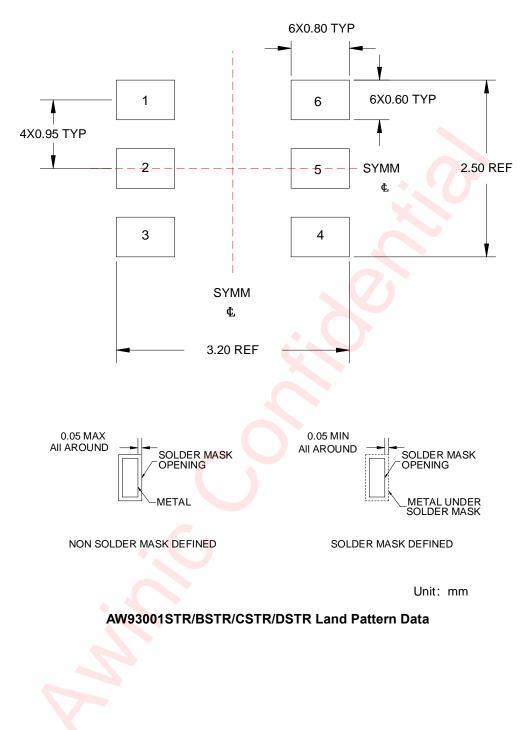

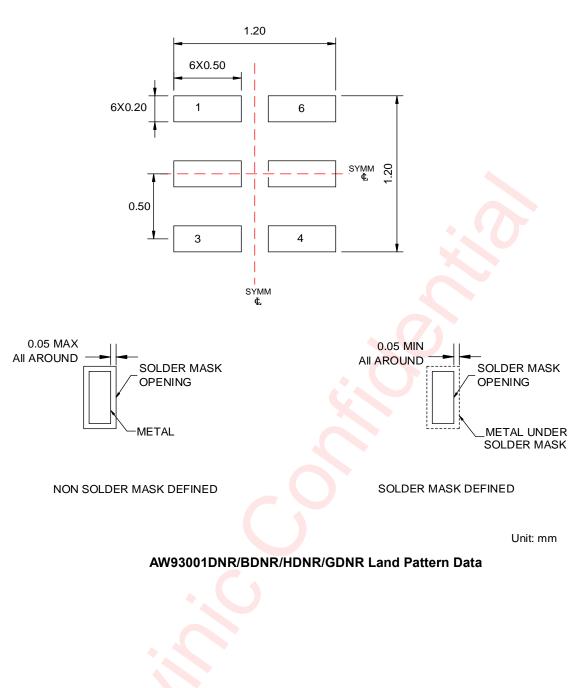

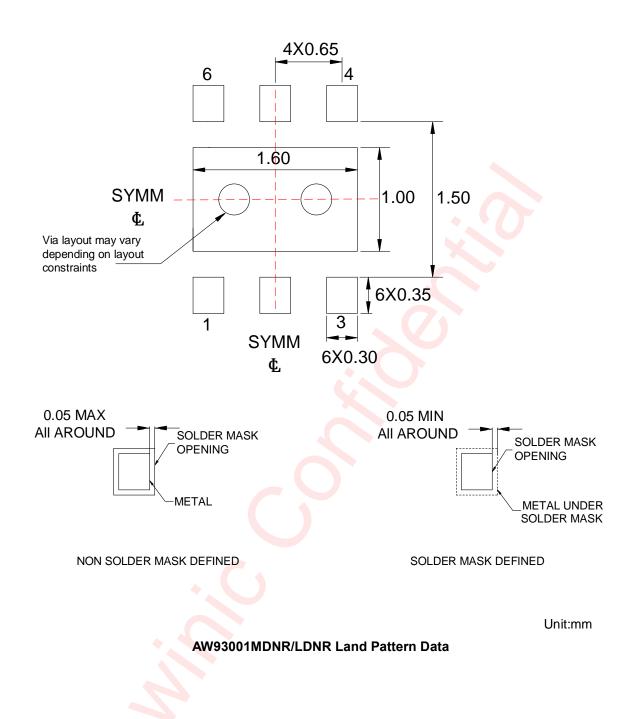

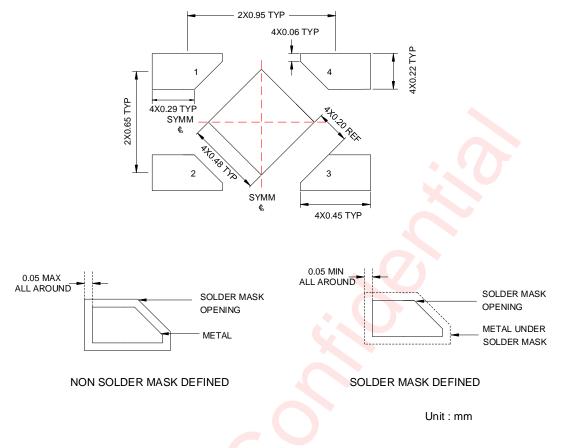

### Land Pattern Data

艾为电子技术股份有限公司

shanghai awinic technology co., ltd.

awini

awinic

awinic

AW93001CDNR/DDNR/EDNR/FDNR Land Pattern Data

## **Revision History**

| Version | Date      | Change Record                                                                                                                                        |  |  |  |

|---------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V1.0    | Feb.2021  | Officially released                                                                                                                                  |  |  |  |

| V1.1    | Feb.2021  | Merge the AW93001STR/BSTR/DNR/BDNR's datasheet;<br>Add a resistor between Cs and Touch pad in Typical Application Circuit                            |  |  |  |

| V1.2    | May.2021  | Update Ordering Information                                                                                                                          |  |  |  |

| V1.3    | Jul.2021  | Add the chip,AW93001HDNR's information                                                                                                               |  |  |  |

| V1.4    | Jul.2021  | Correct the AW93001HDNR's tracing code, update the package DFN1510-6's POD information                                                               |  |  |  |

| V1.5    | Jul.2021  | Add the chip,AW93001GDNR's information, update the Device Comparison table                                                                           |  |  |  |

| V1.6    | Nov.2021  | Add the chip,AW93001MDNR/LDNR's information, update the Device<br>Comparison table;<br>Correct the R3 resistor value in Recommended Components List. |  |  |  |

| V1.7    | Dec.2021  | Update Ordering Information                                                                                                                          |  |  |  |

| V1.8    | Mar.2022  | Update Device Comparison, correct the AW93001STR/BSTR/DNR/BDNR's MOT value, update Functional Block Diagram.                                         |  |  |  |

| V1.9    | May.2022  | Add the chip, AW93001CSTR's information, update the Device Comparison table                                                                          |  |  |  |

| V2.0    | Sep.2022  | Update the Absolute Maximum Ratings, correct the maximum voltage range;<br>Update the AW93001STR/BSTR/CSTR Tape And Reel Information                 |  |  |  |

| V2.1    | Oct.2022  | Add the chip,AW93001DSTR's information, update the Device information                                                                                |  |  |  |

| V2.2    | Jul.2023  | Add the minimum response time in the table of Electrical Characteristics (P7).                                                                       |  |  |  |

| V2.3    | Sep.2023  | Add the part of Capacitor Cs Selection (P10~P11).                                                                                                    |  |  |  |

| V2.4    | Jan.2024  | Update the description of features (P1).<br>Delete the part of Capacitor Cs Selection (P10).                                                         |  |  |  |

| V2.5    | Jul. 2024 | Update the power consumption(P1 and P7)                                                                                                              |  |  |  |

| V2.6    | Jul. 2024 | Add the chip: AW93001CDNR/DDNR/EDNR/FDNR                                                                                                             |  |  |  |

| V2.7    | Feb. 2025 | Add the power on timing(P12)                                                                                                                         |  |  |  |

### **Disclaimer**

All trademarks are the property of their respective owners. Information in this document is believed to be accurate and reliable. However, Shanghai AWINIC Technology Co., Ltd (AWINIC Technology) does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

AWINIC Technology reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. Customers shall obtain the latest relevant information before placing orders and shall verify that such information is current and complete. This document supersedes and replaces all information supplied prior to the publication hereof.

AWINIC Technology products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an AWINIC Technology product can reasonably be expected to result in personal injury, death or severe property or environmental damage. AWINIC Technology accepts no liability for inclusion and/or use of AWINIC Technology products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications that are described herein for any of these products are for illustrative purposes only. AWINIC Technology makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

All products are sold subject to the general terms and conditions of commercial sale supplied at the time of order acknowledgement.

Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

Reproduction of AWINIC information in AWINIC data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. AWINIC is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of AWINIC components or services with statements different from or beyond the parameters stated by AWINIC for that component or service voids all express and any implied warranties for the associated AWINIC component or service and is an unfair and deceptive business practice. AWINIC is not responsible or liable for any such statements.

单击下面可查看定价,库存,交付和生命周期等信息

>>AWINIC(艾为)