# High Efficiency, 3-Channel WLED Driver with Flash Function

# Feature

awinic

- ± 1% current matching across voltage, temperature, and process

- ± 3% current accuracy across voltage, temperature, and process

- High efficiency, up to 91%

- Up to 29.6mA/string in backlight mode and up to 79.9mA/string in flash mode

- I<sup>2</sup>C/PWM dual dimming control mode

- 11-bit I<sup>2</sup>C exponential or linear mapping with programmable transition ramp time

- Programmable current sink turn on/off ramp time

- Selectable boost converter switching frequency 1MHz or 500kHz with shift up and down option

- Programmable slew rate control minimize switching noise and improve EMI performance

- Five configurable OVP thresholds (17.5V, 24V, 31V, 38V, 41.5V)

- Four configurable current limit thresholds (900mA,1800mA, 2700mA, 3400mA)

- Programmable flash current and timeout

- LED open/short protection

- WLCSP 1.64mm x 1.24mm-12B

- 7-bit slave address (A7~A1) is 0110110 binary(0x36H)

# **Applications**

Mobile phones and Tablet Backlighting

# **General Description**

AW99703 is a highly accurate, highly matching three-string LCD backlighting power solution. It is a highly integrated step-up DC-DC converter operating with a wide input voltage from 2.7V to 5.5V and a temperature range from -40°C to 85°C, accommodating 1-cell lithium ion battery or 5V supply.

The AW99703 integrates a high voltage MOSFET, and three high accuracy, high voltage current sinks. Each current sink can be regulated up to 29.6mA in backlight mode. In flash mode, flash current sink can be regulated up to 79.9mA, and flash timeout can be regulated up to 1.5sec.

The LED current is adjusted via an I<sup>2</sup>C interface or through a logic level PWM input. The PWM duty cycle is internally sensed and mapped to an 11-bit linear current.

Thorough protection features include LED fault (open and short) protection, cycle-by-cycle currentlimit protection, output over-voltage protection and thermal shutdown.

1

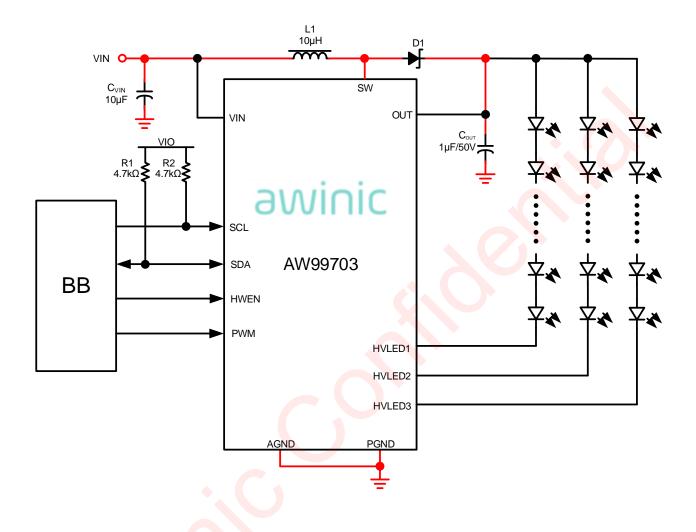

# **Typical Application Circuit**

#### Notice for typical application circuit:

The power/ground path marked in red as shown in the figures above, please traces according power line alignment rules.

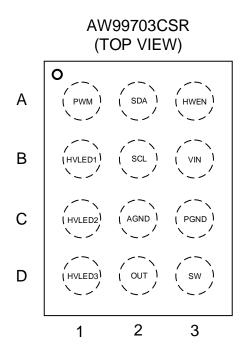

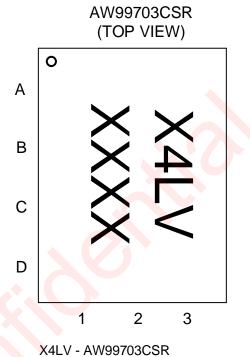

# **Pin Configuration and Top Mark**

XXXX - Production Tracing Code

# **Pin Definition**

| P      | PIN    |        | DESCRIPTION                                                                                                                  |

|--------|--------|--------|------------------------------------------------------------------------------------------------------------------------------|

| NUMBER | NAME   |        |                                                                                                                              |

| A1     | PWM    | Input  | Input for PWM signal. With an internal 400k $\Omega$ pull-down resistor to GND.                                              |

| A2     | SDA    | I/O    | Serial data connection for I <sup>2</sup> C-Compatible interface.                                                            |

| A3     | HWEN   | Input  | Input for Hardware enable. Logic high input to enable the device.<br>With an internal 400kΩ pull-down resistor to GND.       |

| B1     | HVLED1 | Input  | Input pin to high-voltage current sink 1.<br>The minimum voltage of HVLED1, HVLED2 and HVLED3 is chosen to compare with VHR. |

| B2     | SCL    | Input  | Serial clock connection for I <sup>2</sup> C-compatible interface.                                                           |

| B3     | VIN    | Input  | Power voltage with 2.7V to 5.5V range.                                                                                       |

| C1     | HVLED2 | Input  | Input pin to high-voltage current sink 2.<br>The minimum voltage of HVLED1, HVLED2 and HVLED3 is chosen to compare with VHR. |

| C2     | AGND   | GND    | Analog ground.                                                                                                               |

| C3     | PGND   | GND    | Power ground.                                                                                                                |

| D1     | HVLED3 | Input  | Input pin to high-voltage current sink 3.<br>The minimum voltage of HVLED1, HVLED2 and HVLED3 is chosen to compare with VHR. |

| D2     | OUT    | Input  | Connect to the positive pin of the output capacitor. The voltage of OUT pin is sensed for OVP.                               |

| D3     | SW     | Output | Connect to the drain of the internal NFET. Connect SW to the junction of the inductor and the Schottky diode anode.          |

3

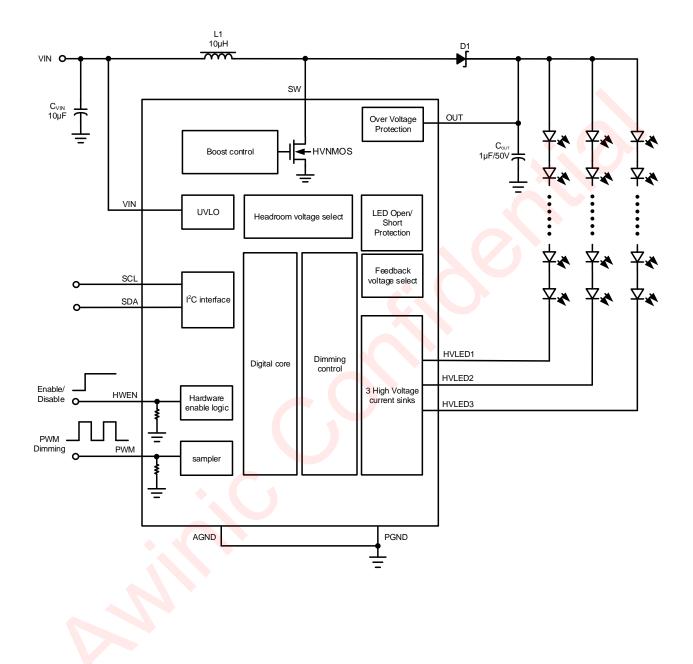

# Functional Block Diagram

4

# Ordering Information

| Part Number | Temperature | Package                    | Marking | Moisture<br>Sensitivity<br>Level | Environmental<br>Information | Delivery Form                |

|-------------|-------------|----------------------------|---------|----------------------------------|------------------------------|------------------------------|

| AW99703CSR  | -40°C~85°C  | WLCSP<br>1.64mmX1.24mm-12B | X4LV    | MSL1                             | ROHS+HF                      | 3000 units/<br>Tape and Reel |

# Absolute Maximum Ratings(NOTE1)

| PARAMETERS                                                     | RANGE          |  |  |

|----------------------------------------------------------------|----------------|--|--|

| Supply voltage range VIN <sup>(NOTE 2)</sup>                   | -0.3V to 6V    |  |  |

| Voltage on PWM, HWEN, SCL, SDA (NOTE 2)                        | -0.3V to 6V    |  |  |

| Voltage on SW, OUT, HVLED1, HVLED2, HVLED3 <sup>(NOTE 2)</sup> | -0.3V to 43V   |  |  |

| Junction-to-ambient thermal resistance $\theta_{JA}$           | 80°C/W         |  |  |

| Operating free-air temperature range                           | -40°C to 85°C  |  |  |

| Operating Junction temperature T <sub>J</sub>                  | -40°C to 150°C |  |  |

| Storage temperature T <sub>STG</sub>                           | -65°C to 150°C |  |  |

| Lead Temperature (Soldering 10 Seconds)                        | 260°C          |  |  |

| ESD <sup>(NOTE 3)</sup>                                        |                |  |  |

| ALL PINS HBM (human body model) (NOTE 4)                       | ±2kV           |  |  |

| ALL PINS CDM (charge device model) (NOTE 5)                    | ±1.5kV         |  |  |

| Lat <mark>c</mark> h-up <sup>(NOTE 6)</sup>                    |                |  |  |

|                                                                | +IT: 200mA     |  |  |

| Latch-up current maximum rating per JEDEC standard             | -IT: -200mA    |  |  |

NOTE1: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

NOTE2: All voltage values are with respect to network ground terminal.

NOTE3: This integrated circuit can be damaged by ESD if you don't pay attention to ESD protection. AWINIC recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

NOTE4: The human body model is a 100pF capacitor discharged through a 1.5kΩ resistor into each pin. Test method: ANSI/ESDA/JEDEC

JS-001

NOTE5: Test Condition: ESDA/JEDEC JS-001-2017

NOTE6: Test Condition: JEDEC STANDARD NO.78E

# **Electrical Characteristics**

Minimum and maximum limits apply over the full operating ambient temperature range ( $-40^{\circ}C \le T_A \le 85^{\circ}C$ ), typical values are at  $T_A = 25^{\circ}C$ , and VIN = 3.6 V (unless otherwise noted).

| PARAMETER           |                                                          | TEST CONDITIONS                                                                   | MIN  | TYP  | MAX  | UNIT |

|---------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------|------|------|------|------|

| Power supply        |                                                          |                                                                                   |      |      |      |      |

| V <sub>IN</sub>     | Input operating range                                    |                                                                                   | 2.7  |      | 5.5  | V    |

| Ishdn               | Shutdown current                                         | Vin = 5.5V, HWEN = GND                                                            |      | 0.1  | 1    | μA   |

| Isb                 | Standby current                                          | Standby, VIN = 4.2V, HWEN =<br>SDA = SCL =1.8V                                    |      | 7    | 10   | μA   |

| UVLO                | Input under voltage<br>lockout                           | Rising edge                                                                       |      | 2.4  | 2.6  | V    |

| UVLO <sub>HYS</sub> | UVLO hysteresis                                          |                                                                                   |      | 0.15 |      | V    |

| Vpor                | Power on reset voltage                                   | falling edge                                                                      |      | 1.7  | 2    | V    |

| BOOST               |                                                          |                                                                                   |      | •    | •    |      |

| Іматсн              | LED current<br>matching ILED1 to<br>ILED2 to ILED3       | 50 $\mu$ A ≤ ILED ≤ 29.6 mA,<br>2.7 V ≤ VIN ≤ 5 V (linear or<br>exponential mode) | -1%  |      | +1%  |      |

| Accuracy            | Absolute accuracy<br>(ILED1,ILED2,<br>ILED3)             | 50 $\mu$ A ≤ ILED ≤ 29.6 mA,<br>2.7 V ≤ VIN ≤ 5 V (linear or<br>exponential mode) | -3%  |      | +3%  |      |

| ILED_MIN_LIN        | Minimum LED<br>current (per string)<br>with linear       | I <sup>2</sup> C current control at I <sub>FS</sub> =20mA                         | 8.8  | 9.77 | 10.7 | μA   |

| ILED_MIN_EXP        | Minimum LED<br>current (per string)<br>with exponential  |                                                                                   | 48.5 | 50   | 51.5 | μA   |

| ILED_MAX            | Maximum LED<br>current in Backlight<br>mode (per string) |                                                                                   | 28.8 | 29.6 | 30.4 | mA   |

| ILED_MAX_FL         | Maximum LED<br>current in flash mode<br>(per string)     |                                                                                   | 77.5 | 79.9 | 82.3 | mA   |

| .,                  | Regulated current                                        | ILED = 20mA                                                                       | 255  | 285  | 325  |      |

| V <sub>HR</sub>     | sink headroom<br>voltage                                 | ILED = 5 mA                                                                       | 120  | 150  | 180  | mV   |

| Vhr_min             | Current sink<br>minimum headroom<br>voltage              | ILED = 5mA down to 95%                                                            |      | 30   | 80   | mV   |

Dec. 2019 V1.2

| PAR                                    | AMETER                         | TEST CONDITIONS                                               |                                  | MIN  | ТҮР  | MAX  | UNIT |

|----------------------------------------|--------------------------------|---------------------------------------------------------------|----------------------------------|------|------|------|------|

| Efficiency                             | Typical efficiency             | V <sub>IN</sub> = 3.8 V, ILED<br>Typical (3P7S) Ap<br>circuit | 0.1                              |      | 87%  |      |      |

| RNMOS                                  | NMOS switch on resistance      | I <sub>sw</sub> = 250 mA                                      |                                  |      | 0.23 | 0.4  | Ω    |

|                                        |                                |                                                               | OCP = 00                         | 0.72 | 0.9  | 1.08 |      |

| Ilimit                                 | NMOS switch current            | 2.7V ≤ VIN ≤ 5V                                               | OCP = 01                         | 1.53 | 1.8  | 2.07 | A    |

|                                        | limit                          | 2.7 0 3 0111 3 50                                             | OCP = 10                         | 2.38 | 2.7  | 3.02 | ~ ~  |

|                                        |                                |                                                               | OCP = 11                         | 3.03 | 3.4  | 3.78 |      |

|                                        |                                |                                                               | OVP = 000                        | 16   | 17.5 | 19   |      |

|                                        |                                |                                                               | OVP = 001                        | 22.5 | 24   | 25.5 |      |

| Vovp                                   | Output overvoltage protection  | 2.7V≤ VIN ≤ 5V                                                | OVP = 010                        | 29.5 | 31   | 32.5 | V    |

|                                        | protection                     |                                                               | OVP = 011                        | 36.5 | 38   | 39.5 |      |

|                                        |                                |                                                               | OVP = 1XX                        | 40   | 41.5 | 43   |      |

| OVP Hysteresis                         |                                |                                                               |                                  |      | 0.5  |      | V    |

| fsw                                    | Switching frequency            | $2.7 \vee \leq \text{VIN} \leq 5 \vee$<br>boost frequency     | Boost<br>Frequency<br>select = 0 | 475  | 500  | 525  | kHz  |

|                                        |                                | shift = 0                                                     | Boost<br>Frequency<br>select = 1 | 950  | 1000 | 1050 |      |

| DMAX                                   | Maximum boost duty cycle       |                                                               |                                  | 92%  | 94%  |      |      |

| Over<br>Temperature<br>Protection(OTP) | IC thermal shutdown threshold  |                                                               |                                  |      | 160  |      | °C   |

| OTP<br>Hysteresis                      | IC thermal shutdown hysteresis |                                                               |                                  |      | 15   |      |      |

| LOGIC CONTRO                           | L                              |                                                               |                                  |      |      |      |      |

| Min f <sub>РWM</sub>                   | Minimum PWM input frequency    |                                                               |                                  |      |      | 50   | Hz   |

| Max fpwm                               | Maximum PWM input frequency    |                                                               |                                  | 50   |      |      | kHz  |

|                                        |                                | Sample rate = 24 MHz                                          |                                  |      |      | 183  |      |

| tmin_on                                | Minimum pulse ON<br>time       | Sample rate = 4 MHz                                           |                                  |      |      | 1100 | ns   |

|                                        |                                | Sample rate = 800 kHz                                         |                                  |      |      | 5500 |      |

7

Dec. 2019 V1.2

| PA                         | RAMETER                                   | TEST CONDITIONS                                                                     | MIN  | ТҮР  | MAX  | UNIT   |  |

|----------------------------|-------------------------------------------|-------------------------------------------------------------------------------------|------|------|------|--------|--|

|                            |                                           | Sample rate = 24 MHz                                                                |      |      | 183  |        |  |

| t <sub>MIN_OFF</sub>       | Minimum pulse OFF time                    | Sample rate = 4 MHz                                                                 |      |      | 1100 | 100 ns |  |

|                            |                                           | Sample rate = 800 kHz                                                               |      |      | 5500 |        |  |

| PWM <sub>RES</sub>         | Input PWM duty resolution                 | 1.6 kHz $\leq f_{PWM} \leq$ 12 kHz,<br>PWM hysteresis = 00, PWM<br>sample rate = 11 |      | 11   |      | bits   |  |

|                            |                                           | Sample rate = 24 MHz                                                                | 0.61 | 0.68 | 0.75 |        |  |

| tpwm_stby                  | PWM shutdown<br>period                    | Sample rate = 4 MHz                                                                 | 3.69 | 4.1  | 4.51 | ms     |  |

|                            | ponod                                     | Sample rate = 800 kHz                                                               | 18.4 | 20.5 | 22.6 |        |  |

| VIH                        | Input logic high                          | HWEN, PWM inputs                                                                    | 1.4  |      | VIN  | v      |  |

| VIL                        | Input logic low                           | HWEN, PWM inputs                                                                    | 0    |      | 0.4  | V      |  |

| R <sub>PDEN</sub>          | HWEN pull down resistor                   |                                                                                     | 300  | 400  | 500  | kΩ     |  |

| Rpdpwm                     | PWM pull down resistor                    |                                                                                     | 300  | 400  | 500  | kΩ     |  |

| tg⊔тсн                     | PWM input glitch rejection                | PWM pulse filter = 00                                                               |      | 0    | 15   | - ns   |  |

|                            |                                           | PWM pulse filter = 01                                                               | 60   | 100  | 140  |        |  |

|                            |                                           | PWM pulse filter = 10                                                               | 90   | 150  | 210  |        |  |

|                            |                                           | PWM pulse filter = 11                                                               | 120  | 200  | 280  |        |  |

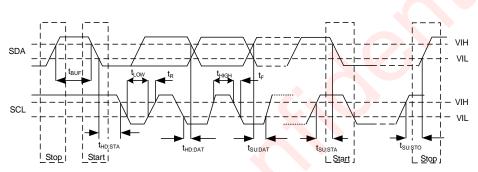

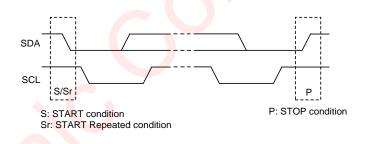

| I <sup>2</sup> C INTERFACI | E, see Figure1                            |                                                                                     |      |      |      |        |  |

| VIH                        | Input logic high                          |                                                                                     | 1.4  |      | VIN  | V      |  |

| VIL                        | Input logic low                           |                                                                                     | 0    |      | 0.4  | V      |  |

| Vol                        | SDA Output Logic<br>Low                   | I <sub>SDA</sub> = 3mA                                                              |      |      | 0.4  | V      |  |

| Fscl                       | Interface Clock<br>frequency              |                                                                                     |      |      | 400  | kHz    |  |

| THD: STA                   | (Repeat-start) Start condition hold time  |                                                                                     | 0.6  |      |      | μs     |  |

| TLOW                       | Low level width of SCL                    |                                                                                     | 1.3  |      |      | μs     |  |

| Тнідн                      | High level width of SCL                   |                                                                                     | 0.6  |      |      | μs     |  |

| Ts∪: STA                   | (Repeat-start) Start condition setup time |                                                                                     | 0.6  |      |      | μs     |  |

| THD: DAT                   | Data hold time                            |                                                                                     | 0    |      |      | μs     |  |

| T <sub>SU</sub> : DAT      | Data setup time                           |                                                                                     | 0.1  |      |      | μs     |  |

8

#### **OWINIC** 上海艾为电子技术股份有限公司 shanghai awinic technology co., ltd.

AW99703

Dec. 2019 V1.2

| PAF                  | RAMETER                               | TEST CONDITIONS | MIN | ТҮР | MAX | UNIT |

|----------------------|---------------------------------------|-----------------|-----|-----|-----|------|

| T <sub>R</sub>       | Rising time of SDA and SCL            |                 |     |     | 0.3 | μs   |

| T⊧                   | Falling time of SDA and SCL           |                 |     |     | 0.3 | μs   |

| T <sub>SU</sub> :STO | Stop condition setup time             |                 | 0.6 |     |     | μs   |

| TBUF                 | Time between start and stop condition |                 | 1.3 |     | 2   | μs   |

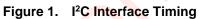

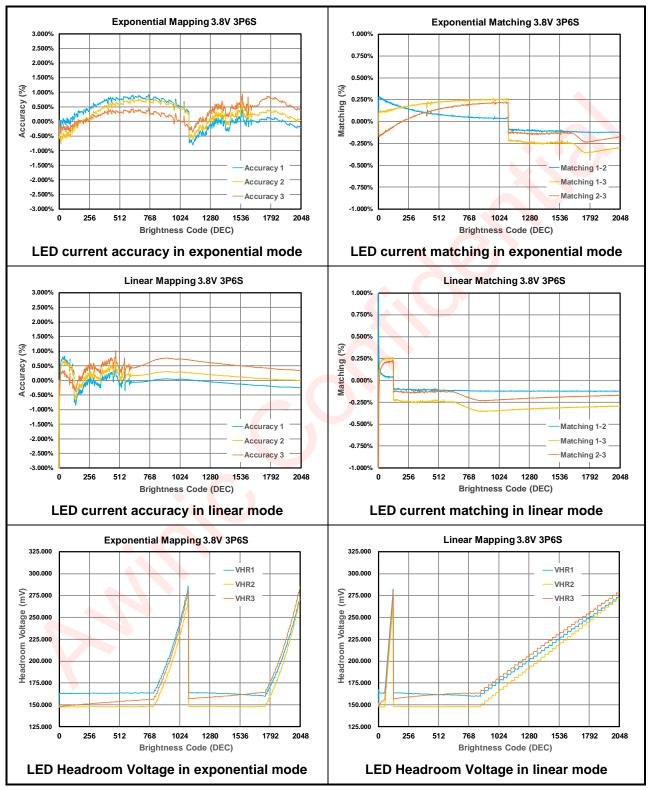

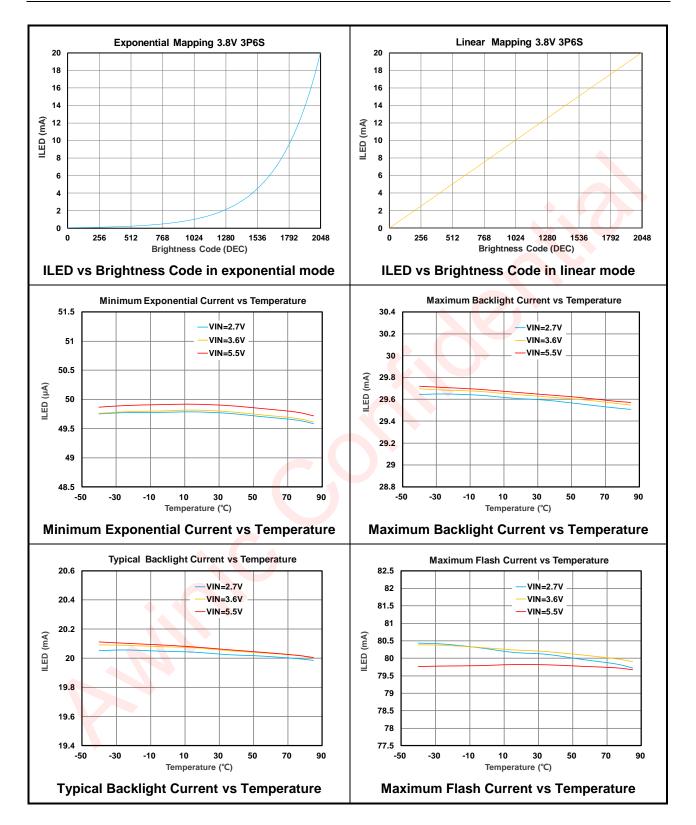

# **Typical Characteristics**

L=LPS4018-103ML and D=NSR0340V2T1G as noted in graphs, LEDs are 17-21/T1D-CP2R1TY/3T, temperature = 27°C, VIN = 3.8 V, unless otherwise noted.

#### **OWINIC** 上海艾为电子技术股份有限公司 shanghai awinic technology co., ltd.

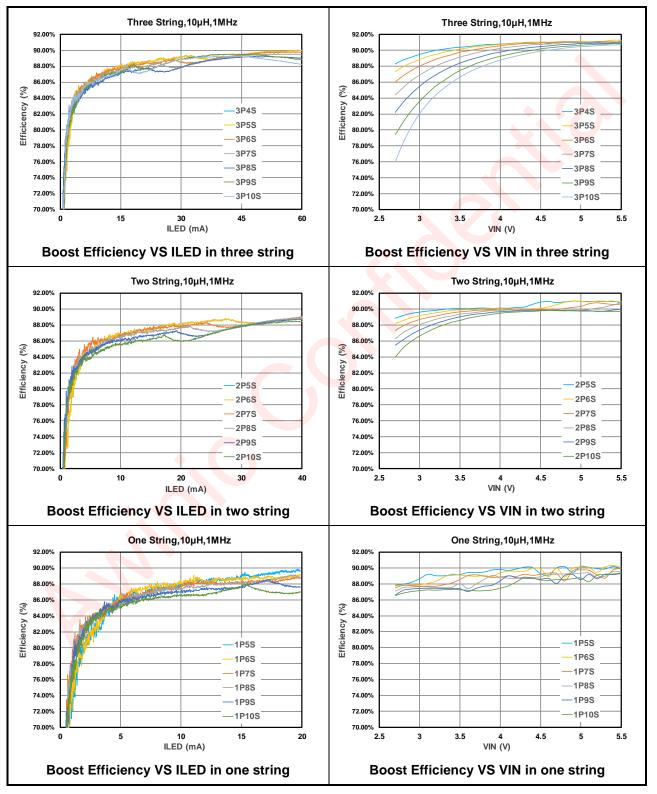

L=LPS4018-472ML and D=NSR0340V2T1G as noted in graphs, LEDs are 17-21/T1D-CP2R1TY/3T, temperature =  $27^{\circ}C$ , VIN = 3.8 V, unless otherwise noted.

#### **OWINIC** 上海艾为电子技术股份有限公司 shanghai awinic technology co., ltd.

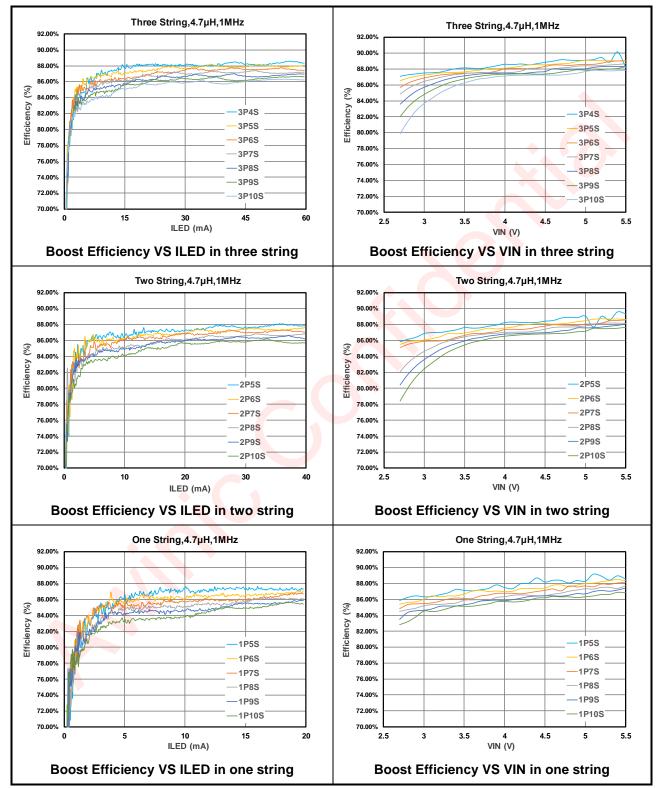

L=LPS4018-103ML and D=NSR0340V2T1G as noted in graphs, LEDs are 17-21/T1D-CP2R1TY/3T, temperature =  $27^{\circ}C$ , VIN = 3.8 V, unless otherwise noted.

# awinic 上海艾为电子技术股份有限公司 shanghai awinis technology sour ltd

# **Detailed Functional Description**

AW99703 is an inductive boost converter for WLED backlight display. AW99703 have three high-voltage LED strings with high current accuracy and string-to-string matching.

AW99703 supports 11 bits resolution analog dimming via I<sup>2</sup>C register set or via PWM duty changed. AW99703 also supports flash mode by enhancing sink current up to 79.9mA/string with the flash timeout protection.

#### Hardware Enable & Standby Mode

When HWEN is pulled low, AW99703 enters Shutdown mode, all I<sup>2</sup>C registers are reset to default state, and the I<sup>2</sup>C interface is disabled, the device will not respond to any I<sup>2</sup>C command.

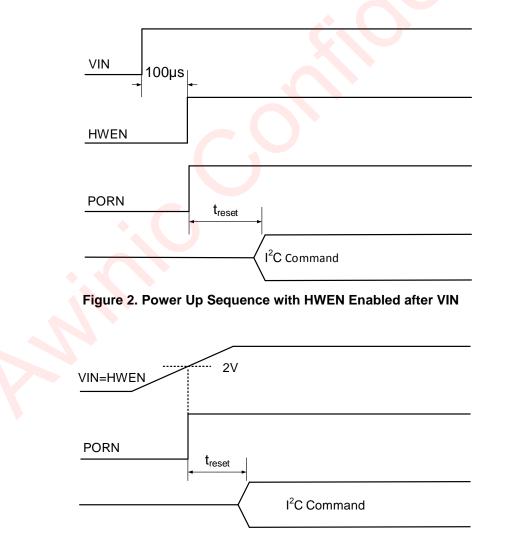

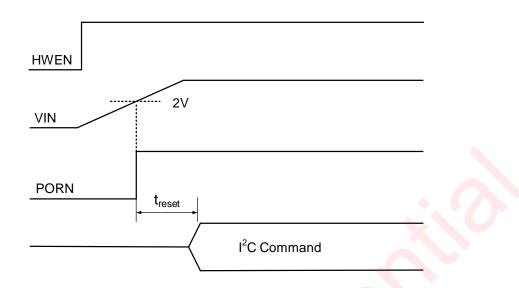

When HWEN is pulled high, the device goes into Standby mode, Whether the I<sup>2</sup>C interface is enabled depends on PORN state. When VIN>2V, PORN goes high and the device can respond to I<sup>2</sup>C command for at least treset=250µs.

Based on HWEN's connection and the power-up sequences, there are 3 situations shown in Figure 2,

#### Figure 3 and Figure 4.

Figure 3. Power Up Sequence with HWEN Tied to VIN

#### Figure 4. Power Up Sequence with HWEN Enabled before VIN

Both HWEN and I<sup>2</sup>C command can be used to turn off the LED current, but there are some differences:

If pulling HWEN low, the LED current will be turned off immediately without any ramp.

If HWEN is keeping high, the LED current will ramp down with a fixed time by controlling I<sup>2</sup>C command to turn off backlight/flash mode.

#### **Operation States**

awinic

AW99703 has 4 states referred to **Table 1**, which are switched by HWEN or I<sup>2</sup>C command. When HWEN is pulled low, AW99703 enters Shutdown state and the leakage current is less than 1µA.

If HWEN is pulled high without I<sup>2</sup>C command, device enters Standby state. If SCL/SDA's pull up voltage is much less than VIN voltage, it can cause a small leakage current and the current is less than 10µA.

| HWEN | Register<br>0x02[1:0] | States    |

|------|-----------------------|-----------|

| Low  | 00 (default)          | Shutdown  |

| High | 00                    | Standby   |

| High | 01                    | Backlight |

| High | 1X                    | Flash     |

#### Table 1. AW99703 Operating States

### Backlight I<sup>2</sup>C Dimming

AW99703 has 11-bit dimming level, including the 8-bit MSBs from LED Brightness MSB Register 0x07 Bits[7:0] and the 3-bit LSBs from LED Brightness LSB Register 0x06 Bits[2:0]. When programming 11-bit brightness code, the 3-bit LSBs should be programmed primarily, then the 8-bit MSBs are programmed.

There are two different shapes to map the dimming code to the LED current: linear and exponential, which are programmed by Mode Register 0x02 Bits[2]. These two modes determine the transfer characteristic of brightness code to LED current.

#### **Linear Mapping**

In the 11-bit linear mapped mode, per channel of the LED current follows the equation:

$$I_{LED_{BL}} = I_{FS} \times D_{PWM} \times \frac{Code}{2047}$$

(Code=0~2047)

where I<sub>FS</sub> is the backlight full-scale LED current, D<sub>PWM</sub> is the input PWM duty cycle if PWM dimming is enabled, otherwise D<sub>PWM</sub>=1, Code is an 11-bit I<sup>2</sup>C brightness code.

When 11-bit brightness code is set to 0, all current sinks and boost converter will be disabled, LED will be turned off.

#### **Exponential Mapping**

In the 11-bit exponential mapped mode, per channel of the LED current follows the equation:

$I_{LED_{BL}} = I_{FS} \times D_{PWM} \times \frac{1.002931237^{Code}}{400}$  (Code=1~2047)

When 11-bit brightness code is set to 0, all current sinks and boost converter will be disabled, LED will be turned off.

In the 11-bit exponential mapped mode, each code step (0.293%) is small enough under low LED current condition so that the transition from one code to the next is smooth to the human eye.

#### **Backlight PWM Dimming**

AW99703 converts the PWM input duty cycle into an 11-bit digital code D<sub>PWM</sub>. The PWM dimming function can be enabled or disabled by the Mode Register 0x02 Bit[4].

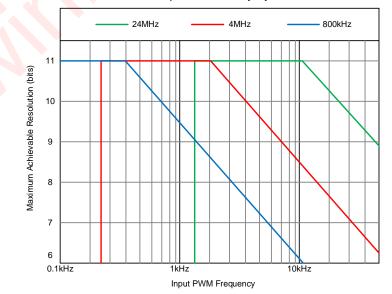

The PWM input frequency range is 50Hz to 50kHz, and there are three selectable sample rates (24MHz/4MHz/800kHz) for the PWM input, programmed by PWM Control Register 0x08 Bits[7:6].

To achieve the maximum resolution of PWM duty cycle, the input PWM duty cycle resolution must be  $\geq 11$  bits, and the PWM sample period (1/*f*<sub>SAMPLE</sub>) must be smaller than the minimum PWM input pulse width. Figure 5 shows the possible dimming resolutions based on the input PWM frequency.

For flash mode, the current is not related to the input PWM duty cycle.

16

#### Backlight PWM Hysteresis

awinic

PWM hysteresis helps filter out jitter of the PWM input that could cause LED flicker (especially at light currents), AW99703 owns seven selectable hysteresis settings to prevent jitter at the input PWM signal. The hysteresis only works during the opposite direction of PWM duty cycle change. When the change is larger or equal to the number of LSBs programmed, the output LED current starts to follow the change. Once the initial hysteresis has been overcome and the direction in duty cycle change remains the same, the PWM duty will change without hysteresis.

Table 2 shows the relationship between the minimum LSB(s) and the PWM duty cycle hysteresis. The drawback of setting PWM hysteresis too high is that the output current becomes less accurate due to the hysteresis.

| PWM Register 0x08 Bits[4:2] | Minimum LSB(s) | PWM Duty Cycle Hysteresis |

|-----------------------------|----------------|---------------------------|

| 000                         | 0              | 0/2047=0%                 |

| 001                         | 1 LSB          | 1/2047=0.049%             |

| 010                         | 2 LSBs         | 2/2047=0.098%             |

| 011                         | 3 LSBs         | 3/2047=0.147%             |

| 100                         | 4 LSBs         | 4/2047=0.195%             |

| 101                         | 5 LSBs         | 5/2047=0.244%             |

| 110                         | 6 LSBs         | 6/2047=0.293%             |

| 111                         | 7 LSBs         | 7/2047=0.342%             |

#### Table 2. PWM input Hysteresis

#### **PWM Timeout**

PWM timeout feature will turn off the boost output, if the PWM is enabled and there is no PWM pulse detected during some time. The timeout duration is determined by the PWM Sample Rate, so there is three minimum supported PWM input frequency corresponding to the PWM Sample Rate. The sample rate, timeout, minimum supported PWM frequency and maximum recommended PWM frequency for 11 bits resolution are summarized in Table 3.

| Table 3. | PWM | input | Hysteresis |

|----------|-----|-------|------------|

|----------|-----|-------|------------|

| SAMPLE RATE | TIMEOUT | MINIMUM SUPPORTED PWM<br>FREQUENCY | MAXIMUM RECOMMENDED<br>PWM FREQUENCY FOR 11<br>BITS RESOLUTION |

|-------------|---------|------------------------------------|----------------------------------------------------------------|

| 800kHz      | 20.5ms  | 50Hz                               | 390Hz                                                          |

| 4MHz        | 4.1ms   | 0.35kHz                            | 1.95kHz                                                        |

| 24MHz       | 0.68ms  | 1.6kHz                             | 11.7kHz                                                        |

### Full-scale LED Current in Backlight Mode

The full-scale LED current (I<sub>FS</sub>) is programmed by the LED current Register 0x03 Bits[7:3]. Full scale current ranges from 4.8mA to 29.6mA with 0.8mA/step and 20mA as the default. I<sub>FS</sub> is defined when PWM dimming duty cycle  $D_{PWM}$  is 100% and the I<sup>2</sup>C brightness code is 2047.

17

#### Flash LED Current

The flash LED current of every channel is programmed by Flash Setting Register 0x0b Bits[3:0].

The equation is:

$I_{LED\_FLASH} = \left(1 + \frac{Code\_FL + 2}{10}\right) \times 29.6mA \qquad (Code=0~15)$

Where Code\_FL is set by Flash Setting Register 0x0b Bits[3:0]. Flash current ranges from 35.52mA to 79.92mA, with 59.2mA as the default.

#### **Flash Timeout**

The flash timeout is programmed by Flash Setting Register 0x0b Bits[7:4] from 0ms to 1.5sec with 100ms/step, and default value is 500ms. If the switching frequency is shifted up or down, the flash timeout will be decreased or increased synchronously.

#### Turn On/Off Ramp

When AW99703 is enabled from Standby mode to backlight mode or flash mode, LED current ramp up time is programmed by Turn ON/OFF Ramp Register 0x09[7:4], When AW99703 is disabled to Standby mode, LED current ramp down time is programmed by Turn ON/OFF Ramp Register 0x09[3:0]. Both turn on and off time have 16 options, its range is from 512µs to 16384ms, with 8ms as default. Please note that if the switching frequency is shifted up or down, all ramp time will be decreased or increased synchronously.

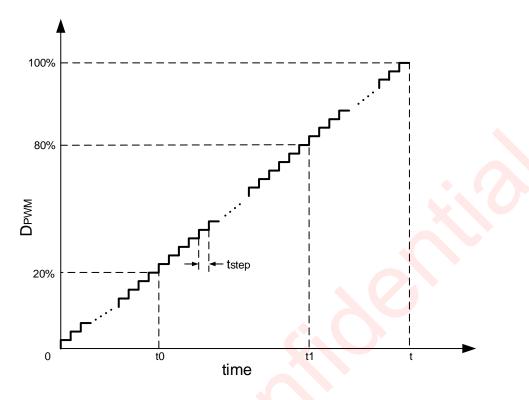

#### **Dimming Transition Ramp**

The transition ramp time can be programmed by Register 0x0a after the turn on ramp is done. If the LED current is changed from one to another by I<sup>2</sup>C brightness code or PWM duty cycle, the current transition ramp time will follow the value of the Register 0x0a programmed.

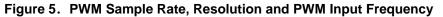

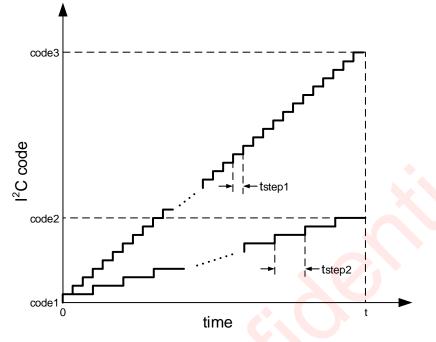

If the LED current is changed by I<sup>2</sup>C brightness code, the transition ramp time can be programmed by 0x0a Bits[3:0]. For Code 0001~1111, there are 15 programmable options (128ms ~ 4096ms) of the ramp time, it is the total time of ramp independent of the brightness code change as shown in **Figure 6**. The ramp time from code1 to code2 is the same as that from code1 to code3. For Code 0000, the slope of the ramp is a fixed value:  $t_{step}=1\mu s/step$ , so the final transition ramp time is dependent on the 11-bit brightness code change. As shown in **Figure 7**, the ramp time from code1 to code2 is equal to |code1-code2|x1µs/step.

awinic

Figure 6. Only I<sup>2</sup>C Transition Ramp when 0x0a bits[3:0]=0001~1111

Figure 7. Only I<sup>2</sup>C Transition Ramp when 0x0a bits[3:0]=0000

If the LED current is changed by PWM duty cycle, the transition ramp time can be programmed by 0x0a Bits[6:4], which determines the time of the duty cycle change from the minimum PWM duty cycle to the maximum PWM duty cycle. In other words, its slope is fixed, so the final transition ramp time is dependent on the change of the PWM duty cycle.

Figure 8. Only PWM Transition Ramp

As shown in **Figure 8**, 0x0a[6:4] determine how long it takes from  $D_{PWM}=0$  to  $D_{PWM}=100\%$ , which is t. Therefore, if  $D_{PWM}$  is changed from 20% to 80%, the ramp time t1-t0=(80%-20%)×t. In other words, the different PWM ramp time decides the different t<sub>step</sub>.

When the system switches between backlight mode and flash mode, the LED current transition ramp time will always choose 1µs/step of I<sup>2</sup>C brightness code and PWM duty cycle change, to minimize the transition time. Please note that if the switching frequency is shifted up or down, all ramp time will be decreased or increased synchronously.

#### Channel Enable/Disable

awinic

All channels are enabled as default and can be enabled or disabled through LED Current Register 0x03 Bits [2:0].

### Switching Frequency

There are two switching frequencies of boost converter to be programmed by Control Register 0x04 Bit[5]: 500kHz and 1MHz, with 1MHz as default. Once the switching frequency is set, this nominal value can be shifted up or down via 0x04 Bits[7:6]. This function is to prevent switching noise interference if the selected switching frequency is within the sensitive frequency range of the system. The adjustment of the switching frequency can optimize the efficiency under load current condition.

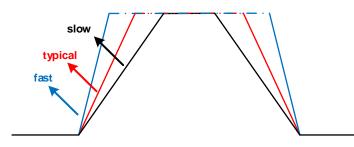

### **EMI** Reduction

Programmable Slew Rate Control uses a combinational drivers for boost switch. Enabling all drivers allows boost switch on/off transition time to be the shortest, enabling just one driver allows boost switch on/off transition time to be the longest. The longer the transition time, the lower the switching noise on the SW pin. Note that the shortest transition time brings the best efficiency as the switching losses are the lowest.

**Figure 9** shows the EMI programmable steps, and the Programmable Slew Rate Control operates at the Boost Control2 Register 0x05 Bits[5:3].

Figure 9. EMI Reduction Operation

#### Auto-Switching Frequency

awinic

In order to optimize efficiency between frequency and load current, the AW99703 provides an automatic frequency change mode. This function can be enabled or disabled by Boost Control2 Register 0x05 Bit[7], with disabled as default. When this function is disabled, the switching frequency operates at the programmed frequency (Register 0x04 Bit[5]), no matter what LED current is.

Auto-frequency mode operates through 2 programmable registers: Auto Frequency High Threshold (Register 0x0c) and Auto Frequency Low Threshold (0x0d). The boost switching frequency is determined by the comparison results between 8 MSBs of the brightness register (Register 0x07) and 8-bit High/Low Threshold. The high threshold determines the switchover from 1MHz to 500kHz. The low threshold determines the switchover from 500kHz to 250kHz. Please note that the 250kHz frequency is only accessible in auto-frequency mode and its maximum duty ( $D_{MAX}$ ) cycle is restricted to 50%. Table 4 details the boundaries for this mode. Table 5 provides a guideline for the low threshold setting, the actual setting needs to be verified in the application.

| BRIGHTNESS CODE MSBs (Register 0x07 Bits[7:0])                                                                            | BOOST SWITCHING FREQUENCY |

|---------------------------------------------------------------------------------------------------------------------------|---------------------------|

| <auto (register="" 0x0d="" bits[7:0])<="" frequency="" low="" td="" threshold=""><td>250 kHz (DMAX = 50%)</td></auto>     | 250 kHz (DMAX = 50%)      |

| > Auto Frequency Low Threshold (Register 0x0d Bits[7:0]) and < Auto Frequency High<br>Threshold (Register 0x0c Bits[7:0]) | 500 kHz                   |

| ≥ Auto Frequency High Threshold Register 0x0c Bits[7:0])                                                                  | 1 MHz                     |

#### Table 4. Auto-Switching Frequency Operation

#### Table 5. Auto Frequency 250 kHz Threshold Settings

| $\begin{array}{c} \text{CONDITION} \\ \text{(V}f = 3.2 \text{ V, ILED} = 25 \text{ mA)} \end{array}$ | INDUCTOR (µH) | RECOMMENDED AUTO FREQUENCY<br>LOW THRESHOLD MAXIMUM VALUE<br>(NO SHIFT) | OUTPUT POWER AT AUTO<br>FREQUENCY SWITCHOVER<br>(W) |

|------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------|-----------------------------------------------------|

| 3 × 4 LEDs                                                                                           | 10            | 0x17                                                                    | 0.079                                               |

| 3 × 5 LEDs                                                                                           | 10            | 0x15                                                                    | 0.089                                               |

| 3 × 6 LEDs                                                                                           | 10            | 0x13                                                                    | 0.097                                               |

| 3 × 7 LEDs                                                                                           | 10            | 0x11                                                                    | 0.101                                               |

| 3 × 8 LEDs                                                                                           | 10            | OxOf                                                                    | 0.102                                               |

#### Inductor Select

The AW99703 can use inductors in the range of  $4.7\mu$ H to  $10\mu$ H. In order to optimize the converter loop response, the minimum inductor select bit Boost Control Register 0x05 Bit[6] should be set depending on which value of inductance is chosen. For  $10\mu$ H inductors, this bit should be set to 1. For less than  $10\mu$ H, this bit should be set to 0.

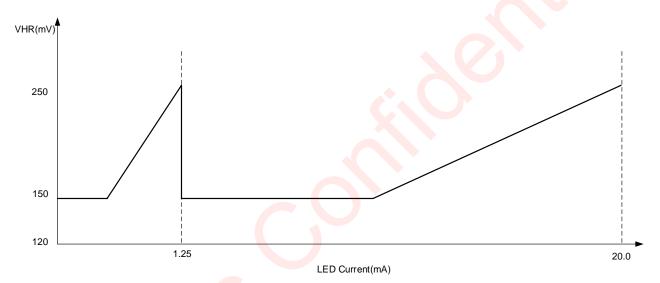

#### Auto Headroom Voltage

The adaptive headroom voltage (VHR) regulates the output voltage to supply the necessary minimal headroom voltage for the current sinks to provide the set ILED current. **Figure 10** shows the typical variation of VHR with LED current. It is implied that the reference voltage of Error Amplifier is adjusted with the LED current changing, since the current sinks need less headroom at lower LED current than at higher LED current.

Figure 10. AW99703 Typical Regulated Headroom Voltage vs Programmed LED Current

#### **Over Voltage Protection (OVP)**

The OVP block monitors the boost output voltage ( $V_{OUT}$ ) and protects OUT and SW from exceeding safe operating voltages. There are five programmable OVP thresholds (17.5V, 24V, 31V, 38V and 41.5V) by Boost Control1 Register 0x04 Bits[4:2].

After OVP Flag is set, user needs to restart the IC by toggling HWEN or sending software reset command or reading back fault register.

### **Over Current Protection (OCP)**

The OCP (over current protection) protects device from high current density by a cycle-by-cycle current limit of internal high voltage NFET. Once inductor peak current exceeds the threshold, the NFET will be turn off immediately. Then the OCP Flag is set and latched. The AW99703 has four selectable OCP thresholds (900mA,1800mA, 2700mA and 3400mA). These are programmable in Boost Control1 Register 0x04 Bits[1:0].

After OCP Flag is set, user needs to restart the IC by toggling HWEN or sending software reset command or reading back fault register .

#### **Over Temperature Protection (OTP)**

OTP (Over temperature protection) function monitors the IC's junction temperature in real-time. If it reaches 165°C, the boost converter stops switching and current sinks are all disabled. Once it drops by 15°C, the chip will resume to its previous settings.

If temperature goes above 165°C for more than 64µs, the OTP Flag is set and latched. After OTP Flag is set, user needs to restart the IC by toggling HWEN or sending software reset command or reading back fault register.

#### **LED Fault Detection**

awinic

AW99703 is equipped with LED short/open detection function. LED short condition can be detected when the voltage between  $V_{OUT}$  and any enabled current sink input has dropped below 1V. LED open condition can be detected when any enabled current sink input  $\leq 40$ mV at the rising edge of OVP Flag.

#### UVLO

Under voltage lock-out (UVLO) is integrated to detect the input voltage VIN. Once VIN drops below UVLO falling threshold, the current sinks are disabled and the boost converter stops switching. If VIN increases above UVLO rising threshold, the boost converter and the current sinks will resume to their previous settings.

#### Software Reset

Writing 0x01 to Soft Reset Register 0x01 Bit[0] via I<sup>2</sup>C interface will reset all internal circuits and configuration registers. Then the device will not respond to any I<sup>2</sup>C command for 2ms.

# **I<sup>2</sup>C Interface**

The device supports the I<sup>2</sup>C serial bus and data transmission protocol. It operates as a slave on the I<sup>2</sup>C bus. The maximum clock frequency specified by the I<sup>2</sup>C standard is 400kHz. Connect to the bus are made via the open-drain I/O pins SCL and SDA. The pull-up resistor can be selected in the range of  $1k\Omega$ ~10k $\Omega$  and the typical value is 4.7k $\Omega$  when I<sup>2</sup>C frequency is 400kHz. Different high level from 1.8V to 3.3V of this I<sup>2</sup>C interface is supported.

#### **Device Address**

AW99703 7-bit slave address (A7~A1) is 0110110 binary (0x36H). After the START condition, the I<sup>2</sup>C master sends the 7-bit device address followed by an eighth (A0) read or write bit (R/W). R/W= 0 indicates a WRITE and R/W = 1 indicates a READ.

|    | Table 6. Device Address |    |    |    |    |    |     |  |  |  |

|----|-------------------------|----|----|----|----|----|-----|--|--|--|

| A7 | A6                      | A5 | A4 | A3 | A2 | A1 | A0  |  |  |  |

| 0  | 1                       | 1  | 0  | 1  | 1  | 0  | R/W |  |  |  |

### I<sup>2</sup>C Start/Stop

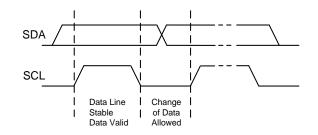

I<sup>2</sup>C start: SDA changes from high level to low level when SCL is high level. I<sup>2</sup>C stop: SDA changes from low level to high level when SCL is high level.

Figure 11. I<sup>2</sup>C Start/Stop Condition Timing

### **Data Validation**

When SCL is high level, SDA level must be constant. SDA can be changed only when SCL is low level.

Figure 12. Data Validation Diagram

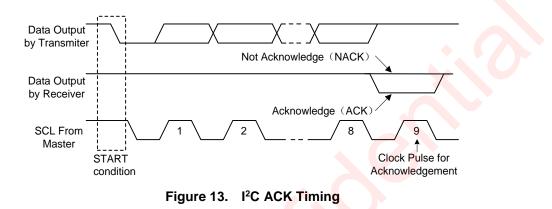

#### ACK (Acknowledgement)

awinic

ACK means the successful transfer of I<sup>2</sup>C bus data. After master sends an 8-bit data, SDA must be released; SDA is pulled to GND by slave device when slave acknowledges.

When master reads, slave device sends 8-bit data, releases the SDA and waits for ACK from master. If ACK is send and I<sup>2</sup>C stop is not send by master, slave device sends the next data. If ACK is not send by master, slave device stops to send data and waits for I<sup>2</sup>C stop.

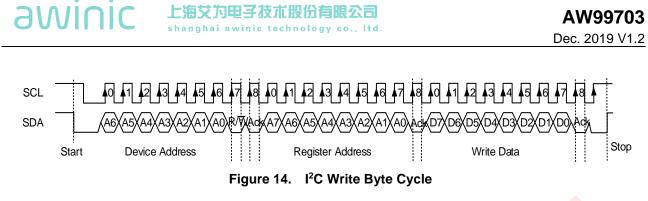

#### Write Cycle

One data bit is transferred during each clock pulse. Data is sampled during the high state of the serial clock (SCL). Consequently, throughout the clock's high period, the data should remain stable. Any changes on the SDA line during the high state of the SCL and in the middle of a transaction, aborts the current transaction. New data should be sent during the low SCL state. This protocol allows a single data line to transfer both command/control information and data using the synchronous serial clock.

Each data transaction is composed of a start condition, a number of byte transfers (set by the software) and a stop condition to terminate the transaction. Every byte written to the SDA bus must be 8 bits long and is transferred with the most significant bit first. After each byte, an Acknowledge signal must follow.

In a write process, the following steps should be followed:

- a) Master device generates START condition. The "START" signal is generated by lowering the SDA signal while the SCL signal is high.

- b) Master device sends slave address (7-bit) and the data direction bit (R/W = 0).

- c) Slave device sends acknowledge signal if the slave address is correct.

- d) Master sends control register address (8-bit)

- e) Slave sends acknowledge signal

- f) Master sends data byte to be written to the addressed register

- g) Slave sends acknowledge signal

- h) If master will send further data bytes the control register address will be incremented by one after acknowledge signal (repeat step f and g)

- i) Master generates STOP condition to indicate write cycle end

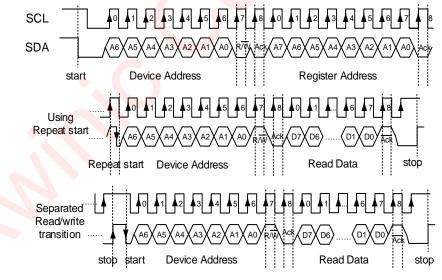

### **Read Cycle**

In a read cycle, the following steps should be followed:

- a) Master device generates START condition

- b) Master device sends slave address (7-bit) and the data direction bit (R/W = 0).

- c) Slave device sends acknowledge signal if the slave address is correct.

- d) Master sends control register address (8-bit)

- e) Slave sends acknowledge signal

- f) Master generates STOP condition followed with START condition or REPEAT START condition

- g) Master device sends slave address (7-bit) and the data direction bit (R/W = 1).

- h) Slave device sends acknowledge signal if the slave address is correct.

- i) Slave sends data byte from addressed register.

- j) If the master device sends acknowledge signal, the slave device will increase the control register address by one, then send the next data from the new addressed register.

- k) If the master device generates STOP condition, the read cycle is ended.

Figure 15. I<sup>2</sup>C Read Byte Cycle

| ADDR | NAME    | R/W | Bit7        | Bit6               | Bit5        | Bit4         | Bit3         | Bit2         | Bit1  | Bit0  | Default |

|------|---------|-----|-------------|--------------------|-------------|--------------|--------------|--------------|-------|-------|---------|

| 0x00 | ID      | R   |             |                    |             | CI           | HIP_ID       |              |       |       | 0x03    |

| 0x01 | SFTRST  | R/W |             |                    |             | R            |              |              |       | RESET | 0x00    |

| 0x02 | MODE    | R/W |             | R                  |             | PDIS         | R            | MAP          | WORK  | MODE  | 0x00    |

| 0x03 | LEDCUR  | R/W |             |                    | BL_FS       |              |              | <b>CH3EN</b> | CH2EN | CH1EN | 0x9F    |

| 0x04 | BSTCTR1 | R/W | SF_         | _SFT               | SF          | OVF          | SEL          |              | OCF   | PSEL  | 0x2E    |

| 0x05 | BSTCTR2 | R/W | AFEN        | AFEN INDSEL EMISEL |             |              |              |              | 0x00  |       |         |

| 0x06 | LEDLSB  | R/W |             |                    | R           |              |              |              | LSB 🔷 |       | 0x07    |

| 0x07 | LEDMSB  | R/W |             | MSB                |             |              |              |              |       | 0xFF  |         |

| 0x08 | PWM     | R/W | P_          | _SF                | P_ACT       |              | P_HYS        | P_HYS P_FLT  |       |       | 0x93    |

| 0x09 | TURNCFG | R/W |             | ON                 | _TIM        |              |              | OFF          |       |       | 0x44    |

| 0x0A | TRANCFG | R/W | R           |                    | PWM_TIM     | l            |              | IIC_TIM      |       |       | 0x00    |

| 0x0B | FLASH   | R/W |             | FLT                | D_TIM       |              |              | FL           | S     |       | 0x58    |

| 0x0C | AFHIGH  | R/W |             |                    |             | AF           | _HIGH        | XX           |       |       | 0x80    |

| 0x0D | AFLOW   | R/W |             | AF_LOW             |             |              |              |              |       | 0x10  |         |

| 0x0E | FLAGS1  | R   | CH1<br>OPEN | CH2<br>OPEN        | CH3<br>OPEN | CH1<br>SHORT | CH2<br>SHORT | CH3<br>SHORT | OCP   | ОТ    | 0x00    |

| 0x0F | FLAGS2  | R   | OVP         | UVLO               | FLTO        |              |              | R            |       |       | 0x00    |

# **Register Configuration**<sup>(NOTE7)</sup>

NOTE7: The default value refers to the set value of the registers when the chip is manufactured, which is the recommendation setting to maintain the overall function and good performance of the chip as well.

### **Register Detailed Description**

#### ID : CHIP ID Register (Address 00H)

| Bit | Symbol  | R/W | Description | Default |

|-----|---------|-----|-------------|---------|

| 7:0 | CHIP_ID | R   | CHIP ID     | 0x03    |

#### SFTRST : Soft Reset Register (Address 01H)

| Bit | Symbol | R/W | Description                                                                  | Default |

|-----|--------|-----|------------------------------------------------------------------------------|---------|

| 7:1 | -      | R   | Reserved                                                                     |         |

| 0   | RESET  | R/W | Soft reset<br>0: Don't reset (default)<br>1: Reset (automatically back to 0) | 0x00    |

#### MODE : Mode Register (Address 02H)

| Bit | Symbol | R/W | Description                                              | Default |

|-----|--------|-----|----------------------------------------------------------|---------|

| 7:5 | -      | R   | Reserved                                                 |         |

| 4   | PDIS   | R/W | PWM dimming disable<br>0: enable (default)<br>1: disable | 0x00    |

| 3   | -      | R   | Reserved                                                 |         |

| 2   | MAP    | R/W | Map type                                                 |         |

# **るいでに、上海艾为电子技术股份有限公司** shanghai awinic technology co., ltd.

# AW99703

Dec. 2019 V1.2

| Bit | Symbol   | R/W | Description                                                      | Default |

|-----|----------|-----|------------------------------------------------------------------|---------|

|     |          |     | 0: exponential (default)                                         |         |

|     |          |     | 1: linear                                                        |         |

| 1:0 | WORKMODE | R/W | Work mode<br>00: standby (default)<br>01: backlight<br>1x: flash |         |

#### LEDCUR : LED Current Register (Address 03H)

| Bit | Symbol | R/W | Description                                                                                                                                      | Default |

|-----|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7:3 | BL_FS  | R/W | Backlight full scale current<br>IFS = 4.8mA + code × 0.8mA<br>00000 = 4.8mA<br>00001 = 5.6mA<br><br>10011 = 20mA (default)<br><br>11111 = 29.6mA |         |

| 2   | CH3EN  | R/W | CH3 enable<br>0: disable<br>1: enable (default)                                                                                                  | 0x9F    |

| 1   | CH2EN  | R/W | CH2 enable<br>0: disable<br>1: enable (default)                                                                                                  |         |

| 0   | CH1EN  | R/W | CH1 enable<br>0: disable<br>1: enable (default)                                                                                                  |         |

#### BSTCTR1 : Boost Control1 Register (Address 04H)

| Bit | Symbol | R/W | Description                                                                                                                  | Default |

|-----|--------|-----|------------------------------------------------------------------------------------------------------------------------------|---------|

| 7:6 | SF_SFT | R/W | Switching frequency shift<br>00: No Shift (default)<br>01: Shift Up by 17%<br>10: Shift Down by 11%<br>11: Shift Down by 19% |         |

| 5   | SF     | R/W | Switching frequency<br>0: 500kHz<br>1: 1000kHz (default)                                                                     | 0x2E    |

| 4:2 | OVPSEL | R/W | Over voltage protect select<br>000: 17.5V<br>001: 24V<br>010: 31V<br>011: 38V (default)<br>1xx: 41.5V                        | UXZE    |

| 1:0 | OCPSEL | R/W | Over current protect select<br>00: 0.9A                                                                                      |         |

# **awinic** 上海艾为电子技术股份有限公司 shanghai awinic technology co., Itd.

# AW99703

Dec. 2019 V1.2

| Bit | Symbol | R/W | Description        | Default |

|-----|--------|-----|--------------------|---------|

|     |        |     | 01: 1.8A           |         |

|     |        |     | 10: 2.7A (default) |         |

|     |        |     | 11: 3.4A           |         |

#### BSTCTR1 : Boost Control2 Register (Address 05H)

| Bit | Symbol | R/W | Description                                                                                                                            | Default |

|-----|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7   | AFEN   | R/W | Auto frequency enable<br>0: disable (default)<br>1: enable                                                                             |         |

| 6   | INDSEL | R/W | Inductor select<br>0: 4.7µH (default)<br>1: 10µH                                                                                       |         |

| 5:3 | EMISEL | R/W | EMI Select<br>000: typical (default)<br>001: slow3<br>010: slow2<br>011: slow1<br>100: fast1<br>101: fast2<br>110: fast3<br>111: fast4 | 0x00    |

| 2:0 | -      | R   | Reserved                                                                                                                               |         |

#### LEDLSB : LED Brightness LSB Register (Address 06H)

| Bit | Symbol | R/W | Description                   | Default |

|-----|--------|-----|-------------------------------|---------|

| 7:3 | -      | R/W | Reserved                      | 0x07    |

| 2:0 | LSB    | R/W | LED brightness lower 3bit LSB | 0x07    |

#### LEDMSB : LED Brightness MSB Register (Address 07H)

| Bit | Symbol | R/W | Description                    | Default |

|-----|--------|-----|--------------------------------|---------|

| 7:0 | MSB    | R/W | LED brightness higher 8bit MSB | 0xFF    |

#### PWM : PWM Control Register (Address 08H)

| Bit | Symbol | R/W | Description                                                      | Default |

|-----|--------|-----|------------------------------------------------------------------|---------|

| 7:6 | P_SF   | R/W | PWM sample rate<br>00: 800kHz<br>01: 4MHz<br>1x: 24MHz (default) |         |

| 5   | P_ACT  | R/W | PWM active<br>0: high active (default)<br>1: low active          | 0x93    |

| 4:2 | P_HYS  | R/W | PWM hysteresis<br>000: none<br>001: 1 LSB                        |         |

Dec. 2019 V1.2

| Bit | Symbol | R/W | Description                                                                                      | Default |

|-----|--------|-----|--------------------------------------------------------------------------------------------------|---------|

|     |        |     | 010: 2 LSBs<br>011: 3 LSBs<br>100: 4 LSBs (default)<br>101: 5 LSBs<br>110: 6 LSBs<br>111: 7 LSBs |         |

| 1:0 | P_FLT  | R/W | PWM filter<br>00: no filter<br>01: 100ns<br>10: 150ns<br>11: 200ns (default)                     | 2       |

#### TURNSET : Turn ON/OFF Ramp Time Register (Address 09H)

| Bit | Symbol  | R/W | Description                                                                                                                                                                                                                                                            | Default |

|-----|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7:4 | ON_TIM  | R/W | Turn on ramp time<br>0000: 512µs<br>0001: 1ms<br>0010: 2ms<br>0011: 4ms<br>0100: 8ms (default)<br>0101: 16ms<br>0110: 32ms<br>0111: 64ms<br>1000: 128ms<br>1001: 256ms<br>1010: 512ms<br>1011: 1024ms<br>1100: 2048ms<br>1101: 4096ms<br>1110: 8192ms<br>1111: 16384ms | 0x44    |

| 3:0 | OFF_TIM | R/W | Turn off ramp time<br>0000: 512µs<br>0001: 1ms<br>0010: 2ms<br>0011: 4ms<br>0100: 8ms (default)<br>0101: 16ms<br>0110: 32ms<br>0111: 64ms<br>1000: 128ms<br>1001: 256ms<br>1010: 512ms<br>1011: 1024ms<br>1101: 2048ms<br>1101: 4096ms                                 |         |

Dec. 2019 V1.2

| Bit | Symbol | R/W | Description   | Default |

|-----|--------|-----|---------------|---------|

|     |        |     | 1110: 8192ms  |         |

|     |        |     | 1111: 16384ms |         |

#### TRANSET : Transition Ramp Time Register (Address 0AH)

| Bit | Symbol  | R/W | Description                                                                                                                                                                                                                                                                                             | Default |

|-----|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7   | -       | R   | Reserved                                                                                                                                                                                                                                                                                                |         |

| 6:4 | PWM_TIM | R/W | PWM transition ramp time<br>000: 2ms (default)<br>001: 4ms<br>010: 8ms<br>011: 16ms<br>100: 32ms<br>101: 64ms<br>110: 128ms<br>111: 256ms                                                                                                                                                               |         |

| 3:0 | IIC_TIM | R/W | I <sup>2</sup> C transition ramp time<br>0000: 1µs/step (default)<br>0001: 128ms<br>0010: 192ms<br>0011: 256ms<br>0100: 320ms<br>0101: 384ms<br>0110: 448ms<br>0111: 512ms<br>1000: 576ms<br>1001: 640ms<br>1010: 768ms<br>1011: 1024ms<br>1100: 1280ms<br>1101: 1536ms<br>1110: 2560ms<br>1111: 4096ms | 0x00    |

### FLASH : Flash Setting Register (Address 0BH)

| Bit | Symbol   | R/W | Description                                                                                                                                                                                   | Default |

|-----|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7:4 | FLTO_TIM | R/W | Flash timeout time<br>0000: no flash timeout<br>0001: 100ms<br>0010: 200ms<br>0011: 300ms<br>0100: 400ms<br>0101: 500ms (default)<br>0110: 600ms<br>0111: 700ms<br>1000: 800ms<br>1001: 900ms | 0x58    |

31

Dec. 2019 V1.2

| Bit | Symbol | R/W | Description                                     | Default |

|-----|--------|-----|-------------------------------------------------|---------|

|     |        |     | 1010: 1000ms                                    |         |

|     |        |     | 1011: 1100ms                                    |         |

|     |        |     | 1100: 1200ms                                    |         |

|     |        |     | 1101: 1300ms                                    |         |

|     |        |     | 1110: 1400ms                                    |         |

|     |        |     | 1111: 1500ms                                    |         |

|     |        |     | Flash current                                   |         |

|     |        |     | $I_{FLASH} = (1 + (code + 2)/10) \times 29.6mA$ |         |

|     |        |     | 0000: 35.52mA                                   |         |

|     |        |     | 0001: 38.48mA                                   |         |

| 3:0 | FL_S   | R/W |                                                 |         |

|     |        |     | 1000: 59.2mA (default)                          |         |

|     |        |     |                                                 |         |

|     |        |     | 1110: 76.96mA                                   |         |

|     |        |     | 1111: 79.92mA                                   |         |

#### AFHIGH : Auto Frequency High Threshold Register (Address 0CH)

| Bit | Symbol  | R/W | Description                         | Default |

|-----|---------|-----|-------------------------------------|---------|

| 7:0 | AF_HIGH | R/W | Auto frequency high threshold value | 0x80    |

#### AFLOW : Auto Frequency Low Threshold Register (Address 0DH)

| Bit | Symbol | R/W | Description                        | Default |

|-----|--------|-----|------------------------------------|---------|

| 7:0 | AF_LOW | R/W | Auto frequency low threshold value | 0x10    |

#### FLAG1 : FLAGS1 Register (Address 0EH)

| Bit | Symbol    | R/W | Description                      | Default |

|-----|-----------|-----|----------------------------------|---------|

| 7   | LED10PEN  | R/W | Channel 1 open flag              |         |

| 6   | LED2OPEN  | R/W | Channel 2 open flag              |         |

| 5   | LED3OPEN  | R/W | Channel 3 open flag              |         |

| 4   | LED1SHORT | R/W | Channel 1 short flag             | 0x00    |

| 3   | LED2SHORT | R/W | Channel 2 short flag             | 0000    |

| 2   | LED3SHORT | R/W | Channel 3 short flag             |         |

| 1   | OCP       | R/W | Over current protection flag     |         |

| 0   | ОТ        | R/W | Over temperature protection flag |         |

#### FLAG2 : FLAGS2 Register (Address 0FH)

| Bit | Symbol | R/W | Description                  | Default |

|-----|--------|-----|------------------------------|---------|

| 7   | OVP    | R/W | Over voltage protection flag |         |

| 6   | UVLO   | R/W | UVLO flag                    | 0x00    |

| 5   | FL_TO  | R/W | Flash timeout flag           | 0,000   |

| 4:0 | -      | R   | Reserved                     |         |

# **Application Information**

#### **Inductor Selection Guideline**

Because the selection of inductor affects power supply's steady state operation, transient behavior, loop stability and the boost converter efficiency, the inductor is one of the most important components in switching power regulator design. There are three important inductor specifications, inductor value, DC resistance and saturation current.

The inductor DC current can be calculated as:

$$I_{\text{IN}_{\text{DC}}} = \frac{V_{\text{OUT}} \times I_{\text{out}}}{V_{\text{IN}} \times \eta}$$

The inductor current peak to peak ripple can be calculated as

$$I_{PP} = \frac{1}{L \times F_{s} \times (\frac{1}{V_{OUT} + V_{F} - V_{IN}} + \frac{1}{V_{IN}})}$$

Therefore, the peak current IP seen by the inductor is calculated as

$$I_{\rm P} = I_{\rm IN_DC} + \frac{I_{\rm PP}}{2}$$

The inductor saturation current rating should be considered to cover the inductor peak current. Smaller size and better efficiency are the major concerns for portable devices. The inductor should have low core loss and low DCR for better efficiency. For these reasons, a  $4.7\mu$ H to  $10\mu$ H inductor value range is recommended for backlight mode. A  $10\mu$ H inductor optimized the efficiency for most application while maintaining low inductor peak to peak ripple. Table 7 lists the recommended inductor for the AW99703. When recommending inductor value, the factory has considered –40% and +20% tolerance from its nominal value.

| Part<br>Number    | L<br>(µH) | DCR Max<br>(Ω) | Saturation Current<br>(mA) | Size<br>(L x W x H mm) | Vendor    |

|-------------------|-----------|----------------|----------------------------|------------------------|-----------|

| MRSC252A10-100M-N | 10        | 0.5            | 900                        | 2.5 x 2 x 1            | Chilisin  |

| LQH3NPN100NM0     | 10        | 0.3            | 750                        | 3 x 3 x 1.5            | Murata    |

| CDH3809/SLD       | 10        | 0.3            | 570                        | 4 x 4 x 1.0            | Sumida    |

| LPS4018-472ML     | 4.7       | 0.125          | 1900                       | 4 x 4 x 1.8            | Coilcraft |

Table 7. Recommended Inductors for AW99703 at backlight mode

### Schottky Diode Selection

To optimize the efficiency, a high-speed and low reverse-recovery current Schottky diode are recommended. Make sure the diode's average and peak current ratings exceed the output average LED current and the peak inductor current. In addition, the diode's break-down voltage rating must exceed the maximum voltage across the diode. Usually, unexpected high-frequency voltage spikes can be seen across the diode when the diode turns off. Therefore, leaving some voltage rating margin is always needed to guarantee normal long-term operation when selecting a diode. The MBR0540 and the NSR05F40 are recommended for AW99703.

(3)

(5)

#### Input and Output Capacitors Selection

awini

The output capacitor keeps the output voltage ripple small and ensures feedback loop stability. This ripple voltage is related to the capacitor's capacitance and its equivalent series resistance (ESR). Assuming ESR of a capacitor is zero, the minimum capacitance needed for a given ripple can be calculated by:

$$C_{OUT} = \frac{(V_{OUT} - V_{IN}) \times I_{out}}{V_{OUT} \times F_S \times V_{ripple}}$$

(6)

Where, V<sub>ripple</sub> represents peak-to-peak output ripple. The additional output ripple caused by ESR can be calculated as:

$$V_{\text{ripple ESR}} = I_{\text{out}} \times R_{\text{ESR}}$$

(7)

V<sub>ripple\_ESR</sub> can be neglected for ceramic capacitors due to its low ESR, but must be considered if tantalum or electrolytic capacitors are used.

Note that with a tolerance, temperature and DC voltage shift, the effective capacitance will be much lower than its nominal capacitance. A minimum effective capacitance at the output should be over  $0.4\mu$ F in the application. The output capacitor affects the loop stability of the boost regulator. If the output capacitor is below the range, the boost regulator can potentially become unstable. Therefore, leave enough margin on the voltage rating to ensure adequate capacitance at the required output voltage. Table 8 lists the recommended output capacitors for the AW99703.

An X5R or X7R capacitor of  $10\mu$ F is recommended for input side. The output requires an X5R or X7R capacitor in the range of  $0.47\mu$ F to  $4.7\mu$ F. A 100nF capacitor and a 33 pF capacitor are recommended to use in parallel with the input capacitor and the output capacitor to suppress high frequency noise.

Note that capacitor degradation will increase the ripple dramatically. Select the capacitor with 50V rated voltage to reduce the degradation at the output voltage. If the output ripple is too large, change a capacitor with less degradation effect or with higher rated voltage could be helpful.

| Part<br>Number                   | С<br>(µF) | Voltage Rating<br>(V) | Case<br>Size | Tolerance<br>(%) | Temperature<br>Coefficient (%) | Vendor |

|----------------------------------|-----------|-----------------------|--------------|------------------|--------------------------------|--------|

| CGA3E3X5R1H105K080AB             | 1.0       | 50                    | 0603         | ±10              | ±15                            | TDK    |

| CGA4J3X7R1H105K125AB             | 1.0       | 50                    | 0805         | ±10              | ±15                            | TDK    |

| C2012X5R1H225K085AB              | 2.2       | 50                    | 0805         | ±10              | ±15                            | TDK    |

| GRT188R61H105KE13                | 1.0       | 50                    | 0603         | ±10              | ±15                            | Murata |

| GR <mark>T21BR71H105K</mark> E01 | 1.0       | 50                    | 0805         | ±10              | ±15                            | Murata |

| GRM188R61H225KE11                | 2.2       | 50                    | 0603         | ±10              | ±15                            | Murata |

Table 8.

Recommended output capacitors for the AW99703

For example, with a 10% tolerance, a 15% temperature coefficient and the DC voltage characteristic, the value of capacitance must be  $\ge 0.4/(0.9 \times 0.85)=0.523\mu$ F. For configurations where the output voltage is high, the two of these capacitors can be paralleled, or a larger capacitor such as the GRM188R61H225KE11 recommended be used.

#### **OWINIC** 上海艾为电子技术股份有限公司 shanghai awinic technology co., Itd

# **Power Dissipation**

The maximum IC junction temperature should not be exceed  $125^{\circ}$ C under normal operating conditions. This restriction limits the power dissipation of the AW99703. It is recommended to keep the actual dissipation less than or equal to  $P_{D(max)}$ . The maximum-power-dissipation limit is determined by using the following equation:

$$\mathsf{P}_{\mathsf{D}(\mathsf{max})} = \frac{\mathsf{T}_{\mathsf{Jmax}} - \mathsf{T}_{\mathsf{A}}}{\theta_{\mathsf{ia}}}$$

Where,  $T_{Jmax}$  is the Maximum Junction Temperature,  $T_A$  is the maximum ambient temperature for the application.  $\theta_{ja}$  is the thermal resistance junction-to-ambient given in Power Dissipation Table.

# PCB Layout Consideration

#### Layout Guidelines

PCB layout is an important design step for those high frequency, high current switching power regulators in order to minimize noise and keep loop stable. To reduce switching losses, it is better to make the SW pin rise and fall times as short as possible. Minimizing the length and area of all traces connected to the SW pin and using a ground plane under the switching regulator are strongly recommended to minimize inter-plane coupling. The input capacitor should be very close to the IC to get the best decoupling. The path of the inductor, schottky diode and output capacitor should be kept as short as possible to minimize noise and ringing. HVLED1, HVLED2, HVLED3 are sensitive nodes and they should be kept separate from the SW pin in the PCB layout.

The input and the output bypass capacitors should be placed as close to the IC as possible. Minimize trace lengths between the IC and the inductor, the diode and the output capacitor; keep these traces short, direct, and wide.

# Layout Example VIN CIN L1 **U1** $\bigcirc$ $\bigcirc$ SBD VOUT COUT **Top Layer** 2rd Layer Via to GND

#### Figure 16. AW99703 Layout Example

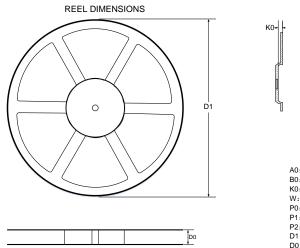

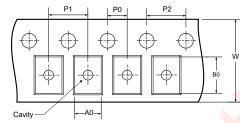

# **Tape And Reel Information**

TAPE DIMENSIONS

A0: Dimension designed to accommodate the component width

- B0: Dimension designed to accommodate the component length

- K0: Dimension designed to accommodate the component thickness W: Overall width of the carrier tape

- P0: Pitch between successive cavity centers and sprocket hole P1: Pitch between successive cavity centers

- P2: Pitch between sprocket hole D1: Reel Diameter

- D0: Reel Width

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### DIMENSIONS AND PIN1 OR IENTATION

| D1     | D0   | A0   | B0   | K0   | P0   | P1   | P2   | W    | Pin1 Quadrant |

|--------|------|------|------|------|------|------|------|------|---------------|

| (mm)   | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) |               |

| 179.00 | 9.00 | 1.35 | 1.75 | 0.70 | 2.00 | 4.00 | 4.00 | 8.00 | Q1            |

All dimensions are nominal

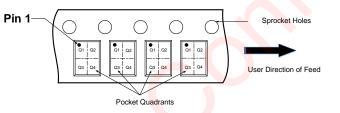

# **Package Description**

Copyright © 2018 SHANGHAI AWINIC TECHNOLOGY CO., LTD

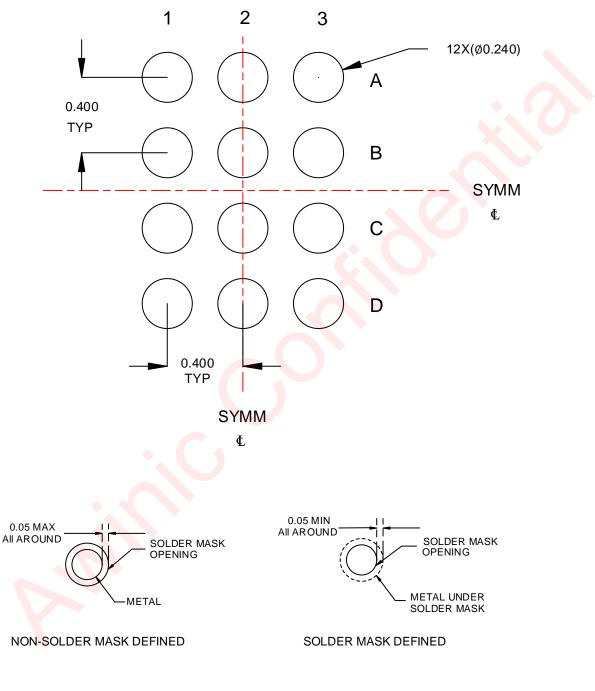

# Land Pattern

Unit: mm

# **Revision History**

| Version | Date      | Change Record                                                                                                                                                                                                                                                          |

|---------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V1.0    | Oct. 2018 | First official version released                                                                                                                                                                                                                                        |

| V1.1    | Sep. 2019 | Update chip performance parameters and increase efficiency laboratory result                                                                                                                                                                                           |

| V1.2    | Dec. 2019 | Update the value of V <sub>HR</sub> in Electrical Characteristics part<br>Update the value of θ <sub>JA</sub> in Absolute Maximum Ratings<br>Update the Operation States<br>Update the Input and Output Capacitors Selection<br>Distinguish AGND and PGND of chip pins |

# **るいうに 上海交为电子技术股份有限公司** shanghai awinic technology co., ltd.

## **Disclaimer**

All trademarks are the property of their respective owners. Information in this document is believed to be accurate and reliable. However, Shanghai AWINIC Technology Co., Ltd (AWINIC Technology) does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.