## I<sup>2</sup>S/TDM Input, 10.25V BOOST Digital Smart K Audio Amplifier with Speaker Voltage and Current Sense

## **FEATURES**

awinic

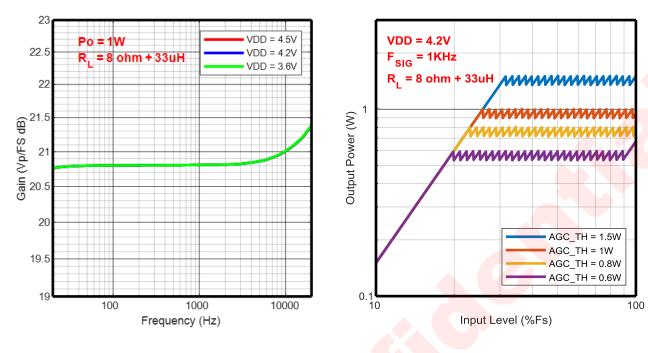

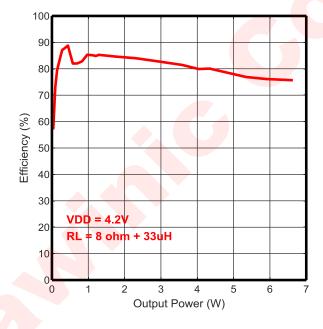

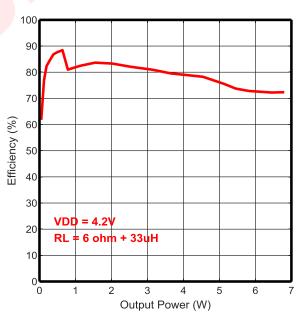

- Smart BOOST with total efficiency up to 84%

- High RF noise suppression, eliminate the TDD noise completely

- Low noise: 12uV

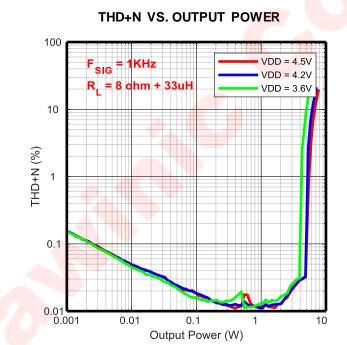

- THD+N: 0.02%

- Speaker Voltage and Current Sense

- Supports 6Ω Speaker

- Extensive Pop-Click Suppression

- Volume control(from -96dB to 0dB)

- I<sup>2</sup>S/TDM interface:

- I<sup>2</sup>S, Left-Justified and Right-Justified

- Supports four slots TDM

- Input Sample Rates from 8kHz to 96kHz

- Data Width: 16, 20, 24, 32 Bits

- I<sup>2</sup>C-bus control interface(400kHz)

- Power Supplies:

- VDD: 3.0V-5.5V

- DVDD: 1.65V~1.95V

- Short-Circuit Protection, Over-Temperature Protection, Under-Voltage Protection and Over-Voltage Protection

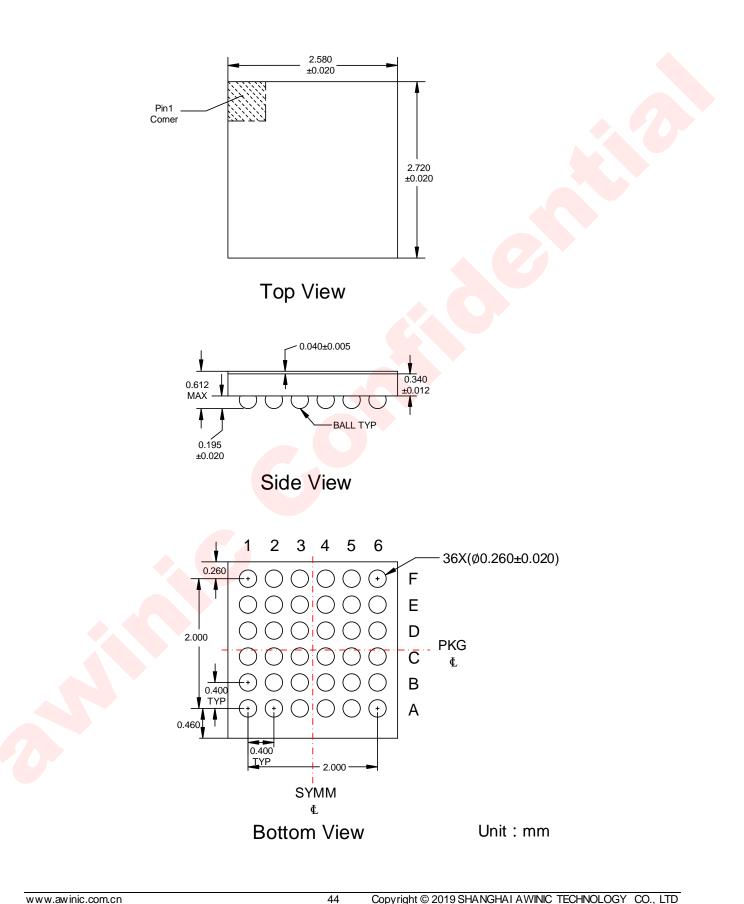

- WLCSP 2.58X2.72-36B package

## **APPLICATIONS**

- Mobile phones

- Tablets

- Portable Audio Devices

## DESCRIPTION

The AW88263 is an l<sup>2</sup>S/TDM input, high efficiency digital Smart K audio amplifier with an integrated 10.25V smart boost converter. Due to its 12uV noise floor and ultra-low distortion, clean listening is guaranteed. It can deliver 5.2W output power into an 8 $\Omega$  speaker at 1% THD+N.

The AW88263 integrates a high-efficiency smart boost converter as the Class-D amplifier supply rail. The output voltage of boost converter can be adjusted smartly according to the input amplitude, which extremely improves the efficiency without clipping distortion.

The AW88263 features high RF suppression and eliminates TDD noise completely benefited from the digital audio input interface. General settings are communicated via an I<sup>2</sup>C-bus interface, and the device address is configurable.

The AW88263 offers Short Circuit Protection, Over-Temperature Protection, Under-Voltage Protection and Over-Voltage Protection to protect the device.

AW88263 is available in a WLCSP 2.58X2.72-36B package.

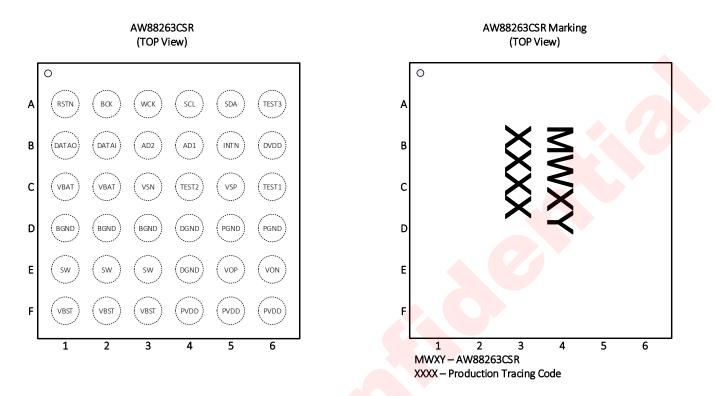

## **PIN CONFIGURATION AND TOP MARK**

awinic

#### Figure 1 AW88263CSR pin diagram top view and device marking

| Pin No | Pin Name | Description                                                |

|--------|----------|------------------------------------------------------------|

| A1     | RSTN     | Active low hardware reset                                  |

| A2     | вск      | I <sup>2</sup> S/TDM bit clock input                       |

| A3     | WCK      | I <sup>2</sup> S word select input / TDM frame sync signal |

| A4     | SCL      | I <sup>2</sup> C clock input                               |

| A5     | SDA      | I <sup>2</sup> C data IO                                   |

| A6     | TEST3    | Test signal IO 3                                           |

| B1     | DATAO    | I <sup>2</sup> S/TDM data out                              |

| B2     | DATAI    | I <sup>2</sup> S/TDM data input                            |

| B3     | AD2      | I <sup>2</sup> C address select input 2                    |

| B4     | AD1      | I <sup>2</sup> C address select input 1                    |

| B5     | INTN     | Interrupt output                                           |

| B6     | DVDD     | Digital power supply                                       |

| C1, C2 | VBAT     | Battery power supply                                       |

| C3     | VSN      | Voltage sense inverting                                    |

## **PIN DESCRIPTION**

www.awinic.com.cn

Copyright © 2019 SHANGHAI A WINIC TECHNOLOGY CO., LTD

上海艾为电子技术股份有限公司 shanghai awinic technology co., ltd.

VON

VBST

PVDD

awinic

D1,

E1,

E6 F1,F2,F3

F4,F5,F6

AW88263 July. 2019 V1.0

|          |          | •                            |  |

|----------|----------|------------------------------|--|

|          |          |                              |  |

| Pin No   | Pin Name | Description                  |  |

| C4       | TEST2    | Test signal IO 2             |  |

| C5       | VSP      | Voltage sense non-inverting  |  |

| C6       | TEST1    | Test signal IO 1             |  |

| D1,D2,D3 | BGND     | Boost GND                    |  |

| D4,E4    | DGND     | Digital GND                  |  |

| D5,D6    | PGND     | Power GND                    |  |

| E1,E2,E3 | SW       | Boost switch pin             |  |

| E5       | VOP      | Non-inverting Class-D output |  |

|          |          |                              |  |

Inverting Class-D output

Power supply voltage

Boost output

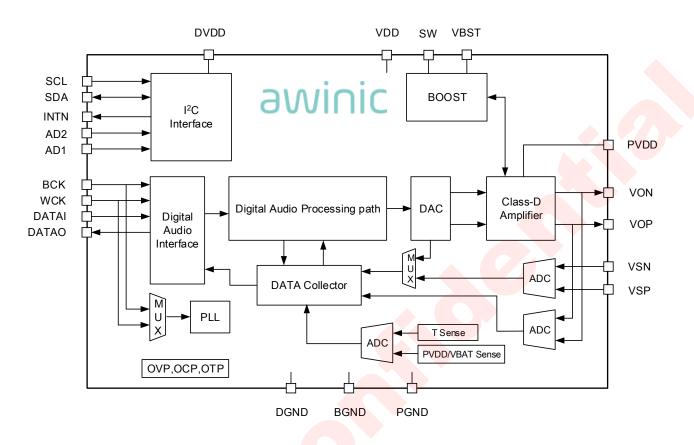

## FUNCTIONAL BLOCK DIAGRAM

awinic

Figure 2 FUNCTIONAL BLOCK DIAGRAM

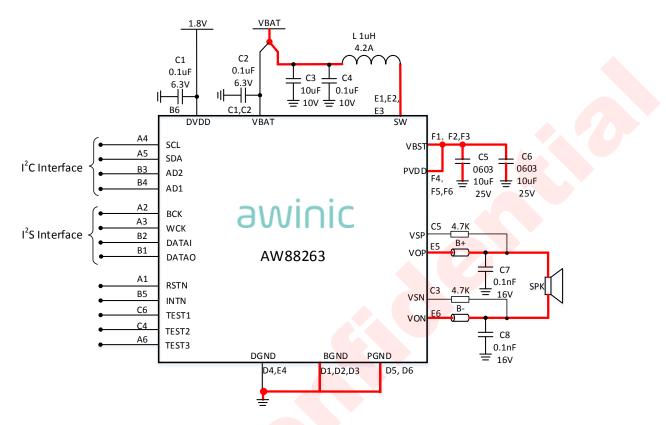

## **APPLICATION DIAGRAM**

awinic

Figure 3 AW88263 Application Circuit

Note: Traces carry high current are marked in red in the above figure

All trademarks are the property of their respective owners.

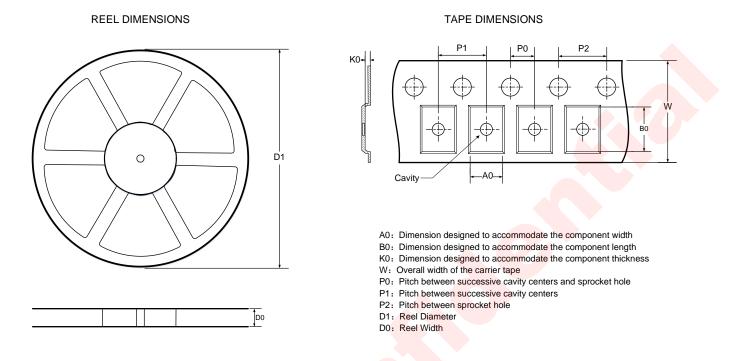

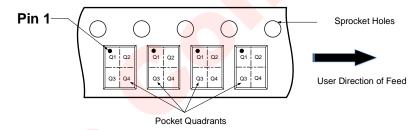

## ORDERING INFORMATION

| Product Type | Temperature  | Package                | Device<br>Marking | Moisture<br>Sensitivity<br>Level | Environmental<br>Information | Delivery Form                |

|--------------|--------------|------------------------|-------------------|----------------------------------|------------------------------|------------------------------|

| AW88263CSR   | -40°C ~ 85°C | WLCSP<br>2.58X2.72-36B | MWXY              | MSL1                             | RoHS+HF                      | 6000 units/<br>Tape and Reel |

## ABSOLUTE MAXIMUM RATING(NOTE1)

| Parameter                                       | Range                |  |  |

|-------------------------------------------------|----------------------|--|--|

| Battery Supply Voltage VDD                      | -0.3V to 6V          |  |  |

| Digital Supply Voltage VDVDD                    | -0.3V to 2V          |  |  |

| Boost output voltage VPVDD                      | -0.3 to 13V          |  |  |

| Boost SW pin voltage                            | -0.3 to Vpvdd+2V     |  |  |

| Minimum load resistance R∟                      | 5Ω                   |  |  |

| Package Thermal Resistance θJA                  | 60°C/W               |  |  |

| Ambient Temperature Range                       | -40°C to 85°C        |  |  |

| Maximum Junction Temperature TJMAX              | 165°C                |  |  |

| Storage Temperature Range Tstg                  | -65°C to 150°C       |  |  |

| Lead Temperature (Soldering 10 Seconds)         | 2 <mark>60</mark> °C |  |  |

| ESD Rating (Note 2,3)                           |                      |  |  |

| HBM (Human Body Model)                          | ±3000V               |  |  |

| CDM(Charge Device Model)                        | ±1000V               |  |  |

| Latch-up                                        |                      |  |  |

| Test Condition: JEDEC STANDARD NO.78E SEPTEMBER | +IT: 450mA           |  |  |

| 2016                                            | -IT: -450mA          |  |  |

**Note 1:** Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute -maximum-rated conditions for extended periods may affect device reliability.

**Note 2:** The human body model is a 100pF capacitor discharged through a 1.5kΩ resistor into each pin. Test method: MIL - STD-883J Method 3015.9

**Note 3:** Test method: JEDEC EIA/JESD22-C101F

## **ELECTRICAL CHARACTERISTICS**

## CHARACTERISTICS

Test condition : TA=25°C , VDD=3.6V , DVDD=1.8V , PVDD=10.25V , RL=8 $\Omega$ +33 $\mu$ H , f=1kHz(unless otherwise noted)

| Symbol  | Description                         | Test Conditions                                    | Min  | Тур.                         | Max  | Units |

|---------|-------------------------------------|----------------------------------------------------|------|------------------------------|------|-------|

| Vdd     | Battery supply voltage              | On pin VDD                                         | 3    |                              | 5.5  | V     |

| Vdvdd   | Digital supply voltage              | On pin DVDD                                        | 1.65 | 1.8                          | 1.95 | V     |

|         | Detter comply compart               | Operating mode                                     |      | 5.5                          |      | mA    |

| Ivdd    | Battery supply current              | Power down mode                                    |      | 0.3                          | 2    | μA    |

|         | Disitel suggle sugget               | Operating mode                                     |      | 4.5                          |      | mA    |

| DVDD    | Digital supply current              | Power down mode                                    |      | 5                            | -    | μA    |

| Boost   | 1                                   | L                                                  |      |                              |      |       |

| Vpvdd   | Boost output voltage                |                                                    |      | 10.25 <sup>(</sup><br>Note1) |      | V     |

| Vovp    | Over-voltage threshold              |                                                    |      | Vpvdd+<br>0.5                |      | V     |

|         | OVP hysteresis voltage              |                                                    |      | 500                          |      | mV    |

| L_PEAK  | Inductor peak current limit         |                                                    |      | 3.75 <sup>(No</sup> te1)     |      | A     |

| FBST    | Operating Frequency                 | fs = 48KHz                                         |      | 1.6                          |      | MHz   |

| DMAX    | The maximum duty cycle              |                                                    |      | 90                           |      | %     |

| ηвѕт    | Boost converter efficiency          | VDD=4.2V, lioad = 0.5A<br>SmartBoost               |      | 88                           |      | %     |

| Class-D |                                     |                                                    |      | ·                            |      |       |

| Rdson   | Drain-Source on-state<br>resistance | High side MOS + Low side<br>MOS                    |      | 300                          |      | mΩ    |

|         |                                     | THD+N=1%, R∟=8Ω+33μH,<br>VDD=4.2V, PVDD=10.25V     |      | 5.2                          |      | W     |

| Po      | Speaker Output Power                | THD+N=10%,<br>R∟=8Ω+33μH, Vdd=4.2V,<br>PVDD=10.25V |      | 6.2                          |      | w     |

| FU      | Speaker Output Fower                | THD+N=1%, R∟=6Ω+33μH,<br>Vpp=4.2V, PVDD=10.25V     |      | 5.35                         |      | W     |

|         |                                     | THD+N=10%,<br>R∟=6Ω+33μH, Vpd=4.2V,<br>PVDD=10.25V |      | 6.5                          |      | w     |

| Vos     | Output offset voltage               | l <sup>2</sup> S signal input 0                    | -30  | 0                            | 30   | mV    |

| η       | Total efficiency                    | Vpp=4.2V, Po=0.5W,<br>R∟=8Ω+33μH                   |      | 89                           |      | %     |

www.awinic.com.cn

Copyright © 2019 SHANGHAI A WINIC TECHNOLOGY CO., LTD

July. 2019 V1.0

| Symbol      | Description                              | Test Conditio                                                      | ns    | Min            | Тур. | Max            | Units |

|-------------|------------------------------------------|--------------------------------------------------------------------|-------|----------------|------|----------------|-------|

|             | (Class-D)                                |                                                                    |       |                |      |                |       |

|             | Total efficiency<br>(SmartBoost+Class-D) | VDD=4.2V, Po=1W,<br>RL=8Ω+33μH                                     |       |                | 84   |                | %     |

| THD+N       | Total harmonic distortion plus noise     | V <sub>DD</sub> =4.2V, Po=1W,<br>R∟=8Ω+33µH, f=1kH<br>PVDD=10.25V  | łz,   |                | 0.02 |                | %     |

|             | Speaker Mode Output noise                | A-weighting                                                        |       |                | 22   |                | μV    |

| En          | Receiver Mode Output noise               | A-weighting                                                        |       |                | 12   |                | μV    |

| SNR         | Signal-to-noise ratio                    | V <sub>DD</sub> =4.2V, PVDD=10<br>Po=5.2W, R∟=8Ω+33<br>A-weighting |       |                | 109  |                | dB    |

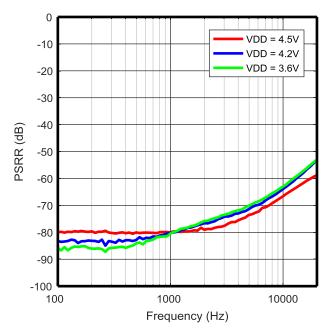

| PSRR        | Power supply rejection                   | Receiver Mode ,<br>VDD=4.2V,                                       | 217Hz |                | -85  |                | dB    |

|             | ratio                                    | VDD=4.2V,<br>Vp-p_sin=200mV                                        | 1kHz  |                | -80  |                | dB    |

| Current Se  | ense                                     |                                                                    |       |                |      |                |       |

| ISNS_FS     | Current sense full scale                 |                                                                    |       |                | 3.67 |                | А     |

| SNR         | Signal-to-noise ratio                    | lpeak=1A, R∟=8Ω+3<br>A-weighting                                   | 3µH,  |                | 65   |                | dB    |

| THD+N       | Total harmonic distortion plus noise     | lpeak=1A, RL=8Ω+33µH                                               |       |                | 0.25 |                | %     |

| ΔIsns       | Current sense accuracy                   | lpeak=1A, R∟=8Ω+3                                                  | 3µH   |                | 2    |                | %     |

| Voltage Se  | ense                                     |                                                                    |       |                | I    |                | 1     |

| Vsns_fs     | Voltage sense full scale                 |                                                                    |       |                | 18   |                | V     |

| SNR         | Signal-to-noise ratio                    | lpeak=1A, R∟=8Ω+3<br>A-weighting                                   | 3µH,  |                | 65   |                | dB    |

| THD+N       | Total harmonic distortion plus noise     | lpeak=1A, R∟=8Ω+3                                                  | 3µH   |                | 0.1  |                | %     |

|             | Voltage sense accuracy                   | lpeak=1A, R∟=8Ω+33µH                                               |       |                | 2    |                | %     |

| Digital Log | gical Interface                          | •                                                                  |       | •              |      | •              | •     |

| VIL         | Logic input low level                    |                                                                    | Din   |                |      | 0.3 x<br>Vdvdd | V     |

| Vін         | Logic input high level                   | - BCK, WCK, DATAI Pin                                              |       | 0.7 x<br>Vdvdd |      | Vdvdd          | V     |

| VIL         | Logic input low level                    | RSTN, SCL, SDA, A                                                  | .D1,  |                |      | 0.3 x<br>Vdvdd | V     |

| Vін         | Logic input high level                   | AD2 Pin                                                            |       | 0.7 x<br>Vdvdd |      | 3.6            | V     |

| Vol         | Logic output low level                   | Ιουτ=2mA                                                           |       |                |      | 0.45           | V     |

|             | 1                                        | •                                                                  |       |                | 1    | 1              |       |

Copyright © 2019 SHANGHAI AWINIC TECHNOLOGY CO., LTD

AW88263

July. 2019 V1.0

| Symbol     | Description                                          | Test Conditions | Min             | Тур. | Мах   | Units |

|------------|------------------------------------------------------|-----------------|-----------------|------|-------|-------|

| Vон        | Logic output high level                              | lout=-2mA       | Vdvdd -<br>0.45 |      | Vdvdd | V     |

| Protection |                                                      |                 |                 |      |       |       |

| Tsp        | Over temperature protection threshold                |                 |                 | 160  |       | °C    |

| Tsdr       | Over temperature<br>protection recovery<br>threshold |                 |                 | 130  |       | °C    |

| UVP        | Under-voltage protection voltage                     |                 |                 | 2.6  |       | V     |

| UVP        | Under-voltage protection hysteresis voltage          |                 |                 | 100  |       | mV    |

Note 1: Registers are adjustable; Refer to the list of registers.

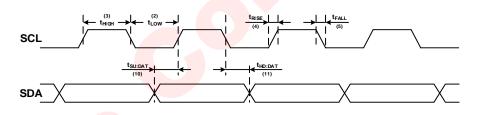

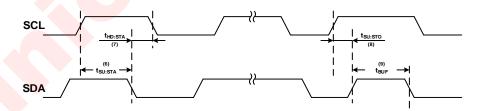

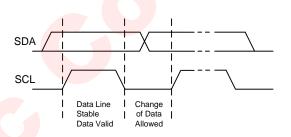

### I<sup>2</sup>C INTERFACE TIMING

|     | Parameter     |                                             |     |     | МАХ      | UNIT |

|-----|---------------|---------------------------------------------|-----|-----|----------|------|

| No. | Sym           | Name                                        | MIN | TYP | шал      | ONT  |

| 1   | fsc∟          | SCL Clock frequency                         |     |     | 400      | kHz  |

| 2   | t∟ow          | SCL Low level Duration                      | 1.3 |     |          | μs   |

| 3   | tніgн         | SCL High level Duration                     | 0.6 |     |          | μs   |

| 4   | trise         | SCL, SDA rise time                          |     |     | 0.3      | μs   |

| 5   | <b>t</b> FALL | SCL, SDA fall time                          |     |     | 0.3      | μs   |

| 6   | tsu:sta       | Setup time SCL to START state               | 0.6 |     |          | μs   |

| 7   | thd:sta       | (Repeat-start) Start condition hold time    | 0.6 |     | <u>~</u> | μs   |

| 8   | tsu:sto       | Stop condition setup time                   | 0.6 |     |          | μs   |

| 9   | tвuғ          | the Bus idle time START state to STOP state | 1.3 |     |          | μs   |

| 10  | tsu:dat       | SDA setup time                              | 0.1 |     |          | μs   |

| 11  | thd:dat       | SDA hold time                               | 10  |     |          | ns   |

Figure 4 SCL and SDA timing relationships in the data transmission process

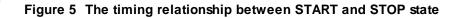

## DIGITAL AUDIO INTERFACE TIMING

|              | Parameter Name                  | Min   | Тур. | Max    | Units |

|--------------|---------------------------------|-------|------|--------|-------|

| fs           | sampling frequency, on pin WCK  | 8     |      | 96     | kHz   |

| <b>f</b> bck | Bit clock frequency, on pin BCK | 32*fs |      | 128*fs | Hz    |

| tsu          | WCK, DATAI Setup time to BCK    | 10    |      |        | ns    |

| th           | WCK, DATAI hold time to BCK     | 10    |      |        | ns    |

| td           | DATAO output delay time to BCK  |       |      | 50     | ns    |

#### Figure 6 Digital Audio Interface Timing

www.awinic.com.cn

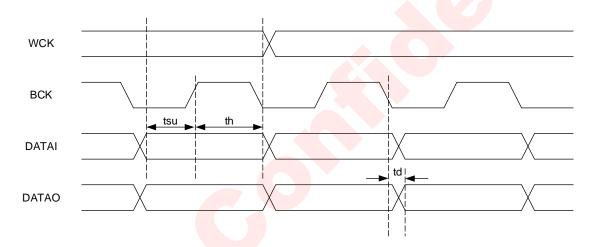

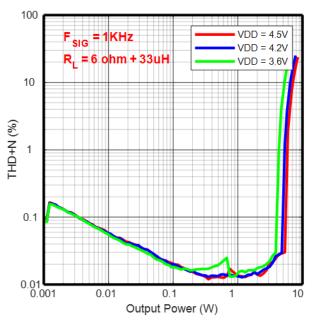

## TYPICAL CHARACTERISTIC CURVES

THD+N VS. OUTPUT POWER

#### GAIN VS. FREQUENCY

awinic

**OUTPUT POWER VS. Din**

EFFICIENCY VS. OUTPUT POWER

EFFICIENCY VS. OUTPUT POWER

#### **awinic** 上海艾为电子技术股份有限公司 shanghai awinic technology co., Itd.

RECEIVER PSRR VS. FREQUENCY

## **DETAIL FUNCTIONAL DESCRIPTION**

#### **POWER ON RESET**

The device provides a power-on reset feature that is controlled by VDD and DVDD supply voltage. When the VDD supply voltage raises from 0V to 2.1V, or DVDD supply voltage raises from 0V to 1.1V. The reset signal will be generated to perform a power-on reset operation, which will reset all circuits and configuration registers.

#### **OPERATION MODE**

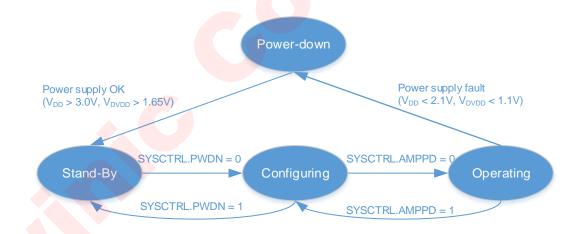

The device supports 4 operation modes.

| Table 1 | Operating | Mode |

|---------|-----------|------|

|---------|-----------|------|

| Mode        | Condition                                          | Description                                                                                                                  |

|-------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Power-Down  | V <sub>DD</sub> < 2.1V<br>V <sub>DVDD</sub> < 1.1V | Power supply is not ready, chipset is power down.                                                                            |

| Stand-By    | $V_{DD} > 3V$ $V_{DVDD} > 1.65V$                   | Power supply is ready, most parts of the device are power down for<br>low power consumption except I <sup>2</sup> Cinterface |

| Configuring | PWDN = 0                                           | Device is biased while boost and class-D output is floating.<br>System configuration carried out in this mode                |

| Operating   | AMPPD = 0                                          | Amplifier is fully operating                                                                                                 |

Figure 7 Device operating modes transition

#### POWER-DOWN MODE

The device switches to power-down mode when any of the following events occurred:

- Vdvdd < 1.1 V

- Vdd < 2.1 V

- RSTN pin goes LOW

In this mode, all circuits inside this device will be shut down except the power-on-reset circuit. I<sup>2</sup>C interface isn't accessible in this mode, and all of the internal configurable registers are cleared.

The device will jump out of the power-down mode automatically when all of the supply voltages are OK: VDVDD > 1.65 V and VDD > 3 V And RSTN goes HIGH.

#### STAND-BY MODE

The device switches stand-by mode when the power supply voltages are OK and RSTN pin is HIGH. In this mode I<sup>2</sup>C interface is accessible, other modules are still powered down. Customer can set device to mode when the device is no needed to work.

#### CONFIG MODE

The device switches to OFF mode when:

- SYSCTRL.PWDN = 0;

- SYSCTRL.AMPPD = 1;

In this mode the internal bias, OSC, PLL will start to work

#### OPERATING MODE

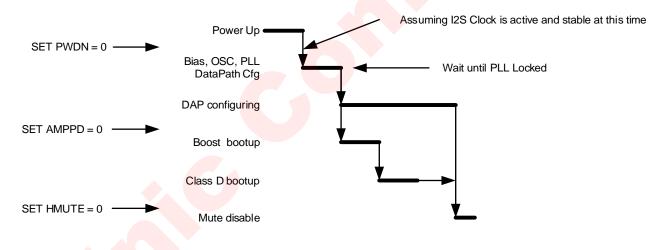

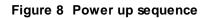

The device is fully operational in this mode. Boost, amplifier loop and power stage circuits will start to work. Customer can set SYSCTRL.AMPPD = 0 to make device in this mode. This device power up sequence is illustrated in the following figure:

Detail description for each step is listed in the following table.

| Index | description                                                                  | Mode             |

|-------|------------------------------------------------------------------------------|------------------|

| 1     | Wait for VDD $\sqrt{1000}$ DVDD supply power up                              | Power-Down       |

| 2     | I <sup>2</sup> S + Data Path Configuration                                   | Stand-By         |

| 3.1   | Enable system (SYSCTRL.PWDN = 0)                                             |                  |

| 3.2   | Bias, OSC, PLL active                                                        | Configuring      |

| 3.3   | Waiting for PLL locked                                                       |                  |

| 4.1   | Enable Boost and amplifier (SYSCTRL.AMPPD =0)<br>Boost and Amplifier boot up |                  |

| 4.2   | wait SYSST.SWS =1                                                            | <b>Operating</b> |

| 5     | Release Hard-Mute<br>Data Path active                                        |                  |

#### Table 2 Detail Description of Power up sequence

#### Power up sequence considering I2S, I2C timing shows as below:

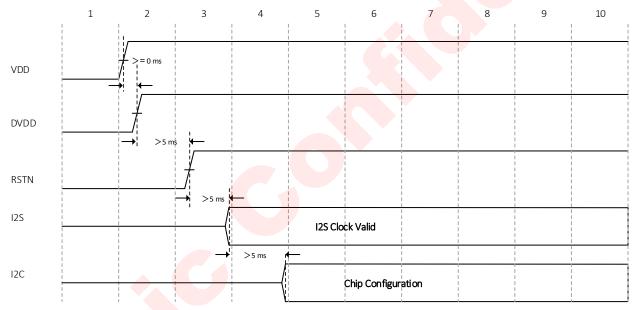

Power down sequence considering I2S, I2C timing shows as below:

#### SOFTWARE RESET

awinic

Writing 0x55AA to register ID (0x00) via I<sup>2</sup>C interface will reset the device internal circuits and all configuration registers.

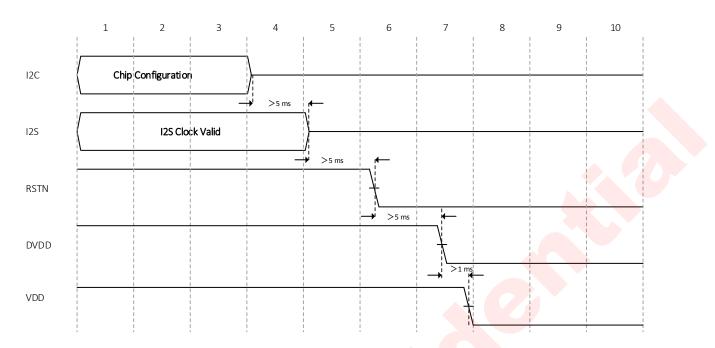

#### DIGITAL AUDIO INTERFACE

Audio data is transferred between the host processor and the device via the Digital Audio Interface. The digital audio interface is in full-duplex via 4 dedicated pins:

- BCK

- WCK

- DATAI

- DATAO

Two-slot I<sup>2</sup>S and 4-slot TDM are supported in this device. The digital audio Interface on this device is slave only and flexible with data width options, including 16, 20, 24, or 32 bits by configurable registers.

Three modes of I<sup>2</sup>S are supported, including standard I<sup>2</sup>S mode, left-justified mode and right-justified data mode, which can be configured via I2SCTRL.I2SMD. These modes are all MSB-first, with data width programmable via I2SCTRL.I2SFS.

The word clock WCK is used to define the beginning of a frame. The frequency of this clock corresponds to the sampling frequency. The device supports the following sample rates (fs): 8 kHz, 11.025 kHz, 12 kHz, 16 kHz, 22.05 kHz, 24 kHz, 32 kHz, 44.1 kHz, 48 kHz and 96 kHz. It is selected via configurable register I2SCTRL.I2SSR.

The bit clock BCK is used to sample the digital audio data across the digital audio interface. The number of bitclock pulses in a frame is defined as slot length. Three kind of slot length are supported (16/24/32) via configurable register I2SCTRL.I2SBCK. The frequency of BCK can be calculated according to the following equation:

#### BCK frequency = SampleRate \* SlotLength \* SlotNumber

www.awinic.com.cn

**SampleRate**: Sample rate for this digital audio interface;

SlotLength: The length of one audio slot in unit of BCK clock;

**SlotNumber**: How many slots supported in this audio interface. For example: 2-slot supported in I2S mode, 4-slot supported in TDM mode.

The word select and bit clock signals of the I<sup>2</sup>S input are the reference signals for the digital audio interface and Phased Locked Loop (PLL).

The input audio data can be attenuated -6dB in this module, by setting bit I2SCTRL.INPLEV. The audio source can be from left channel, right channel or the average of the left and right channel, which is controlled by I2SCTRL.CHSEL.

| Interface format(MSB first) | Data width                       | BCK frequency                  |

|-----------------------------|----------------------------------|--------------------------------|

| Standard I <sup>2</sup> S   | 16b<br>20b/24b/32b               | 32fs/48fs /64fs<br>48fs /64fs  |

| left-justified              | 16b<br>20b/24b/32b               | 32fs/48fs /64fs<br>48fs /64fs  |

| right-justified             | 16b<br>20b/24b/ <mark>32b</mark> | 32fs /48fs /64fs<br>48fs /64fs |

The output port DATAO, can be enabled or disabled via bit I2SCFG1.I2STXEN. The unused slots can be set to Hi-z or zero, which is controlled by I2SCFG1.DOHZ.

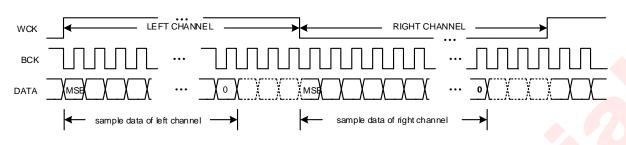

#### STANDARD &S MODE

awinid

#### Figure 9 I<sup>2</sup>S Timing for Standard I<sup>2</sup>S Mode

- When WCK=0 indicating the left channel data, and WCK=1 indicating the right channel data.

- The MSB of the left channel is valid on the second rising edge of the bit clock after the falling edge of the word clock. Similarly the MSB of the right channel is valid on the second rising edge of the bit clock after the rising edge of the word clock.

#### LEFT-JUSTIFIED MODE

ລູເນເດີ

#### Figure 10 I<sup>2</sup>S Timing for Left-Justified Mode

- When WCK=1 indicating the left channel data, and WCK=0 indicating the right channel data.

- The MSB of the left channel is valid on the first rising edge of the bit clock after the rising edge of the word clock. Similarly the MSB of the right channel is valid on the first rising edge of the bit clock after the falling edge of the word clock.

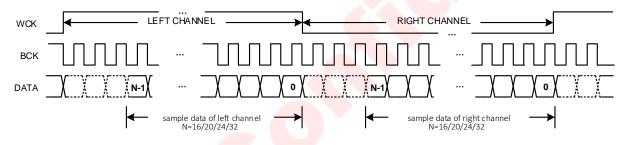

#### RIGHT-JUSTIFIED MODE

Figure 11 I<sup>2</sup>S Timing for Right-Justified Mode

- When WCK is high indicating the left channel data, and WCK=0 indicating the right channel data.

- The LSB (bit 0) of the left channel is valid on the rising edge of the bit clock preceding the falling edge of the word clock. Similarly, the LSB (bit 0) of the right channel is valid on the rising edge of the bit clock preceding the rising edge of the word clock.

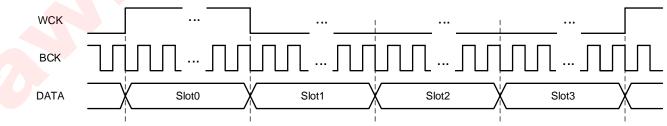

#### TDM MODE

All of the three kind of bit synchronization modes (standard, left-justified, right-justified) are also supported in TDM mode. The difference between TDM and I<sup>2</sup>S is the slot number supported. 4-slot is supported in TDM mode, while 2-slot is supported in I<sup>2</sup>S mode

Figure 12 TDM Timing

Note: The high level pulse width of WCK signal can be one slot time or one period of BCK.

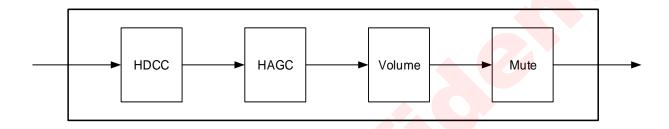

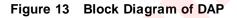

#### DIGITAL AUDIO PROCESSING

This device provides algorithm supporting for audio signal processing. The following functions are processed in this module.

• HDCC

awinic

- Hardware AGC

- Volume control

- Mute

The signal processing flow in the DAP(Digital Audio Processor) is illustrated in the following figure.

#### HDCC

This module performs hardware DC canceling for the input audio stream. It blocks DC components into analog class D loop.

#### HAGC

In the actual audio application, system output power tends to be more than rated power of speaker, such as in the 10.25V power supply, as for 80hms speaker, the maximum undistorted power is about 5.3W, but many speakers' rated power is about 1W, if there is no output power control, the overload signal can cause damage to the speaker. The audio power amplifier with hardware AGC can protect the speaker effectively, When the output power is not exceeds the setting threshold, the hardware AGC module will not attenuate the internal gain. Once the output power exceeds the setting threshold, the hardware AGC module will reduce the internal gain of amplifier and restricts the output power under the setting threshold.

#### VOLUME CONTROL

The volume control function attenuates the audio signal at the end of digital audio processing. The range of volume setting is from 0db to -96db with 0.5db/step

#### MUTE

This module perform mute control for the audio stream

www.awinic.com.cn

#### **DC-DC CONVERTER**

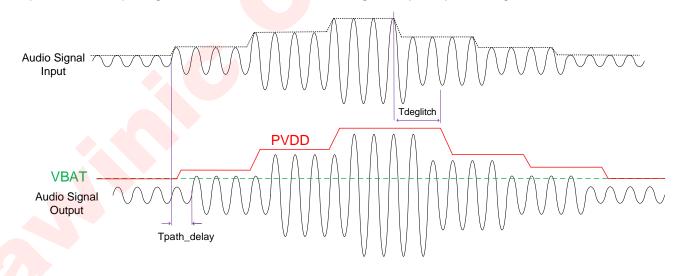

This device using smart boost converter generates the amplifier supply rail, working in 1.6MHz. The DC-DC converter can work in different mode via BSTCTRL2.BST\_MODE:

- Pass-through mode: the voltage of VDD is transparently passed to output of converter PVDD

- Force boost mode: the output voltage is boosted to the programmed output voltage

- Smart boost 1 mode: the output voltage can be switch between VDD and programmed output voltage according to the input audio level.

- **Smart boost 2 mode**: the output voltage can be dynamically adjusted according to the amplifier output's signal swing requirements in order to maximize efficiency.

#### Pass-through mode

The internal boost circuit is not working; the voltage of VDD is passed to PVDD directly.

#### Force boost mode

The boost circuit is always working and converts the voltage of VDD to the programmed output voltage. The output voltage is configured via BSTCTRL2.VOUT\_VREFSET

#### Smart boost 1 mode

Smart boost 1 mode can dynamically turn off the boost according to the amplifier output's signal swing requirements in order to maximize efficiency.

#### Smart boost 2 mode

The boost circuits working dynamically according to the input audio level. When the level of input audio signal is below the setting threshold, the boost circuit will be deactivated. Till the level of input audio signal raised up and above the threshold, the boost circuit starts to work and boost the amplifier supply rail to the voltage fit the requirement of output signal before the audio stream arriving at amplifier power stage.

#### Figure 14 Boost Circuit Behavior in Smart Boost 2 Mode

#### **PROTECTION MECHANISMS**

**Over Voltage Protection (OVP)**

The boost circuit has integrated the over voltage protection control loop. When the output voltage PVDD is above the threshold, the boost circuits will stop working, until the voltage of PVDD going down and under the normal fixed working voltage.

#### Over Temperature Protection (OTP)

The device has automatic temperature protection mechanism which prevents heat damage to the chip. It is triggered when the junction temperature is larger than the preset temperature high threshold (default =  $160^{\circ}$ C). When it happens, the output stages will be disabled. When the junction temperature drops below the preset temperature low threshold (less than  $130^{\circ}$ C), the output stages will start to operate normally again

#### Over Current (short) Protection (OCP)

The short circuit protection function is triggered when VOP/VON is short to PVDD/GND or VOP is short to VON, the output stages will be shut down to prevent damage to itself. When the fault condition is disappeared, the output stages of device will restart.

#### Under Voltage Detection (UVL)

The interrupt bit SYSINT.UVLI will be set to 1 when under voltage occurs, which will be cleared by a read operation of SYSINT register. Usually the SYSINT.UVLI bit can be used to check whether an unexpected under-voltage event has taken place.

#### BATTERY VOLTAGE MONITORING

The device monitors the voltage on the VDD pin, which is most commonly the battery for the system. The battery voltage level is available via bits VBAT\_DET in the Battery Supply Voltage register VBAT. Status bits BAT\_DET can be used to calculate the battery voltage. The battery voltage level VBAT is:

$$V_{BAT} = \frac{VBAT\_DET}{2^{10} - 1} \times 6.025V$$

For example, if VBAT\_DET = 101010011, the battery voltage level VBAT is equal to 3.6V.

#### PVDD VOLTAGE MONITORING

The device monitors the voltage on the PVDD pin, which is most commonly the PVDD voltage level for the system. The PVDD pin voltage level is available via bits PVDD\_DET in the Power Supply Voltage monitor register PVDD. Status bits PVDD\_DET can be used to calculate the PVDD voltage. The PVDD voltage level VPVDD is:

$$V_{PVDD} = \frac{PVDD\_DET}{2^{10} - 1} \times 12.05V$$

For example, if PVDD\_DET = 101010011, the PVDD voltage level VPVDD is equal to 7.2V.

#### DIE TEMPERATURE MONITORING

The device monitors the die temperature and the result is available via bits TEMP\_DET in the Temperature register TEMP. The TEMP\_DET is a two's complement value. For example, if TEMP\_DET = 00011001, the die temperature is 25°C.

#### **CURRENT SENSING**

awinic

The device provides speaker current sense for real time monitoring of loudspeaker behavior. The current sensing transfer function IsNs is:

$$I_{SNS} = \frac{D_{OUT}}{2^{11} - 1} \times 3.667A$$

DOUT: the current sense I2S output stream

#### VOLTAGE SENSING

The device provides speaker voltage sense for real time monitoring of loudspeaker behavior. The voltage sensing transfer function VsNs is:

$$V_{SNS} = \frac{D_{OUT}}{2^{11} - 1} \times 18V$$

#### AMPLIFIER TRANSFER FUNCTION

The transfer function from the input to the amplifier PWM output (when no gain and attenuation is applied in digital signal domain) is:

$$V_o = AMP \_NORM \_V \times D_{in}$$

D<sub>in</sub>: the level of input signal with a range from -1 to +1

AMP\_NORM\_V: the equivalent amplifier output voltage when D<sub>in</sub> is 1. In receiver mode the AMP\_NORM\_V is 5V, in speaker mode it's 16V.

#### **RECEIVER MODE**

The device built-in Receiver mode is easy to realize the Speaker and Receiver combo applications, it saves the system cost and board space. If the receiver magnification is one times, the noise floor will be 12µV. Speaker and Receiver combo applications can be realized without changing any hardware.

When the device is set to receiver mode, the power supply of Class D driver stage is from VDD directly without boost.

#### I<sup>2</sup>C INTERFACE

awinia

This device supports the I<sup>2</sup>C serial bus and data transmission protocol in fast mode at 400 kHz. This device operates as a slave on the I<sup>2</sup>C bus. Connections to the bus are made via the open-drain I/O pins SCL and SDA. The pull-up resistor can be selected in the range of  $1k \sim 10k\Omega$  and the typical value is  $4.7k\Omega$ . This device can support different high level ( $1.8V \sim 3.3V$ ) of this I<sup>2</sup>C interface.

#### DEVICE ADDRESS

The I<sup>2</sup>C device address (7-bit) can be set using the AD pin according to the following table: The AD1, AD2 pin configures the two LSB bits of the following 7-bit binary address A6-A0 of 01101xx. The permitted I<sup>2</sup>C addresses are 0x34(7-bit) through 0x37(7-bit).

| AD2 | AD1 | Address(7-bit)     |

|-----|-----|--------------------|

| 0   | 0   | 0x34               |

| 0   | 1   | 0x35               |

| 1   | 0   | <mark>0x</mark> 36 |

| 1   | 1   | 0x37               |

#### DATA VALIDATION

When SCL is high level, SDA level must be constant. SDA can be changed only when SCL is low level.

Figure 15 Data Validation Diagram

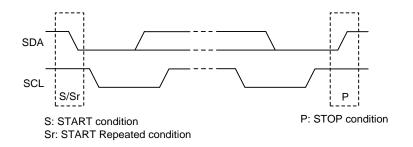

#### **PC START/STOP**

I<sup>2</sup>C start: SDA changes form high level to low level when SCL is high level.

I<sup>2</sup>C stop: SDA changes form low level to high level when SCL is high level.

Figure 16 I<sup>2</sup>C Start/Stop Condition Timing

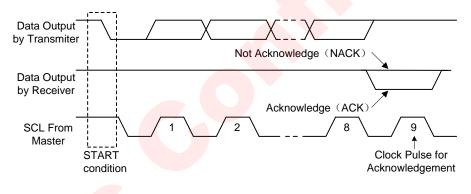

#### ACK (ACKNOWLEDGEMENT)

ACK means the successful transfer of I<sup>2</sup>C bus data. After master sends 8bits data, SDA must be released; SDA is pulled to GND by slave device when slave acknowledges.

When master reads, slave device sends 8bit data, releases the SDA and waits for ACK from master. If ACK is send and I<sup>2</sup>C stop is not send by master, slave device sends the next data. If ACK is not send by master, slave device stops to send data and waits for I<sup>2</sup>C stop.

Figure 17 I<sup>2</sup>C ACK Timing

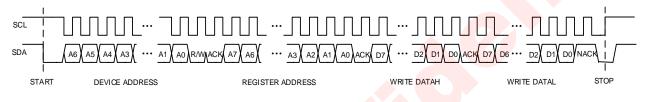

#### WRITE CYCLE

One data bit is transferred during each clock pulse. Data is sampled during the high state of the serial clock (SCL). Consequently, throughout the clock's high period, the data should remain stable. Any changes on the SDA line during the high state of the SCL and in the middle of a transaction, aborts the current transaction. New data should be sent during the low SCL state. This protocol allows a single data line to transfer both command/control information and data using the synchronous serial clock.

Each data transaction is composed of a Start Condition, a number of byte transfers (set by the software) and a Stop Condition to terminate the transaction. Every byte written to the SDA bus must be 8 bits long and is transferred with the most significant bit first. After each byte, an Acknowledge signal must follow.

In a write process, the following steps should be followed:

- a) Master device generates START condition. The "START" signal is generated by lowering the SDA signal while the SCL signal is high.

- b) Master device sends slave address (7-bit) and the data direction bit (r/w = 0).

- c) Slave device sends acknowledge signal if the slave address is correct.

- d) Master sends control register address (8-bit)

- e) Slave sends acknowledge signal

- f) Master sends high data byte of 16-bit data to be written to the addressed register

- g) Slave sends acknowledge signal

- h) Master sends low data byte of 16-bit data to be written to the addressed register

- i) Slave sends acknowledge signal

- j) If master will send further 16-bit data bytes the control register address will be incremented by one after acknowledge signal of step g (repeat step f to g)

- k) Master generates STOP condition to indicate write cycle end

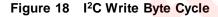

#### READ CYCLE

In a read cycle, the following steps should be followed:

- a) Master device generates START condition

- b) Master device sends slave address (7-bit) and the data direction bit (r/w = 0).

- c) Slave device sends acknowledge signal if the slave address is correct.

- d) Master sends control register address (8-bit)

- e) Slave sends acknowledge signal

- f) Master generates STOP condition followed with START condition or REPEAT START condition

- g) Master device sends slave address (7-bit) and the data direction bit (r/w = 1).

- h) Slave device sends acknowledge signal if the slave address is correct.

- i) Slave sends read high data byte of 16-bit data from addressed register.

- j) Master sends acknowledge signal.

- k) Slave sends read low data byte of 16-bit data from addressed register.

- If the master device sends acknowledge signal, the slave device will increase the control register

address by one, then send the next 16-bit data from the new addressed register.

- m) If the master device generates STOP condition, the read cycle is ended.

Figure 19 I<sup>2</sup>C Read Byte Cycle

AW88263

July. 2019 V1.0

## **REGISTER MAP**

#### **REGISTER DESCRIPTION**

#### REGISTER LIST

| ADDR | NAME     | R/W | Bit15             | Bit14 | Bit13   | Bit12            | Bit11 | Bit10   | Bit9    | Bit8     | Bit7  | Bit6                               | Bit5   | Bit4   | Bit3      | Bit2      | Bit1    | BitO |

|------|----------|-----|-------------------|-------|---------|------------------|-------|---------|---------|----------|-------|------------------------------------|--------|--------|-----------|-----------|---------|------|

| 0x00 | ID       | RO  |                   |       |         |                  |       |         | IDCODE  |          |       |                                    |        |        |           |           |         |      |

| 0x01 | SYSST    | RO  | OVP2S             | UVLS  | ADPS    | DPS BSTOCS OVPS  |       |         | BSTS    | SWS      | CLIPS |                                    | NOCLKS | CLKS   | OCDS      | CLIP_PRES | OTHS    | PLLS |

| 0x02 | SYSINT   | RC  | OVP2I             | UVLI  | ADPI    | ADPI BSTOCI OVPI |       |         | BSTI    | SWI      | CLIPI |                                    | NOCLKI | CLKI   | OCDI      | CLIP_PREI | OTHI    | PLLI |

| 0x03 | SYSINTM  | RW  | OVP2M             | UVLM  | ADPM    | ADPM BSTOCM OVPM |       | BSTM    | SWM     | CLIPM    |       | NOCLKM                             | CLKM   | OCDM   | CLIP_PREM | OTHM      | PLLM    |      |

| 0x04 | SYSCTRL  | RW  | SPK_GAIN RCV_GAIN |       |         |                  | SAIN  | INTMODE | INTN    | RCV_MODE | 12SEN | WSINV                              | BCKINV | IPLL   |           | AMPPD     | PWDN    |      |

| 0x05 | SYSCTRL2 | RW  |                   |       |         |                  |       |         |         | RMSE     | HAGCE | HDCCE                              | HMUTE  |        | BST_IPEA  | λK        |         |      |

| 0x06 | I2SCTRL  | RW  |                   |       | INPLEV  | I2SRXEN          | CHS   | EL      | I2SM    | D        | 12SFS | S                                  | I2SBCK |        |           | 12SSR     |         |      |

| 0x07 | I2SCFG1  | RW  |                   |       | I2S_TX_ | SLOTVLD          |       | I2S_RX_ | SLOTVLD |          | CFSE  | CFSEL DRVSTREN DOHZ FSYNC_TYPE SLC |        |        | SLOT_NUM  | 12SCHS    | 12STXEN |      |

| 0x09 | HAGCCFG1 | RW  |                   |       |         | RVTH             | 1     |         |         |          |       |                                    |        | A      | VTH       |           |         |      |

| 0x0a | HAGCCFG2 | RW  |                   |       |         |                  |       |         |         |          | АТТН  |                                    |        |        |           |           |         |      |

| 0x0b | HAGCCFG3 | RW  |                   |       |         |                  |       |         |         |          | RTTH  |                                    |        |        |           |           |         |      |

| 0x0c | HAGCCFG4 | RW  |                   |       |         | VOL              |       |         |         |          |       |                                    |        | НО     | LDTH      |           |         |      |

| 0x10 | HAGCST   | RO  |                   |       |         |                  |       |         |         |          |       |                                    |        |        | BSTVOU    | T_ST      |         |      |

| 0x12 | VBAT     | RO  |                   |       |         |                  |       |         |         |          |       |                                    | VBA    | T_DET  |           |           |         |      |

| 0x13 | TEMP     | RO  |                   |       |         |                  |       |         |         |          |       |                                    | TEM    | IP_DET |           |           |         |      |

www.awinic.com.cn

Copyright © 2019 SHANGHAI A WINIC TECHNOLOGY CO., LTD

## AW88263

July. 2019 V1.0

| ADDR | NAME     | R/W | Bit15     | Bit14   | Bit13   | Bit12    | Bit11 | Bit10 | Bit9     | Bit8         | Bit7                     | Bit6 | Bit5   | Bit4    | Bit3 | Bit2 | Bit1 | BitO |

|------|----------|-----|-----------|---------|---------|----------|-------|-------|----------|--------------|--------------------------|------|--------|---------|------|------|------|------|

| 0x14 | PVDD     | RO  |           |         |         | PVDD_DET |       |       |          |              |                          |      |        |         |      |      |      |      |

| 0x60 | BSTCTRL1 | RW  |           | BST_RTH |         |          |       |       |          |              | BST_ATH                  |      |        |         |      |      |      |      |

| 0x61 | BSTCTRL2 | RW  | VOUT_CTMD |         | BST_MOD | DE       |       |       | BST_TDEG |              | VOUT_VFBSET VOUT_VREFSET |      |        |         |      |      |      |      |

| 0x78 | EFRH     | RO  |           |         |         |          |       |       |          | EF_VSN_GESLP |                          |      |        |         |      |      |      |      |

| 0x7a | EFRM1    | RO  |           |         |         |          |       |       |          |              |                          |      | EF_ISN | N_GESLP |      |      |      |      |

www.awinic.com.cn

#### DETAILED REGISTER DESCRIPTION

| Bit  | Symbol | R/W | Description                                                                                                                           | Default |

|------|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------|---------|

| 15:0 | IDCODE | RO  | Chip ID (1852h) will be returned after read.<br>All configuration registers will be reset to default value after 0x55aa is<br>written | 0x1852  |

| SYSST: | (Address 01h) |     |                                                                |         |

|--------|---------------|-----|----------------------------------------------------------------|---------|

| Bit    | Symbol        | R/W | Description                                                    | Default |

| 15     | OVP2S         | RO  | Boost OVP2 status indicator                                    | 0       |

| 14     | UVLS          | RO  | VDD under voltage indicator<br>0: VDD > 2.8V<br>1: VDD < 2.8V  | 0       |

| 13     | ADPS          | RO  | Boost Adaptive status.<br>0: transparent<br>1: boost           | 0       |

| 12     | Reserved      | RO  | Not used                                                       | 0       |

| 11     | BSTOCS        | RO  | Boost over current indicator                                   | 0       |

| 10     | OVPS          | RO  | Boost OVP status indicator                                     | 0       |

| 9      | BSTS          | RO  | Boost start up finished.<br>0: not finished<br>1: finished     | 0       |

| 8      | SWS           | RO  | Ampifier switching status.<br>0: not switching<br>1: switching | 0       |

| 7      | CLIPS         | RO  | Ampifier clipping status.<br>0: not clipping<br>1: clipping    | 0       |

| 6      | Reserved      | RO  | Not used                                                       | 0       |

| 5      | NOCLKS        | RO  | The reference clock of PLL is not available                    | 0       |

| 4      | CLKS          | RO  | All internal clock are stable CLKS = PLLS & $\sim$ IDP         | 0       |

| 3      | OCDS          | RO  | Over current status in amplifier                               | 0       |

| 2      | CLIP_PRES     | RO  | Ampifier clipping pre status.                                  | 0       |

| 1      | OTHS          | RO  | Die Temperature is higher than 160degrees                      | 0       |

| 0      | PLLS          | RO  | PLL locked status.<br>0: unlocked<br>1: locked                 | 0       |

|        |               |     |                                                                |         |

| SYS <mark>INT</mark> : | (Address 02h) |     |                                           |         |

|------------------------|---------------|-----|-------------------------------------------|---------|

| Bit                    | Symbol        | R/W | Description                               | Default |

| 15                     | OVP2I         | RC  | Interrupt indicator for OVP2S.            | 0       |

| 14                     | UVLI          | RC  | Interrupt indicator for Power On and UVLS | 0       |

| 13                     | ADPI          | RC  | Interrupt indicator for ADPS              | 0       |

| 12                     | Reserved      | RC  | Not used                                  | 0       |

| 11                     | BSTOCI        | RC  | Interrupt indicator for BSTOCS.           | 0       |

| 10                     | OVPI          | RC  | Interrupt indicator for OVPS.             | 0       |

| 9                      | BSTI          | RC  | Interrupt indicator for BSTS.             | 0       |

| 8                      | SWI           | RC  | Interrupt indicator for SWS.              | 0       |

| 7                      | CLIPI         | RC  | Interrupt indicator for CLIPS.            | 0       |

www.awinic.com.cn

32

Copyright © 2019 SHANGHAI AWINIC TECHNOLOGY CO., LTD

# **awinic** L海艾为电子技术股份有限公司 shanghai awinic technology co., Itd.

## AW88263

July. 2019 V1.0

| 6 | Reserved  | RC | Not used                          | 0 |

|---|-----------|----|-----------------------------------|---|

| 5 | NOCLKI    | RC | Interrupt indicator for NOCLKS.   | 0 |

| 4 | CLKI      | RC | Interrupt indicator for CLKS.     | 0 |

| 3 | OCDI      | RC | Interrupt indicator for OCDS      | 0 |

| 2 | CLIP_PREI | RC | Interrupt indicator for CLIP_PRES | 0 |

| 1 | ОТНІ      | RC | Interrupt indicator for OTHS.     | 0 |

| 0 | PLLI      | RC | Interrupt indicator for PLLS.     | 0 |

| SYSINTI | M: (Address 03h) |     |                                |         |

|---------|------------------|-----|--------------------------------|---------|

| Bit     | Symbol           | R/W | Description                    | Default |

| 15      | OVP2M            | RW  | Interrupt mask for OVP2I       | 1       |

| 14      | UVLM             | RW  | Interrupt mask for UVLI.       | 1       |

| 13      | ADPM             | RW  | Interrupt mask for ADPI        | 1       |

| 12      | Reserved         | RW  | Not used                       | 0       |

| 11      | BSTOCM           | RW  | Interrupt mask for BSTOCI.     | 1       |

| 10      | OVPM             | RW  | Interrupt mask for OVPI        | 1       |

| 9       | BSTM             | RW  | Interrupt mask for BSTI.       | 1       |

| 8       | SWM              | RW  | Interrupt indicator for SWI.   | 1       |

| 7       | CLIPM            | RW  | Interrupt indicator for CLIPI. | 1       |

| 6       | Reserved         | RW  | Not used                       | 0       |

| 5       | NOCLKM           | RW  | Interrupt mask for NOCLKI.     | 1       |

| 4       | CLKM             | RW  | Interrupt mask for CLKI.       | 1       |

| 3       | OCDM             | RW  | Interrupt mask for OCDI.       | 1       |

| 2       | CLIP_PREM        | RW  | Interrupt mask for CLIP_PREI.  | 1       |

| 1       | OTHM             | RW  | Interrupt mask for OTHI.       | 1       |

| 0       | PLLM             | RW  | Interrupt mask for PLU.        | 1       |

| SYSCTR | L: (Address 04h) |     |                                                                                                                                              |         |

|--------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Bit    | Symbol           | R/W | Description                                                                                                                                  | Default |

| 15     | Reserved         | RW  | Not used                                                                                                                                     | 0       |

| 14:12  | SPK_GAIN         | RW  | Configuration for gain in Speaker Mode<br>000: AV=7<br>001: AV=8<br>010: AV=10<br>011: AV=14<br>100: AV=16<br>101: AV=20<br>Others: Reserved | 0x4     |

| 11:10  | RCV_GAIN         | RW  | Configuration for gain in Receiver Mode<br>00: AV=4.5<br>01: AV=5<br>10: AV=5.5<br>11: AV=7.5                                                | 0       |

| 9      | INTMODE          | RW  | Interrupt pad INTN output mode selection<br>0: Open-drain<br>1: Push&Pull                                                                    | 0       |

| 8      | INTN             | RW  | Interrupt pad INTN pin-source selection<br>0: SYSINT<br>1: SYSST                                                                             | 0       |

| 7 | RCV_MODE | RW | Receiver mode enable, active "1".<br>0: Speaker mode, VCOM=1/3*PVDD<br>1: Receiver mode, VCOM=1/2*PVDD                   | 0 |

|---|----------|----|--------------------------------------------------------------------------------------------------------------------------|---|

| 6 | I2SEN    | RW | Disable/Enable whole I2S interface module<br>0: disable<br>1: enable                                                     | 0 |

| 5 | WSINV    | RW | I2S Left/Right channel switch<br>0: No switch<br>1: Left/Right switch                                                    | 0 |

| 4 | BCKINV   | RW | I2S bit clock invert control<br>0: not invert<br>1: inverted                                                             | 0 |

| 3 | IPLL     | RW | PLL reference clock selection<br>0: bit clock<br>1: word selection signal                                                | 0 |

| 2 | Reserved | RW | Not used                                                                                                                 | 0 |

| 1 | AMPPD    | RW | Amplifier power down control bit, PowerDown until system<br>configuration finished<br>0: normal working<br>1: power down | 1 |

| 0 | PWDN     | RW | System power down control bit<br>0: System normal working<br>1: All circuits will enter power down mode                  | 1 |

**awinic** L海艾为电子技术股份有限公司 shanghai awinic technology co., Itd.

| Bit  | Symbol   | R/W      | Description                                                            | Defa |

|------|----------|----------|------------------------------------------------------------------------|------|

| 15:8 | Reserved | RW       | Not used                                                               | 0    |

| 7    | RMSE     | RW       | Enable of RMS HAGC<br>O:disable<br>1:enable                            | 0    |

| 6    | HAGCE    | RW       | Disable/Enable Peak AGC<br>O:disable<br>1:enable                       | 0    |

| 5    | HDCCE    | RW       | Enable/Disable Hardware DC Canceling module<br>0: disable<br>1: enable | 1    |

| 4    | HMUTE    | RW       | Enable/Disable Hardware mute module<br>0: disable<br>1: enable         | 1    |

|      |          | <u> </u> |                                                                        |      |

34

July. 2019 V1.0

July. 2019 V1.0

| 3:0 | BST_IPEAK | RW | Boost peak current limiter threshold<br>0000: 1.5A<br>0001: 1.75A<br>0010: 2.0A<br>0011: 2.25A<br>0100: 2.5A<br>0100: 2.5A<br>0101: 2.75A<br>0110: 3.0A<br>0111: 3.25A<br>1000: 3.5A<br>1001: 3.75A<br>1010: 4A<br>1011: 4.25A<br>Others: Reserved |  | 8 |

|-----|-----------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|---|

|-----|-----------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|---|

| I2SCTR | I2SCTRL: (Address 06h) |     |                                                                                                                                               |         |  |

|--------|------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

| Bit    | Symbol                 | R/W | Description                                                                                                                                   | Default |  |

| 15:14  | Reserved               | RW  | Not used                                                                                                                                      | 0       |  |

| 13     | INPLEV                 | RW  | Input level selection bit, when it is set to 1, all input signal will be<br>attenuated at first<br>0: not attenuated<br>1: attenuated by -6dB | 0       |  |

| 12     | I2SRXEN                | RW  | Disable/Enable I2S receiver module<br>0: disable<br>1: enable                                                                                 | 1       |  |

| 11:10  | CHSEL                  | RW  | Left/right channel selection for I2S input<br>00: reserved<br>01: left<br>10: right<br>11: mono, (L+R)/2                                      | 1       |  |

| 9:8    | I2SMD                  | RW  | I2S interface mode<br>00: Philip standard I2S (default)<br>01: MSB justified<br>10: LSB justified<br>11: Reserved                             | 0       |  |

| 7:6    | I2SFS                  | RW  | I2S LSB justified mode data width selection<br>00: 16 bits<br>01: 20 bits<br>10: 24 bits<br>11: 32 bits                                       | 3       |  |

| 5:4    | I2SBCK                 | RW  | I2S BCK mode<br>00: 32*fs(16*2)<br>01: 48*fs(24*2)<br>10: 64*fs(32*2)<br>11: Reserved                                                         | 2       |  |

July. 2019 V1.0

| 3:0 | I2SSR | RW | I2S interface sample rate configuration<br>0000: 8 kHz<br>0001: 11.025kHz<br>0010: 12 kHz<br>0011: 16 kHz<br>0100: 22.05kHz<br>0101: 24 kHz<br>0110: 32 kHz<br>0111: 44.1 kHz<br>1000: 48 kHz<br>1001: 96 KHz<br>1010: 192KHz<br>Others: Reserved |  | 8 |

|-----|-------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|---|

|-----|-------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|---|

| I2SCFG | I2SCFG1: (Address 07h) |     |                                                                                                                                                                                                                                                                          |         |  |

|--------|------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

| Bit    | Symbol                 | R/W | Description                                                                                                                                                                                                                                                              | Default |  |

| 15:14  | Reserved               | RW  | Not used                                                                                                                                                                                                                                                                 | 0       |  |

| 13:12  | I2S_TX_SLOTVLD         | RW  | TX slot selection, data will be sent to one of the four slots in TDM<br>mode.<br>00: Slot 0<br>01: Slot 1<br>10: Slot 2<br>11: Slot 3                                                                                                                                    | 0       |  |

| 11:8   | I2S_RX_SLOTVLD         | RW  | RX slots selection, two slots will be chosen as active slots in TDM<br>mode. Valid settings are as follows<br>0011: Slots 0 and 1<br>0101: Slots 0 and 2<br>1001: Slots 0 and 3<br>0110: Slots 1 and 2<br>1010: Slots 1 and 3<br>1100: Slots 2 and 3<br>Others: Reserved | 3       |  |

| 7:6    | CFSEL                  | RW  | I2S legacy path output data selection<br>00: HAGC data<br>01: IV sense data<br>Ohters: Reserved                                                                                                                                                                          | 0       |  |

| 5      | DRVSTREN               | RW  | I2S_DATAO PAD driving strength setting<br>0: 2mA<br>1: 8mA                                                                                                                                                                                                               | 1       |  |

| 4      | DOHZ                   | RW  | Unused channel data control<br>0: All Channels available<br>1: Hi-Z                                                                                                                                                                                                      | 1       |  |

| 3      | FSYNC_TYPE             | RW  | Audio Frame synchronization signal (WCK) pulse width configuration<br>0: one slot width<br>1: one BCK clock cycle                                                                                                                                                        | 0       |  |

| 2      | slot_num               | RW  | Slot number selection, the 2-slot mode is compatible with I2S, and 4-<br>slot mode is for TDM mode (max 4 slots support).<br>0: 2 slots<br>1: 4 slots                                                                                                                    | 0       |  |

| 1      | I2SCHS                 | RW  | I2S Tx Channel output selection<br>0: Left channel<br>1: Right channel                                                                                                                                                                                                   | 0       |  |

July. 2019 V1.0

| 0 | I2STXEN | RW | Disable/Enable I2S transmitter module<br>0: disable<br>1: enable | 0 |

|---|---------|----|------------------------------------------------------------------|---|

|---|---------|----|------------------------------------------------------------------|---|

| HAGCCFG1: (Address 09h) |        |     |                                                                                                                                        |         |  |  |

|-------------------------|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|

| Bit                     | Symbol | R/W | Description                                                                                                                            | Default |  |  |

| 15:8                    | RVTH   | RW  | Release Amplitude threshold, in percent of signal full scale                                                                           | 0x39    |  |  |

| 7:0                     | AVTH   | RW  | Attack Amplitude threshold, in percent of signal full scale<br>RMSE = 0: P0= ((i/256*Gain)**2)/8/2<br>RMSE = 1: P0=(i/256)*(Gain**2)/8 | 0x40    |  |  |

| HAGCC | FG2: (Address Oah) |     |                                                                                                |         |

|-------|--------------------|-----|------------------------------------------------------------------------------------------------|---------|

| Bit   | Symbol             | R/W | Description                                                                                    | Default |

| 15:0  | ATTH               | RW  | Attack time threshold in unit of 20.8µs<br>0: reserved<br>n: gain decreased 0.5db per n*20.8us | 0x0030  |

|       |                    |     |                                                                                                |         |

| HAGCCFG3: (Address 0bh) |        |     |                                                                                                 |         |

|-------------------------|--------|-----|-------------------------------------------------------------------------------------------------|---------|

| Bit                     | Symbol | R/W | Description                                                                                     | Default |

| 15:0                    | RTTH   | RW  | Release time threshold in unit of 20.8µs<br>0: reserved<br>n: gain decreased 0.5db per n*20.8µs | 0x01E0  |

| HAGCC | HAGCCFG4: (Address 0ch) |     |                                                                                                             |         |  |

|-------|-------------------------|-----|-------------------------------------------------------------------------------------------------------------|---------|--|

| Bit   | Symbol                  | R/W | Description                                                                                                 | Default |  |

| 15:8  | VOL                     | RW  | Volume control, from 0 to <mark>-9</mark> 6dB<br>[3:0] : in unit of -0.5dB<br>[7:4] : in unit of -6dB       | 0       |  |

| 7:0   | HOLDTH                  | RW  | Attack time threshold in unit of about 1.33ms<br>0: reserved<br>n: attack counter holding at least n*1.33ms | 0x64    |  |

| HAGCS | T: (Address 10h) |     |                                                                                                                                                                         |         |

|-------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Bit   | Symbol           | R/W | Description                                                                                                                                                             | Default |

| 15:6  | Reserved         | RO  | Not used                                                                                                                                                                | 0       |

| 5:0   | BSTVOUT_ST       | RO  | Actual setting of boost output voltage (125mV/Step)<br>000000:3.125V<br>000001:3.25V<br>000010:3.375V<br>000011:3.5V<br>000100:3.625V<br>000101:3.75V<br><br>111111:11V | 0       |

| VBAT: | (Address 12h) |     |                                                                                      |         |

|-------|---------------|-----|--------------------------------------------------------------------------------------|---------|

| Bit   | Symbol        | R/W | Description                                                                          | Default |

| 15:10 | Reserved      | RO  | Not used                                                                             | 0       |

| 9:0   | VBAT_DET      | RO  | Detected Voltage of battery, and the fullrange is 6.025V<br>V_BATS=(VBAT)/1023×6.025 | 0x263   |

37

July. 2019 V1.0

| BitSymbolR/WDescriptionDefault15:10ReservedRONot used0A servedRODetected Die Temperature(Two's Complement), typical values are as<br>follows.<br>0x3D8 : -40degree<br>0x00 : 0 degree<br>0x01 : 1 degree<br>0x1 : 1 degree<br>0x37 : 55 degree<br>Please convert it to decimal number please.0 | TEMP: (Address 13h) |          |     |                                                                                                             |         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------|-----|-------------------------------------------------------------------------------------------------------------|---------|

| 9:0  TEMP_DET  RO  Detected Die Temperature(Two's Complement), typical values are as follows.<br>0x3D8 : -40degree<br>0x00 : 0 degree<br>0x01 : 1 degree<br>0x19 : 25 degree<br>0x37 : 55 degree  0x019                                                                                        | Bit                 | Symbol   | R/W | Description                                                                                                 | Default |

| 9:0 TEMP_DET RO follows.<br>0x3D8:-40degree<br>0x00:0 degree<br>0x01:1 degree<br>0x19:25 degree<br>0x37:55 degree                                                                                                                                                                              | 15:10               | Reserved | RO  | Not used                                                                                                    | 0       |

|                                                                                                                                                                                                                                                                                                | 9:0                 | TEMP_DET | RO  | follows.<br>0x3D8 : -40degree<br>0x00 : 0 degree<br>0x01 : 1 degree<br>0x19 : 25 degree<br>0x37 : 55 degree | 0x019   |

| 15:10  Reserved  RO  Not used    9:0  RVDD_DET  RO  Detected Voltage of PVDD, and the fullrange is 12.05V | PVDD: | (Address 14h) |     |                                                                                     |  | ŕ       |

|-----------------------------------------------------------------------------------------------------------|-------|---------------|-----|-------------------------------------------------------------------------------------|--|---------|

| PLAN BLAD DET RO Detected Voltage of PVDD, and the fullrange is 12.05V                                    | Bit   | Symbol        | R/W | Description                                                                         |  | Default |

|                                                                                                           | 15:10 | Reserved      | RO  | Not used                                                                            |  | 0       |

| PVDD=(PVDD_DET)/1023×12.05                                                                                | 9:0   | PVDD_DET      | RO  | Detected Voltage of PVDD, and the fullrange is 12.05V<br>PVDD=(PVDD_DET)/1023×12.05 |  | 0x263   |

| BSTCTRL1: (Address 60h) |          |     |                                                                                                                                                                                                          |         |

|-------------------------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Bit                     | Symbol   | R/W | Description                                                                                                                                                                                              | Default |

| 15:14                   | Reserved | RW  | Not used                                                                                                                                                                                                 | 0       |

| 13:8                    | BST_RTH  | RW  | Smart boost release threshold setting, When signal is below the threshold, the voltage of VBST will not be raised up higher than VDD in smart boost mode<br>Release threshold = BST_RTH * 1/64 FullScale | 4       |

| 7:6                     | Reserved | RW  | Not used                                                                                                                                                                                                 | 0       |

| 5:0                     | BST_ATH  | RW  | Smart boost attack threshold setting. When signal is above over the threshold, the voltage of VBST will be raised up higher than VDD in smart boost mode<br>Attack threshold = BST_ATH * 1/64 FullScale  | 2       |

| BSTCTF | BSTCTRL2: (Address 61h) |     |                                                                                                                                                               |         |  |

|--------|-------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

| Bit    | Symbol                  | R/W | Description                                                                                                                                                   | Default |  |

| 15     | VOUT_CTMD               | RW  | BOOST output voltage control mode selection<br>0: PVDD controlled by VREF (125mV/step)<br>1: PVDD controlled by VFB (4 levels)                                | 0       |  |

| 14:12  | BST_MODE                | RW  | BOOST mode selection, Initialize to 6.<br>000: Transparent Mode<br>001: Force Boost Mode<br>011: Test Boost Mode<br>101: Class G Mode<br>Others: Class H Mode | 0x6     |  |

| 11     | Reserved                | RW  | Not used                                                                                                                                                      | 0       |  |

July. 2019 V1.0

| 10:8 | BST_TDEG     | RW | Smart ClassG Boost small signal level detection deglitch time<br>000: 0.33 ms<br>001: 1.40 ms<br>010: 5.60 ms<br>011: 21.30 ms<br>100: 44 ms<br>101: 88 ms<br>110: 352 ms<br>111: 1.4 s | 0x6  |  |

|------|--------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|

| 7:6  | VOUT_VFBSET  | RW | BOOST output voltage control bits controlled by VFB<br>00: 8.5V<br>01: 9.5V<br>10: 10.5V<br>11: 10.5V                                                                                   | 1    |  |