# 6-Channel Capacitive Touch Controller with 9-LED Driver

#### **FEATURES**

- 6-channel capacitive input with sensitivity configurable

- RF noise suppression

- Intrinsic capacitance cancelling

- Adaptive environmental variation compensation

- Auto calibration

- User-configurable gesture detection (slide and click)

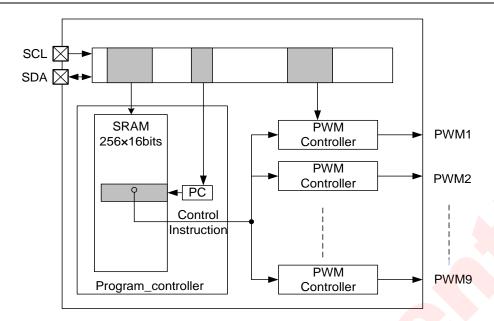

- 9 LED driver controlled by SRAM program

- 256word x16bit program SRAM

- Individual 8-step DC current, max 24.5mA

- Individual 256 step PWM dimming, 9 bit PWM resolution

- Touch and gesture triggers LED lighting program

- I<sup>2</sup>C compatible Interface: 1.8V ~ 2.8V, device address 0x2C/0x2D selectable

- Interrupt output pin

- Single power supply: 3.0V~4.5V

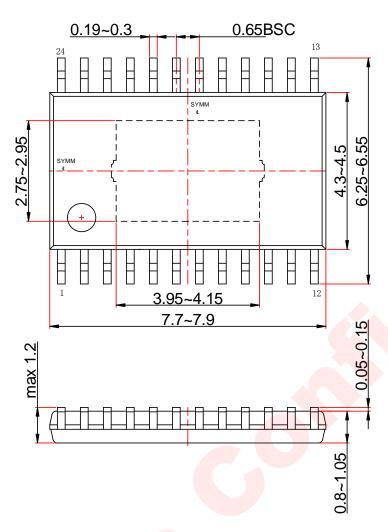

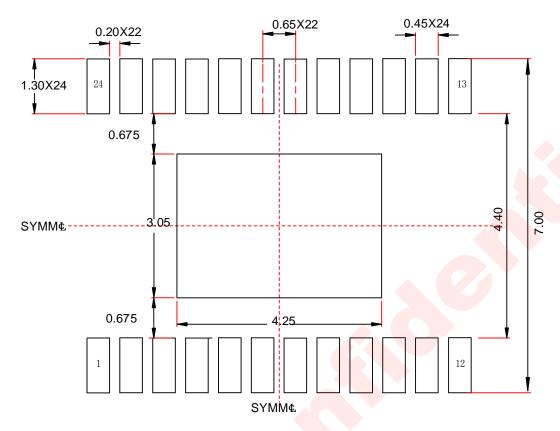

- TSSOP7.8mm×6.4mm\_24L Package

#### GENERAL DESCRIPTION

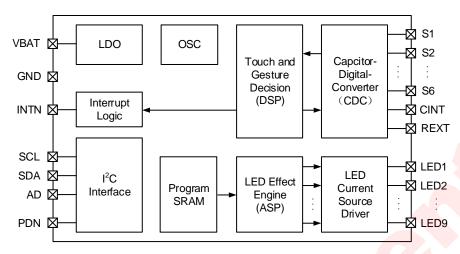

AW9069 integrates 6-channel capacitive input detection and a smart SRAM-controlled 9-LED driver. By SRAM programming and register configuration, the touch and/or gesture could trigger pre-defined program to generate funny and complicated LED lighting effect as feedback without the aid of external MCU, so as to greatly enhance the interactive experience and reduce power consumption.

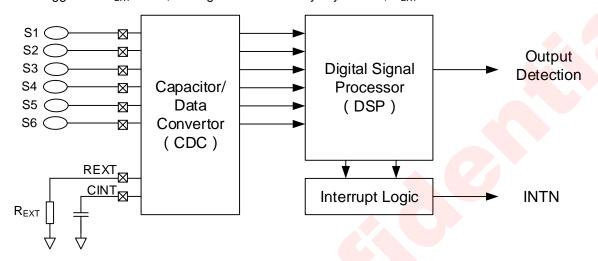

High performance sigma-delta capacitance digital conversion technology is adapted to detect input capacitance, and further touch and gesture decision is implemented by internal DSP.

9 LEDs are driven by independent constant current sinks with PWM duty adjustment. Each LED is selectable to be controlled by I<sup>2</sup>C interface directly or internal program in SRAM.

The device provides 400kHz fast I<sup>2</sup>C compatible interface with device address set by AD pin. The operating voltage range is 3.0V~4.5V.

## **APPLICATIONS**

White goods appliances, Intelligent devices

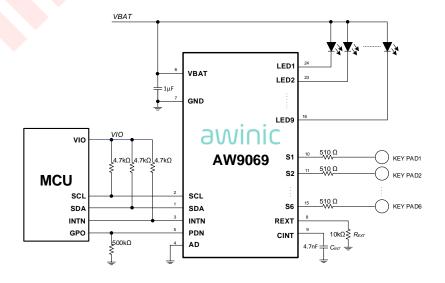

## TYPICAL APPLICATION CIRCUIT

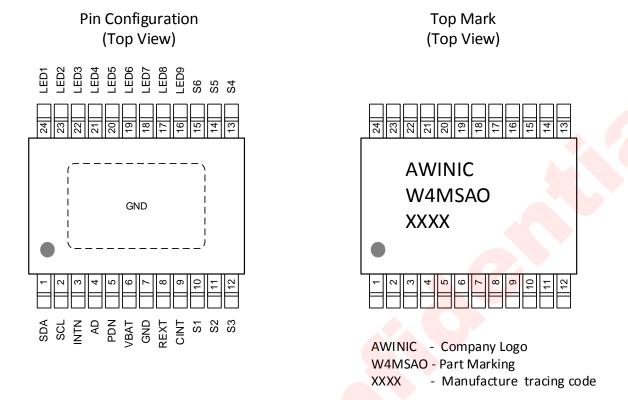

## PIN CONFIGURATION AND TOP MARK

Figure 1 AW9069 Pin Configuration and Top Mark

## **PIN DEFINITION**

| No. | NAME                                                                      | DESCRIPTION                                                                                     |  |  |  |  |

|-----|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|

| 1   | SDA                                                                       | Serial data I/O for I <sup>2</sup> C interface                                                  |  |  |  |  |

| 2   | SCL                                                                       | Serial clock input for I <sup>2</sup> C interface                                               |  |  |  |  |

| 3   | INTN                                                                      | Interrupt output (Open-drain), low Active. (Typically tie 4.7k $\Omega$ resistor to $V_{IO}$ ). |  |  |  |  |

| 4   | I <sup>2</sup> C device address selection. Internally pulled down to GND. |                                                                                                 |  |  |  |  |

| 5   | PDN                                                                       | Power down pin, low active(internal 1Mohm pull-down resistor)                                   |  |  |  |  |

| 6   | VBAT                                                                      | Power supply (3.0V to 4.5V)                                                                     |  |  |  |  |

| 7   | GND                                                                       | Ground                                                                                          |  |  |  |  |

| 8   | REXT                                                                      | External resistor for adjusting sensitivity (typical is 10kΩ)                                   |  |  |  |  |

| 9   | CINT                                                                      | External reference capacitor(typical is 4.7nF)                                                  |  |  |  |  |

| 10  | S1                                                                        | Capacitive touch input S1, floating if un-used                                                  |  |  |  |  |

| 11  | S2                                                                        | Capacitive touch input S2, floating if un-used                                                  |  |  |  |  |

| 12  | S3                                                                        | Capacitive touch input S3, floating if un-used                                                  |  |  |  |  |

| 13  | S4                                                                        | Capacitive touch input S4, floating if un-used                                                  |  |  |  |  |

| 14  | <b>S</b> 5                                                                | Capacitive touch input S5, floating if un-used                                                  |  |  |  |  |

| 15  | S6                                                                        | Capacitive touch input S6, floating if un-used                                                  |  |  |  |  |

| 16  | LED9                                                                      | LED9 cathode driver, anode connected to VBAT                                                    |  |  |  |  |

| 17          | LED8 | LED8 cathode driver, anode connected to VBAT |  |

|-------------|------|----------------------------------------------|--|

| 18          | LED7 | LED7 cathode driver, anode connected to VBAT |  |

| 19          | LED6 | LED6 cathode driver, anode connected to VBAT |  |

| 20          | LED5 | LED5 cathode driver, anode connected to VBAT |  |

| 21          | LED4 | LED4 cathode driver, anode connected to VBAT |  |

| 22          | LED3 | LED3 cathode driver, anode connected to VBAT |  |

| 23          | LED2 | LED2 cathode driver, anode connected to VBAT |  |

| 24          | LED1 | LED1 cathode driver, anode connected to VBAT |  |

| Thermal Pad | GND  | Ground                                       |  |

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 2 Functional Block Diagram

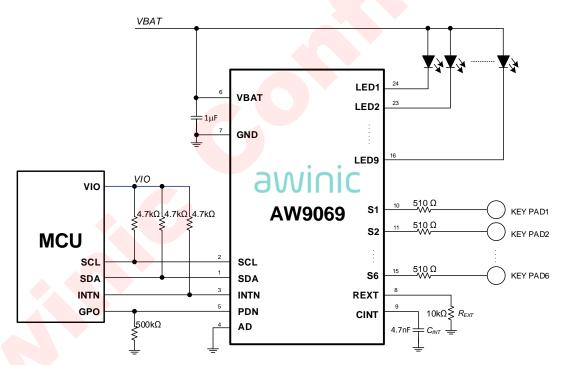

## TYPICAL APPLICATION CIRCUITS

Figure 3 AW9069 Typical Application Circuit

**NOTE1.** Pin S1 - S6 must be connected to a  $500\Omega \sim 600\Omega$  resistor.

NOTE2.  $C_{INT}$  and  $R_{EXT}$  should be placed as close as possible to the chip.

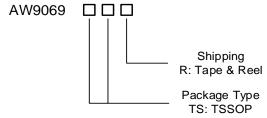

## **ORDERING INFORMATION**

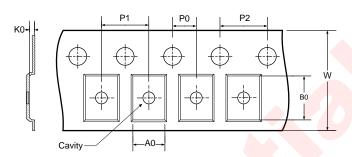

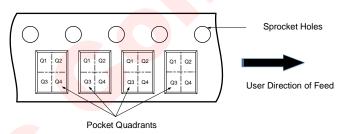

| Part Number | Temperature | Package                      | Marking          | Marking MSL Level |         | <b>Delivery Form</b>         |  |

|-------------|-------------|------------------------------|------------------|-------------------|---------|------------------------------|--|

| AW9069TSR   | -40°C~85°C  | TSSOP<br>7.8mmX6.4mm<br>-24L | AWINIC<br>W4MSAO | MSL3              | ROHS+HF | 3000 units/<br>Tape and Reel |  |

# **ABSOLUTE MAXIMUM RATINGS**(NOTE 3)

| PARAMETERS                                             |                                                                                                                                                                  |  |  |  |  |  |  |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Supply voltage range V <sub>BAT</sub>                  |                                                                                                                                                                  |  |  |  |  |  |  |

| SCL, SDA, AD                                           | -0.3V to 3.6V                                                                                                                                                    |  |  |  |  |  |  |

| PDN, LED1~9                                            | -0.3V to 4.5V                                                                                                                                                    |  |  |  |  |  |  |

| SDA, INTN                                              | -0.3V to 3.6V                                                                                                                                                    |  |  |  |  |  |  |

| Junction-to-ambient thermal resistance θ <sub>JA</sub> |                                                                                                                                                                  |  |  |  |  |  |  |

| Operating free-air temperature range                   |                                                                                                                                                                  |  |  |  |  |  |  |

| Maximum Junction temperature T <sub>JMAX</sub>         |                                                                                                                                                                  |  |  |  |  |  |  |

| e T <sub>STG</sub>                                     | -65°C to 150°C                                                                                                                                                   |  |  |  |  |  |  |

| ng 10 Seconds)                                         | 260°C                                                                                                                                                            |  |  |  |  |  |  |

| ESD <sup>(NOTE 4)</sup>                                |                                                                                                                                                                  |  |  |  |  |  |  |

|                                                        | ±4000V                                                                                                                                                           |  |  |  |  |  |  |

|                                                        | ±2000kV                                                                                                                                                          |  |  |  |  |  |  |

|                                                        |                                                                                                                                                                  |  |  |  |  |  |  |

| Latch-up                                               |                                                                                                                                                                  |  |  |  |  |  |  |

| Test Condition: JEDEC STANDARD NO.78E SEPTEMBER 2016   |                                                                                                                                                                  |  |  |  |  |  |  |

| J. TOE SEFTEINDER 2010                                 | -IT: -450mA                                                                                                                                                      |  |  |  |  |  |  |

|                                                        | SCL, SDA, AD PDN, LED1~9 SDA, INTN I resistance θ <sub>JA</sub> rature range erature T <sub>JMAX</sub> e T <sub>STG</sub> ng 10 Seconds) ESD <sup>(NOTE 4)</sup> |  |  |  |  |  |  |

NOTE3: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

NOTE4: The human body model is a 100pF capacitor discharged through a 1.5k $\Omega$  resistor into each pin. Test method: MIL-STD-883J Method 3015.9

## **ELECTRICAL CHARACTERISTICS**

V<sub>BAT</sub>=3.8V, T<sub>A</sub>=25°C for typical values (unless otherwise noted)

|                          | PARAMETER                          | TEST CONDITION                     | MIN  | TYP  | MAX  | UNIT |

|--------------------------|------------------------------------|------------------------------------|------|------|------|------|

| $V_{BAT}$                | Power supply                       |                                    | 3.0  | 3.8  | 4.5  | V    |

| I <sub>SHUTDOWN</sub>    | Current in Shutdown mode           | PDN=GND                            |      | 8    | 15   | μА   |

| I <sub>STANDBY</sub>     | Current in Standby mode            | PDN=V <sub>IO</sub>                |      | 130  | 160  | μА   |

|                          | Current in LED Active mode         | PDN=V <sub>IO</sub> , GCR=0x01     |      | 0.55 | 0.8  | mA   |

| I <sub>ACTIVE</sub>      | Current in Touch Active mode       | PDN=V <sub>IO</sub> , GCR=0x02     |      | 0.85 | 1.0  | mA   |

| ACTIVE                   | Current in Touch & LED Active mode | PDN=V <sub>IO</sub> , GCR=0x03     |      | 1.0  | 1.5  | mA   |

| Fosc                     | Internal oscillator Frequency      |                                    | 15.2 | 16   | 16.8 | MHz  |

| Digital Lo               | gical Interface                    |                                    |      |      |      |      |

| V <sub>IL</sub>          | Logic input high level             | SDA,SCL,AD,PDN                     | -0.3 |      | 0.45 | V    |

| V <sub>IH</sub>          | Logic input low level              | SDA,SCL,AD,PDN                     | 0.9  |      |      | V    |

| I <sub>IL</sub>          | Low level input current            | SDA,SCL,AD,PDN                     |      | 5    |      | nA   |

| I <sub>IH</sub>          | High level input current           | SDA,SCL,AD,PDN                     |      | 5    |      | nA   |

| $V_{OL}$                 | Logic output low level             | SDA, INTN<br>I <sub>OUT</sub> =3mA |      |      | 0.4  | V    |

| I <sub>OL</sub>          | Maximum output current             | SDA, INTN                          |      |      | 10   | mA   |

| IL                       | Output leakage current             | SDA,INTN Open drain                |      |      | 1    | μА   |

| Capacitive               | Sensor                             |                                    |      |      |      |      |

| CX <sub>range</sub>      | Range <sup>(NOTE5)</sup>           | S1 to S6                           | 0    |      | 80   | pF   |

| CX <sub>resolution</sub> | Resolution <sup>(NOTE5)</sup>      | S1 to S6                           | 0.02 |      |      | pF   |

| F <sub>SCAN</sub>        | Scan frequency                     |                                    |      | 30   |      | Hz   |

| T <sub>DET</sub>         | Response time                      |                                    |      | 100  |      | ms   |

| LED Drive                |                                    |                                    |      |      |      |      |

| I <sub>MAX</sub>         | Max LED current of LED1~9          | I <sub>LED</sub> =24.5mA           | 18.5 | 24.5 | 30.5 | mA   |

| I <sub>MATCH</sub>       | Matching accuracy                  | I <sub>LED</sub> =24.5mA           |      |      | 10   | %    |

| V <sub>DROPOUT</sub>     | Drop-out voltage                   | I <sub>LED</sub> =24.5mA           |      |      | 300  | mV   |

| F                        | PWM frequency                      | LCR.FREQ=1                         | 110  | 122  | 135  | Hz   |

| F <sub>PWM</sub>         | 1 vvivi ii equelicy                | LCR.FREQ=0                         | 220  | 244  | 270  | Hz   |

NOTE5: the value is tested in default configuration.

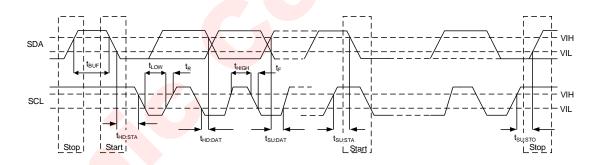

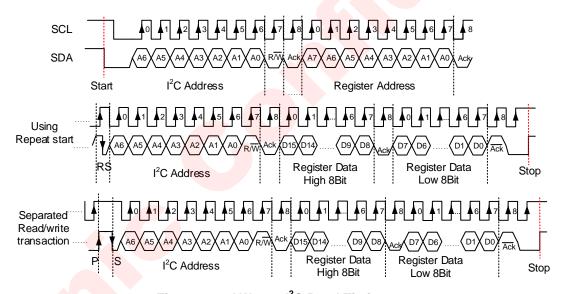

# I<sup>2</sup>C INTERFACE TIMING

|                       | Parameter Name                    |           | MIN | TYP | MAX | UNIT |

|-----------------------|-----------------------------------|-----------|-----|-----|-----|------|

| F <sub>SCL</sub>      | Interface Clock frequency         |           |     | 400 | kHz |      |

| T <sub>DEGLITCH</sub> | Do alitab tion a                  | SCL       |     | 200 |     | ns   |

|                       | Deglitch time                     | SDA       |     | 250 |     | ns   |

| T <sub>HD:STA</sub>   | (Repeat-start) Start condition he | old time  | 0.6 |     |     | μs   |

| T <sub>LOW</sub>      | Low level width of SCL            | 1.3       |     |     | μs  |      |

| T <sub>HIGH</sub>     | High level width of SCL           |           | 0.6 |     |     | μs   |

| T <sub>SU:STA</sub>   | (Repeat-start) Start condition se | etup time | 0.6 | •   |     | μs   |

| T <sub>HD:DAT</sub>   | Data hold time                    |           | 0   |     |     | μs   |

| T <sub>SU:DAT</sub>   | Data setup time                   |           | 0.1 |     |     | μs   |

| T <sub>R</sub>        | Rising time of SDA and SCL        | ). (C     |     | 0.3 | μs  |      |

| T <sub>F</sub>        | Falling time of SDA and SCL       |           |     | 0.3 | μs  |      |

| T <sub>SU:STO</sub>   | Stop condition setup time         | 0.6       |     |     | μs  |      |

| T <sub>BUF</sub>      | Time between start and stop co    | ondition  | 1.3 |     |     | μs   |

Figure 4 I<sup>2</sup>C Timing

#### **FUNCTIONAL DESCRIPTION**

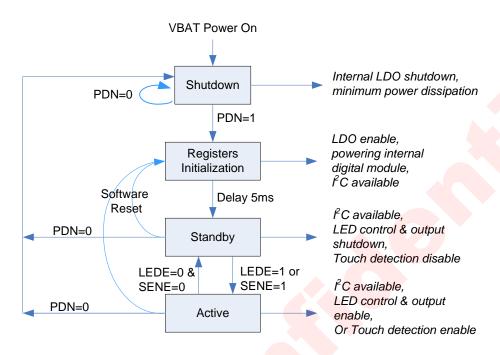

#### **WORK MODE**

Figure 5 AW9069 Work Mode

After VBAT powered on, if pin PDN is low, the AW9069 is in shut-down mode, the current consumption is typically less than  $10\mu A$ . When PDN pin becomes high, the internal LDO is activated, and a power-on reset (POR) signal is generated to reset all internal registers, the device enters standby mode in low power consumption state, when all circuit functions are disabled. In standby mode, I<sup>2</sup>C interface is active, all internal configuration register can be written. If control bit GCR.SENE or/and GCR.LEDE is set to "1", the device enters the active mode.

#### RESET

#### Hardware Reset

When pin PDN changes from low to high, the power-up reset (POR) signal is generated, all internal registers are reset.

#### Software Reset

Writing 0x55AA to register RSTR via I<sup>2</sup>C interface will activate a software reset to reset all internal registers.

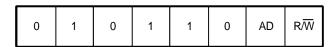

#### I<sup>2</sup>C INTERFACE

AW9069 supports the I<sup>2</sup>C serial bus and data transmission protocol in fast mode at 400kHz. It operates as a slave on the I<sup>2</sup>C bus. Connections to the bus are made via the open-drain I/O pins SCL and SDA. The pull-up resistor can be selected in the range of  $1k\sim10k\Omega$  and the typical value is  $4.7k\Omega$ . I<sup>2</sup>C interface voltage range is  $1.8V\sim3.3V$ .

#### **Device Address**

The I $^2$ C device address (7-bit, followed by the R/W bit(Read=1/Write=0)) of AW9069 depends on the status of pin AD. When pin AD is tied low or floating, the device address is 0x2C; when pin AD is tied high, the device address is 0x2D.

Figure 6 Device Address Configuration

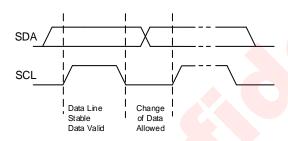

#### Data Validation

When SCL is high level, SDA level must be constant. SDA can be changed only when SCL is low level.

Figure 7 Data Validation Diagram

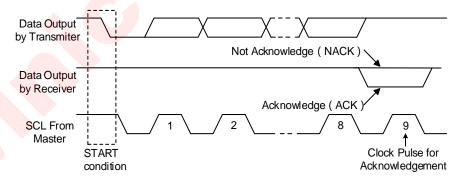

#### ACK(Acknowledgement)

ACK means the successful transfer of I<sup>2</sup>C bus data. After master sends 8bits data, SDA must be releases; SDA is pulled to GND by slave device when slave acknowledges.

When master reads, AW9069 sends 8bit data, releases the SDA and waits for ACK from master. If ACK is sent and I<sup>2</sup>C stop is not sent by master, AW9069 sends the next data. If ACK is not sent by master, AW9069 stops to send data and waits for I<sup>2</sup>C stop.

Figure 8 I<sup>2</sup>C ACK Timing

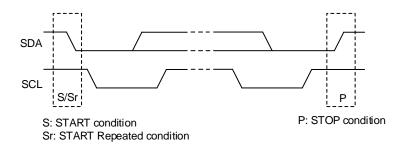

## PC Start/Stop

I<sup>2</sup>C start: SDA changes form high level to low level when SCL is high level.

I<sup>2</sup>C stop: SDA changes form low level to high level when SCL is high level.

Figure 9 I<sup>2</sup>C Start/Stop Condition Timing

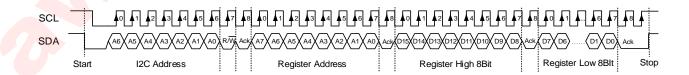

#### Write Cycle

One data bit is transferred during each clock pulse. Data is sampled during the high state of the serial clock (SCL). Consequently, throughout the clock's high period, the data should remain stable. Any changes on the SDA line during the high state of the SCL and in the middle of a transaction, aborts the current transaction. New data should be sent during the low SCL state. This protocol permits a single data line to transfer both command/control information and data using the synchronous serial clock.

Each data transaction is composed of a Start Condition, a number of byte transfers (set by the software) and a Stop Condition to terminate the transaction. Every byte written to the SDA bus must be 8 bits long and is transferred with the most significant bit first. After each byte, an Acknowledge signal must follow.

In a write process, the following steps should be followed:

- a) Master device generates START condition. The "START" signal is generated by lowering the SDA signal while the SCL signal is high.

- b) Master device sends slave address (7-bit) and the data direction bit  $(R/\overline{W} = 0)$ .

- c) Slave device sends acknowledge signal if the slave address is correct.

- d) Master sends control register address (8-bit)

- e) Slave sends acknowledge signal

- f) Master sends data high 8Bit to be written to the addressed register

- g) Slave sends acknowledge signal

- h) Master sends data low 8Bit to be written to the addressed register

- I) Slave sends acknowledge signal

- j) Master generates STOP condition to indicate write cycle end

Figure 10 AW9069 I<sup>2</sup>C Write Timing

#### Read Cycle

In a read cycle, the following steps should be followed:

- a) Master device generates START condition

- b) Master device sends slave address (7-bit) and the data direction bit  $(R/\overline{W} = 0)$ .

- c) Slave device sends acknowledge signal if the slave address is correct.

- d) Master sends control register address (8-bit)

- e) Slave sends acknowledge signal

- f) Master generates STOP condition followed with START condition or REPEAT START condition

- g) Master device sends slave address (7-bit) and the data direction bit  $(R/\overline{W} = 1)$ .

- h) Slave device sends acknowledge signal if the slave address is correct.

- i) Slave sends data high 8Bit from addressed register.

- j) Master sends acknowledge signal

- k) Slave sends data low 8Bit from addressed register.

- I) If the master device sends acknowledge signal, the slave device will increase the control register address by one, then send the next data from the new addressed register. If master sends no acknowledge signal, the slave device stop to send data and wait for STOP condition.

- If the master device generates STOP condition, the read cycle is ended.

Figure 11 AW9069 I<sup>2</sup>C Read Timing

#### **OSCILLATOR**

An internal oscillator provides clock for both capacitive touch detecting and LED controlling circuit. If bit SENE or LENE in register GCR is set, the OSC starts to work, the start-up time is about 5 us. When both the register bit SENE and LEDE are "0", the internal OSC stops.

#### CAPACITIVE TOUCH DETECTION

With high performance sigma-delta capacitive digital conversion technology, the capacitance on pin Sx is measured, the finger touch decision is made according to the increment of Sx capacitance. Before finger touched, the key capacitance is only formed by the sensing electrode and surrounding ground, which is called intrinsic capacitance usually. When finger touched, an additional parallel plate capacitor (electrode-media-finger) is formed, resulting in the capacitance value increment on pin Sx. In general,

because of the variation of different electrode size and dielectric characteristic of media materials, the capacitance increment caused by finger touch varies in a range of about 0.5pF~5pF.

In AW9069, the resolution of CDC data is 12-bit. the sampling period can be set by control register. The capacitive sample are send to DSP for further processing, including digital filtering, base-line compensation, touch and gesture judge, and so on.

The capacitive sensitivity can be adjusted by externally connected resistance  $R_{EXT}$  between pin REXT and GND. The bigger the  $R_{EXT}$  value, the higher the sensitivity. By default,  $R_{EXT}$  is recommended to be  $10k\Omega$ .

Figure 12 Functional Block of Capacitive Touch Detection

When control bit SENE in register GCR is 0, all capacitive touch detection circuit is reset. When control bit SENE is set, the SLPR register control the enable/disable touch detection. If control bits SLPx (x=1,2,..,6) in register SLPR is 0, touch detection on pin Sx is activated. If control bits SLPx is set to 1, touch pin Sx is disabled to save power consumption.

#### **Touch Status**

In AW9069, the raw touch detection result of pin S1~S6 can be read via register RAWST (address 0x31).

#### Adjacent key suppression

Usually when a touch key is designed small and very close to the adjacent key, it is very possible that one finger touch trigger not only the intend key, but the surrounding keys also. The AW9069 supports the so-called adjacent suppression (AKS) function.

The register AKSCR(address 0x07) defines the AKS group, select which keys are included for AKS recognition. When more than one key in AKS group are triggered at the same time, the AKS algorithm identify the only most likely key in AKS group, and output the detect result with AKS function in register KEYST (address 0x32).

#### Touch Interrupt

Touching status can generate the interrupt output on pin INTN, the interrupt enable control is defined by register KINTER (address 0x03). There are 4 interrupt mode selections defined by control bits KIMD[1:0] in register KINTER to select interrupt triggered by different event.

- KIMD[1:0] =00 interrupt triggered when touch status changed

- KIMD[1:0] =01 interrupt triggered when touch status changed from 1 to 0 (key released)

- KIMD[1:0] =10 interrupt triggered when touch status changed from 0 to 1 (key touched)

- KIMD[1:0] =11 interrupt triggered when touch status is 1 (touch active)

The INTN pin is driven in Open-drain mode, and usually connected to VIO via pull-up resistor.

When interrupt is active, the corresponding bit in interrupt status register KISR (0x30) will be set, and if the corresponding enable bit in register KINTER (address 0x03) is "1", the pin INTN is pulled down to GND to inform interrupt to the external MCU. Once the interrupt status register KISR is read via  $I^2$ C interface, it will be cleared, then the pin INTN will be released and pulled up to  $V_{IO}$  by external resistor.

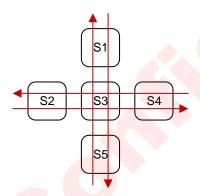

#### Gesture Detection

Besides for touch detection, AW9069 provides gesture detection function, such as slide and click (single, double and triple click), which is implemented automatically by internal gesture recognition module. Once one gesture is detected, the corresponding bit in gesture interrupt status register GISR (address 0x2E) will be set. The enable bit in gesture interrupt enable register GIER (address 0x2D) defines whether gesture event output to pin INTN.

#### Slip gesture

The slider is consisted of several sense electrodes (keys). When finger touching slips over the slider, touched state will be detected one by one in certain sequence. The gesture detection module identifies the gesture based on the comparing of occurring order of touch detected with the predefined sequence in register GSTRx.

Figure 13 An Example of Slide Gesture

The figure above gives a general touch key application supporting slide gesture. The left-slide and right-slide are defined as slip along keys S4-S3-S2 and along keys S2-S3-S4 respectively. The down-slide and up-slide gesture are defined as touch along keys S1-S3-S5 and along keys S5-S3-S1 respectively.

#### Tap gesture

Tap gesture means that finger click the touchpad quickly. there are 3 types of tap can be recognized by AW9069: single click, double click and triple click, and usually the single click and double click are adapted mostly. The continuously, fast finger clicks on touch sensor will make the touch detection status switching between ON and OFF state quickly. By analyzing the touch status and timing of ON/OFF transition, pre-defined tap gesture can be detected.

#### Gesture configuration

The registers GDCR (address 0x20), GDTR(address 0x21),TDTR(address 0x22) defines the basic configuration of gesture detection, such as the sensor selection for tap gesture, the max OFF time during slide detection, the max ON and OFF time during tap detection, and so on. The bit7 (GSTMD) of register GDCR set the time to report gesture detected. If GSTMD=0, gesture detected status is set when finger has left the touch pad completely. If GSTMD=1, gesture status is set as soon as the predefined sequence of touch event is checked.

The register GSSR1~4 (address 0x23~0x26) configure 4 user-defined slide gestures.

AW9069 Nov. 2017 V1.0

| 15 | 14     | 13 | 12 | 11 | 10   | 9 | 8 | 7 | 6    | 5 | 4 | 3 | 2    | 1 | 0 |

|----|--------|----|----|----|------|---|---|---|------|---|---|---|------|---|---|

| 0  | KCODE1 |    | 0  | K  | CODE | 2 | 0 | K | CODE | 3 | 0 | K | CODE | 4 |   |

KCODE1~4 is the encoding of pin Sx (x=1~6), which is defined as "000" for pin S1, "001" for pin S2, ..., "110" for S6. If KCODEx="000", no touch pin is selected.

The touch sequence of current slide gesture is always defined as: KCODE1 – KCODE2-KCODE3 – KCODE4. In AW9069, any slide gesture needs more than 3 touch input involved. If the slider only contains only 3 inputs, KCODE1~3 must be set, and KCODE4 must be set as "000".

Register TAPR(address 0x27) defines the click gesture.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5  | 4   | 3 | 2 | 1   | 0   |

|----|----|----|----|----|----|---|---|---|---|----|-----|---|---|-----|-----|

| 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 |   |   | CS | SEL |   |   | TIM | 1ES |

Bits TIMES[1:0] selects different mode of click gesture. If TIMES ="01", single click mode is enabled; if TIMES="10", double click mode is enabled; if TIMES="11", triple click is enabled.

Bits CEL[5:0] select the touch inputs relevant to click gesture, if CSEL[x]=1, pin Sx is selected for click gesture detection. If more than one touch input are set, all input will be looked as one key to detect gesture.

By default, 4 slide and 1 double-click have been defined in relevant registers, which is shown in the table below.

| Register Name | Default Value | Input Selection | Gesture Defined     |  |  |

|---------------|---------------|-----------------|---------------------|--|--|

| GSSR1         | 2340h         | S2-S3-S4        | Slip to Right Side  |  |  |

| GSSR2         | 4320h         | S4-S3-S2        | Slip to Left Side   |  |  |

| GSSR3         | 1350h         | S1-S3-S5        | Slip to upper Side  |  |  |

| GSSR4         | 5310h         | S5-S3-S1        | Slip to bottom Side |  |  |

| TAPR1         | 0012h         | S3              | Double clock on S3  |  |  |

#### **Gesture Interrupt**

The result of gesture detection can be read in interrupt status register GISR (address 0x2E). If the an pre-defined gesture is detected, the bit GISx or TISx in register GISR will be set. The register GIER(address 0x2D) is interrupt enable register of gesture detection.

If a gesture is detected and the corresponding interrupt is enable, interrupt will occur to pull down INTN pin. After a reading of register via I<sup>2</sup>C interface, the interrupt would be removed, pin INTN be released and then pulled high, the register GISR be cleared to "0x0000".

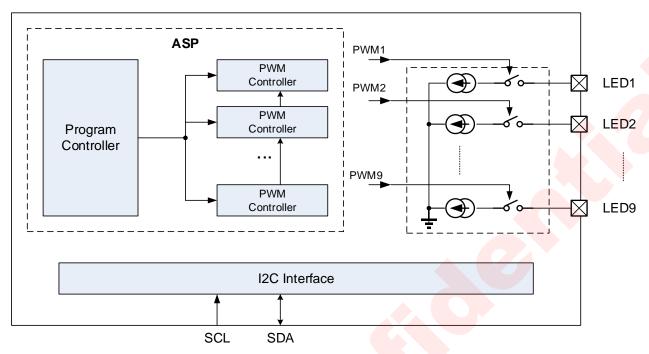

#### LED DRIVER

In AW9069, 9 LED is driven by independent constant current sinks to drive LEDs. A dedicated Application-Specific-Processor (ASP)is designed to produce versatile lighting effect for different application.

If the control bit GCR.LEDE is 0, LED driver circuit is in reset state, all 9 LED outputs are disabled. If control bit LEDE in register GCR is set to "1", the LED driver circuit is enabled, the control bits LENx (x=1 to 9) in register LER configure the corresponding LED channel is active or not.

Figure 14 AW9069 LED Dimming Control Module Diagram

#### LED brightness controller

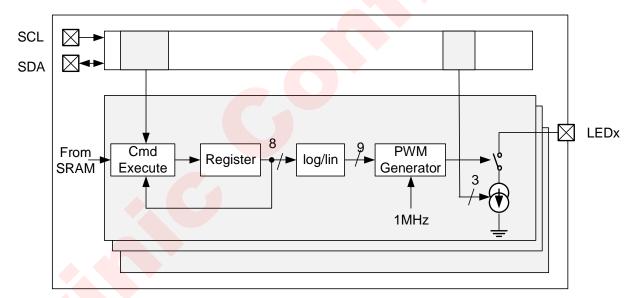

In AW9069, Pulse Width Modulation (PWM) is used to adjust the brightness of LED. The PWM is 8-bit /256-step programmable with 12-bit resolution. And the frequency of PWM could be configured between 125Hz or 250Hz by control bit FREQ in register LCR (address 0x52).

The ASP execute the user-preloaded program in a 256word x 16bit SRAM, and control the PWM level of all LEDs to produce complicated LED lighting effect.

With the setting of register CGRS (address 0x55), each LED controller can be selected to be controlled by SRAM program or by I<sup>2</sup>C directly.

- CTRS[n] = 0, LEDn controller is controlled by the internal SRAM instruction;

- CTRS[n] = 1, LEDn controller is controlled by the external  $I^2$ C instruction.

#### LED Constant current driver

For each LED, the output DC current is set by register IMAX (address 0x57~0x59), there are 8-step of current options, and the max current is 24.5mA. The constant current output of each LED driver is regulated by PWM level from ASP for dimming adjustment.

The register LER (address 0x50) controls individual LED to be work or not. If bit LEx is set to "1", the corresponding LEDx output is enabled. If bit LEx is "0", the pin LEDx output is disabled.

#### ASP

In AW9069, the ASP is consisted of one program controller and 9 PWM controllers.

Figure 15 ASP Structure Diagram

#### **Program Controller**

The program controller is clocked by 32kHz internal clock, each instruction is executed in one clock cycle.

The program controller contains a program SRAM, an algorithmic logic unit (ALU), timer and other internal registers. The 256x16bit internal SRAM is used to store LED lighting effect program loaded through I<sup>2</sup>C interface, the I<sup>2</sup>C interface also can start or stop the program execution.

There are 4 internal registers RA/RB/RC/RD participating ALU operation so as to generate complicated program control, such as repeating and looping. Except for that, there are 8 8-bit temporary data registers(R1~R8) and 5 special function registers. Their internal address and function description is shown in the table below.

Register Address(HEX) Illustration 00 R1 data temporary register, 8bit, I<sup>2</sup>C readable R1 R2 01 R2 data temporary register, 8bit, I<sup>2</sup>C readable R3 data temporary register, 8bit, I<sup>2</sup>C readable R3 02 R4 data temporary register, 8bit, I<sup>2</sup>C readable R4 03 R5 04 R5 data temporary register, 8bit, I<sup>2</sup>C readable R6 05 R6 data temporary register, 8bit, I<sup>2</sup>C readable R7 06 R7 data temporary register, 8bit, I<sup>2</sup>C readable R8 07 R8 data temporary register, 8bit, I<sup>2</sup>C readable **AKST** 80 Touch status with AKS **KST** 09 Raw touch status TISR1 Key interrupt status register, clear after reading 0a TISR2 0b Key interrupt status register, clear after reading 0c reserved GMSK1 0d Global control mask register(M8~M1) GMSK2 0e Global control mask register(M9)

Table 1 ASP Internal Data Registers List

Table 2 Particular registers detail illustration

| Register         B7         B6         B5         B4         B3         B2         B1         B0         Illustration |  |

|-----------------------------------------------------------------------------------------------------------------------|--|

|-----------------------------------------------------------------------------------------------------------------------|--|

| KST     | -  | -  | K6    | K5    | K4    | K3    | K2    | K1    | Touch status, Kx=1 means Sx is touched.                                  |  |  |

|---------|----|----|-------|-------|-------|-------|-------|-------|--------------------------------------------------------------------------|--|--|

| KST_AKS | -  | -  | AST6  | AST5  | AST4  | AST3  | AST2  | AST1  | AKS touch status, ASTx=1 means that Sx is touched.                       |  |  |

| TISR1   | -  | -  | KINT6 | KINT5 | KINT4 | KINT3 | KINT2 | KINT1 | Touch interrupt status. Cleared by ASP reading.                          |  |  |

| TISR2   | -  | -  | -     | TAP   | G4    | G3    | G2    | G1    | Gesture interrupt status. Cleared by ASP reading.                        |  |  |

| GMSK1   | M8 | M7 | M6    | M5    | M4    | МЗ    | M2    | M1    | Mask control for global control instruction. When Mn=1, LEDn will not be |  |  |

| GMSK2   | -  | -  | -     | -     | -     | -     | -     | M9    | affected by global control instruction.                                  |  |  |

#### **PWM Controller**

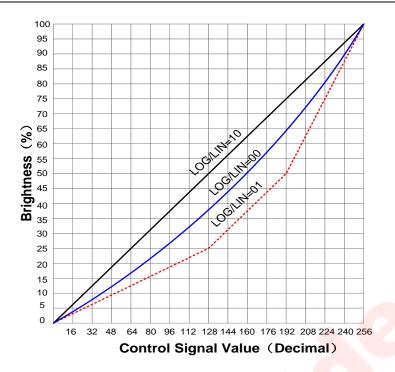

The PWM controller is execution unit of LED control instruction. There are 9 PWM controllers receiving the LED effect instruction from SRAM, and generate 8bit PWM code, which will be convert to 12bit duty cycle control code by logarithmic I transformation. If bits LOGLN[1:0] of register LCR is "00", the transformation is natural logarithm(  $log_e$ ). If LOGLN[1:0] is "01", the transformation is logarithm of 10 ( $log_{10}$ ), otherwise the 8b-to-12b transformation of PWM code is linear..

Figure 16 PWM Controller

Figure 17 PWM Dimming Curve

#### **Program Loading and execution**

#### a) Program loading

It is recommended to load SRAM program only when control bits PROGMD[1:0] of register PMD is "00". In this state, the internal program can be read/write through I<sup>2</sup>C interface. When loading program, please write the SRAM loading address in register WADDR(address 0x7E) at first, and then write the 16bit LED effect instruction to register WDATA(address 0x7F). Continuously loading program is supported, after a 16b instruction is written through register WDATA, the value of WADDR will automatically plus by 1.

#### b) Program execution

Register bits PROGMD[1:0] in register PMD controls the loading and execution mode of SRAM program.

When PROGMD[1:0]= "00", program execution is shut down, SRAM program and program pointer(PC) are permitted to be loaded.

When PROGMD[1:0] is written to be "01" from another value, current program will stop, and PC will be reload by register SADDR, and then executes the SRAM program starting from the address of PC

When PROGMD[1:0] ="10", the SRAM program will be executed by the mode defined by register bit RMD.RUNMD[1:0]

Table 3 Program running mode control register

| RMD.RUNMD | Function Description                                                                                                                                                                            |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 0       | Hold mode. program stop and PC hold after one instruction is finished.                                                                                                                          |

| 0 1       | Single step mode, only used for debugging. Once writing 01 to bits RUNMD[1:0] in register RMD, only one instruction will be executed with PC+1, and then RUMND is cleared (return to hold mode) |

| 1 0       | Continuously running mode, program starts from the address of PC.                                                                                                                               |

| 1 1       | Repeating mode, only used for debugging. Once writing 11 to RUNMD, current instruction will be executed without PC+1, and then RUMND is cleared (return to hold mode)                           |

#### **SRAM** program instructions

There are 27 commands in ASP instruction set, including LED control command, data operation and transfer command, wait and branch control command. The Rx, Ry and Rz in instruction list means the internal register RA, RB, RC and RD, each of them can participate the ALU operation as source or destination register.

Table 4 LED Effect Instruction

| Command               | 15 | 14 | 13  | 12 | 11 | 10  | 9    | 8   | 7             | 6 | 5 | 4   | 3     | 2    | 1   | 0   |

|-----------------------|----|----|-----|----|----|-----|------|-----|---------------|---|---|-----|-------|------|-----|-----|

| JP                    | 0  | 0  | 0   | 0  | 0  | 0   | 0    | 0   |               |   |   | ADD | R[7:0 | )]   |     |     |

| NOP                   | 0  | 0  | 0   | 0  | 0  | 0   | 0    | 1   | -             | - | - | -   | -     |      | -   | -   |

| JPZ Addr              | 0  | 0  | 0   | 0  | 0  | 1   | 0    | 0   |               |   |   | ADD | R[7:0 | ]    |     |     |

| JPNZ Addr             | 0  | 0  | 0   | 0  | 0  | 1   | 0    | 1   |               |   |   | ADD | R[7:0 | )]   |     |     |

| JPS Addr              | 0  | 0  | 0   | 0  | 0  | 1   | 1    | 0   |               |   |   | ADD | R[7:0 | )]   |     |     |

| JPNS Addr             | 0  | 0  | 0   | 0  | 0  | 1   | 1    | 1   |               |   |   | ADD | R[7:0 | )]   |     |     |

| LD Rz Im              | 0  | 0  | 0   | 0  | 1  | 0   | F    | Rz  |               |   |   | lm  | [7:0] |      |     |     |

| CMPI Rz Im            | 0  | 0  | 0   | 0  | 1  | 1   | F    | Rz  |               |   |   | lm  | [7:0] |      |     |     |

| ANDR Rz Im            | 0  | 0  | 0   | 1  | 0  | 0   | F    | Rz  |               |   |   | lm  | [7:0] |      |     |     |

| ORR Rz Im             | 0  | 0  | 0   | 1  | 0  | 1   | F    | Rz  |               |   |   | lm  | [7:0] |      |     |     |

| RDR Rz Addr           | 0  | 0  | 0   | 1  | 1  | 0   | F    | Rz  |               |   |   | ADD | R[7:0 | )]   |     |     |

| <b>WDR</b> Rz Addr    | 0  | 0  | 0   | 1  | 1  | 1   | ł    | Rz  |               |   |   | ADD | R[7:0 | )]   |     |     |

| ADDI Rz Im            | 0  | 0  | 1   | 0  | 0  | 0   | ŀ    | Rz  |               |   |   | lm  | [7:0] |      |     |     |

| AUBI Rz Im            | 0  | 0  | 1   | 0  | 0  | 1   | F    | Rz  |               |   |   | lm  | [7:0] |      |     |     |

| ADDR Rx Ry            | 0  | 0  | 1   | 0  | 1  | 0   | F    | Rz  | -             | - | - | -   | R     | Х    | F   | ₹у  |

| SUBR Rx Ry            | 0  | 0  | 1   | 0  | 1  | 1   | F    | Rz  | -             | - | - | -   | R     | Х    | F   | ₹у  |

| CMPR Rx Ry            | 0  | 0  | 1   | 1  | 0  | 0   | 0    | 0   | -             | - | - | -   | R     | Х    | F   | ₹у  |

| END Int Rst           | 0  | 0  | 1   | 1  | 0  | 1   | 0    | 0   | -             | - | - | -   | ı     | ı    | Int | Rst |

| INTN_MASKOFF          | 0  | 0  | 1   | 1  | 0  | 1   | 1    | 0   | -             | - | - | -   | ı     | ı    | -   | -   |

| INTN_MASKON           | 0  | 0  | 1   | 1  | 0  | 1   | 1    | 1   | -             | - | - | -   | ı     | ı    | -   | -   |

| WAITI Pre Time        | 0  | 0  | 1   | 1  | 1  | Pre |      |     | T[9:0]        |   |   |     |       |      |     |     |

| SETPWMR Rx Ry         | 0  | 1  | 0   | 0  | 0  | 0   | 0    | -   | - 0 0 0 Rx Ry |   |   |     |       |      |     |     |

| RAMPR Dir Rx Ry       | 0  | 1  | 0   | 0  | 0  | 0   | 1    | Dir | -             | 0 | 0 | 0   | R     | Х    | F   | ₹у  |

| SETSTEPTMRR Pre Rx Ry | 0  | 1  | 0   | 0  | 0  | 1   | 0    | -   | Pre           | 0 | 0 | 0   | R     | X    | F   | ₹у  |

| SETSTEPTMRI Pre Ch Im | 1  | 0  | 0   |    |    | Ch[ | 4:0] |     | Pre           | - |   |     | lm[   | 5:0] |     | ·   |

| SETPWMI Ch Im         | 1  | 0  | 1   |    |    | Ch[ | 4:0] |     |               |   |   | lm  | [7:0] |      |     |     |

| RAMPI Dir Ch Im       | 1  | 1  | Dir |    |    | Ch[ | 4:0] |     |               |   |   | lm  | [7:0] |      |     |     |

#### a) Special LED Control Command

There are 3 kinds of LED control command.

- **SETPWM:** set the brightness level (0~255) for specified LED channel;

- **RAMP:** set the specified LED channel fade in or fade out for expected step( 0~255)

SETSTEP: set the fading slope for specified LED channel;

All control parameter in above commands can either come from specified register (RA~RD), or from immediate data contained in command..

All LED control command supports broadcast mode, one instruction may send to multiple or all LEDs

When SRAM program running, if Ch field or value of Rx in LED control command is "11111", the current command is active for all LED with setting of CTRSR.bitn=0. If Ch field or value of Rx in LED control command is "11110", the current command is only active for those channel with setting of GMSKx=0.

When LED instruction is come from I<sup>2</sup>C interface directly, it is recommended to use only the command with immediate data. If the Ch field in command is "11111", the current command is only active for those LED with STRSR.bitn=1..

Table 5 LED Control Instruction explanation

| Instruction           | Description                                                                                                                                                                                         |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register Parameter    |                                                                                                                                                                                                     |

| SETPWMR Rx Ry         | Set the PWM brightness level with parameter in register Rx: LED channel number, 0~8 for LED1~ LED9 respectively Ry: Brightness level, 0~255                                                         |

| RAMPR Dir Rx Ry       | Set the Fade-in/Fade-out for specified step with parameter in register Dir: 1: Fade-in; 0: Fade-out Rx: LED channel number, 0~8 for LED1~ LED9 respectively Ry: the step number of Fade-in/Fade-out |

| SETSTEPTMRR Pre Rx Ry | Set the RAMP slope with parameter in register Pre: basic time unit, 0: 0.5ms; 1: 16ms Rx: LED channel number, 0~8 for LED1~ LED9 respectively Ry: RAMP step time = (Ry+1)*Pre, 0~255                |

| Immediate Data        |                                                                                                                                                                                                     |

| SETPWMI Ch Im         | Set the PWM brightness level with immediate parameter Ch: LED channel number, 0~8 for LED1~ LED9 respectively Im: Brightness level, 0~255                                                           |

| RAMPI Dir Ch Im       | Set the Fade-in/Fade-out for specified steps with immediate parameter Dir: 1: Fade-in; 0: Fade-out Ch: LED channel number, 0~8 for LED1~ LED9 respectively Im: the steps of Fade-in/Fade-out        |

| SETSTEPTMRI Pre Ch Im | Set the RAMP step time with immediate parameter Pre: basic unit of time, 0: 0.5ms; 1: 16ms Ch: LED channel number, 0~8 for LED1~ LED9 respectively Im: RAMP step time = (Im +1)*Pre, 0~255          |

## **Table 6 Program Control and operation Instruction**

| Instruction        | Encoding    | Description                                                           |

|--------------------|-------------|-----------------------------------------------------------------------|

| branch Instruction | n           |                                                                       |

| JP Addr            | 0x00xx      | Immediate Jump, jump to PC = Addr                                     |

| JPZ Addr           | 0x04xx      | Conditional Jump, If Rz is 0, jump to PC = Addr                       |

| JPNZ Addr          | 0x05xx      | Conditional Jump, If Rz is not 0, jump to PC = Addr                   |

| JPS Addr           | 0x06xx      | Conditional Jump, If Rz < 0, jump to PC = Addr                        |

| JPNS Addr          | 0x07xx      | Conditional Jump, If Rz >= 0, jump to PC = Addr                       |

| Data Transfer Inst | ruction     |                                                                       |

| I D D I I I        | 0x08xx      | Do las                                                                |

| <b>LD</b> Rz Im    | 0x0bxx      | Rz = Im                                                               |

|                    | 0x18xx      |                                                                       |

| RDR Rz Addr        | -<br>0x1bxx | Rz = *Addr                                                            |

|                    | 0x1cxx      |                                                                       |

| WDR Rz Addr        | -<br>0x1fxx | *Addr = Rz                                                            |

| Computation Inst   | ruction     |                                                                       |

|                    | 0x0cxx      |                                                                       |

| CMPI Rz Im         | -<br>0x0fxx | Rz – Im, only change S/Z flag                                         |

| CMPR Rx Ry         | 0x30xx      | Rx – Ry, only change S/Z flag                                         |

|                    | 0x10xx      |                                                                       |

| ANDR Rz Im         | -<br>0x13xx | Rz = Rz & Im, affect S/Z flag                                         |

|                    | 0x14xx      |                                                                       |

| ORR Rz Im          | -<br>0x17xx | Rz = Rz   Im, affect S/Z flag                                         |

|                    | 0x20xx      |                                                                       |

| ADDI Rz Im         | 0x23xx      | Rz = Rz + Im, affect S/Z flag                                         |

|                    | 0x24xx      |                                                                       |

| SUBI Rz Im         | -<br>0x27xx | Rz = Rz - Im, affect S/Z flag                                         |

|                    | 0x28xx      |                                                                       |

| ADDR Rz Rx Ry      | -<br>0x2bxx | Rz = Rz + Ry, affect S/Z flag                                         |

|                    | 0x28xx      |                                                                       |

| SUBR Rz Rx Ry      | -           | Rz = Rz - Ry, affect S/Z flag                                         |

| Control Instructio | 0x2bxx      |                                                                       |

| END Int Rst        | n<br>0x34xx | Program end with optionally reset register RMD and generate interrupt |

| בוזום וווו עצו     | UX34XX      | Program end with optionally reset register RMD and generate interrupt |

|                |                       | Int= 0: no interrupt after instruction executed; Int= 1: generate interrupt after instruction executed Rst=0: PC add 1 after instruction executed; Rst=1: Reload PC with SADDR after instruction executed |

|----------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTN_MASKOFF   | 0x36xx                | Unmask internal interrupt                                                                                                                                                                                 |

| INTN_MASKON    | 0x37xx                | Mask internal interrupt                                                                                                                                                                                   |

| WAITI Pre Time | 0x38xx<br>-<br>0x3fxx | Wait for specified time Pre: time of basic waiting cycle, 0: 0.5ms; 1: 16ms Time: number of waiting cycle, max value is 1023, wait time=Pre*Time                                                          |

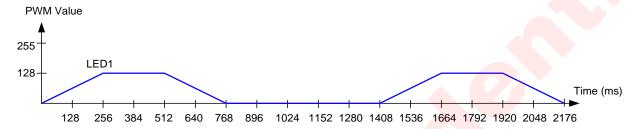

#### **Example**

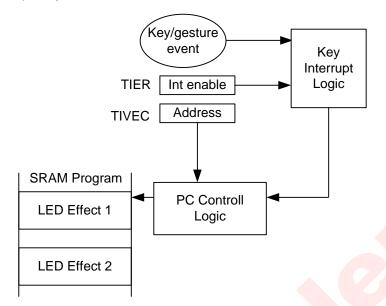

Figure 18 LED Effect Programming Diagram

Table 7 Reference Instruction of LED Effect Programming

| PC | Assemble Instruction       | Machine Code | explanation                     |

|----|----------------------------|--------------|---------------------------------|

| 0  | SETSTEPTMRI 0x00 0x1F 0x03 | 0x9F03       | RAMPI step time: 2ms            |

| 1  | SETPWMI 0x1F 0x00          | 0xBF00       | ALL LED turn off                |

|    | START:                     |              | Address Label "START" (01H)     |

| 2  | RAMPI 0x01 0x00 0x80       | 0xE080       | LED1 fade in, 128 steps breath  |

| 3  | WAITI 0x01 0x20            | 0x3C20       | Wait 512ms                      |

| 4  | RAMPI 0x00 0x00 0x80       | 0xC080       | LED1 fade out, 128 steps breath |

| 5  | WAITI 0x01 0x38            | 0x3C38       | Wait 896ms                      |

| 6  | JP START                   | 0x0002       | Jump to START, PC=2             |

#### Step1: Power On, configure register

- VBAT power on, 4.2V

- Pull pin PDN to 3V

- Wait 5ms

- Write register GCR = 0x0001 // enable LED module

- Writer register LER = 0x0001 // enable LED1

- Write register PMD=0x0000 // bits PROGRMD[1:0] = 00,hold mode

Write register RMD=0x0000 // bits RUNMD[1:0] = 00,hold mode

#### Step 2: Load Instruction to SRAM

- Write register WADDR= 0x0000 // load program starting at address =0x0000

- Write register WDATA = 0x9F03

- Write register WDATA = 0xBF00

- Write register WDATA = 0xE080

- Write register WDATA = 0x3C20

- Write register WDATA = 0xC080

- Write register WDATA = 0x3C38

Write register WDATA = 0x0002

#### Step3: Run

- Write register SADDR = 0x0000

- Write register RMD=0x0002 // bits RUNMD[1:0] = 10,change to run mode,

- Write register PMD=0x0001 // bit PROGMD[1:0] = 01 ,start program from 0x0000

## **Link Touch Status to LED Lighting Effect**

There are two optional ways to connect touch status to LED lighting effect inside the device: direct output mode and program mode .

In direct output mode, the touch detection status directly turn on or off the specified LED. In program mode, user can adapt internal touch and gesture interrupt to start LED lighting effect program to generate complex touch feedback.

#### Direct output mode

If bit OEx (x=1~6) in register OSRn (n=1~3) is 1, the touch status on pin Sx directly output to the LED defined by bits LSELx[3:0] in register OSRn. When touch detected, the LED turn on, when touch released, the LED turns off.

The control bit LSELx[3:0] of register OSRn defines which LED display the touch status of pin Sx:

```

LSELx[3:0]=0000, touch status sent to LED1

LSELx[3:0]=0001, touch status sent to LED2

...

LSELx[3:0]=1000, touch status sent to LED9

```

The control bit FONx, FOFx in register OSRn select the transition way between state on and off

FONx=1, turn on LED in smooth way (fade in) when Sx touch detected; FONx=0, turn on LED immediately (without fade-in) when Sx touch detect;

FOFx=1, turn off LED in smooth way (fade out) when Sx touch released FOFx=0, turn off LED immediately (without fade-out) when Sx touch released

When FOFx=1 or FONx=1, the speed of fade in/fade out is set by external MCU control command ( SETSTEP) through I<sup>2</sup>C interface.

#### Program link mode

Internal ASP can read several touch/gesture-related register to obtain the status of touch/gesture detection, such as register KST (Key Status), TISR1, TISR2 (Touch Interrupt status register). Once an event of touch or gesture is detected, program can jump to execute special subroutine to generate user-predefined lighting effect.

Besides invoking touch feedback lighting by polling the touch/gesture status, the touch feedback subroutine can be invoked by interrupt control mode. When touch and gesture are detected, the register bits KISx(x=1~6), GISy (y=1~2) and TAP in register TISR 1/TISR2 will be set; if corresponding interrupt enable bits KIEx, GIEy, and TIE in register TIER are set, internal interrupt mechanism is triggered. After interrupt occurs, ASP's PC pointer jumps to the beginning address defined by register TIVEC at once to execute interrupt subroutine.

Generally interrupt subroutine would read registers TISR1/TISR2 first to resolve the interrupt source, and then to execute the corresponding touch-related lighting program. After register TISR1/TISR2 read out, they will be cleared automatically.

The register TIER (Touch Interrupt Enable) contains 3 types of interrupt enable bits: KIE, GIE and TIE. The KIEx is the touch status interrupt, which has 4 types operating mode configured by bits INMD[1:0] in register

LCR. The GIEy are the slide gesture interrupt enable bits, and TIE is the tap gesture interrupt enable bit. All interrupts have the same priority.

Figure 19 Touch/Gesture Event triggers LED Program Interrupt

## **REGISTER DESCRIPTION**

## **REGISTER CONFIGURATION**

| DANOL   DRST   D15D14   D13D12D11   D10   D9   D8   D7   D6   D5   D4   D3   D2   D1   D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Address   | Register | 15  | 14   | 13   | 12   | 11    | 10   | 9   | 8        | 7    | 6    | 5    | 4     | 3      | 2    | 1     | 0       |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|-----|------|------|------|-------|------|-----|----------|------|------|------|-------|--------|------|-------|---------|--|

| Ox01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x00      |          | D15 | D14  | D13  | D12  | D11   | D10  | D9  | D8       | D7   | D6   | D5   | D4    | D3     | D2   | D1    | D0      |  |

| Ox00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |          |     |      |      |      |       |      |     |          |      |      |      |       |        |      |       |         |  |

| 0x03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |          |     |      | 0    |      |       | 0    |     |          |      | -    | SLP6 | SLP5  | SLP4   | SLP3 |       |         |  |

| Ox04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |          |     |      |      |      |       |      | K   |          |      |      |      |       |        |      |       |         |  |

| DN05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |          | OE2 | FON2 |      |      |       | LS   | EL2 | 2        |      |      |      |       |        |      |       | 777     |  |

| 0x06                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |          | OE4 | FON4 | FOF4 | 0    |       |      |     |          |      | FON3 |      |       |        |      |       |         |  |

| 0x07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           | OSR3     | OE6 | FON6 | FOF6 | 0    |       |      |     |          | OE5  | FON5 | FOF5 |       |        |      |       |         |  |