## High Efficiency Low Noise Large Volume Handsets Stereo TLTR-AGC 3<sup>rd</sup> Smart K Audio Amplifier

#### **FEATURES**

- Triple-Level Triple-Rate AGC algorithm:

- · Enhance bass, improve the dynamic range

- Increase volume, eliminate noise, timely and effectively protect the speaker

- Output Power: 3.1W@8Ω, 3.5W@6Ω

- Low Noise: 11μV

- ◆ Low THD+N: 0.02%

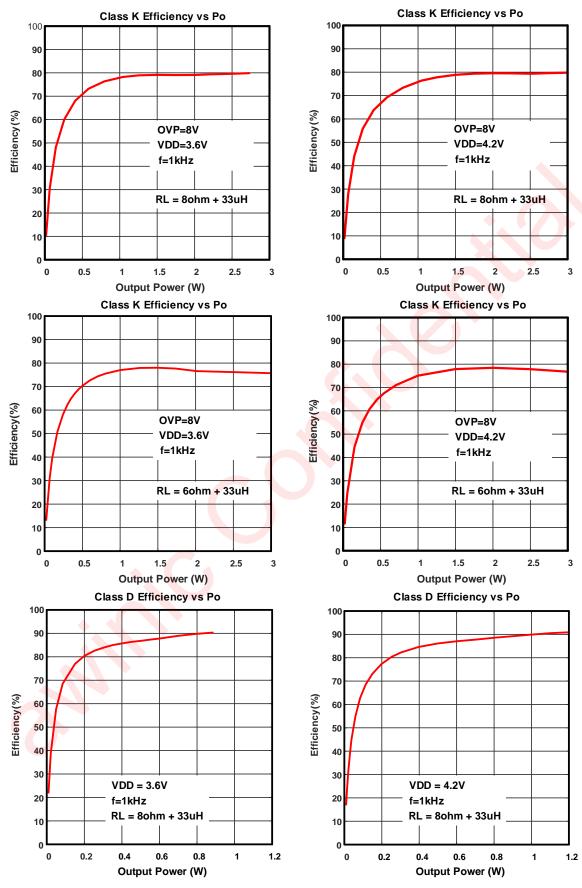

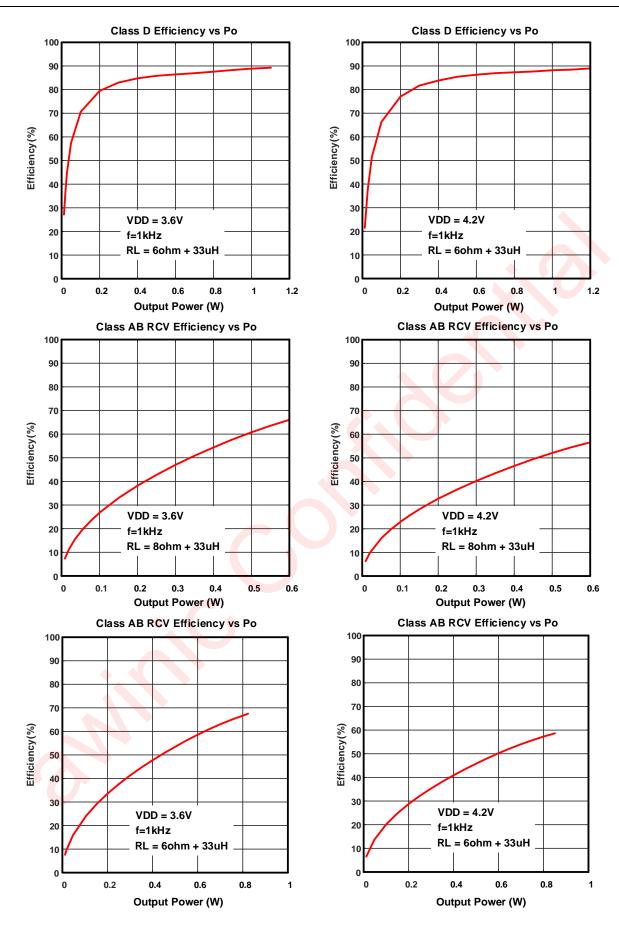

- Overall efficiency up to 80%

- Support high power receiver stereo application

- Support AB/D speaker , AB/D receiver 2-in-1 application

- AB receiver: 0dB, Vn=11 $\mu$ V, THD+N=0.2%

- D receiver: 4.5dB, Vn=16µV, THD+N=0.02%

- Support 1.8V I2C Control

- Over current protection, over-temperature protection and short-circuit protection

- Super TDD-Noise suppression

- Excellent pop-click suppression

- High PSRR: -90dB (217Hz)

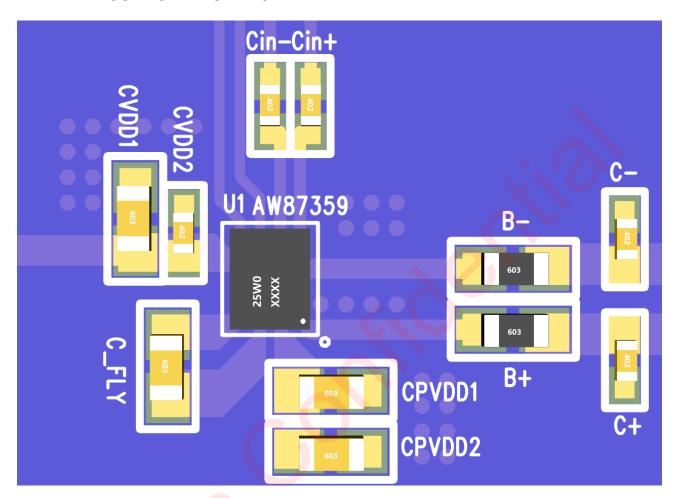

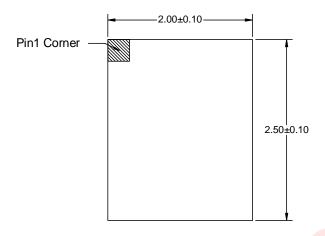

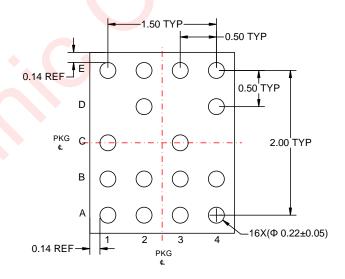

- FCQFN 2.5mmX2.0mmX0.55mm-16L package

## **APPLICATIONS**

Smart phone、Tablet PC、Tactile feedback

## **DESCRIPTION**

AW87359 is specifically designed to improve the musical output dynamic range, enhance the overall sound quality, which is a new high efficiency, low noise, constant large volume, 3rd Smart K audio amplifier. AW87359 integrates awinic's proprietary Triple-Level Triple-Rate AGC audio algorithm, effectively eliminating music noise and improving sound quality and volume. AW87359 integrated efficiency up to 90% of high voltage DO-Chargepump technology, significantly improving the dynamic range of the music output. AW87359 noise floor is as low as to 38µV at speaker mode, with 102dB high signal-to-noise-ratio (SNR). The ultra-low distortion 0.02% and unique Triple-Level Triple-Rate AGC technology bring high quality music enjoyment.

AW87359 support speaker and high power receiver stereo applications; supports speaker and receiver 2-in-1 applications, class AB/D receiver optional, ultra-low noise is 11µV.

AW87359 controls internal registers through the I<sup>2</sup>C interface. Register parameters include output voltage, power amplifier gain, Triple-Level Triple-Rate AGC parameters etc.

AW87359 built-in over current protection, over temperature protection and short circuit protection function, effectively protect the chip. AW87359 features small FCQFN 2.5mmX2.0mmX0.55mm-16L package.

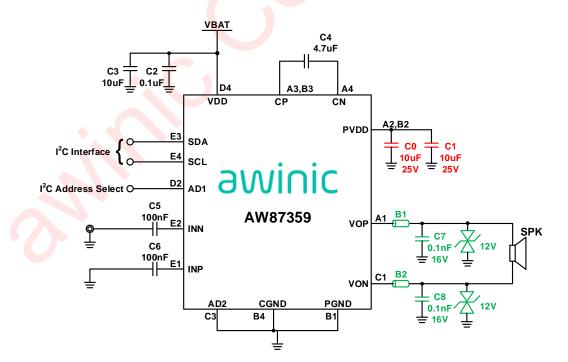

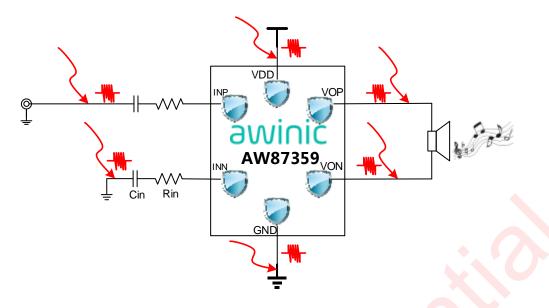

## TYPICAL APPLICATION CIRCUIT

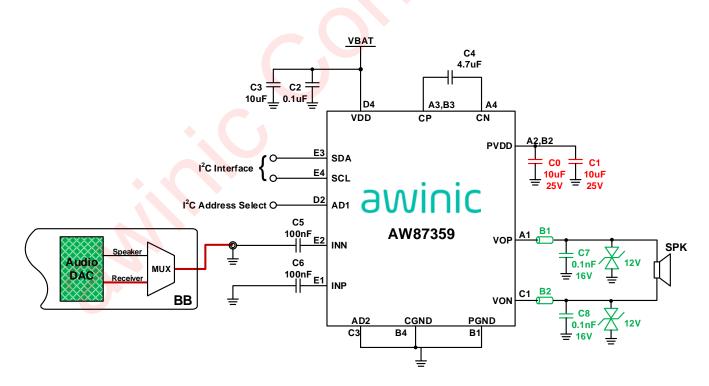

Figure 1 AW87359 Single-ended input mode Application Diagram

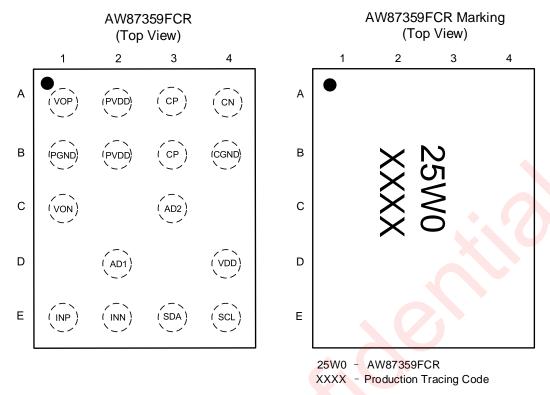

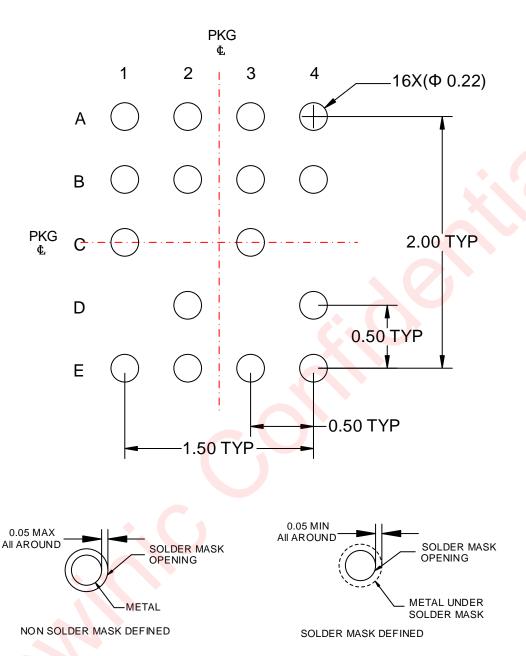

## PIN CONFIGURATION ANG TOP MARK

Figure 2 AW87359 Pin configuration and Top Mark

## **PIN DESCRIPTION**

| Number | Symbol | Description                                                  |  |  |  |  |  |

|--------|--------|--------------------------------------------------------------|--|--|--|--|--|

| A1     | VOP    | Posit <mark>iv</mark> e audio <mark>output</mark> terminal   |  |  |  |  |  |

| A2,B2  | PVDD   | Charge Pump output voltage                                   |  |  |  |  |  |

| A3,B3  | СР     | Positive input Charge Pump Flying Capacitance                |  |  |  |  |  |

| A4     | CN     | Nega <mark>ti</mark> ve input Charge Pump Flying Capacitance |  |  |  |  |  |

| B1     | PGND   | mplifier power ground                                        |  |  |  |  |  |

| B4     | CGND   | Charge Pump power ground                                     |  |  |  |  |  |

| C1     | VON    | Negative audio output terminal                               |  |  |  |  |  |

| C3     | AD2    | I <sup>2</sup> C address pin2                                |  |  |  |  |  |

| D2     | AD1    | I <sup>2</sup> C address pin1                                |  |  |  |  |  |

| D4     | VDD    | Power supply                                                 |  |  |  |  |  |

| E1     | INP    | Positive audio input terminal                                |  |  |  |  |  |

| E2     | INN    | Negative audio input terminal                                |  |  |  |  |  |

| E3     | SDA    | I <sup>2</sup> C-bus data input/output                       |  |  |  |  |  |

| E4     | SCL    | I <sup>2</sup> C-bus clock input                             |  |  |  |  |  |

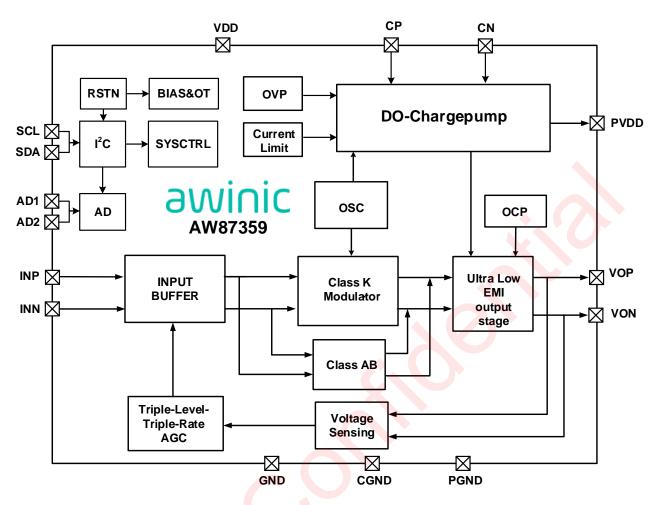

## **FUNCTIONAL DIAGRAM**

Figure 3 AW87359 Functional Diagram

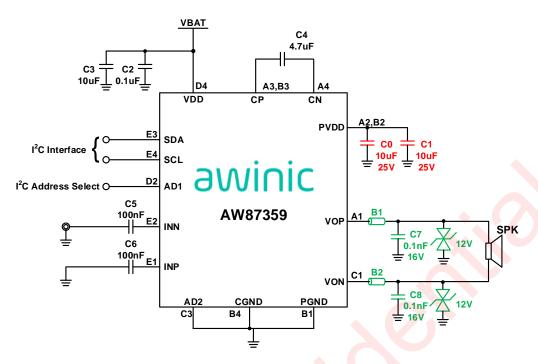

## **TYPICAL APPLICATION CIRCUIT**

Figure 4 AW87359 Single-ended input mode Application Diagram(Note 1)

**Note1:** When single-ended input, audio signal line from audio DAC (HPL or HPR) can arbitrarily connected to either of INN or INP input terminal. The other terminal must be connected to reference ground (HPREF) through input capacitor and resistor.

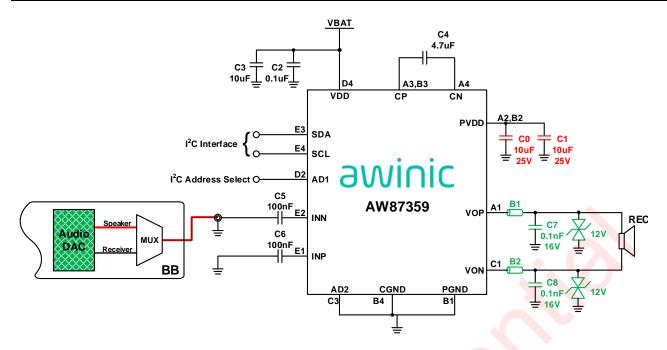

Figure 5 AW87359 Speaker & Receiver 2-in-1 Mode Application Diagram

Figure 6 AW87359 High Power Receiver Stereo Mode Application

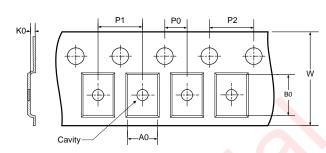

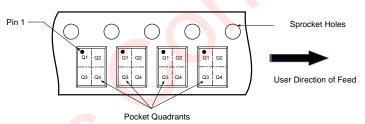

## **ORDERING INFORMATION**

| Part Number | Temperature | Package                | Marking | Moisture<br>Sensitivity<br>Level | Environmental<br>Information | Delivery<br>Form             |

|-------------|-------------|------------------------|---------|----------------------------------|------------------------------|------------------------------|

| AW87359FCR  | -40°C ~85°C | FCQFN<br>2.5mmX2mm-16L | 25W0    | MSL1                             | ROHS+HF                      | 6000 units/<br>Tape and Reel |

## ABSOLUTE MAXIMUM RATING (Note2)

| Parameter                                                     | Range              |  |  |

|---------------------------------------------------------------|--------------------|--|--|

| Supply Voltage V <sub>DD</sub>                                | -0.3V to 6V        |  |  |

| INN,INP                                                       | -0.3V to VDD+0.3V  |  |  |

| Charge pump output voltage PVDD                               | -0.3V to 9.5V      |  |  |

| VOP,VON                                                       | -0.6V to PVDD+0.6V |  |  |

| СР                                                            | -0.3V to PVDD+0.3V |  |  |

| CN                                                            | -0.3V to VDD+0.3V  |  |  |

| Minimum load resistance R∟                                    | 5Ω                 |  |  |

| Package Thermal Resistance θ <sub>JA</sub>                    | 65.2°C/W           |  |  |

| Ambient Temperature Range                                     | -40°C to 85°C      |  |  |

| Maximum Junction T <mark>e</mark> mperature Т <sub>ЈМАХ</sub> | 165°C              |  |  |

| Storage Temperature Range T <sub>STG</sub>                    | -65°C to 150°C     |  |  |

| Lead Temperature (Soldering 10 Seconds)                       | 260°C              |  |  |

| ♦ ESD Rating (Note 3)                                         |                    |  |  |

| HBM (human body model)                                        | ±2kV               |  |  |

| MM (machine model)                                            | ±400V              |  |  |

| CDM (charged-device model)                                    | ±1.5kV             |  |  |

| Latch-up                                                      |                    |  |  |

| Total Condition   IEDEC CTANDARD NO 705                       | +IT: 450mA         |  |  |

| Test Condition: JEDEC STANDARD NO.78E                         | -IT: -450mA        |  |  |

**NOTE2:** Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

**NOTE3:** The human body model is a 100pF capacitor discharged through a  $1.5k\Omega$  resistor into each pin. Test method: ESDA/JEDEC JS-001-2017

Test method of the charge device model: ESDA/JEDEC JS-002-2014

## **ELECTRICAL CHARACTERISTICS**

$Test\ condition:\ T_A=25^{\circ}C,\ VDD=3.6V,\ PVDD\ OVP=8V,\quad R_L=8\Omega+33\mu H,\ f=1kHz\ (unless\ otherwise\ noted)$

|                  | Parameter                                      | Test                                                                         | cond | ditions | Min  | Тур                      | Max      | Units |

|------------------|------------------------------------------------|------------------------------------------------------------------------------|------|---------|------|--------------------------|----------|-------|

| V <sub>DD</sub>  | Power supply voltage                           |                                                                              |      |         | 2.8  |                          | 5.5      | V     |

|                  | Under-voltage protection voltage               |                                                                              |      |         |      | 2.5                      |          | V     |

| UVLO             | Under-voltage protection hysteresis voltage    |                                                                              |      |         |      | 100                      |          | mV    |

| V <sub>IH</sub>  | SCL, SDA, AD1, AD2 high-level input voltage    |                                                                              |      |         | 1.3  |                          | $V_{DD}$ | V     |

| V <sub>IL</sub>  | SCL, SDA, AD1, AD2 low-level input voltage     |                                                                              |      |         | 0    | <b>*</b>                 | 0.45     | ٧     |

| I <sub>SB</sub>  | Standby current                                | V <sub>DD</sub> =3.6V                                                        |      |         |      | 5                        |          | μA    |

| T <sub>SD</sub>  | Over temperature protection threshold          |                                                                              |      |         |      | 160                      |          | °C    |

| T <sub>SDR</sub> | Over temperature protection recovery threshold |                                                                              |      |         |      | 130                      |          | °C    |

| T <sub>ON</sub>  | Turn-On time                                   |                                                                              |      |         |      | 45                       |          | ms    |

| DO-Char          | gepump                                         |                                                                              |      |         |      |                          |          |       |

| PVDD             | The maximum Output voltage                     | V <sub>DD</sub> =2.8V to 4V, P                                               | VDD  | OVP=8V  |      | 2*VDD                    |          | V     |

| PVDD             | The maximum Odiput voltage                     | V <sub>DD</sub> >4V                                                          |      | X       |      | 8 (Note4)                |          | V     |

| OV/D             | OVP voltage                                    | V <sub>DD</sub> >4V                                                          |      |         |      | 8 (Note4)                |          | V     |

| OVP              | OVP hysteresis voltage                         | V <sub>DD</sub> >4V                                                          |      |         |      | 50                       |          | mV    |

| F <sub>CP</sub>  | Chargepump operating frequency                 | V <sub>DD</sub> =2.8V to 5.5V                                                |      |         | 1.08 | 1.45                     | 1.8      | MHz   |

| η <sub>CP</sub>  | Chargepump efficiency                          | V <sub>DD</sub> =4.2V, I <sub>load</sub> =200mA                              |      |         |      | 90                       |          | %     |

| T <sub>ST</sub>  | Softstart Time                                 | No load, COUT=4.7μF                                                          |      |         |      | 0.5                      |          | ms    |

| Class K I        | MODE                                           |                                                                              |      |         |      | Į.                       |          | I     |

| Vos              | Output offset voltage                          | No input                                                                     |      |         | -30  | 0                        | 30       | mV    |

| Iq               | Speaker Quiescent current                      | $V_{DD}$ =3.6V, input ac grounded, $R_L$ =8Ω+33μH                            |      |         | 14.2 |                          | mA       |       |

| η                | total efficiency (CP+Class D)                  | $V_{DD}$ =4.2V, Po=2.5W, R <sub>L</sub> =8 $\Omega$ +33 $\mu$ H, PVDD OVP=8V |      |         | 80   |                          | %        |       |

| Vinp             | Recommended input signal amplitude             | V <sub>DD</sub> =2.8V to 5.5V                                                |      |         |      |                          | 1        | Vp    |

| Fosc             | Modulation frequency                           | V <sub>DD</sub> =2.8V to 5.5V                                                |      |         | 540  | 720                      | 900      | kHz   |

| Page             | TLTR AGC power                                 | R <sub>L</sub> =8Ω+33μH                                                      |      |         | 0.72 | 0.8 (Note4)              | 0.88     | W     |

| Pagc             | TETR AGC power                                 | R <sub>L</sub> =6Ω+33μH                                                      |      |         | 0.96 | 1.067 <sup>(Note4)</sup> | 1.17     | W     |

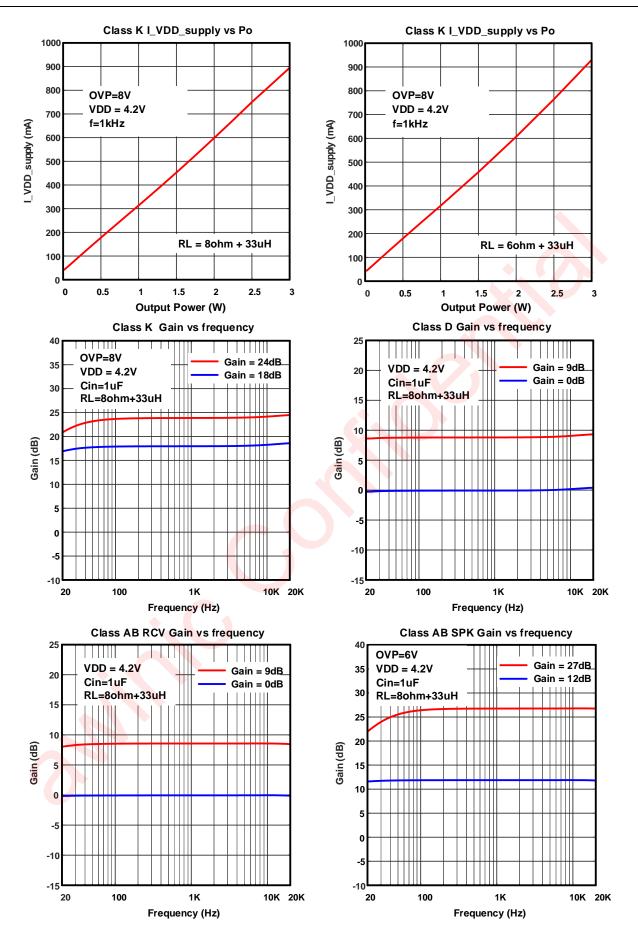

| PSRR             | Power supply rejection ratio                   | V <sub>DD</sub> =4.2V,                                                       |      | 217Hz   |      | -82                      |          | dB    |

| TORK             | Tower supply rejection ratio                   | Vpp_sin=200mV                                                                |      | 1kHz    |      | -75                      |          | dB    |

| SNR              | Signal-to-noise ratio                          | V <sub>DD</sub> =4.2V, PVDD<br>Av=18dB , THD+N                               |      |         | 102  |                          | dB       |       |

| SNR              | Signal-to-noise ratio                          | V <sub>DD</sub> =4.2V, PVDD OVP=8<br>Av=18dB, R <sub>L</sub> =8Ω+33μH        |      |         |      | 94                       |          | dB    |

| _                |                                                | Av=16 V/V                                                                    |      |         |      | 48                       |          |       |

| E <sub>N</sub>   | Speaker Output noise                           | Av=8 V/V grounded, A-weighting                                               |      |         |      | 38                       |          | μV    |

| Av               | Speaker gain                                   | V <sub>DD</sub> =2.8V to 5.5V                                                |      |         |      | 24 (Note4)               |          | dB    |

www.awinic.com.cn

|                | Parameter                              | Test co                                                          | Min                         | Тур        | Max      | Units |     |

|----------------|----------------------------------------|------------------------------------------------------------------|-----------------------------|------------|----------|-------|-----|

| D:::           | Speaker Inner input resistance         | Av=16 V/V                                                        |                             |            | 9        |       | 1.0 |

| Rini           | Speaker Inner input resistance         | Av=8 V/V                                                         |                             |            | 18       |       | kΩ  |

|                | Speaker input Cut-off frequency        | Cin=68nF, Av=16 V                                                | /V                          |            | 260      |       |     |

| Fin            | Speaker input Cut-off frequency        | Cin=68nF, Av=8 V/V                                               | V                           |            | 130      |       | Hz  |

|                | Speaker input Cut-off frequency        | Cin=100nF, Av=16                                                 | V/V                         |            | 177      |       | 112 |

|                | Speaker input Cut-off frequency        | Cin=100nF, Av=8 V                                                |                             | 89         |          |       |     |

| THD+N          | Total harmonic distortion + noise      | V <sub>DD</sub> =4.2V, Po=0.6W<br>R <sub>L</sub> =8Ω+33μH, f=1kl |                             |            | 0.03     |       | %   |

|                |                                        | THD+N=1%, RL=8Ω<br>PVDD OVP=8V                                   | 2+33μH, Vdd=4.2V,           |            | 3.1      |       | W   |

| Po             | Speaker Output Power                   | THD+N=10%, RL=8<br>PVDD OVP=8V                                   | Ω+33μH, Vdd=4.2V,           |            | 3.7      |       | W   |

| 10             | Speaker Output I Ower                  | THD+N=1%, RL=6Ω<br>PVDD OVP=8V                                   | 2+33μH, Vdd=4.2V,           |            | 3.5      |       | W   |

|                |                                        | THD+N=10%, R <sub>L</sub> =6<br>PVDD OVP=8V                      |                             | 4.2        |          | W     |     |

| AB Speal       | ker MODE (PVDD OVP=6V)                 |                                                                  |                             |            |          |       |     |

| Iq             | Speaker Quiescent current              | $V_{DD}$ =3.6V, input ac $R_L$ =8 $\Omega$ +33 $\mu$ H           | grounded,                   |            | 12.3     |       | mA  |

| η              | total efficiency (CP+Class D)          | V <sub>DD</sub> =4.2V, Po=1.2W                                   |                             | 40         |          | %     |     |

|                | E <sub>N</sub> Speaker Output noise    | Av=16 V/V                                                        |                             | 46         |          | 11)/  |     |

| E <sub>N</sub> | Speaker Output noise                   | Av=8 V/V                                                         | ac grounded,<br>A-weighting |            | 36       |       | μV  |

| Av             | Speaker gain                           | V <sub>DD</sub> =2.8V to 5.5V                                    |                             | 24 (Note4) |          | dB    |     |

| D'ar'          | Speaker Inner input resistance         | Av=16 V/V                                                        |                             |            | 9        |       | kΩ  |

| Rini           | Speaker Inner input resistance         | Av=8 V/V                                                         |                             |            | 18       |       | kΩ  |

|                | Speaker input Cut-off frequency        | Cin=68nF, Av=16 V                                                | N                           |            | 260      |       |     |

| Fin            | Speaker input Cut-off frequency        | Cin=68nF, Av=8 V/                                                | V                           |            | 130      |       |     |

| FIN            | Speaker input Cut-off frequency        | Cin=100nF, Av=16                                                 | V/V                         |            | 177      |       | Hz  |

|                | Speaker input Cut-off frequency        | Cin=100nF, Av=8 V                                                | N                           |            | 89       |       |     |

| D0DD           | AB Speaker Power supply rejection      | V <sub>DD</sub> =4.2V,                                           | 217Hz                       |            | -80      |       | dB  |

| PSRR           | ratio                                  | Vp-p_sin=200mV 1kHz                                              |                             |            | -82      |       | dB  |

| THD+N          | Total harmonic distortion + noise      | V <sub>DD</sub> =4.2V, Po=1.2W<br>R <sub>L</sub> =8Ω+33μH, f=1kH |                             | 0.1        |          | %     |     |

| D-             | AD Constant Outsid Downs               | THD+N=1%, R <sub>L</sub> =8Ω                                     |                             | 2.1        |          | W     |     |

| Po             | AB Speaker Output Power                | THD+N=10%, RL=8                                                  |                             | 2.6        |          | W     |     |

| 2-in-1 Re      | ceiver MODE(1X Chargepump)             | 1                                                                |                             | 1          | <u>t</u> |       |     |

| Iq             | D Receiver quiescent current (overall) | $V_{DD}$ =3.6V, input ac $R_L$ =8 $\Omega$ +33 $\mu$ H           | grounded,                   |            | 5.0      |       | mA  |

|                  | Parameter                               | Test                                                                          | conditions                      | Min  | Тур          | Max | Units |

|------------------|-----------------------------------------|-------------------------------------------------------------------------------|---------------------------------|------|--------------|-----|-------|

|                  | AB Receiver quiescent current (overall) | $V_{DD}$ =3.6V, input a R <sub>L</sub> =8 $\Omega$ +33 $\mu$ H                |                                 | 6.3  |              | mA  |       |

|                  | D Receiver efficiency                   | V <sub>DD</sub> =4.2V, Po=0.                                                  |                                 | 88   |              | %   |       |

| η                | AB Receiver efficiency                  | V <sub>DD</sub> =4.2V, Po=0.                                                  | 4W , R <sub>L</sub> =8Ω+33μH    |      | 47           |     | %     |

|                  | D Receiver gain                         | V <sub>DD</sub> =2.8V to 5.5\                                                 | I                               |      | 4.5 (Note4)  |     | dB    |

| Av               | AB Receiver gain                        | V <sub>DD</sub> =2.8V to 5.5\                                                 | /                               |      | (Note4)      |     | dB    |

| Rini             | D Receiver Inner input resistance       | Av=4.5dB                                                                      |                                 |      | 48           |     | kΩ    |

| KIIII            | AB Receiver Inner input resistance      | Av=0dB                                                                        |                                 |      | 72           |     | kΩ    |

|                  |                                         | Cin=68nF, Av=4                                                                | .5dB                            |      | 49           |     |       |

|                  | D Receiver input cut-off frequency      | Cin=100nF, Av=                                                                | 4.5dB                           |      | 33           |     | Hz    |

| Fin              | AB Receiver input cut-off               | Cin=68nF, Av=0                                                                | dB                              |      | 33           |     |       |

|                  | frequency                               | Cin=100nF, Av=                                                                |                                 | 22   |              | Hz  |       |

| _                | D Receiver output noise                 | Av=4.5dB                                                                      | 20Hz to 20kHz, input ac         |      | 16           |     | μV    |

| E <sub>N</sub>   | AB Receiver output noise                |                                                                               | grounded, A-weighting           |      | 11           |     | μV    |

| THD+N            | Total harmonic distortion + noise       | V <sub>DD</sub> =4.2V, Po=0.1W,R <sub>L</sub> =8Ω+33μH,<br>f=1kHz, D Receiver |                                 |      | 0.01         |     | %     |

| THETH            | Total Harmonio distortion 1 Holse       | V <sub>DD</sub> =4.2V, Po=0.<br>f=1kHz, AB Rece                               |                                 | 0.15 |              | %   |       |

|                  | D Receiver Power supply rejection       | V <sub>DD</sub> =4.2V,                                                        | 217Hz                           |      | -78          |     | dB    |

| DODD             | ratio                                   | Vp-p_sin=200mV 1kHz                                                           |                                 |      | -76          |     | dB    |

| PSRR             | AB Receiver Power supply                | V <sub>DD</sub> =4.2V,                                                        | 217Hz                           |      | -93          |     | dB    |

|                  | rejection ratio                         | Vp-p_sin=200m\                                                                | / 1kHz                          |      | -88          |     | dB    |

|                  | D Possiver Output Power                 | THD+N=1%, RL=                                                                 | =8Ω+33μH, V <sub>DD</sub> =4.2V |      | 0.98         |     | W     |

| Po               | D Receiver Output Power                 | THD+N=10%, R                                                                  | L=8Ω+33μH, VDD=4.2V             |      | 1.21         |     | W     |

|                  |                                         | THD+N=1%, RL=                                                                 | =8Ω+33μH, Vdd=4.2V              |      | 0.46         |     | W     |

|                  | AB Receiver Output Power                | THD+N=10%, R                                                                  | L=8Ω+33μH, VDD=4.2V             |      | 0.63         |     | W     |

| Triple-Le        | vel Triple-Rate AGC                     |                                                                               |                                 | ı    | 1            | ı   |       |

| T <sub>AT1</sub> | AGC1 Attack Time                        |                                                                               |                                 |      | 0.08 (Note4) |     | ms/dB |

| T <sub>AT2</sub> | AGC2 Attack Time                        |                                                                               |                                 |      | 0.64 (Note4) |     | ms/dB |

| T <sub>AT3</sub> | AGC3 Attack Time                        |                                                                               |                                 |      | 41 (Note4)   |     | ms/dB |

| T <sub>RLT</sub> | Release time                            |                                                                               |                                 |      | 21 (Note4)   |     | ms/dB |

| A <sub>MAX</sub> | The maximum attenuation gain            | V <sub>DD</sub> =2.8V to 5.5\                                                 | /                               |      | -13.5        |     | dB    |

**Note 4**: Registers are adjustable; Refer to the list of registers.

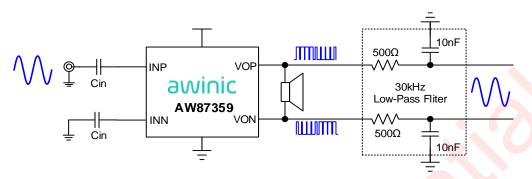

## **MEASUREMENT SETUP**

AW87359 features switching digital output, as shown in Figure 7. Need to connect a low pass filter to VOP/VON output respectively to filter out switch modulation frequency, then measure the differential output of filter to obtain analog output signal.

Figure 7 AW87359 Test Setup

Low pass filter uses resistance and capacitor values listed in Table 1.

| R <sub>filter</sub> | Cfilter | Low-pass cutoff frequency |

|---------------------|---------|---------------------------|

| 500Ω                | 10nF    | 32kHz                     |

| 1kΩ                 | 4.7nF   | 34kHz                     |

Table 1 AW87359 Recommended Values for Low Pass Filter

## **Output Power Calculation**

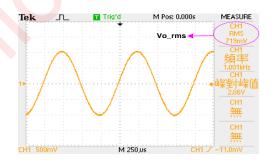

According to the above test methods, the differential analog output signal is obtained at the output of the low pass filter. The valid values Vo\_rms of the differential signal, as shown in Figure 8:

Figure 8 Output RMS Value

The power calculation of Speaker is as follows:

$$P_L = \frac{(V_{O_ms})^2}{R_L}$$

R<sub>L</sub>: load impedance of the speaker

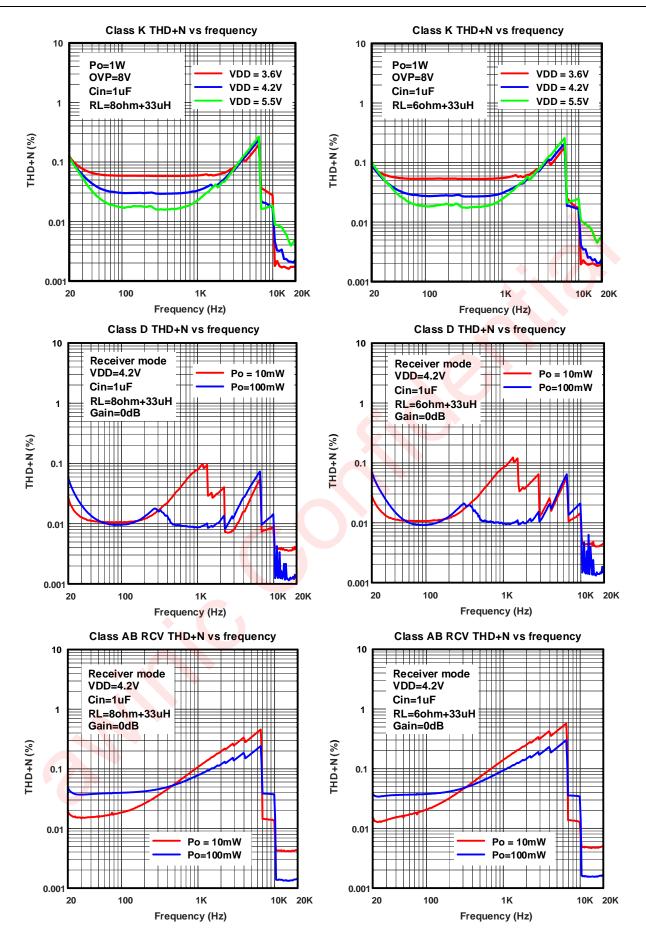

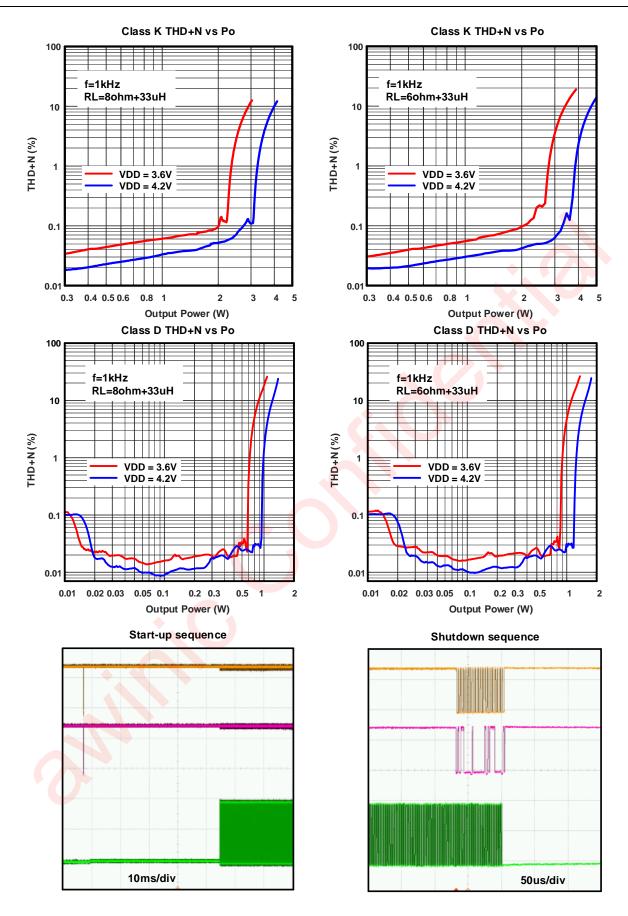

## TYPICAL CHARATERISTICS

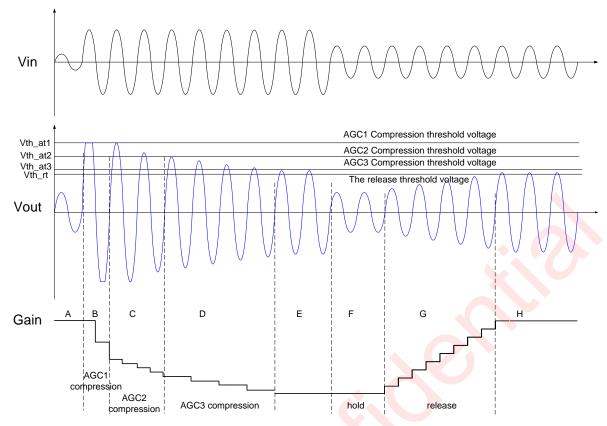

Triple-Level Triple Rate AGC Release Timing

## **WORKING PRINCIPLE**

AW87359 is specifically designed to improve the musical output dynamic range, enhance the overall sound quality, which is a new high efficiency, low noise, constant large volume, 3rd Smart K audio amplifier. AW87359 integrates awinic's proprietary Triple-Level Triple-Rate AGC audio algorithm, effectively eliminating music noise and improving sound quality and volume. AW87359 integrated efficiency up to 90% of High voltage DO-Chargepump boost technology, significantly improving the dynamic range of the music output. AW87359 noise floor is as low as to 38µV at speaker mode, with 102dB high signal-to-noise-ratio (SNR). The ultra-low distortion 0.02% and unique Triple-Level Triple-Rate AGC technology bring high quality music enjoyment.

AW87359 support Speaker and High power Receiver stereo applications; supports speaker and receiver 2-in-1 applications; class AB/D Receiver optional, ultra-low noise is 11uV.

AW87359 controls internal registers through the I2C interface. Register parameters include chargepump output Voltage, power amplifier gain, Triple-Level Triple-Rate AGC parameters etc.

AW87359 built-in over current protection, over temperature protection and short circuit protection function, effectively protect the chip. AW87359 features small FCQFN 2.5mmX2.0mmX0.55mm-16L package.

#### **CONSTANT OUTPUT POWER**

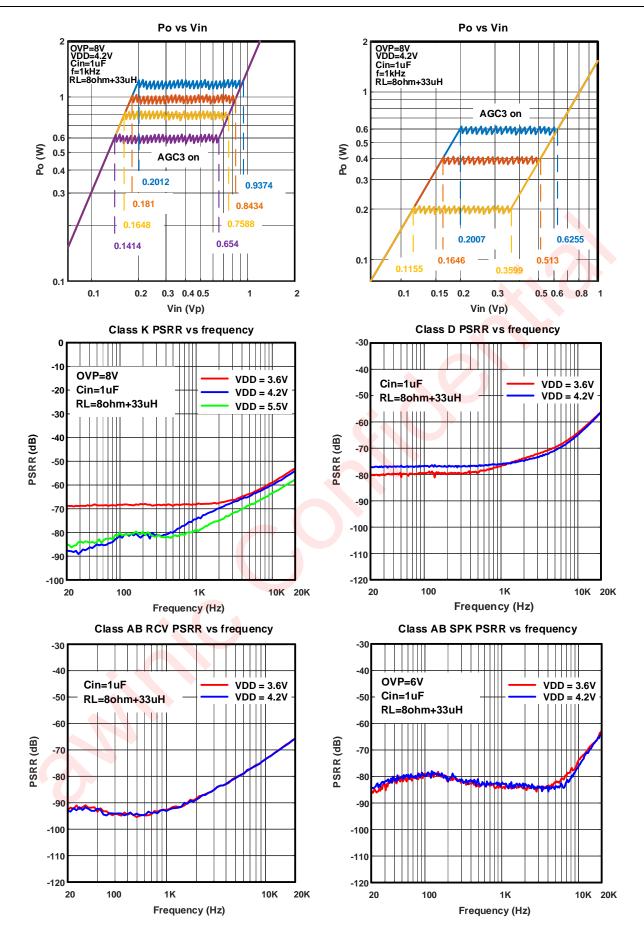

In the mobile phone audio applications, the AGC function to promote music volume and quality is very attractive, but as the lithium battery voltage drops, general power amplifier output power will reduce gradually. So, it is hard to provide high quality music within the battery voltage range. AW87359 uses unique Triple-Level Triple-Rate technology, within lithium battery voltage range (3.3V~4.35V), to guarantee that output power is constant, and the output power will not drop along with the decrease of lithium battery voltage. In the process of using the phone, even if the battery voltage drops, AW87359 can still provide high quality large volume music enjoyment. The output power of AW87359 can be configured from 0.1W to 2W via I<sup>2</sup>C, matching general speakers. Unique Triple-Level Triple-Rate AGC technology can bring high-quality music enjoyment.

## Triple-Level Triple-Rate AGC technology

AWINIC proprietary Triple-Level Triple-Rate AGC technology is designed for the protection of the high voltage power amplifier, which is divided into AGC1, AGC2 and AGC3 power levels, to obtain a large volume while maintaining excellent sound quality.

In practical applications, speaker can continuously work long hours at rated power, and also can work short-term at high power. For example, in the standard reliability of the loudspeaker experiment, the powder of peak power reached around four times of the rated power. For achieving larger volume and better sound quality, speakers need to work at high power for short periods of time, in order to improve the performance of the speaker. AW87359 Triple-Level Triple-Rate AGC technology can fit the speaker better and perform better overall performance. AGC1 prevents output signal clipping by detecting output voltage in a very short time after clipping, which can effectively restrain the noise clipping; AGC2 can improve the dynamic range of the music in a relatively short period of time; AGC3 can make the speaker work under rated power, which can effectively improve the volume and protect the speaker. Triple-Level Triple-Rate AGC can obtain more excellent overall performance.

Triple-Level Triple-Rate AGC detects the peak output voltage of the power amplifier, when the output peak voltage is higher than the compression threshold voltage, the amplifier gain decreases in 0.5dB step. When the output peak voltage is lower than the release threshold voltage, the amplifier gain is recovery to the initial gain in 0.5dB step. The detailed process can be described as follows:

Figure 9 Triple-Level Triple-Rate AGC Operation Principle

A: Small input signal, the output voltage is lower than threshold voltage Vth of AGC, AGC don't work.

B: Input voltage becomes large. It leads to the output voltage clipping, AGC1 starts fast compression, the attack time is set through the I<sup>2</sup>C register 0x0Ah [2:1], when the output voltage is higher than Vth\_at1, and gain register began to decrease. Gain decreases when the output signal passes through the zero. It eliminates the clipping noise as soon as possible.

C: When the output voltage is not clipping and higher than threshold voltage Vth\_at2, AGC2 starts work, the attack time is set through the I²C register 0x09h [4:2], gain register begins to decrease at a certain rate. Gain register began to decrease. Gain decreases when the output signal passes through the zero. The output voltage gradually decreases to below the AGC2 attack threshold voltage Vth\_at2, which can protect the speaker and enhance the sound.

D: When the output voltage is lower than the AGC2 attack threshold voltage Vth\_at2 and higher than the AGC3 attack threshold voltage Vth\_at3, AGC3 starts work, the attack time is set through the I²C register 0x07h [4:2], and gain register began to decrease at a certain rate. Gain decreases when the output signal passes through the zero, so the output voltage gradually decreases to below of the AGC3 attack threshold voltage Vth\_at3, matching the speaker to achieve greater volume and better sound quality.

E: Triple-Level Triple-Rate AGC attack time ends, Amplifier output power is close to the speaker rated power.

F: Input voltage decreases, the output voltage becomes lower than the release threshold voltage Vth\_rt, at this point, gain remains the same in the maintain time (10ms~20ms).

G: Gain increases when the time of output voltage lower than the release threshold voltage Vth\_rt is longer than the holding time. The release time can be set through I<sup>2</sup>C register 0x07h [7:5].

H: Stop release when the output signal is larger than the release threshold or the gain is equal to the initial value. The output voltage remains constant.

Triple-Level Triple-Rate AGC can switch independently according to different application requirements. Such as close AGC1 and AGC2, retain only AGC3, this is the single-AGC mode, similar to AW8736 (AGC3 attack time is set to 1.28ms/dB; release time is set to 41ms/dB); Close AGC2, open AGC1 and AGC3, this is

Multi\_level AGC. It can be set similar to AW8738 (AGC1 attack time is set to 80us/dB; AGC3 attack time is set to 0.64ms/dB; release time is set to 10.24ms/dB).

## **Zero-Crossing Adjustment Technology**

Traditional AGC doesn't contain zero adjustment technology; AGC gain changes generally at the peak, the gain variation at the peak would generate a certain transient distortion, such distortions are audibly imperceptible. Such as individual songs have a slight click.

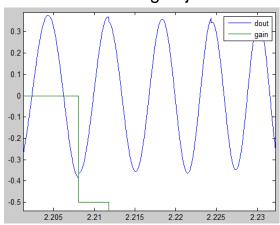

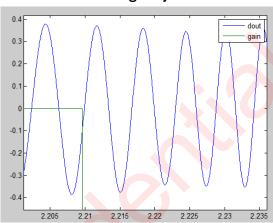

## no zero-crossing adjustment

## zero-crossing adjustment

Figure 10 Zero-adjust Comparison

As shown above, when there is no zero-adjustment technology, it can be seen the obvious step change at the peak of large signal, the steps sound slightly perceived in special audio. Gain changes at zero. The steps disappear by using zero-crossing detection technology. Using zero detection technology can make the music pure and natural.

## **DO-Chargepump**

AW87359 features DO-chargepump technology, with high efficiency and high drive capability, operating frequency 1.6MHz, built-in soft start circuit, current limiting control loop and over-voltage control loop to ensure circuit stable and reliable work.

#### **High efficiency**

AW87359 features DO-chargepump architecture, the output voltage PVDD is twice of the input voltage VDD, ideal efficiency up to 100%. The efficiency of the DO-chargepump is the ratio of the output power to input power:

$$\eta = \frac{P_{OUT}}{P_{DU}} * 100\%$$

For example, in an ideal M times the DO-chargepump, the input current  $I_{I\!N}$  is M times of  $I_{0UT}$ , the efficiency formula is:

$$\eta = \frac{P_{OUT}}{P_{IN}} * 100\% = \frac{V_{OUT} * I_{OUT}}{V_{IN} * M * I_{OUT}} * 100\% = \frac{V_{OUT}}{M * V_{IN}} * 100\%$$

Where M is the operating mode variable of the chargepump,  $V_{IN}$  is the output voltage of chargepump,

$I_{\it OUT}$  is the load current. For the DO-chargepump, the output voltage is twice of the input voltage, can greatly improve the power efficiency, taking into account the chargepump internal switching losses and IC quiescent current loss, the actual efficiency is as high as 90%.

AW87359 DO-chargepump can be set to pass-through mode and 2X chargepump mode via the register 0x02h [3] to supply power to the Class D output stage.

#### Chargepump structure

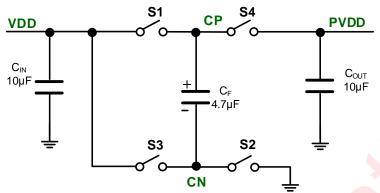

The basic diagram of the chargepump shows in Figure 11, the chargepump in AW87359 has four switches, the output voltage PVDD can reach twice of the input voltage through the four switches of the timing control.

Figure 11 Chargepump Schematic Diagram

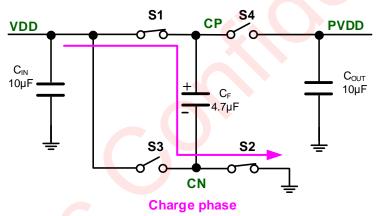

The chargepump works with two phases, in  $\Phi$ 1, as shown in the Figure 12: S1, S2 on, VDD charges the capacitor  $C_F$ .

Figure 12 Φ1: Flying Capacitor Charging

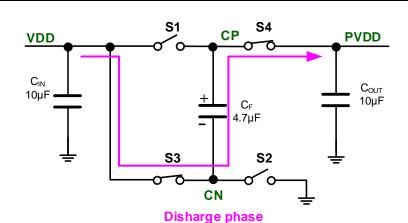

In  $\Phi$ 2, as shown in the Figure 13: S1 and S2 off, S3 and S4 on, since the voltage across the capacitor cannot be changed abruptly, the capacitors  $C_F$  are superimposed on VDD, causing the PVDD to rise to a higher voltage.

Figure 13 Φ2: Flying Capacitor Charge is Transferred to C<sub>OUT</sub>

#### Soft start

In order to limit the inrush current of the power supply during the start of the chargepump, the chargepump has a soft start function. The current limit is 300mA during start-up.

#### **Current limiting control**

DO-chargepump architecture integrates the current limiting control loop, in normal operation, the current limiting control loop controls the maximum output current capability of the chargepump when the load is too heavy or the chargepump flows through a large current.

#### Over-voltage protection(OVP) control

The output voltage PVDD is twice of the input voltage VDD in DO-chargepump structure, providing high voltage rail for internal power amplifier circuits, allowing the amplifier in the lithium battery voltage range to provide greater output dynamic range, in order to achieve high volume, high-quality class K audio amplifier playback sound quality. DO-chargepump integrated over-voltage protection control loop, when the input voltage VDD is greater than 4V, the output voltage PVDD is not twice of VDD, it is determined by the over-voltage control loop. And PVDD is stable at 8.0V.

#### Speaker & Receiver 2-in-1 application

AW87359 built-in speaker and receiver 2-in-1 application mode, through the register settings, there are class AB-type 2-in-1 receiver mode and class D-type 2-in-1 receiver mode can be selected, the gain can be adjusted through the I<sup>2</sup>C register 0x05, adjustable range of 0~9dB, the application is very flexible. The 2-in-1 receiver mode uses the signal path of the speaker, with ultra-low distortion and strong drive capability, and eliminates the need for additional peripheral components, saving system cost and PCB layout space.

In the typical application case of Figure 5, the input capacitance Cin=68nF, the gain is 16V/V in the speaker application mode, the input high-pass cutoff frequency is 260Hz; In 4.5dB gain class D-type 2-in-1 receiver application mode, The output noise is 16µV, the input high-pass cut-off frequency is 34Hz; In 0dB gain class AB-type 2-in-1 receiver application mode, the output noise is as low as 11µV, the input high-pass cut-off frequency is 22Hz, which is very suitable for high-definition voice applications. AW87359 can achieve speaker and receiver's 2-in-1 application without changing any hardware in the case.

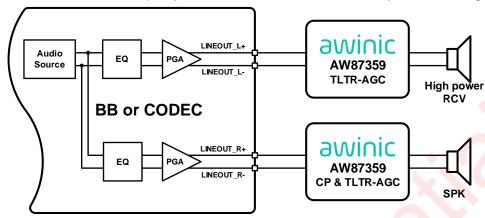

## **High Power Receiver Stereo Applications**

AW87359 built-in high-power receiver stereo application mode, makes full use of the receiver, not only takes the voice calls into account and uses the receiver as speaker, but also combines the AWINIC's propriety TLTR-AGC technology, significantly enhancing the stereo sound quality and volume, enhancing the dynamic music, therefore, high power receiver stereo application has gradually become a mainstream application in smart phone.

AW87359 is in the high-power receiver stereo application mode, when the register 0x02h [2] is set to 1. Gain adjustable range is 0~ 27dB by adjusting the I<sup>2</sup>C register 0x05h [4: 0], AGC3 power adjustable range is 0.1W~1.5W@8ohm receiver, 0.025W~0.375W@32ohm receiver through adjusting the I<sup>2</sup>C register 0x06h [3:0]. AW87359 can flexibly match a variety of high-power Receiver, combined with TLTR AGC technology, significantly enhance the stereo sound quality and volume, and enhance music dynamic listening.

Figure 14 AW87359 High Power Receiver Stereo Mode Application

## **RNS(RF TDD Noise Suppression)**

#### **TDD Noise Causes**

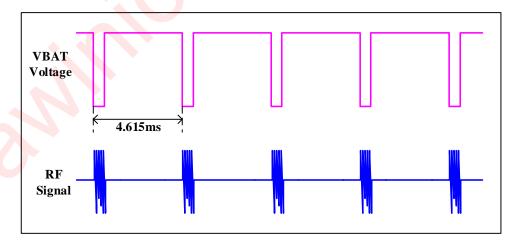

GSM cell phones use TDMA (Time Division Multiple Access) slot sharing technology. The time is divided into periodic frames in TDMA, and each frame is subdivided into a plurality of time slots. In order to transmit signals to the base station, the signals sent from the base stations to the plurality of mobile terminals are arranged in a predetermined time slot in the transmission. In this case, each TDMA frame contains 8 time slots, the entire frame is about 4.615ms long, and each slot time is 0.577ms.

With GSM handset, the RF power amplifier will transmit once every 4.615ms (217Hz), and the signal will produce intermittent Burst current and strong electromagnetic radiation. Intermittent Burst current will form a power fluctuation of 217 Hz; High frequency (900MHz and 1800MHz) RF signals form a 217Hz RF envelope signal. 217Hz power fluctuations will be conducted through the conduction to the audio signal path, 217Hz RF envelope signal will be coupled through the radiation into the audio signal path, if the protection is not good, it will produce an audible TDD Noise, which includes the 217Hz noise And a harmonic noise signal of 217 Hz.

Figure 15 Schematic Diagram of Power Supply Voltage and RF Signal during GSM RF Operation

RNS fully inhibit the conduction and radiation interference by the AWINIC unique circuit architecture. Effectively improve the ability to suppress TDD Noise.

## Conduction noise suppression

When the RF power amplifier is operating, it will draw the current from the battery by 217Hz frequency, Power supply will be introduced to 217Hz power ripple since the battery has a certain internal resistance, it will be coupled to the speaker through the audio power amplifier. The ability to suppress power fluctuations depends on the PSRR of the audio power amplifier.

$$PSRR = 20log(\frac{vout_{ac}}{vdd_{ac}})$$

Due to the input and output of the fully differential amplifier is perfectly symmetrical, theoretically, the effect of the power supply fluctuation on the two outputs is exactly the same, and the differential output is completely unaffected by the power supply fluctuation. In practice, due to process bias and other factors, the amplifier will have a certain mismatch, PSRR is generally better than -60dB, it shows the output relative to the power fluctuations can be reduced by 1000 times, such as 500mVp power fluctuations, the differential output of 0.5 MV, which basically can meet the application requirements.

But in practical applications, the power amplifier may encounter conduction of TDD Noise problem even if its PSRR is -60dB or -80dB, why is this? Because we also need to consider the impact of peripheral power mismatches of audio power amplifiers

For conventional audio power amplifiers, when the input resistor Rin and the input capacitor Cin mismatch, will greatly affect the audio power amplifier PSRR indicators, in the case of 24 times the gain, PSRR will be weakened to -46dB or so if the input resistance and Capacitor with 1% mismatch. PSRR will be weakened to -28dB or so if the input resistance and input capacitance mismatch with 10% mismatch, when the power fluctuations, it is easy to produce audible TDD Noise.

In order to enhance the audio power amplifier PSRR in the input resistance and input capacitance mismatch case, AW87359 features a unique conduction noise suppression circuit, making the power amplifier to maintain a high PSRR value even in the input resistance, the input capacitance deviation of 10% or more, this greatly inhibits the generation of conducted noise.

#### Radiation noise suppression

Input traces, output traces, horn loops, and even power and ground loops are likely to be subject to RF radiation interference in the audio signal module, longer input traces and output traces similar to the antenna, especially vulnerable RF radiation effects.

The reasonable PCB layout can reduce the influence of RF radiation in the design, such as shorten the line length of input and output as much as possible; audio devices should be shielded and far away from the RF antenna, maintain the integrity of the device to audio signal pathway; to increase the small bypass capacitor RF signals in the sensitive nodes. However, in practical applications, PCB layout is difficult to fully consider the influence of RF radiation on the audio signal path, and some RF energy will still be coupled to the audio signal path to form audible TDD Noise. Therefore, AW87359 features a unique RF radiation suppression circuit, a shielding layer inside the chip, effectively prevent high frequency energy into RF chip, to ensure that the drive single of the amplifier provided to the speaker will not be affected by the antenna RF radiation, thus avoiding the antenna RF Radiation caused by TDD Noise.

Figure 16 RF Radiation Coupling Graph

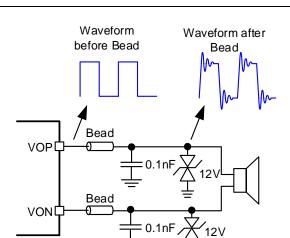

## Class D amplifier without filter

When the traditional class D amplifier is in idle state of no input signal, the output will have the inverse square wave, it will directly above the load of the speaker, will form a large current power switch on the speaker, therefore we need to increase the LC filter to restore the analog audio signal at the amplifier output. The LC filter increase the cost and PCB layout area, while increase the power consumption, reduce the performance of THD+N.

The AW87359 features a Class D amplifier without a filter, eliminating the need for an output LC filter. In the idle state of no input signal, the two outputs (VOP, VON) of the amplifier are in-phase square waves and not generate idle switching currents on the speaker load. When the input signal is added to the input terminal, the duty ratio of the output is changed. The duty cycle of the VOP becomes larger and the duty cycle of the VON becomes smaller, and the difference value of the output forms the differential amplified signal on the speaker.

#### EEE

The AW87359 features a unique Enhanced Emission Elimination (EEE) technology, that controls fast transition on the output, greatly reduces EMI over the full bandwidth, fully meet FCC CLASS B specification requirements.

## **Pop-Click Suppression**

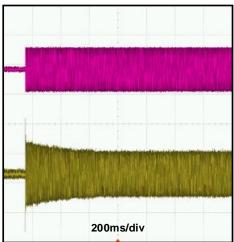

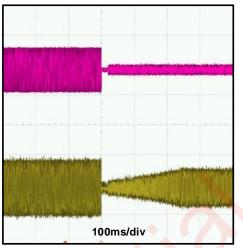

The AW87359 features unique timing control circuit, that comprehensively suppresses pop-click noise, eliminates audible transients on shutdown, wakeup, and power-up/down.

#### over temperature protection

When the AW87359 operates in a fault condition, the chip temperature is too high, up to a preset temperature protection temperature threshold (160°C), the system starts overheating protection, the chip will be turned off, restarts to resume normal work when the chip temperature returns to normal operating range (less than 130°C).

#### Automatic recovery of overcurrent protection

AW87359 with automatic recovery of the output overcurrent protection function, when the overcurrent occurs, AW87359 internal protection circuit will chip off to ensure that the chip is not damaged, when the short-circuit fault is eliminated, the chip will automatically resume working without restarting.

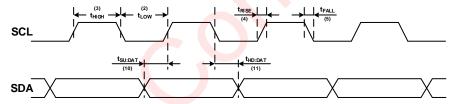

## I<sup>2</sup>C Timing feature

|     |                     | Parameter                                   | MIN    | TYP | MAX   | UNIT |  |

|-----|---------------------|---------------------------------------------|--------|-----|-------|------|--|

| No. | Sym                 | Name                                        | IVIIIV | ••• | IVIAA |      |  |

| 1   | f <sub>SCL</sub>    | SCL Clock frequency                         |        |     | 400   | kHz  |  |

| 2   | t <sub>LOW</sub>    | SCL Low level Duration                      | 1.3    |     |       | μs   |  |

| 3   | tніgн               | SCL High level Duration                     | 0.6    |     |       | μs   |  |

| 4   | trise               | SCL, SDA rise time                          |        |     | 0.3   | μs   |  |

| 5   | tFALL               | SCL, SDA fall time                          |        |     | 0.3   | μs   |  |

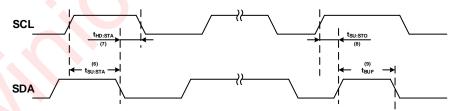

| 6   | tsu:sta             | Setup time SCL to START state               | 0.6    |     |       | μs   |  |

| 7   | thd:STA             | (Repeat-start) Start condition hold time    | 0.6    |     |       | μs   |  |

| 8   | t <sub>SU:STO</sub> | Stop condition setup time                   | 0.6    |     |       | μs   |  |

| 9   | t <sub>BUF</sub>    | the Bus idle time START state to STOP state | 1.3    |     |       | μs   |  |

| 10  | t <sub>SU:DAT</sub> | SDA setup time                              | 0.1    |     |       | μs   |  |

| 11  | thd:dat             | SDA hold time                               | 10     |     |       | ns   |  |

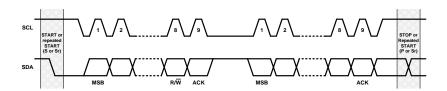

Figure 17 SCL and SDA timing relationships in the data transmission process

Figure 18 the Timing Relationship between START and STOP State

## General I<sup>2</sup>C Operation

The I<sup>2</sup>C bus employs two signals, SDA (data) and SCL (clock), to communicate between integrated circuits in a system. The device is addressed by a unique 7-bit address; the same device can send and receive data. In addition, Communications equipment has distinguish master from slave device: In the communication process, only the master device can initiate a transfer and terminate data and generate a corresponding clock signal. The devices using the address access during transmission can be seen as a slave device.

SDA and SCL connect to the power supply through the current source or pull-up resistor. SDA and SCL

default is a high level. All data to start transmission and end of transmission requires the main device to issue START state and STOP status:

START state: The SCL maintain a high level, SDA from high to low level

STOP state: The SCL maintain a high level, SDA pulled low to high level

Start and Stop states can be only generated by the master device. In addition, if the device does not produce STOP state after the data transmission is completed, instead re-generate a START state (Repeated START, Sr), and it is believed that this bus is still in the process of data transmission. Functionally, Sr state and START state is the same. As shown in Figure 19.

Figure 19 START and STOP State Generation Process

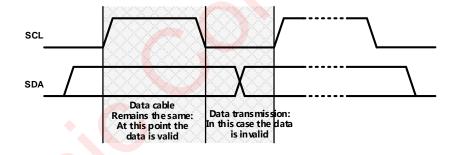

In the data transmission process, when the clock line SCL maintains a high level, the data line SDA must remain the same. Only when the SCL maintain a low level, the data line SDA can be changed, as shown in Figure 20. Each transmission of information on the SDA is 9 bits as a unit. The first eight bits are the data to be transmitted, and the first one is the most significant bit (Most Significant Bit, MSB), the ninth bit is an confirmation bit (Acknowledge, ACK or A), as shown in Figure 21. When the SDA transmits a low level in ninth clock pulse, it means the acknowledgment bit is 1, namely the current transmission of 8 bits data are confirmed, otherwise it means that the data transmission has not been confirmed. Any amount of data can be transferred between START and STOP state.

Figure 20 The Data Transfer Rules on the I<sup>2</sup>C Bus

The whole process of actual data transmission is shown in Figure 21. When generating a START condition, the master device sends an 8-bit data, including a 7-bit slave addresses (Slave Address), and followed by a "read / write" flag ( $R/\overline{W}$ ). The flag is used to specify the direction of transmission of subsequent data. The master device will produce the STOP state to end the process after the data transmission is completed. However, if the master device intends to continue data transmission, you can directly send a Repeated START state, without the need to use the STOP state to end transmission.

Figure 21 Data Transmission on the I<sup>2</sup>C Bus

#### I<sup>2</sup>C Read/Write Processes

The following describes two kinds of ways of the I<sup>2</sup>C bus data transmission:

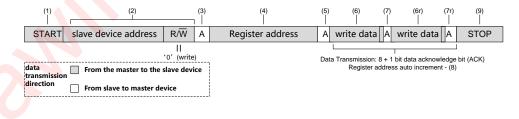

#### **Write Process**

Writing process refers to the master device write data into the slave device. In this process, the transfer direction of the data is always unchanged from the master device to the slave device. All acknowledge bits are transferred by the slave device, in particular, AW87359 as the slave device, the transmission process in accordance with the following steps, as shown in Figure 22:

Master device generates START state. The START state is produced by pulling the data line SDA to a low level when the clock SCL signal is a high level.

Master device transmits the 7-bits device address of the slave device, followed by the "read / write" flag  $(flag R/\overline{W} = 0)$ ;

The slave device asserts an acknowledgment bit (ACK) to confirm whether the device address is correct:

The master device transmits the 8-bit AW87359 register address to which the first data byte will written:

The slave device asserts an acknowledgment (ACK) bit to confirm the register address is correct; Master sends 8 bits of data to register which needs to be written;

The slave device asserts an acknowledgment bit (ACK) to confirm whether the data is sent successfully;

If the master device needs to continue transmitting data, it does not need further to send the register address for AW87359, within AW87359 each send confirmation bit(ACK) regret automatic accumulation register address then only need to repeat the sixth step and seven step:

The master device generates the STOP state to end the data transmission.

Figure 22 Writing Process (Data Transmission Direction Remains the Same)

## **Read Process**

Reading process refers to the slave device reading data back to the master device. In this process, the direction of data transmission will change. Before and after the change, the master device sends START state and slave address twice, and sends the opposite "read/write" flag. In particular, AW87359 as the

slave device, the transmission process carried out by following steps listed in Figure 23:

Master device asserts a start condition;

Master device transmits the 7 bits address of AW87359, and followed by a "read / write" flag (R/W = 0); The slave device asserts an acknowledgment bit (ACK) to confirm whether the device address is correct;

The master device sends the 8bit address that the AW87359 register needs to read the data;

The slave device asserts an acknowledgment (ACK) bit to confirm whether the register address is correct or not;

The master device restarts the data transfer process by continuously generating STOP state and START state or a separate Repeated START.

Master sends 7-bits address of the slave device and followed by a read / write flag (flag R/W = 1) again.

The slave device asserts an acknowledgment (ACK) bit to confirm whether the register address is correct or not.

The master transmits 8 bits of data to register which needs to be read;

The slave device sends an acknowledgment bit (ACK) to confirm whether the data is sent successfully. AW87359 automatically increment register address once after the slave sent each acknowledge bit (ACK).

The master device generates the STOP state to end the data transmission.

Figure 23 Reading Process (Data Transmission Direction Remains the Same)

## **Register List**

| name     | addr<br>ess | Bit7       | Bit6       | Bit5       | Bit4       | Bit3                      | Bit2                      | Bit1                      | Bit0                      |

|----------|-------------|------------|------------|------------|------------|---------------------------|---------------------------|---------------------------|---------------------------|

| Chip ID  | 0x00        | 0          | 1          | 0          | 1          | 1                         | 0                         | 0                         | 1                         |

| SYSCTRL  | 0x01        | 0          | 0          | 0          | 0          | EN_PA                     | EN_CP                     | 0                         | EN_SW                     |

| MODECTRL | 0x02        | 0          | 0          | 0          | 0          | EN_2X                     | EN_SPK(1)                 | EN_LG                     | EN_AB(2)                  |

| CPOVP    | 0x03        | 0          | 0          | 0          | 0          | CP_OVP <sup>(3)</sup> [3] | CP_OVP <sup>(3)</sup> [2] | CP_OVP <sup>(3)</sup> [1] | CP_OVP <sup>(3)</sup> [0] |

| CPP      | 0x04        | 0          | 0          | 0          | 0          | 0                         | 1                         | 0                         | 1                         |

| Gain     | 0x05        | 0          | 0          | 0          | Gain [4]   | Gain [3]                  | Gain [2]                  | Gain [1]                  | Gain [0]                  |

| AGC3_Po  | 0x06        | 0          | 0          | 0          | 0          | AGC3_Po[3]                | AGC3_Po[2]                | AGC3_Po[1]                | AGC3_Po[0]                |

| AGC3     | 0x07        | AGC3_RT[2] | AGC3_RT[1] | AGC3_RT[0] | AGC3_AT[2] | AGC3_AT[1]                | AGC3_AT[0]                | AGC3FAST[1]               | AGC3FAST[0]               |

| AGC2_Po  | 80x0        | 0          | 0          | 0          | 0          | AGC2_Po[3]                | AGC2_Po[2]                | AGC2_Po[1]                | AGC2_Po[0]                |

| AGC2     | 0x09        | 0          | 0          | 0          | AGC2_AT[2] | AGC2_AT[1]                | AGC2_AT[0]                | AGC2FAST[1]               | AGC2FAST[0]               |

| AGC1     | 0x0A        | 0          | 1          | 0          | 0          | 1                         | AGC1_AT[1]                | AGC1_AT[0]                | PD_AGC1                   |

- (1) EN\_SPK: enable speaker application

- (2) EN\_AB: enable class AB application

- (3) CP\_OVP: chargepump OVP voltage

| register | 0x00 | 0x01 | 0x02 | 0x03 | 0x04 | 0x05                                              | 0x06                                                   | 0x0<br>7 | 0x08                   | 0x09 | 0x0A |

|----------|------|------|------|------|------|---------------------------------------------------|--------------------------------------------------------|----------|------------------------|------|------|

|          |      |      |      |      |      | 0x00<br>(EN_SPK=1 &&<br>EN_LG=1)   <br>(EN_SPK=0) | 0x00<br>(EN_SPK=1 &&<br>EN_LG=1)                       | 0x4      | 0x06<br>(EN_SPK<br>=1) |      |      |

| Default  | 0x59 | 0x0C | 0x0C | 0x08 | 0x05 | 0x10<br>(EN_SPK=1 &&<br>EN_LG=0)                  | 0x07<br>(EN_SPK=1 &&<br>EN_LG=0)<br>0x0F<br>(EN_SPK=0) | E        | 0x09<br>(EN_SPK<br>=0) | 0x08 | 0x4A |

#### Table 2 AW87359 Register Default Value

Any register address which is more than 0x0A and all reserved bits are reserved for debugging and testing purposes. Changing their values may affect the normal function of the power amplifier; Reading them will get any possible values. AW87359's I2C address is 10110A2A1, as shown in Table 3, in order to avoid conflict with other I2C devices address, you can pull up or pull-down AW87359 of AD2 and AD1 pins to set the value of A2 and A1, respectively. The following lists specific information about all visible registers, including default values and programmable ranges.

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| 1    | 0    | 1    | 1    | 0    | A2   | A1   | R/W  |

#### Table 3 AW87359 Address Byte

## CHIP ID Register (address: 0x00)

| I <sup>2</sup> C Bit | Name   | R/W | Default Description |                                                                                                                            |

|----------------------|--------|-----|---------------------|----------------------------------------------------------------------------------------------------------------------------|

| 7:0                  | IDCODE | R   | 0x59                | Chip ID will be returned after reading. All configuration registers will be reset to default values after 0xAA is written. |

#### SYSTEM CONTROL (SYSCTRL) Register (address: 0x01)

| I <sup>2</sup> C Bit | Name        | R/W   | Default | Description                                    |

|----------------------|-------------|-------|---------|------------------------------------------------|

| 7:4                  |             |       | 0000    | Reserved and Unused                            |

|                      |             |       | 4       | Power Amplifier enable                         |

| 2                    | 3 EN PA R/W | R/W   |         | 0: Power Amplifier disable                     |

| 3                    | EN_FA       | IN/VV | ľ       | 1: Power Amplifier enable, the PA working mode |

|                      |             |       |         | depends on EN_AB                               |

| 2                    | EN_CP       | R/W   | 1       | Chargepump Enable                              |

www.awinic.com.cn

|   |       |     |   | 0: Charge Pump disable, PVDD=0                              |

|---|-------|-----|---|-------------------------------------------------------------|

|   |       |     |   | 1: Charge Pump enable, the CP working mode depends on EN 2X |

| 1 |       |     | 0 | Reserved and Unused                                         |

|   |       |     |   | CP and PA software power-up                                 |

| 0 | EN_SW | R/W | 0 | 0: CP and PA software power-down                            |

|   |       |     |   | 1: CP and PA software power-up                              |

## MODE CONTROL (MODECTRL) Register (address: 0x02)

| I <sup>2</sup> C Bit | Name   | R/W | Default | Description                         |

|----------------------|--------|-----|---------|-------------------------------------|

| 7:4                  |        |     | 000     | Reserved and Unused                 |

|                      |        |     |         | 2X Charge Pump Mode enable          |

| 3                    | EN_2X  | R/W | 1       | 0: 1X Direct Through Mode enable    |

|                      |        |     |         | 1: 2X Charge Pump Mode enable       |

|                      |        |     |         | SPK Mode or RCV Mode enable         |

| 2                    | EN_SPK | R/W | 1       | 0: SPK Mode disable                 |

|                      |        |     |         | 1: SPK Mode enable                  |

|                      |        |     |         | Low Gain enable                     |

| 1                    | EN_LG  | R/W | 0       | 0: Low Gain disable                 |

|                      |        |     |         | 1: Low Gain enable                  |

|                      |        | R/W |         | Class AB enable, Class D disable    |

| 0                    | EN_AB  |     | 0       | 0: Class AB disable, Class D enable |

|                      | _      |     |         | 1: Class AB enable, Class D disable |

## CHARGEPUMP OUTPUT VOLTAGE (CPOVP) Register (address: 0x03)

| I <sup>2</sup> C Bit | Name   | R/W   | Default | Description                                    |

|----------------------|--------|-------|---------|------------------------------------------------|

| 7:4                  |        |       | 0000    | Reserved and Unused                            |

|                      |        |       |         | Setting Chargepump OVP Voltage                 |

|                      |        |       |         | 1011~1111: reserved. If set, turns to default. |

|                      |        |       |         | 0000: 6.0V                                     |

|                      |        |       |         | 0001: 6.25V                                    |

|                      |        |       |         | 0010: 6.5V                                     |

|                      |        |       |         | 0011: 6.75V                                    |

| 3:0                  | CP_OVP | R/W   | 1000    | 0100: 7V                                       |

|                      |        |       |         | 0101: 7.25V                                    |

|                      |        |       |         | 0110: 7.5V                                     |

|                      |        |       |         | 0111: 7.75V                                    |

|                      |        |       |         | <u>1000</u> : 8V                               |

|                      |        |       |         | 1001: 8.25V                                    |

|                      |        |       |         | 1010: 8.5V                                     |

|                      |        |       |         | Charge Pump OVP voltage setting. When EN_AB=1  |

|                      |        |       |         | && EN_2X=1                                     |

| 3:0                  | CP OVP | R/W   | 0000    | 0011~1111: reserved. If set, turns to default. |

| 3.0                  | GF_OVF | IT/VV | 0000    | <u>0000</u> : 6.0V                             |

|                      |        |       |         | 0001: 6.25V                                    |

|                      |        |       |         | 0010: 6.5V                                     |

## CHAREPUMP PARAMETER (CPP) Register (address: 0x04)

| I <sup>2</sup> C Bit | Name | R/W | Default  | Description         |

|----------------------|------|-----|----------|---------------------|

| 7:0                  |      |     | 00000101 | Reserved and Unused |

## GAIN CONTROL (Gain) Register (address: 0x05)

#### For EN\_SPK=1 && EN\_LG=1:

| I <sup>2</sup> C Bit | Name | R/W | Default | Description         |

|----------------------|------|-----|---------|---------------------|

| 7:5                  |      |     | 000     | Reserved and Unused |

|     |      |     |       | Power Amplifier Gain setting 10011~11111: reserved. If set, turns to default. 00000: 0dB                                                      |

|-----|------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 4:0 | Gain | R/W | 00000 | 00001: 1.5dB<br>00010: 3dB<br>00011: 4.5dB<br>00100: 6dB<br>00101: 7.5dB<br>00110: 9dB<br>00111: 10.5dB<br>01000: 12dB                        |

|     |      |     |       | 01001: 13.5dB<br>01010: 15dB<br>01011: 16.5dB<br>01100: 18dB<br>01101: 19.5dB<br>01110: 21dB<br>01111: 22.5dB<br>10000: 24dB<br>10001: 25.5dB |

#### For EN\_SPK=1 && EN\_LG=0:

| I <sup>2</sup> C Bit | Name | R/W | Default | Description                                                                                                                                                                                                                             |

|----------------------|------|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5                  |      |     | 000     | Reserved and Unused                                                                                                                                                                                                                     |

| 4:0                  | Gain | R/W | 10000   | Power Amplifier Gain setting  00000~00111, 10011~11111: reserved. If set, turns to default.  01000: 12dB  01001: 13.5dB  01010: 15dB  01011: 16.5dB  01100: 18dB  01101: 19.5dB  01110: 21dB  01111: 22.5dB  10000: 24dB  10001: 25.5dB |

## For EN\_SPK=0:

| I <sup>2</sup> C Bit | Name | R/W | Default | Description                                                                                           |

|----------------------|------|-----|---------|-------------------------------------------------------------------------------------------------------|

| 7:5                  |      |     | 000     | Reserved and Unused                                                                                   |

| 0                    |      |     |         | Power Amplifier Gain setting 00111~11111: reserved. If set, turns to default. 00000: 0dB 00001: 1.5dB |

| 4:0                  | Gain | R/W | 00000   | 00011: 1.5dB<br>00010: 3dB<br>00011: 4.5dB<br>00100: 6dB                                              |

|                      |      |     |         | 00101: 7.5dB<br>00110: 9dB                                                                            |

## AGC3 OUTPUT POWER (AGC3\_Po) Register (address: 0x06)

#### For EN\_SPK=1 && EN\_LG=1:

| I <sup>2</sup> C Bit | Name | R/W | Default | Description |

|----------------------|------|-----|---------|-------------|

www.awinic.com.cn

| 7:4 |         |     | 000  | Reserved and Unused                                                                                                                                                                                                                                                              |

|-----|---------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0 | AGC3_PO | R/W | 0000 | Reserved and Unused  AGC3 Output Power setting  0000: 0.1W@8Ω  0001: 0.2W@8Ω  0010: 0.3W@8Ω  0011: 0.4W@8Ω  0100: 0.5W@8Ω  0101: 0.6W@8Ω  0110: 0.7W@8Ω  0111: 0.8W@8Ω  1000: 0.9W@8Ω  1001: 1.0W@8Ω  1001: 1.1W@8Ω  1011: 1.2W@8Ω  1101: 1.4W@8Ω  1110: 1.5W@8Ω  1111: AGC3 OFF |

#### For EN\_SPK=1 && EN\_LG=0:

| I <sup>2</sup> C Bit | Name    | R/W | Default | Description                                                                                                                                                                                                                                                    |

|----------------------|---------|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4                  |         |     | 000     | Reserved and Unused                                                                                                                                                                                                                                            |

| 3:0                  | AGC3_PO | R/W | 0111    | AGC3 Output Power setting  0000~0011: reserved. If set, turns to default.  0100: 0.5W@8Ω  0101: 0.6W@8Ω  0110: 0.7W@8Ω  0111: 0.8W@8Ω  1000: 0.9W@8Ω  1001: 1.0W@8Ω  1010: 1.1W@8Ω  1011: 1.2W@8Ω  1101: 1.3W@8Ω  1101: 1.4W@8Ω  1101: 1.5W@8Ω  1111: AGC3 OFF |

#### For EN\_SPK=0:

| I <sup>2</sup> C Bit | Name    | R/W | Default Description |                                                |  |

|----------------------|---------|-----|---------------------|------------------------------------------------|--|

| 7:4                  | <b></b> |     | 000                 | Reserved and Unused                            |  |

|                      |         |     |                     | AGC3 Output Power setting                      |  |

| 3:0                  | AGC3_PO | R/W | 1111                | 0000~1110: reserved. If set, turns to default. |  |

|                      |         |     |                     | 1111: AGC3 OFF                                 |  |

## AGC3 PARAMETER (AGC3) Register (address: 0x07)

| I <sup>2</sup> C Bit | Name    | R/W | Default | ault Description          |  |  |  |

|----------------------|---------|-----|---------|---------------------------|--|--|--|

|                      |         |     |         | AGC3 Release Time setting |  |  |  |

|                      |         |     |         | 000: 5.12ms/dB            |  |  |  |

|                      |         |     |         | 001: 10.24ms/dB           |  |  |  |

|                      |         |     |         | <u>010</u> : 20.48ms/dB   |  |  |  |

| 7:5                  | AGC3_RT | R/W | 010     | 011: 41ms/dB              |  |  |  |

|                      |         |     |         | 100: 82ms/dB              |  |  |  |

|                      |         |     |         | 101: 164ms/dB             |  |  |  |

|                      |         |     |         | 110: 328ms/dB             |  |  |  |

|                      |         |     |         | 111: 656ms/dB             |  |  |  |

| 4:2                  | AGC3_AT | R/W | 011     | AGC3 Attack Time setting  |  |  |  |

www.awinic.com.cn

|     |          |     |    | 000: 1.28ms/dB                 |

|-----|----------|-----|----|--------------------------------|

|     |          |     |    | 001: 2.56ms/dB                 |

|     |          |     |    | 010: 10.24ms/dB                |

|     |          |     |    | 011: 41ms/dB                   |

|     |          |     |    | 100: 82ms/dB                   |

|     |          |     |    | 101: 164ms/dB                  |

|     |          |     |    | 110: 328ms/dB                  |

|     |          |     |    | 111: 656ms/dB                  |

|     |          |     |    | AGC3 First Attack Time setting |

|     |          |     |    | 00: 10.24ms/dB                 |

| 1:0 | AGC3FSAT | R/W | 10 | 01: 20.48ms/dB                 |

|     |          |     |    | <u>10</u> : 41ms/dB            |

|     |          |     |    | 11: 82ms/dB                    |

## AGC2 OUTPUT POWER(AGC2\_Po) Register (address: 0x08)

## For EN\_SPK=1:

| I <sup>2</sup> C Bit | Name    | R/W | R/W Default Description |                                                |  |  |  |  |

|----------------------|---------|-----|-------------------------|------------------------------------------------|--|--|--|--|

| 7:4                  |         |     | 000 Reserved and Unused |                                                |  |  |  |  |

|                      |         |     |                         | AGC2 Output Power setting                      |  |  |  |  |

|                      |         |     |                         | 1010~1111: reserved. If set, turns to default. |  |  |  |  |

|                      |         |     |                         | 0000: 0.4W@8Ω                                  |  |  |  |  |

|                      |         |     |                         | 0001: 0.6W@8Ω                                  |  |  |  |  |

|                      |         |     |                         | 0010: 0.8W@8Ω                                  |  |  |  |  |

| 3:0                  | AGC2_PO | R/W | 0110                    | 001 <mark>1:</mark> 1.0W@8Ω                    |  |  |  |  |

|                      |         |     |                         | 0100 <mark>: 1.2W@8</mark> Ω                   |  |  |  |  |