300mA Ultra-low Noise, Ultra-Fast CMOS LDO Regulator

#### **FEATURES**

- Ultra-low Noise

- Ultra-Fast Response in Line/Load Transient

- 0.01μA Standby Current When Shutdown

- Low Dropout: 205mV@300mA

- Wide Operating Voltage Ranges: 2.2V to 6V

- Low Temperature Coefficient

- Current Limiting Protection

- Thermal Shutdown Protection

- Only 1μF Output Capacitor Required for Stability

- High Power Supply Rejection Ratio

- Fast output discharge

- Available in SOT23-5, SOT23-3, SC70-5 and DFN1×1-4L Package

### **APPLICATIONS**

- Cellular and Smart Phones

- Cordless Telephones

- Battery-Powered Equipment

- Laptop, Palmtops, Notebook Computers

- Hand-Held Instruments

- PCMCIA Cards

- MP3/MP4/MP5 Players

- Portable Information Appliances

#### **DESCRIPTION**

The BL9161G is designed for portable applications with demanding performance and space requirements. The BL9161G performance is optimized for battery-powered systems to deliver ultra low noise and low quiescent current. Regulator ground current increases only slightly in dropout, further prolonging the battery life. The BL9161G also works with low-ESR ceramic capacitors, reducing the amount of board necessary for power applications, critical in hand-held wireless devices. The BL9161G consumes only 0.01µA current in shutdown mode and has fast turn-on time (Typical 50µs). The other features include ultra low dropout voltage, high output accuracy, current limiting protection, and high ripple rejection ratio.

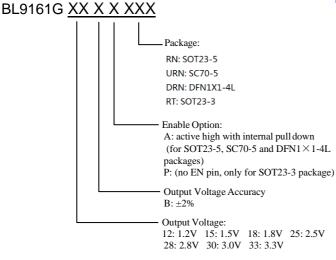

### ORDERING INFORMATION

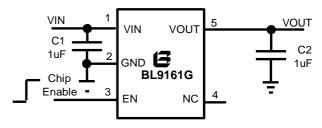

### **TYPICAL APPLICATION**

#### **Application hints:**

Output capacitor (C2 $\geqslant$  2.2uF) is recommended in BL9161G-1.2V, BL9161G-1.5V and BL9161G-1.8V application to assure the stability of circuit.

300mA Ultra-low Noise, Ultra-Fast CMOS LDO Regulator

# **Absolute Maximum Rating** (Note 1)

Input Supply Voltage (VIN) EN Pin Input Voltage Output Voltages Output Current

-0.3V to +6V -0.3V to VIN -0.3V to VIN+0.3V 300mA Maximum Junction Temperature 150°C

Operating Temperature Range (Note2) -40°C to 85°C

Storage Temperature Range -65°C to 125°C

Lead Temperature (Soldering, 10s) 300°C

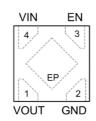

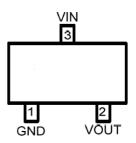

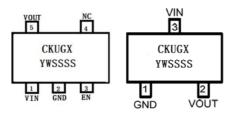

### **PIN CONFIGURATIONS**

### **SOT23-5 &SC70-5(TOP VIEW)**

### **DFN1X1-4L(TOP VIEW)**

### SOT23-3(TOP VIEW)

## **Package Marking**

#### SOT23-5 & SC70-5 SOT23-3

DFN1×1-4L

### Thermal Resistance (Note 3):

| Package | $\Theta_{JA}$ | $\Theta_{JC}$ |

|---------|---------------|---------------|

| SOT23-5 | 250℃/W        | 130°C/W       |

| SC70-5  | 333℃///       | 170°C/W       |

CKUG: Chip ID

X: Output voltage

Y: Data code—Year

W: Data code—Week

G: Chip ID

X: Output voltage

W: Data code—Week

| Output voltage                 | 1.2V | 1.5V | 1.8V | 2.5V | 2.8V | 3.0V | 3.3V |

|--------------------------------|------|------|------|------|------|------|------|

| X(SOT23-5, SOT23-3&<br>SC70-5) | В    | С    | D    | E    | G    | 1    | K    |

| X(DFN1×1-4L)                   | В    | С    | D    | Е    | G    | I    | K    |

| Y     | 4    | 5    | 6    | <br>0    | 1    |  |

|-------|------|------|------|----------|------|--|

| Year  | 2014 | 2015 | 2016 | <br>2020 | 2021 |  |

| i cai | 2014 | 2013 | 2010 | <br>2020 | 2021 |  |

| W    | Α | <br>Υ  | Z  | а  | <br>У  | Z  |

|------|---|--------|----|----|--------|----|

|      |   |        |    |    |        |    |

| Week | 1 | <br>25 | 26 | 27 | <br>51 | 52 |

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

Note 2: The BL9161G is guaranteed to meet performance specifications from 0°C to 70°C. Specifications over the – 40°C to 85°C operating temperature range are assured by design, characterization and correlation withstatistical process controls.

Note 3: Thermal Resistance is specified with approximately 1 square of 1 ozcopper.

300mA Ultra-low Noise, Ultra-Fast CMOS LDO Regulator

## **Pin Description**

## SOT23-5, SC70-5 & SOT23-3

| PIN                |         |      |                                                              |

|--------------------|---------|------|--------------------------------------------------------------|

| SOT23-5<br>&SC70-5 | SOT23-3 | NAME | FUNCTION                                                     |

| 1                  | 3       | VIN  | Power Input Voltage.                                         |

| 2                  | 1       | GND  | Ground.                                                      |

| 3                  |         | EN   | Chip Enable Pin, This pin has an internal pull-down resistor |

| 4                  |         | NC   | No Connection.                                               |

| 5                  | 2       | VOUT | Output Voltage.                                              |

### DFN1X1-4L

| PIN     | NAME | FUNCTION                                                       |

|---------|------|----------------------------------------------------------------|

| 1       | VOUT | Output Voltage.                                                |

| 2       | GND  | Ground.                                                        |

| 3       | EN   | Chip Enable Pin, This pin has an internal pull-down resistor   |

| 4       | VIN  | Power Input Voltage.                                           |

| Exposed |      | The exposed pad should be connected to a large ground plane to |

| Pad     |      | maximize thermal performance.                                  |

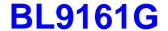

# **Block Diagram**

300mA Ultra-low Noise, Ultra-Fast CMOS LDO Regulator

## **Electrical Characteristics** (Note 4)

( $V_{IN}$ =Vout +1V, EN= $V_{IN}$ ,  $C_{IN}$ = $C_{OUT}$ =1 $\mu$ F,  $T_A$ =25 $^{\circ}$ C, unless otherwise noted.)

|                         | rameter                                        | Symbol            | Conditions                                         | MIN | TYP  | MAX  | unit          |

|-------------------------|------------------------------------------------|-------------------|----------------------------------------------------|-----|------|------|---------------|

| Inpu                    | t Voltage                                      | V <sub>IN</sub>   |                                                    | 2.2 |      | 6    | V             |

| Output Voltage Accuracy |                                                | $\Delta V_{OUT}$  | V <sub>IN=</sub> Vout+1V,<br>I <sub>OUT</sub> =1mA | -2  |      | +2   | %             |

| Cur                     | rent Limit                                     | I <sub>LIM</sub>  | $R_{LOAD}=1\Omega$                                 | 360 | 450  |      | mA            |

| Quieso                  | ent Current                                    | ΙQ                | V <sub>EN</sub> >1.2V, I <sub>OUT</sub> =0mA       |     | 70   | 110  | μΑ            |

| Drong                   | out Voltage                                    | $V_{DROP}$        | $I_{OUT}$ =200mA, $V_{OUT}$ =3.3V                  |     | 135  | 200  | - mV          |

| Бторс                   | out voltage                                    | V DROP            | $I_{OUT}$ =300mA, $V_{OUT}$ =3.3V                  |     | 205  | 300  | IIIV          |

| Line Reg                | gulation <sup>(Note 5)</sup>                   | $\Delta V_{LINE}$ | V <sub>IN</sub> =Vout+1V to 5.5V                   |     | 0.02 | 0.17 | %/V           |

|                         |                                                |                   | I <sub>OUT</sub> =1mA                              |     |      |      |               |

| Load Re                 | egulation(Note6)                               | $\Delta V_{LOAD}$ | 1mA <i<sub>OUT&lt;300mA</i<sub>                    |     | 20   |      | mV            |

|                         | Output Voltage(Note 7) Temperature Coefficient |                   | I <sub>OUT</sub> =1mA                              |     | ±60  |      | ppm/°C        |

| Stand                   | by Current                                     | I <sub>STBY</sub> | V <sub>EN</sub> =GND,<br>Shutdown                  |     | 0.01 | 1    | μА            |

| EN Input                | Bias Current                                   | I <sub>IBSD</sub> | V <sub>EN</sub> =GND or V <sub>IN</sub>            |     |      | 2    | μΑ            |

| EN<br>Input             | Logic Low                                      | V <sub>IL</sub>   | V <sub>IN</sub> =3V to 5.5V,<br>Shutdown           |     |      | 0.4  | V             |

| Threshold               | Logic High                                     | V <sub>IH</sub>   | V <sub>IN</sub> =3V to 5.5V,<br>Start up           | 1.2 |      |      | V             |

|                         | Output Noise<br>Voltage                        |                   | 10Hz to100KHz,<br>I <sub>OUT</sub> =100mA          |     | 180  |      | $\mu V_{RMS}$ |

| Power                   | f=217Hz                                        |                   |                                                    |     | -75  |      |               |

| Supply                  | f=1KHz                                         | PSRR              | RR I <sub>OUT</sub> =10mA                          |     | -71  |      | dB            |

| Rejection .<br>Ratio    | f=10KHz                                        |                   |                                                    |     | -55  |      | 1             |

| Therma<br>Tem           | al Shutdown<br>nperature                       | T <sub>SD</sub>   | Shutdown, Temp increasing                          |     | 170  |      | $^{\circ}$    |

|                         | al Shutdown<br>steresis                        | T <sub>SDHY</sub> |                                                    |     | 30   |      | $^{\circ}$ C  |

Note 4: Production test at +25°C. Specifications over the temperature range are guaranteed by design and characterization.

Note 5: Line regulation is calculated by

$$\Delta V_{LINE} = \left| \left( \frac{V_{OUT1} - V_{OUT2}}{\Delta V_{IN} \times V_{OUT (normal)}} \right) \right| \times 100$$

Where  $V_{OUT1}$  is the output voltage when  $V_{IN}$ =5.5V, and  $V_{OUT2}$  is the output voltage when  $V_{IN}$ =4.3V,

$\Delta V_{IN}$ =1.2V.  $V_{OUT}$  (normal) =3.3V.

Note 6: Load regulation is calculated by V<sub>load</sub>=Vout1-Vout2

Where V<sub>OUT1</sub> is the output voltage when I<sub>OUT</sub>=1mA, and V<sub>OUT2</sub> is the output voltage when I<sub>OUT</sub>=300mA.

**Note 7:** The temperature coefficient is calculated by  $TC_{T_{OUT}} = \frac{\Delta V_{OUT}}{\Delta T \times V_{OUT}}$

300mA Ultra-low Noise, Ultra-Fast CMOS LDO Regulator

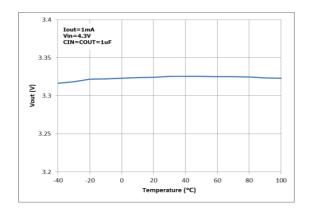

## **Typical Performance Characteristics**

### **Output Voltage Vs. Temperature**

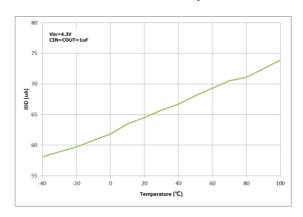

#### **Quiescent Current Vs. Temperature**

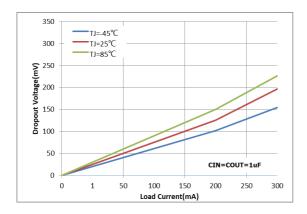

### **Dropout Voltage Vs. Load Current**

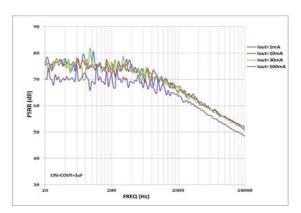

#### **PSRR**

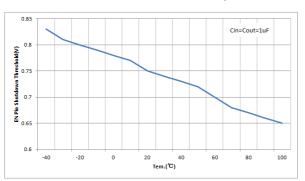

### EN Pin Shutdown Threshold Vs. Temperature

300mA Ultra-low Noise, Ultra-Fast CMOS LDO Regulator

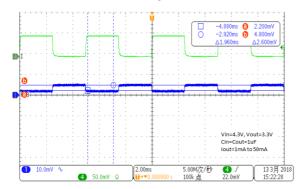

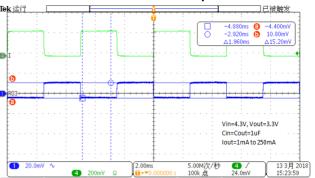

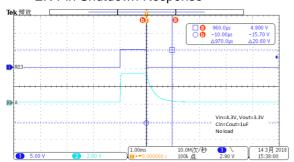

#### **Load Transient Response**

# Load Transient Response

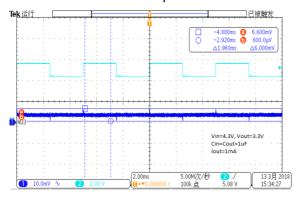

#### Line transient Response

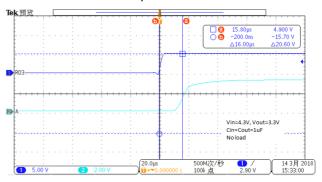

#### Start up

#### EN Pin Shutdown Response

300mA Ultra-low Noise, Ultra-Fast CMOS LDO Regulator

# **Applications Information**

Like any low-dropout regulator, the external capacitors used with the BL9161G must be carefully selected for regulator stability and performance. Using a capacitor whose value is > 1µF on the BL9161G input and the amount of capacitance can be increased without limit. The input capacitor must be located a distance of not more than 0.5 inch from the input pin of the IC and returned to a clean analog ground. Any good quality ceramic or tantalum can be used for this capacitor. The capacitor with larger value and lower ESR (equivalent series resistance) provides better PSRR and line-transient response. The output capacitor must meet both requirements for minimum amount of capacitance and ESR in all LDOs application. The BL9161G is designed specifically to work with low ESR ceramic output capacitor in space-saving and performance consideration. Using a ceramic capacitor whose value is at least 1µF with ESR is >  $25m\Omega$  on the BL9161G output ensures stability. The BL9161G still works well with output capacitor of other types due to the wide stable ESR range. Output capacitor of larger capacitance can reduce noise and improve load transient response, stability, and PSRR. The output capacitor should be located not more than 0.5 inch from the Vout pin of the BL9161G and returned to a clean analog ground.

#### **Enable Function**

The BL9161G features an LDO regulator enable/disable function. To assure the LDO regulator will switch on; the EN turn on control level must be greater than 1.2 volts. The LDO regulator will go into the shut-

down mode when the voltage on the EN pin falls below 0.4 volts. For to protect the system, the BL9161G have a quick discharge function. If the enable function is not needed in a specific application, it may be tied to  $V_{\text{IN}}$  to keep the LDO regulator in a continuously on state.

#### **Thermal Considerations**

Thermal protection limits power dissipation in BL9161G. When the operation junction temperature exceeds 170°C, the OTP circuit starts the thermal shutdown function turn the pass element off. The pass element turns on again after the junction temperature cools by 30°C.

For continue operation, do not exceed absolute maximum operation junction temperature 125°C. The power dissipation definition in device is:

$$P_D(MAX) = (T_J(MAX) - T_A)/\theta_{JA}$$

Where T<sub>J</sub>(MAX) is the maximum operation junction temperature 125°C, T<sub>A</sub> is the ambient temperature and the  $\theta_{JA}$  is the junction to ambient thermal resistance. For recommended operating conditions specification of BL9161G, where T<sub>J</sub>(MAX) is the maximum junction temperature of the die (125°C) and T<sub>A</sub> is the maximum ambient temperature. The junction ambient thermal resistance ( $\theta_{JA}$  is layout dependent) for SOT-23-5 package is 250°C/W, on standard JEDEC 51-3 thermal test board. The maximum power dissipation at T<sub>A</sub>= 25°C can be calculated by following formula:

300mA Ultra-low Noise, Ultra-Fast CMOS LDO Regulator

$P_D(MAX) = (125^{\circ}C-25^{\circ}C)/250 = 400$ mW (SOT-23-5)

The maximum power dissipation depends on operating ambient temperature for fixed  $T_J(MAX)$  and thermal resistance  $\theta_{JA}$ . It is also useful to calculate the junction of temperature of the BL9161G under a set of specific conditions. In this example let the Input voltage  $V_{IN}=3.3V$ , the output current Io=300mA and the case temperature  $T_A=40^{\circ}C$  measured by a thermal couple during operation. The power dissipation for the  $V_{OUT}=2.8V$  version of the BL9161G can be calculated as:

$P_D = (3.3V-2.8V) \times 300mA + 3.6V \times 100uA$ =150mW

And the junction temperature, T<sub>J</sub>, can be calculated as follows:

$T_J=T_A+P_D\times\theta_{JA}=40^{\circ}C+0.15W\times250^{\circ}C/W$ =40°C+37.5°C=77.5°C< $T_J(MAX)$ =125°C

For this operating condition, T<sub>J</sub> is lower than the absolute maximum operating junction temperature,125°C, so it is safe to use the BL9161G in this configuration.

#### **Layout considerations**

To improve ac performance such as PSRR, output noise, and transient response, it is recommended that the PCB be designed with separate ground planes for  $V_{\text{IN}}$  and  $V_{\text{OUT}}$ , with each ground plane connected only at the GND pin of the device.

300mA Ultra-low Noise, Ultra-Fast CMOS LDO Regulator

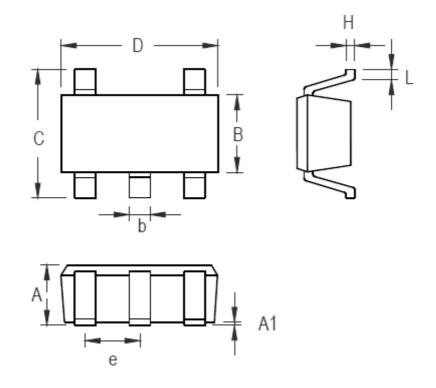

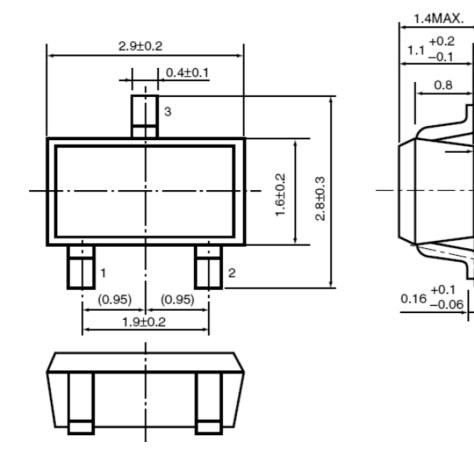

# **Package Description**

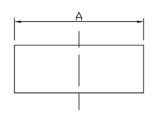

SOT23-5

| Cumbal | Dimensions In | n Millimeters | Dimensions In Inches |       |  |

|--------|---------------|---------------|----------------------|-------|--|

| Symbol | Min           | Max           | Min                  | Max   |  |

| А      | 0.889         | 1.295         | 0.035                | 0.051 |  |

| A1     | 0.000         | 0.152         | 0.000                | 0.006 |  |

| В      | 1.397         | 1.803         | 0.055                | 0.071 |  |

| b      | 0.356         | 0.559         | 0.014                | 0.022 |  |

| С      | 2.591         | 2.997         | 0.102                | 0.118 |  |

| D      | 2.692         | 3.099         | 0.106                | 0.122 |  |

| е      | 0.838         | 1.041         | 0.033                | 0.041 |  |

| Н      | 0.080         | 0.254         | 0.003                | 0.010 |  |

| L      | 0.300         | 0.610         | 0.012                | 0.024 |  |

300mA Ultra-low Noise, Ultra-Fast CMOS LDO Regulator

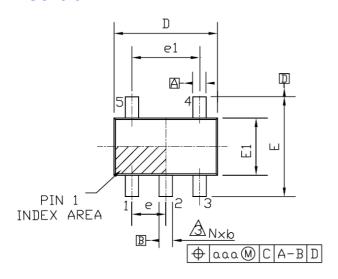

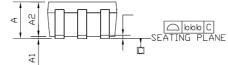

### **SC70-5**

GUAGE PLANE

SEATING PLANE

VIEW A-A

| СПМ        | COMMON DIMENSION |           |      |  |  |  |

|------------|------------------|-----------|------|--|--|--|

| TOWK 49    | IN M             | ILLIMET   | ERS  |  |  |  |

| )<br> <br> | MIN              | NOMAL     | MAX  |  |  |  |

| Α          | 0.80             | ı         | 1.10 |  |  |  |

| A1         | 0                | ı         | 0.10 |  |  |  |

| A2         | 0.80             | 0.90      | 1.00 |  |  |  |

| А3         | 0.47             | 0.52      | 0.57 |  |  |  |

| Α4         | 0.33             | 0.38      | 0.43 |  |  |  |

| b          | 0.15             | ı         | 0.30 |  |  |  |

| Π          | 0.10             | ı         | 0.25 |  |  |  |

| D          | 1.85             | 2.00      | 2.20 |  |  |  |

| е          | C                | .65 BS    | С    |  |  |  |

| е1         | 1                | 1.30 BS   | С    |  |  |  |

| Ε          | 1.80             | 2.10      | 2.40 |  |  |  |

| E1         | 1.15             | 1.25      | 1.35 |  |  |  |

| L          | 0.10             | ı         | 0.45 |  |  |  |

| L1         | O                | 0.42 REF. |      |  |  |  |

| 75         | C                | 0.20 BS0  |      |  |  |  |

| θ          | 0°               | 4°        | 30°  |  |  |  |

| <b>0</b> 1 | 4°               | -         | 12°  |  |  |  |

| aaa        |                  | 0.10      |      |  |  |  |

| bbb        |                  | 0.10      |      |  |  |  |

300mA Ultra-low Noise, Ultra-Fast

CMOS LDO Regulator

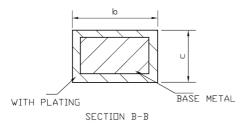

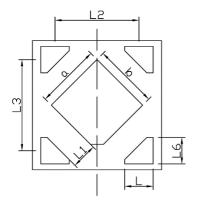

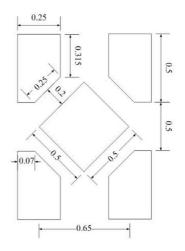

### DFN1×1-4L

There may be slight differences in shape

| Dimensions In<br>Millimeterer |       |       |       |  |  |  |

|-------------------------------|-------|-------|-------|--|--|--|

| Symbol                        | MIN   | TYP   | MAX   |  |  |  |

| Α                             | 0.950 | 1.000 | 1.050 |  |  |  |

| В                             | 0.950 | 1.000 | 1.050 |  |  |  |

| С                             | 0.320 | 0.370 | 0.420 |  |  |  |

| L                             | 0.170 | 0.220 | 0.270 |  |  |  |

| L1                            | 0.140 | 0.190 | 0.240 |  |  |  |

| L2                            | 0.600 | 0.650 | 0.700 |  |  |  |

| L3                            | 0.625 | 0.675 | 0.725 |  |  |  |

| L6                            | 0.175 | 0.225 | 0.275 |  |  |  |

| ۵                             | 0.440 | 0.490 | 0.540 |  |  |  |

| ۵                             | 0.440 | 0.490 | 0.540 |  |  |  |

RECOMMENDED LAND PATTERN (Unit: mm)

300mA Ultra-low Noise, Ultra-Fast

CMOS LDO Regulator

0 to 0.1

0.2 MIN.

### **SOT23-3**

## 单击下面可查看定价,库存,交付和生命周期等信息

>>BELLING(上海贝岭)