#### LCD Driver for 76 Display Units BL55028

#### 1 General Description

The BL55028 is a general LCD driver IC for 76 units LCD panel. It features a wide operating supply voltage range, incorporates simple communication interface with microcomputer and is suitable for multiple application.

#### 2 Features

- Advanced low power CMOS Technology

- Selection of 1/2 or 1/3 bias, selection of 1/2 or 1/3 or 1/4 duty.

- Operation voltage: 2.5~5.5V

- Serial data interface

- 76(19x4) Display Units

- Low power dissipation design: Power saving mode: Idd=14uA at 5V and Idd=9uA at 3.3V;

- On-chip RC oscillator

- VLCD for adjusting LCD operating voltage

- Excellent EMC immunity

- Compatible with general microcomputer

- SOP28 package

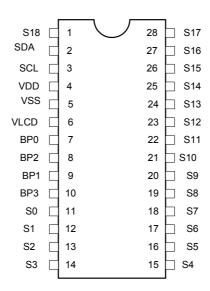

#### 3 Pin Assignment

Fig 1

#### BL55028

Shanghai Belling Corp., Ltd

zip: 200233 Tel: 86-021-64850700 Fax: 86-021-64855865

#### 4 Pin Description

| Pin No. | Pin name               | Function                        |  |  |

|---------|------------------------|---------------------------------|--|--|

| 2       | SDA                    | Serial data input/output        |  |  |

| 3       | SCI                    | Serial clock input              |  |  |

| 4       | Vdd                    | Supply voltage                  |  |  |

| 5       | Vss                    | ground                          |  |  |

| 6       | Vlcd                   | LCD supply voltage              |  |  |

| 7-10    | Com0, Com2, Com1, Com3 | Common terminal driving output  |  |  |

| 11-28、1 | S0S18                  | Segment terminal driving output |  |  |

Tab.1

#### **5 Function Description**

#### 1. function circuit

The BL550028 has all function circuits that can directly drive any static or multiplexed LCD containing up to four commons and up to 19 segments. The function circuits include:Power-on reset, LCD bias generator, LCD voltage selector, Oscillator, display RAM, Timing, Display latch, Shift register, Common/segment outputs, input/output bank selector, Blinker, Data pointer, etc.

#### 2. display function decription

The display RAM is a static 19x 4-bit RAM which stores LCD data. A logic 1 in the RAM bit-map indicates the on state of the corresponding LCD segment; similarly, a logic 0 indicates the off state. There is a one-to-one correspondence between the RAM addresses and the segment outputs, and between the individual bits of a RAM word and the common outputs. (see Fig.2).

| Display RAM address and SEGMENT (SO~S18) output |   |   |   |   |   |   |   |   |   |    |    |    |    |

|-------------------------------------------------|---|---|---|---|---|---|---|---|---|----|----|----|----|

| 6011                                            |   | 0 | 1 | 2 | 3 | 0 | 0 | 0 | 0 | 15 | 16 | 17 | 18 |

| COM<br>(Com0~<br>Com3)<br>输出                    | 0 |   |   |   |   |   |   |   |   |    |    |    |    |

|                                                 | 1 |   |   |   |   |   |   |   |   |    |    |    |    |

|                                                 | 2 |   |   |   |   |   |   |   |   |    |    |    |    |

|                                                 | 3 |   |   |   |   |   |   |   |   |    |    |    |    |

Fig2

When display data is transmitted to the BL55028, the display bytes received are stored in the display RAM in accordance with the selected LCD drive mode. To illustrate the filling order, an example of a 7-segment numeric display showing all drive modes is given in Fig.3; the RAM filling organization depicted applies equally to other LCD types.

#### Shanghai Belling Corp., Ltd

zip: 200233 Tel: 86-021-64850700 Fax: 86-021-64855865

| drive mode         | LCD segments                                           | LCD backplanes | display RAM filling order                                           | transmitted display byte |

|--------------------|--------------------------------------------------------|----------------|---------------------------------------------------------------------|--------------------------|

| static             | S <sub>n</sub> +2                                      |                | n                                                                   | MSB LSB                  |

| 1:2<br>multiplex   | S <sub>n</sub> + 2   0   0   0   0   0   0   0   0   0 | E B            | n n+1 n+2 n+3  bity 0 a f e d  BP 1 b g c DP  2 x x x x x 3 x x x x | MSB LSB                  |

| 1:3<br>multiplex   | S <sub>n</sub> +1                                      | BP0 BF2        | n n+1 n+2  bit 0 b a f BP 1 DP d e 2 c g x 3 x x x                  | MSB LSB                  |

| 1 : 4<br>multiplex |                                                        | BP1 BP2        | n n+1  bity 0 a f BP 1 c e 2 b g 3 DP d                             | MSB LSB                  |

x = data bit unchanged.

Fig 3

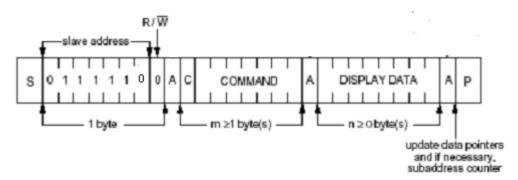

#### 3. I<sup>2</sup>C-bus protocol

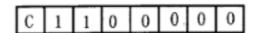

I<sup>2</sup>C-bus slave addresses (0111110) are reserved for the BL55028

The I2C-bus protocol is shown in Fig.4. The sequence is initiated with a START condition (S) from the I2C-bus master which is followed by the BL55028 slave addresses available. After acknowledgement, one or more command bytes (m) follow which define the status of the addressed BL55028. The last command byte is tagged with a cleared most significant bit, the continuation bit C. The command bytes are also acknowledged by the addressed BL55028 on the bus. After the last command byte, a series of display data bytes(n) may follow. These display bytes are stored in the display RAM at the address specified by the data pointer. Data pointer are automatically updated and the data is directed to the intended BL55028 device. After the last display byte, the I2C-bus master issues a STOP condition (P).

Fig 4

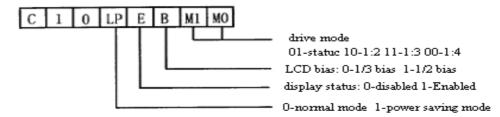

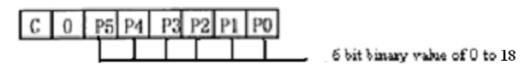

#### 4. command decoder

The command decoder identifies command bytes that arrive on the I<sup>2</sup>C-bus. All available commands carry a continuation bit C in their most significant bit position. The four commands available to the BL55028 are defined in Fig 5.

#### A. Mode set

#### B. Load data pointer

#### C. Blink control

#### D. Device select

Fig 5

**Shanghai Belling Corp., Ltd** zip: 200233 Tel: 86-021-64850700 Fax: 86-021-64855865

### 6 Absolute Maximum Rating

| Parameter                 | Symbol       | Rating            | Unit |

|---------------------------|--------------|-------------------|------|

| Supply voltage            | Vdd          | -0.5~+6.0         | V    |

| LCD operating voltage     | Vlcd         | 0∼ Vdd            | V    |

| Input voltage             | Vi           | Vss-0.5~Vdd+0.5   | V    |

| Output voltage            | Vo           | Vlcd-0.5~Vdd+0.5  | V    |

| Vdd,Vss,Vlcd current      | Idd,Iss,Ilcd | <b>-</b> 50∼+50   | mA   |

| Maximum power consumption | Ptot         | 400               | mW   |

| Operating temperature     | Topr         | <b>-40</b> ∼ +75  | °C   |

| Storage temperature       | Tstg         | <b>-</b> 65∼ +150 | °C   |

#### DC Characteristic

| Symbol | Parameter             | <b>Test Condition</b>                                     | Min    | Тур | Max    | Unit |

|--------|-----------------------|-----------------------------------------------------------|--------|-----|--------|------|

| Vdd    | IC Operating voltage  |                                                           | 2.5    | -   | 5.5    | V    |

| Vlcd   | LCD operating voltage |                                                           | 0      | -   | Vdd-2  | V    |

| Idd1   | Supply current        | Vdd=5V, VLCD=0V, Normal<br>mode, internal oscillator      | -      | 25  | 50     | uA   |

| Idd2   | Supply current        | Vdd=5V, VLCD=0V, power saving mode, internal oscillator   | -      | 14  | 30     | uA   |

| Idd3   | Supply current        | Vdd=3.3V, VLCD=0V, Normal mode, internal oscillator       | -      | 16  | 30     | uA   |

| Idd4   | Supply current        | Vdd=3.3V, VLCD=0V, power saving mode, internal oscillator | -      | 9   | 15     | uA   |

| ViL    | Low voltage input     | SDA,SCL                                                   | Vss    | -   | 0.3Vdd | V    |

| ViH    | High voltage input    | SDA,SCL                                                   | 0.7Vdd | -   | 6.0    | V    |

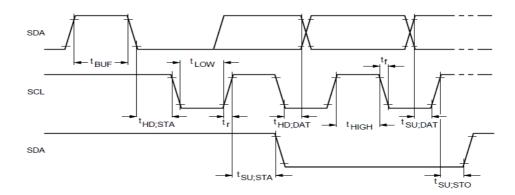

#### AC Characteristic 8

| $T_{c}$ | <u></u> _ | 50 | $\boldsymbol{C}$ |

|---------|-----------|----|------------------|

| 12      | I — /.    | ,  | ι.               |

| Symbol  | Parameter            | <b>Test Condition</b>       | Min | Тур | Max | Unit |

|---------|----------------------|-----------------------------|-----|-----|-----|------|

| Fclk    | Oscillator frequency | Vdd=5V,normal mode          | 125 | 180 | 300 | KHz  |

| Fclklp  | Oscillator frequency | Vdd=3.3V, power saving mode | 21  | 31  | 48  | KHz  |

| Tclkh   | CLK HIGH time        |                             | 1   | -   | -   | us   |

| Telkl   | CLK LOW time         |                             | 1   | -   | -   | us   |

| TBUF    | Bus free time        |                             | 4.7 | -   | -   | us   |

| Thd;STA | START hold time      |                             | 4   | -   | -   | us   |

| Tlow    | SCL LOW time         |                             | 4.7 | -   | -   | us   |

| Thigh   | SCL HIGH time        |                             | 4   | -   | -   | us   |

| Tsu;STA | START set-up time    |                             | 4.7 | -   | -   | us   |

| Thd;DAT | Data hold time       |                             | 0   | -   | -   | us   |

| Tsu;DAT | Data set-up time     |                             | 250 | -   | -   | ns   |

| Tr      | Rise time            |                             | -   | -   | 1   | us   |

| Tf      | fall time            |                             | -   | -   | 300 | ns   |

| Tsu;STO | STOP set-up time     |                             | 4.7 | -   | -   | us   |

Fig 6

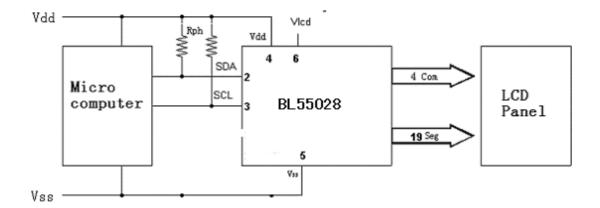

#### 9 Typical Application Circuit

Note:1/ when I<sup>2</sup>C are idle mode,SDA and SCL must be connect to high level(by pull up resistor),otherwise the device maybe can not go into power saving mode.

- 2/ In power-saving mode, SCL frequency must be less than 21KHz.

- 3/ Work at 1/3 bias, Vdd Vlcd must be more than  $2.9V_{\bullet}$

Fig 7

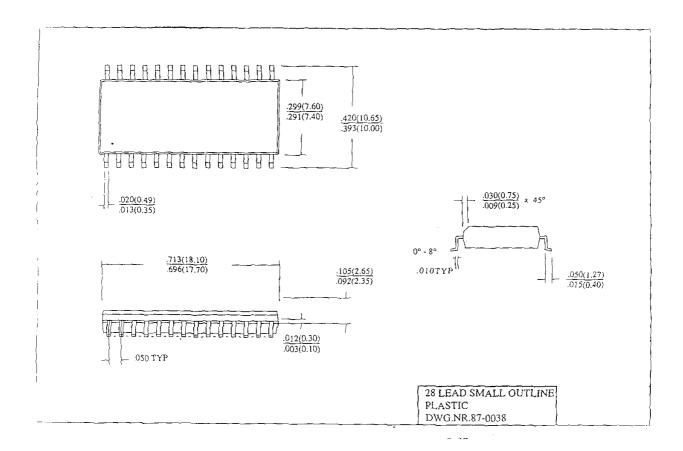

# 10 Package Outline SOP28 Unit: inches (mm)

Fig 8

## 单击下面可查看定价,库存,交付和生命周期等信息

>>BELLING(上海贝岭)