# TISP8200M, BUFFERED P-GATE SCR DUAL TISP8201M, BUFFERED N-GATE SCR DUAL

### COMPLEMENTARY BUFFERED-GATE SCRS FOR DUAL POLARITY SLIC OVERVOLTAGE PROTECTION

# TISP8200M & TISP8201M

High Performance Protection for SLICs with +ve & -ve Battery Supplies

TISP8200M, Negative Overvoltage Protector

- Wide 0 to -90 V Programming Range

- Low 5 mA max. Gate Triggering Current

- High -150 mA min. Holding Current

TISP8201M, Positive Overvoltage Protector

- Wide 0 to +90 V Programming Range

- Low -5 mA max. Gate Triggering Current

- 20 mA min. Holding Current

**Rated for International Surge Wave Shapes**

| Wave Shape | Standard                | I <sub>tsp</sub><br>A |

|------------|-------------------------|-----------------------|

| 2/10 µs    | Telcordia GR-1089-CORE  | 210                   |

| 10/700 μs  | ITU-T K.20, K.21 & K.45 | 70                    |

| 10/1000 µs | Telcordia GR-1089-CORE  | 45                    |

### Surface Mount Small-Outline Package

### Description

The TISP8200M/TISP8201M combination has been designed to protect dual polarity supply rail monolithic SLICs (Subscriber Line Interface Circuits) against overvoltages on the telephone line caused by lightning, a.c. power contact and induction. Protection against negative overvoltages is given by the TISP8200M. Protection against positive overvoltages is given by the TISP8201M. Both parts are in 8-pin small-outline surface mount packages.

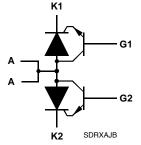

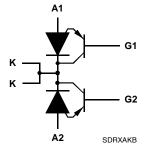

The TISP8200M has an array of two buffered P-gate SCRs with a common anode connection. Each SCR cathode and gate has a separate terminal connection. The NPN buffer transistors reduce the gate supply current.

In use, the cathodes of the TISP8200M SCRs are connected to the two conductors of the POTS line (see applications information). The gates are connected to the appropriate negative voltage battery feed of the SLIC driving the line conductor pair. This ensures that the TISP8200M protection voltage tracks the SLIC negative supply voltage. The anode of the TISP8200M is connected to the SLIC common.

WARNING Cancer and Reproductive Harm www.P65Warnings.ca.gov

MAY 1998 – REVISED JULY 2019 \*RoHS Directive 2015/863, Mar 31, 2015 and Annex. Specifications are subject to change without notice. Users should verify actual device performance in their specific applications. The products described herein and this document are subject to specific legal disclaimers as set forth on the last page of this document, and at www.bourns.com/docs/legal/disclaimer.pdf.

### **Additional Information**

Click these links for more information:

#### **Agency Recognition**

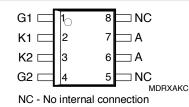

### TISP8200M D Package (Top View)

### **TISP8200M Device Symbol**

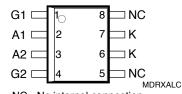

#### TISP8201M D Package (Top View)

### NC - No internal connection

### **TISP8201M Device Symbol**

# BOURNS

#### Description

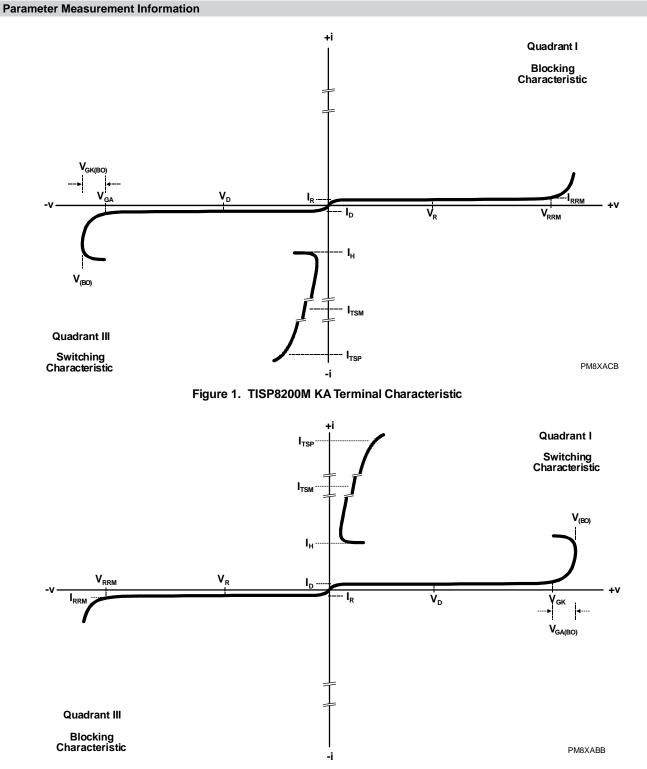

Negative overvoltages are initially clipped close to the SLIC negative supply by emitter follower action of the NPN buffer transistor. If sufficient clipping current flows, the SCR will regenerate and switch into a low voltage on-state condition. As the overvoltage subsides, the high holding current of the SCR helps prevent d.c. latchup.

The TISP8201M has an array of two buffered N-gate SCRs with a common cathode connection. Each SCR anode and gate has a separate terminal connection. The PNP buffer transistors reduce the gate supply current.

In use, the anodes of the TISP8201M SCRs are connected to the two conductors of the POTS line (see applications information). The gates are connected to the appropriate positive voltage battery feed of the SLIC driving that line pair. This ensures that the TISP8201M protection voltage tracks the SLIC positive supply voltage. The cathode of the TISP8201M is connected to the SLIC common.

Positive overvoltages are initially clipped close to the SLIC positive supply by emitter follower action of the PNP buffer transistor. If sufficient clipping current flows, the SCR will regenerate and switch into a low voltage on-state condition. As the overvoltage subsides, the SLIC pulls the conductor voltage down to its normal negative value and this commutates the conducting SCR into a reverse biassed condition.

#### How to Order

| Device    | Package Carrier         |                      | Order As      |

|-----------|-------------------------|----------------------|---------------|

| TISP8200M | D (8-pin Small-Outline) | Embossed Tape Reeled | TISP8200MDR-S |

| TISP8201M | D (8-pin Small-Outline) | Embossed Tape Reeled | TISP8201MDR-S |

### Absolute Maximum Ratings for TISP8200M, T<sub>A</sub> = 25 °C (Unless Otherwise Noted)

| Rating                                                                                      | Symbol           | Value       | Unit |  |

|---------------------------------------------------------------------------------------------|------------------|-------------|------|--|

| Repetitive peak off-state voltage, TISP8200M V <sub>GK</sub> = 0                            | V <sub>DRM</sub> | -120        | V    |  |

| Repetitive peak reverse voltage, V <sub>GA</sub> = -70 V                                    | V <sub>RRM</sub> | 120         | V    |  |

| Non-repetitive peak on-state pulse current, (see Notes 1 and 2)                             |                  |             |      |  |

| 10/1000 $\mu$ s (Telcordia/Bellcore GR-1089-CORE, Issue 2, February 1999, Section 4)        |                  | -45         |      |  |

| 5/310 $\mu$ s (ITU-T K.20, K.21& K.45, K.44 open-circuit voltage wave shape 10/700 $\mu$ s) | ITSP             | -70         | A    |  |

| 2/10 $\mu$ s (Telcordia/Bellcore GR-1089-CORE, Issue 2, February 1999, Section 4)           |                  | -210        | l    |  |

| Non-repetitive peak on-state current, 50/60 Hz (see Notes 1, 2 and 3)                       |                  |             |      |  |

| 100 ms                                                                                      |                  | -11         |      |  |

| 1 s                                                                                         |                  | -6.5        | A    |  |

| 5 s                                                                                         | ITSM             | -3.4        |      |  |

| 300 s                                                                                       |                  | -1.4        |      |  |

| 900 s                                                                                       |                  | -1.3        |      |  |

| Non-repetitive peak gate current, 2/10 $\mu$ s pulse, cathode commoned (see Note 1)         | I <sub>GSM</sub> | 10          | Α    |  |

| Junction temperature                                                                        | TJ               | -55 to +150 | °C   |  |

| Storage temperature range                                                                   | T <sub>stg</sub> | -65 to +150 | °C   |  |

NOTES: 1. Initially, the protector must be in thermal equilibrium with -40 °C ≤ T<sub>J</sub> ≤ 85 °C. The surge may be repeated after the device returns to its initial conditions.

2. These non-repetitive rated currents are peak values. The rated current values may be applied to any cathode-anode terminal pair. Above 85 °C, derate linearly to zero at 150 °C lead temperature.

3. These non-repetitive rated terminal currents are for the TISP8200M and TISP8201M together. Device (A) terminal positive current values are conducted by the TISP8201M and (K) terminal negative current values by the TISP8200M.

Specifications are subject to change without notice.

```

Users should verify actual device performance in their specific applications.

```

# BOURNS

### Absolute Maximum Ratings for TISP8201M, T<sub>A</sub> = 25 °C (Unless Otherwise Noted)

| Rating                                                                                       | Symbol           | Value       | Unit |  |

|----------------------------------------------------------------------------------------------|------------------|-------------|------|--|

| Repetitive peak off-state voltage, $V_{GA} = 0$                                              | V <sub>DRM</sub> | 120         | V    |  |

| Repetitive peak reverse voltage, V <sub>GK</sub> = 70 V                                      | V <sub>RRM</sub> | -120        | V    |  |

| Non-repetitive peak on-state pulse current, (see Notes 1 and 2)                              |                  |             |      |  |

| 10/1000 $\mu$ s (Telcordia (Bellcore) GR-1089-CORE, Issue 2, February 1999, Section 4)       |                  | 45          |      |  |

| 5/310 $\mu s$ (ITU-T K.20, K.21& K.45, K.44 open-circuit voltage wave shape 10/700 $\mu s$ ) | ITSP             | 70          | A    |  |

| $2/10\mu s$ (Telcordia (Bellcore) GR-1089-CORE, Issue 2, February 1999, Section 4)           |                  | 210         | l    |  |

| Non-repetitive peak on-state current, 50/60 Hz (see Notes 1, 2 and 3)                        |                  |             |      |  |

| 100 ms                                                                                       | I <sub>TSM</sub> | 11          |      |  |

| 1s                                                                                           |                  | 6.5         | А    |  |

| 5 s                                                                                          |                  | 3.4         | ~    |  |

| 300 s                                                                                        |                  | 1.4         |      |  |

| 900 s                                                                                        |                  | 1.3         |      |  |

| Non-repetitive peak gate current, 2/10 $\mu$ s pulse, cathode commoned (see Note 1)          | I <sub>GSM</sub> | -10         | А    |  |

| Junction temperature                                                                         | ТJ               | -55 to +150 | °C   |  |

| Storage temperature range                                                                    | T <sub>stg</sub> | -65 to +150 | °C   |  |

NOTES: 1. Initially, the protector must be in thermal equilibrium with -40 °C ≤ T<sub>J</sub> ≤ 85 °C. The surge may be repeated after the device returns to its initial conditions.

2. These non-repetitive rated currents are peak values. The rated current values may be applied to any cathode-anode terminal pair. Above 85 °C, derate linearly to zero at 150 °C lead temperature.

3. These non-repetitive rated terminal currents are for the TISP8200M and TISP8201M together. Device (A) terminal positive current values are conducted by the TISP8201M and (K) terminal negative current values by the TISP8200M.

### **Recommended Operating Conditions**

|         | See Figure 10                                                                               |     |     |  | Unit |

|---------|---------------------------------------------------------------------------------------------|-----|-----|--|------|

| C1, C2  | Gate decoupling capacitor                                                                   | 100 | 220 |  | nF   |

| R1, R2  | Series resistance for Telcordia GR-1089-CORE first-level and second-level surge survival    | 15  | 20  |  | 0    |

| n I, nz | Series resistance for ITU-T K.20, K.21 and K.45 coordination with a 400 V primary protector | 10  | 20  |  | 32   |

Specifications are subject to change without notice.

Users should verify actual device performance in their specific applications.

# BOURNS

### Electrical Characteristics for TISP8200M, T<sub>A</sub> = 25 °C (Unless Otherwise Noted)

|                   | Parameter             | Test Conditions                                                                                                     | Test Conditions        |      |     |     |    |

|-------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------|------------------------|------|-----|-----|----|

| 1-                | Off-state current     |                                                                                                                     | $T_J = 0 \ ^{\circ}C$  |      |     | -5  | μA |

| ۱ <sub>D</sub>    | On-state current      | $V_{D} = V_{DRM}, V_{GK} = 0$                                                                                       | T <sub>J</sub> = 85 °C |      |     | -50 | μA |

| 1_                | Reverse current       |                                                                                                                     | T <sub>J</sub> = 0 °C  |      |     | 5   | μA |

| IR                | neverse current       | V <sub>R</sub> = V <sub>RRM</sub> , V <sub>GA</sub> = -70 V                                                         | T <sub>J</sub> = 85 °C |      |     | 50  | μA |

| V <sub>(BO)</sub> | Breakover voltage     | dv/dt = -250 V/ms, Source Resistance = 300 $\Omega$ , V                                                             |                        |      | -82 | V   |    |

| V <sub>(BO)</sub> | Breakover voltage     | 2/10 waveshape, (I <sub>K</sub> ) I <sub>T</sub> = -100 A, di/dt <sub>max.</sub> = -58 A/s, V <sub>GA</sub> = -80 V |                        |      |     | -95 | V  |

| Ι <sub>Η</sub>    | Holding current       | $(I_K)$ $I_T$ = -1 A, di/dt = 1 A/ms, $V_{GA}$ = -80 V                                                              |                        | -150 |     |     | mA |

| I <sub>GT</sub>   | Gate trigger current  | $(I_K) I_T = -5 \text{ A}, t_{p(g)} 20 \mu\text{s}, V_{GA} = -80 \text{ V}$                                         |                        |      | 5   | mA  |    |

|                   |                       | V <sub>D</sub> = 0                                                                                                  |                        |      | 35  |     |    |

| Coff              | Off-state capacitance | e capacitance $f = 1 \text{ MHz}, V_d = 1 \text{ V}, V_{GA} = -80 \text{ V}, (see Note 4)$                          | V <sub>D</sub> = -5 V  |      |     | 20  | pF |

|                   |                       |                                                                                                                     | V <sub>D</sub> = -50 V |      |     | 10  |    |

NOTE 4: These capacitance measurements employ a three terminal capacitance bridge incorporating a guard circuit. The unmeasured device terminals are a.c. connected to the guard terminal of the bridge.

|                   | Parameter             | Test Conditions                                                                                                         | Test Conditions        |     |    |     |    |

|-------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------|-----|----|-----|----|

| 1-                | l Off state summert   |                                                                                                                         | T <sub>J</sub> = 0 °C  |     |    | 5   | μA |

| ۱ <sub>D</sub>    | Off-state current     | $V_{\rm D} = V_{\rm DRM}, V_{\rm GA} = 0$                                                                               | T <sub>J</sub> = 85 °C |     |    | 50  | μA |

| 1-                | Reverse current       | V <sub>B</sub> = V <sub>BBM</sub> , V <sub>GK</sub> = 70 V                                                              | T <sub>J</sub> = 0 °C  |     |    | -5  | μA |

| Ι <sub>R</sub>    | Reverse current       | $v_{\rm R} = v_{\rm RRM}, v_{\rm GK} = 70$ v                                                                            | T <sub>J</sub> = 85 °C |     |    | -50 | μA |

| V <sub>(BO)</sub> | Breakover voltage     | dv/dt = 250 V/ms, Source Resistance = 300 $\Omega$ , V                                                                  |                        |     | 82 | V   |    |

| V <sub>(BO)</sub> | Breakover voltage     | 2/10 waveshape, (I <sub>A</sub> ) I <sub>T</sub> = 100 A, di/dt <sub>max.</sub> = 58 A/ $\mu$ s, V <sub>GK</sub> = 80 V |                        |     |    | 95  | V  |

| Ι <sub>Η</sub>    | Holding current       | (I <sub>A</sub> ) I <sub>T</sub> = 1 A, di/dt = -1 A/ms, V <sub>GK</sub> = 80 V                                         |                        | +20 |    |     | mA |

| I <sub>GT</sub>   | Gate trigger current  | $(I_A) I_T = 5 \text{ A}, t_{p(g)} \ge 20 \mu\text{s}, V_{GK} = 80 \text{ V}$                                           |                        |     | -5 | mA  |    |

|                   |                       | Iff-state capacitance $f = 1 \text{ MHz}, V_d = 1 \text{ V}, V_{GK} = 80 \text{ V}, (see Note 4)$                       | V <sub>D</sub> = 0     |     |    | 35  |    |

| Coff              | Off-state capacitance |                                                                                                                         | V <sub>D</sub> = 5 V   |     |    | 20  | pF |

|                   |                       |                                                                                                                         | V <sub>D</sub> = 50 V  |     |    | 10  |    |

NOTE 4: These capacitance measurements employ a three terminal capacitance bridge incorporating a guard circuit. The unmeasured device terminals are a.c. connected to the guard terminal of the bridge.

### **Thermal Characteristics**

|                  | Parameter                               | Test Conditions                                                                        | Min | Тур | Max | Unit |

|------------------|-----------------------------------------|----------------------------------------------------------------------------------------|-----|-----|-----|------|

| $R_{\theta J A}$ | Junction to free air thermal resistance | $P_{tot} = 0.52 \text{ W}, T_A = 70 ^{\circ}\text{C}, 5 \text{ cm}^2, \text{ FR4 PCB}$ |     |     | 160 | °C/W |

MAY 1998 – REVISED JULY 2019

Specifications are subject to change without notice. Users should verify actual device performance in their specific applications.

BOURNS

Figure 2. TISP8201M AK Terminal Characteristic

MAY 1998 - REVISED JULY 2019

Specifications are subject to change without notice.

Users should verify actual device performance in their specific applications. The products described herein and this document are subject to specific legal disclaimers as set forth on the last page of this document, and at <u>www.bourns.com/docs/legal/disclaimer.pdf</u>.

### BOURNS

### **APPLICATIONS INFORMATION**

#### **Operation of SLICs using Positive and Negative Voltage Supply Rails**

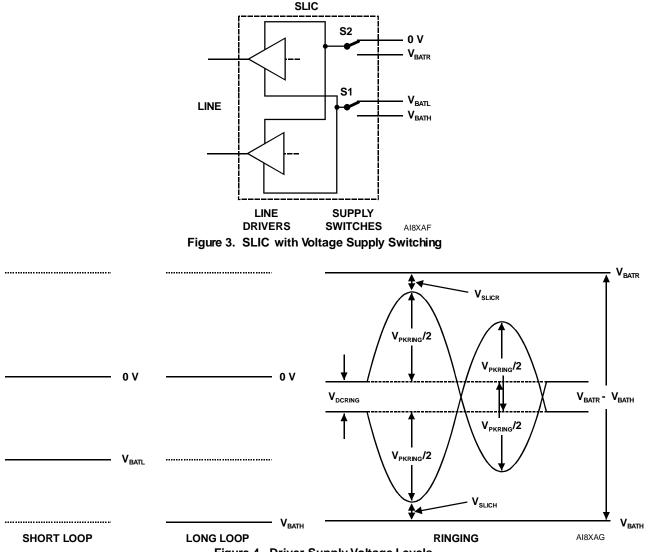

Figure 3 shows a typical powering arrangement for a multi-supply rail SLIC.  $V_{BATR}$  is a positive supply and  $V_{BATL}$  and  $V_{BATH}$  are negative supplies.  $V_{BATH}$  is more negative than  $V_{BATL}$ . With the positive and negative supply switches S2 and S1 in the positions shown, the line driver amplifiers are powered between 0 V and  $V_{BATL}$ . This mode minimizes the power consumption for short loop transmission. For long loops, the driver voltage is increased by operating S1 to connect  $V_{BATH}$ . To generate ringing, S2 is operated to apply  $V_{BATR}$ , powering the drivers from a total supply voltage of  $V_{BATR}$  -  $V_{BATH}$ . These conditions are shown in Figure 4.

Figure 4. Driver Supply Voltage Levels

Conventional ringing is typically unbalanced ground or battery backed. To minimize the supply voltage required, most multi-rail SLICs use balanced ringing as shown in Figure 4. The ringing has d.c.,  $V_{DCRING}$ , and a.c.,  $V_{PKRING}$ , components. A 70 V rms a.c. ring signal has a peak value,  $V_{PKRING}$ , of 99 V. If the d.c. component was 20 V, then the total voltage swing needed would be 99 + 20 = 119 V. There are internal losses in the SLIC from the positive supply,  $V_{SLICR}$ , and the negative supply,  $V_{SLICH}$ . The sum of these two losses generally amounts to a total of 10 V. This makes a total supply rail value of 119 + 10 = 129 V. In practice, the voltage might be distributed as  $V_{BATR}$  = +60 V and  $V_{BATH}$  = -70 V. These values are nominal and some extra voltage should be provided to cover power supply voltage tolerance.

Specifications are subject to change without notice.

Users should verify actual device performance in their specific applications.

# BOURNS

### **SLIC Parameter Values**

The table below shows some details of currently available SLICs using positive and negative supply rails.

| Manufacturer                              |         | INFIN       | IEON‡   |          | LEGE | RITY™‡  | Unit  |

|-------------------------------------------|---------|-------------|---------|----------|------|---------|-------|

| SLIC SERIES                               | SLI     | C-S‡        | SLI     | SLIC-E‡  |      | ISLIC™‡ |       |

| SLIC #                                    | PEB4264 |             | PEI     | PEB 4265 |      | 79R251  |       |

| Data Sheet Issue                          | 14/0    | 7/2000      | 14/0    | 7/2000   | -/08 | /2000   |       |

| Short Circuit Current                     | ±1      | 30          | ±1      | 30       | ±1   | 50      | mA    |

| V <sub>BATH</sub> max.                    | _       | 70          | -       | -90      | -    | 85      | V     |

| V <sub>BATR</sub> max.                    | +       | -50         | -       | +90      | -    | -85     | V     |

| V <sub>BATR</sub> -V <sub>BATH</sub> max. | ę       | 90          |         | 160      | 1    | 150     |       |

| AC Ringing for:                           | 45      |             | 85      |          | 65   |         | V rms |

| V <sub>BATH</sub>                         | -54     |             | -70     |          | -68  |         | V     |

| V <sub>BATR</sub>                         | -       | <b>⊦</b> 36 | +80     |          | +52  |         | V     |

| V <sub>BATR</sub> -V <sub>BATH</sub>      | (       | 90          | 150     |          | 120  |         | V     |

| R or T Power Max. < 10 ms                 | Т       | BA          |         | 10       |      |         | W     |

| R or T Overshoot < 10 ms                  |         |             |         |          | -5   | 5       | V     |

| R or T Overshoot < 1 ms                   | -10     | +10         | -10     | +10      |      |         | V     |

| R or T Overshoot < 10 µs                  | -10     | +30         | -10     | +30      |      |         | V     |

| R or T Overshoot < 1 $\mu$ s              |         |             |         |          | -10  | 10      | V     |

| R or T Overshoot < 250 ns                 |         |             |         |          | -15  | 15      | V     |

| Line Feed Resistance                      | 20      | + 30        | 20 + 30 |          | 50   |         | Ω     |

‡ Legerity, the Legerity logo and ISLIC are the trademarks of Legerity, Inc. (formerly AMD's Communication Products Division). Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

The maximum total voltage,  $V_{BATR} - V_{BATH}$ , is normally about 10 % less than the sum of the maximum  $V_{BATR}$  and maximum  $V_{BATH}$  values. In terms of voltage overshoot, ±10 V is needed for 1  $\mu$ s and ±15 V for 250 ns. It is important to define the protector overshoot under actual circuit conditions. For example, if the series line feed resistor was 20  $\Omega$ , R1 in Figure 10, and Telcordia GR-1089-CORE 2/10 and 10/1000 first level impulses were applied, the peak protector currents would be 100 A and 33 A. Therefore, the protector voltage overshoot should be measured at 100 A, 2/10 and 33 A, 10/1000.

Using the table values for maximum battery voltage and minimum overshoot gives a requirement of  $\pm 105$  V from the output to ground and  $\pm 175$  V between outputs. There needs to be temperature guard banding for the change in protector characteristics with temperature. To cover down to -40 °C, the 25 °C protector minimum values become  $\pm 120$  V referenced to ground,  $\pm 190$  V between outputs and 100 V or -100 V on the gate.

### **Operation of Gated Protectors**

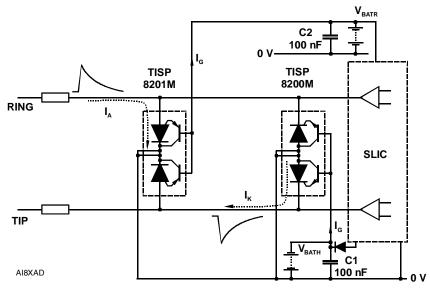

Figure 5 shows how the TISP8200M and TISP8201M limit overvoltages. The TISP8200M SCR sections limit negative overvoltages and the TISP8201M SCR sections limit positive overvoltages.

The TISP8200M (buffered) gate is connected to the negative SLIC battery feed voltage (VBATH) to provide the protection reference voltage. Negative overvoltages are initially clipped close to the SLIC negative supply rail value (VBATH) by the conduction of the TISP8200M transistor base-emitter and the SCR gate-cathode junctions. If sufficient current is available from the overvoltage, then the SCR will crowbar into a low voltage ground referenced on-state condition. As the overvoltage subsides, the high holding current of the SCR prevents d.c. latchup with the SLIC output current.

### BOURNS

### **Operation of Gated Protectors (Continued)**

Figure 5. Overvoltage Conditions

The negative protection voltage,  $V_{(BO)}$ , will be the sum of the gate supply ( $V_{BATH}$ ) and the TISP8200M peak gate(terminal)-cathode voltage ( $V_{GT}$ ). Under a.c. overvoltage conditions  $V_{GT}$  will be less than 2.0 V. The integrated transistor buffer in the TISP8200M greatly reduces protector's source and sink current loading on the  $V_{BATH}$  supply. Without the transistor, the SCR gate current would charge the  $V_{BATH}$  supply. An electronic power supply is not usually designed to be charged like a battery. As a result, the electronic supply would switch off and the SCR gate current would provide the SLIC supply current. Normally the SLIC current would be less than the gate current, which would cause the supply voltage to increase and destroy the SLIC by a supply overvoltage. Older designs using just SCRs needed to incorporate a sacrificial zener diode across the supply line to go short if the supply voltage increased too much. The integrated transistor buffer removes the charging problem and the need for a safety zener.

Fast rising impulses will cause short term overshoots in gate-cathode voltage. The negative protection voltage under impulse conditions will also be increased if there is a long connection between the gate decoupling capacitor, C1, and the gate terminal. During the initial rise of a fast impulse, the gate current (IG) is the same as the cathode current (I<sub>K</sub>). Rates of 60 A/ $\mu$ s can cause inductive voltages of 0.6 V in 2.5 cm of printed wiring track. To minimize this inductive voltage increase of protection voltage, the length of the capacitor to gate terminal tracking should be minimized.

The TISP8201M (buffered) gate is connected to the positive SLIC battery feed voltage ( $V_{BATR}$ ) to provide the protection reference voltage. Positive overvoltages are initially clipped close to the SLIC positive supply rail value ( $V_{BATR}$ ) by the conduction of the TISP8201M transistor base-emitter and the SCR gate-anode junctions. If sufficient current is available from the overvoltage, then the SCR will crowbar into a low voltage ground referenced on-state condition. As the overvoltage subsides the SLIC pulls the conductor voltage down to its normal negative value and this commutates the conducting SCR into a reverse biassed condition.

#### Voltage Stress Levels on the TISP8200M and TISP8201M

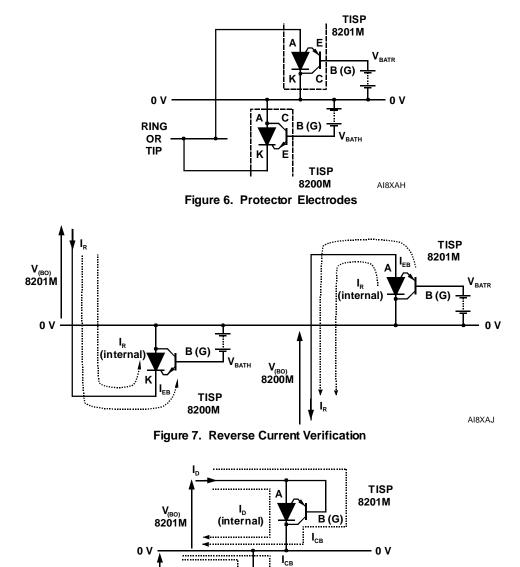

Figure 6 shows the protector electrodes. The package terminal designated gate, G, is the transistor base, B, electrode connection and so is marked as B (G). The following junctions are subject to voltage stress: Transistor EB and CB, SCR AK (reverse and off state). This clause covers the necessary testing to ensure the junctions are good.

Testing transistor EB and SCR AK reverse: The highest reverse EB voltage and reverse AK voltage occurs during the overshoot period of the other protector. For the TISP8200M, the SCR has  $V_{BATR}$  plus the TISP8201M overshoot above  $V_{BATR}$ . The transistor EB has an additional  $V_{BATH}$  voltage applied (see Figure 7). The reverse current, IR, flowing into the K terminal will be the sum of the transistor IEB and the actual internal SCR IR. The reverse voltage applied to the K terminal is the TISP8201M protection voltage,  $V_{(BO)}$  ( $V_{BATR}$  plus overshoot), and the G terminal has  $V_{BATH}$ . Similarly for the TISP8201M, IR is measured with the TISP8200M  $V_{(BO)}$  applied and it is the sum of the transistor IEB and the actual internal SCR IR.

### BOURNS

#### Voltage Stress Levels on the TISP8200M and TISP8201M (Continued)

Testing transistor CB and SCR AK off state: The highest AK voltage occurs during the overshoot period of the protector. To make sure that the SCR blocking junction does not break down during this period, a d.c. test for off-state current can be applied at the overshoot voltage value. To avoid transistor CB current amplification by the transistor gain, the transistor base-emitter is shorted during this test (see Figure 8).

Summary: Two tests are needed to verify the protector junctions. Maximum current values for IR and ID are required.

MAY 1998 - REVISED JULY 2019

Specifications are subject to change without notice. Users should verify actual device performance in their specific applications.

V<sub>(BO)</sub>

8200M

(internal)

The products described herein and this document are subject to specific leaal disclaimers as set forth on the last page of this document, and at www.bourns.com/docs/legal/disclaimer.pdf.

Figure 8. Off-State Current Verification

B (G)

TISP 8200M

AI8XAK

### TISP8200M and TISP8201M Voltage Overwhoot

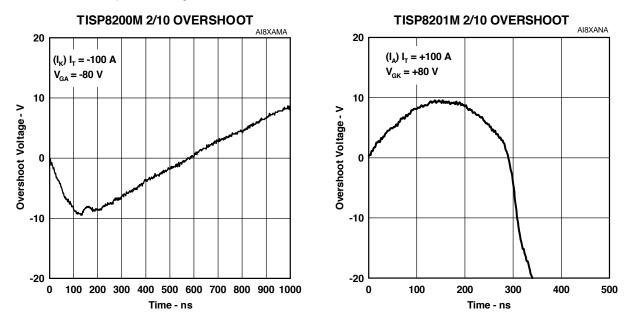

Figure 9 shows typical overshoots on a 100 A 2/10 waveshape. Both devices are under 10 V peak, which meets the needs of the SLICs listed earlier.

BOURNS

### Line Protection with TISP8200M and TISP8201M

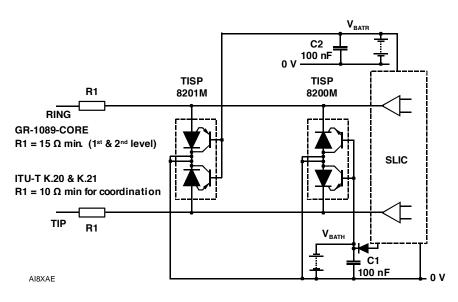

Figure 10 shows a typical circuit for single line protection using one TISP8200M and one TISP8201M. The series resistor values limit the test impulse currents to within the protector ratings.

Figure 9. Voltage Overshoot Referenced to Gate Bias Voltage

Figure 10. Line Protection with TISP8200M and TISP8201M

MAY 1998 – REVISED JULY 2019 Specifications are subject to change without notice.

Users should verify actual device performance in their specific applications.

### BOURNS

### **MECHANICAL DATA**

### **Device Symbolization Code**

Devices are coded as below.

| Device    | Symbolization |

|-----------|---------------|

| TISP8200M | 8200M         |

| TISP8201M | 8201M         |

Asia-Pacific: Tel: +886-2 2562-4117 • Email: asiacus@bourns.com EMEA: Tel: +36 88 885 877 • Email: eurocus@bourns.com The Americas: Tel: +1-951 781-5500 • Email: americus@bourns.com www.bourns.com

"TISP" is a trademark of Bourns, Ltd., a Bourns Company, and is Registered in the U.S. Patent and Trademark Office. "Bourns" is a registered trademark of Bourns, Inc. in the U.S. and other countries.

MAY 1998 – REVISED JULY 2019 Specifications are subject to change without notice. Users should verify actual device performance in their specific applications. The products described herein and this document are subject to specific leaal disclaimers as set forth on the last page of this document, and at <u>www.bourns.com/docs/legal/disclaimer.pdf</u>.

### **Legal Disclaimer Notice**

This legal disclaimer applies to purchasers and users of Bourns<sup>®</sup> products manufactured by or on behalf of Bourns, Inc. and its affiliates (collectively, "Bourns").

Unless otherwise expressly indicated in writing, Bourns<sup>®</sup> products and data sheets relating thereto are subject to change without notice. Users should check for and obtain the latest relevant information and verify that such information is current and complete before placing orders for Bourns<sup>®</sup> products.

The characteristics and parameters of a Bourns<sup>®</sup> product set forth in its data sheet are based on laboratory conditions, and statements regarding the suitability of products for certain types of applications are based on Bourns' knowledge of typical requirements in generic applications. The characteristics and parameters of a Bourns<sup>®</sup> product in a user application may vary from the data sheet characteristics and parameters due to (i) the combination of the Bourns<sup>®</sup> product with other components in the user's application, or (ii) the environment of the user application itself. The characteristics and parameters of a Bourns<sup>®</sup> product also can and do vary in different applications and actual performance may vary over time. Users should always verify the actual performance of the Bourns<sup>®</sup> product in their specific devices and applications, and make their own independent judgments regarding the amount of additional test margin to design into their device or application to compensate for differences between laboratory and real world conditions.

Unless Bourns has explicitly designated an individual Bourns<sup>®</sup> product as meeting the requirements of a particular industry standard (e.g., ISO/TS 16949) or a particular qualification (e.g., UL listed or recognized), Bourns is not responsible for any failure of an individual Bourns<sup>®</sup> product to meet the requirements of such industry standard or particular qualification. Users of Bourns<sup>®</sup> products are responsible for ensuring compliance with safety-related requirements and standards applicable to their devices or applications.

Bourns<sup>®</sup> products are not recommended, authorized or intended for use in nuclear, lifesaving, life-critical or life-sustaining applications, nor in any other applications where failure or malfunction may result in personal injury, death, or severe property or environmental damage. Unless expressly and specifically approved in writing by two authorized Bourns representatives on a case-by-case basis, use of any Bourns<sup>®</sup> products in such unauthorized applications might not be safe and thus is at the user's sole risk. Life-critical applications include devices identified by the U.S. Food and Drug Administration as Class III devices and generally equivalent classifications outside of the United States.

Bourns expressly identifies those Bourns<sup>®</sup> standard products that are suitable for use in automotive applications on such products' data sheets in the section entitled "Applications." Unless expressly and specifically approved in writing by two authorized Bourns representatives on a case-by-case basis, use of any other Bourns<sup>®</sup> standard products in an automotive application might not be safe and thus is not recommended, authorized or intended and is at the user's sole risk. If Bourns expressly identifies a sub-category of automotive application in the data sheet for its standard products (such as infotainment or lighting), such identification means that Bourns has reviewed its standard product and has determined that if such Bourns<sup>®</sup> standard product is considered for potential use in automotive applications, it should only be used in such sub-category of automotive applications, it should only be used in such sub-category of automotive applications product in the data sheet as compliant with the AEC-Q standard or "automotive grade" does not by itself mean that Bourns has approved such product for use in an automotive application.

Bourns<sup>®</sup> standard products are not tested to comply with United States Federal Aviation Administration standards generally or any other generally equivalent governmental organization standard applicable to products designed or manufactured for use in aircraft or space applications. Bourns expressly identifies Bourns<sup>®</sup> standard products that are suitable for use in aircraft or space applications on such products' data sheets in the section entitled "Applications." Unless expressly and specifically approved in writing by two authorized Bourns representatives on a case-by-case basis, use of any other Bourns<sup>®</sup> standard product in an aircraft or space application might not be safe and thus is not recommended, authorized or intended and is at the user's sole risk.

The use and level of testing applicable to Bourns<sup>®</sup> custom products shall be negotiated on a case-by-case basis by Bourns and the user for which such Bourns<sup>®</sup> custom products are specially designed. Absent a written agreement between Bourns and the user regarding the use and level of such testing, the above provisions applicable to Bourns<sup>®</sup> standard products shall also apply to such Bourns<sup>®</sup> custom products.

Users shall not sell, transfer, export or re-export any Bourns<sup>®</sup> products or technology for use in activities which involve the design, development, production, use or stockpiling of nuclear, chemical or biological weapons or missiles, nor shall they use Bourns<sup>®</sup> products or technology in any facility which engages in activities relating to such devices. The foregoing restrictions apply to all uses and applications that violate national or international prohibitions, including embargos or international regulations. Further, Bourns<sup>®</sup> products and Bourns technology and technical data may not under any circumstance be exported or re-exported to countries subject to international sanctions or embargoes. Bourns<sup>®</sup> products may not, without prior authorization from Bourns and/or the U.S. Government, be resold, transferred, or re-exported to any party not eligible to receive U.S. commodities, software, and technical data.

To the maximum extent permitted by applicable law, Bourns disclaims (i) any and all liability for special, punitive, consequential, incidental or indirect damages or lost revenues or lost profits, and (ii) any and all implied warranties, including implied warranties of fitness for particular purpose, non-infringement and merchantability.

For your convenience, copies of this Legal Disclaimer Notice with German, Spanish, Japanese, Traditional Chinese and Simplified Chinese bilingual versions are available at:

Web Page: <u>http://www.bourns.com/legal/disclaimers-terms-and-policies</u> PDF: http://www.bourns.com/docs/Legal/disclaimer.pdf 单击下面可查看定价,库存,交付和生命周期等信息

>>Bourns(伯恩斯)