# **8V to 40V Differential PLC Line Driver**

### Features

- Supply Range: 8V to 40V

- Integrated Common-mode Buffer

- Over Temperature Protection

- Large-Signal Bandwidth

- High Slew Rate

- Wide Output Swing

- Low Distortion

- Low Supply Current:

Full-bias mode: 23mA Mod-bias mode: 18mA Low-bias mode: 16mA Shutdown mode: 0.2mA

### **Applications**

- Smart Meters

- Broadband Power Line Communications

- Broadband Video Line Driver

- Home Networking PLC

- Differential DSL Line Driver

www.cosine-ic.com

### **General Description**

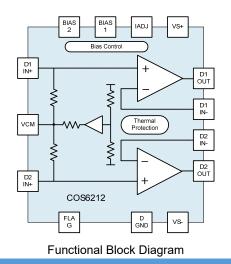

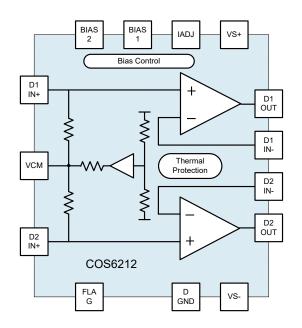

The COS6212 is a differential line-driver amplifier targeted for use in broadband power line communications (PLC) line driver applications that require high linearity while driving heavy line loads.

The integrated mid-supply common-mode buffer eliminates external components, reducing system cost and board space. The amplifier has an adjustable current pin (IADJ) that sets the nominal current consumption along with the multiple bias settings that allow for enhanced power savings where the full performance of the amplifier is not required. Shutdown bias mode provides further power savings during receive mode in time division multiplexed (TDM) systems while maintaining high output impedance.

The wide output swing of 16 Vpp (100 $\Omega$  load) with 12-V power supplies, coupled with over 300-mA current drive (25 $\Omega$  load), allows for wide dynamic range that keeps distortion minimal.

The COS6212 is available in 24-pin QFN5X4-24L and 20-pin QFN4X4-20L package with exposed thermal pad and is specified for operation from -40°C to +125°C ambient temperature.

Rev1.1

Cosine Nanoelectronics

www.cosine-ic.com

The information provided here is believed to be accurate and reliable. Cosine Nanoelectronics assumes no reliability for inaccuracies and omissions. Specifications described and contained here are subjected to change without notice on the purpose of improving the design and performance. All of this information described herein should not be implied or granted for any third party.

Copyright@2020 Cosine Nanoelectronics. All rights reserved

### 1. Overview

The COS6212 is a differential line-driver amplifier targeted for use in broadband power line communications (PLC) line driver applications that require high linearity while driving heavy line loads.

The integrated mid-supply common-mode buffer eliminates external components, reducing system cost and board space. The amplifier has an adjustable current pin (IADJ) that sets the nominal current consumption along with the multiple bias settings that allow for enhanced power savings where the full performance of the amplifier is not required. Shutdown bias mode provides further power savings during receive mode in time division multiplexed (TDM) systems while maintaining high output impedance.

The wide output swing of 16 Vpp (100 $\Omega$  load) with 12-V power supplies, coupled with over 300-mA current drive (25 $\Omega$  load), allows for wide dynamic range that keeps distortion minimal. By using 32-V power supplies and with good thermal design that keep the device within the safe operating temperature, the COS6212 is capable of swinging 58 Vpp into 100- $\Omega$  loads.

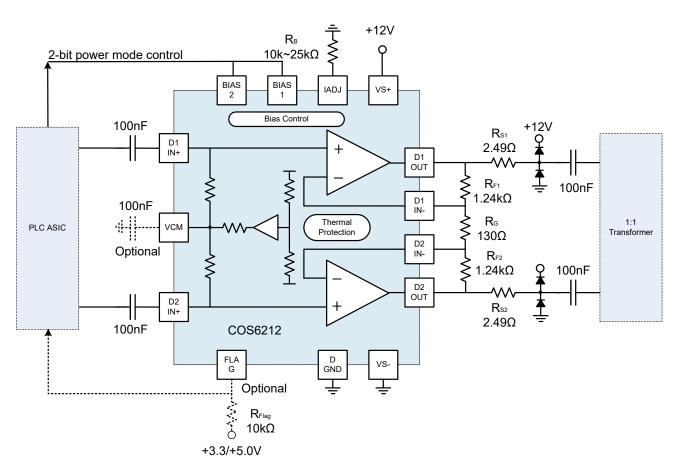

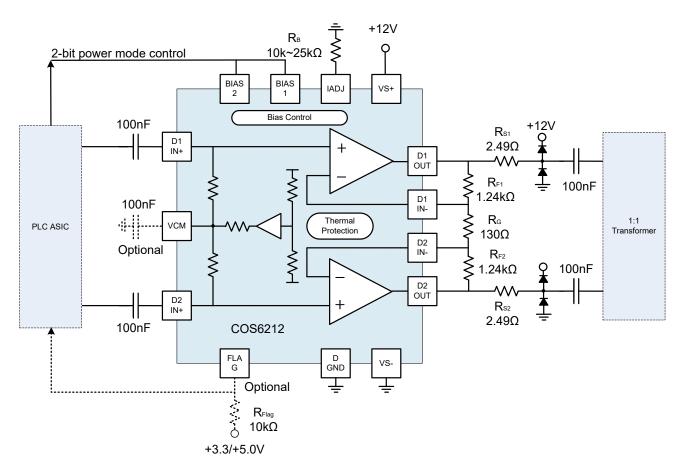

Figure 1. Typical Line Driver Circuit Using the COS6212

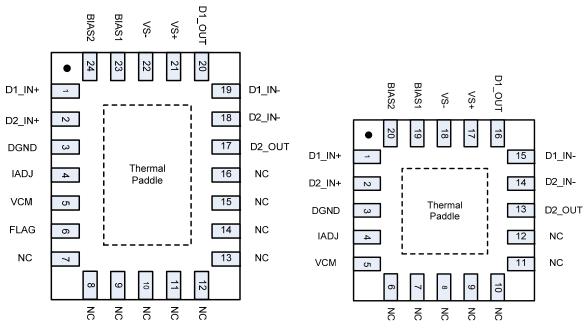

# 2. Pin Configuration and Functions

Figure 2. 24-Pin and 20-Pin QFN with Exposed Thermal Pad (Top View)

| Pin Functions      |                    |          |      |                                                                                          |  |  |

|--------------------|--------------------|----------|------|------------------------------------------------------------------------------------------|--|--|

| Pin No.<br>(QFN24) | Pin No.<br>(QFN20) | Pin Name | Туре | Description                                                                              |  |  |

| 1                  | 1                  | D1_IN+   | I    | Amplifier D1 noninverting input                                                          |  |  |

| 2                  | 2                  | D2_IN+   | I    | Amplifier D2 noninverting input                                                          |  |  |

| 3                  | 3                  | DGND     | I    | Ground reference for bias control pins                                                   |  |  |

| 4                  | 4                  | IADJ     | I    | Bias current adjustment pin (default connect $25k\Omega$ to Vs-)                         |  |  |

| 5                  | 5                  | VCM      | 0    | Common-mode buffer output                                                                |  |  |

| 6                  | -                  | FLAG     | 0    | Active-low error flag output signal that indicates an output fault condition (optional). |  |  |

| 7-16               | 6-12               | NC       | -    | No connection                                                                            |  |  |

| 17                 | 13                 | D2_OUT   | 0    | Amplifier D2 output                                                                      |  |  |

| 18                 | 14                 | D2_IN-   | I    | Amplifier D2 inverting input                                                             |  |  |

| 19                 | 15                 | D1_IN-   | I    | Amplifier D1 inverting input                                                             |  |  |

| 20                 | 16                 | D1_OUT   | 0    | Amplifier D1 output                                                                      |  |  |

| 21                 | 17                 | VS+      | Р    | Positive power-supply connection                                                         |  |  |

| 22                 | 18                 | VS-      | Р    | Negative power-supply connection                                                         |  |  |

| 23                 | 19                 | BIAS-1   | I    | Bias mode control, LSB                                                                   |  |  |

| 24                 | 20                 | BIAS-2   | Ι    | Bias mode control, MSB                                                                   |  |  |

www.cosine-ic.com

| Electrically connected to die substrate and VSThermal PaddlePConnect to VS- on the printed circuit board (PCB)for best performance. |

|-------------------------------------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------|

(1) I = input, O = output, and P = power,

(2) NC = no internal connection.

(3) The COS6212 defaults to the shutdown (disable) state if a signal is not present on the bias pins.

(4) The DGND pin ranges from VS– to (VS+ - 5 V).

# 3. Product Specification

#### 3.1 Absolute Maximum Ratings<sup>(1)</sup>

| Parameter                   | Symbol     | Value      | Units |

|-----------------------------|------------|------------|-------|

| Power Supply                | VS+ to VS- | 44         | V     |

| Storage Temperature Range   | TS         | -65 to 150 | °C    |

| Junction Temperature        | TJ         | 150        | °C    |

| Operating Temperature Range | то         | -40 to 85  | °C    |

| ESD Susceptibility          | HBM        | 5000       | V     |

(1) Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

### 3.2 Thermal Data

| Parameter                                    | Symbol      | Value | Unit  |

|----------------------------------------------|-------------|-------|-------|

| Junction to Ambient Thermal Resistance       | AL $\theta$ | 43.4  | °044/ |

| Junction to Case (Bottom) Thermal Resistance | heta JCbot  | 9.3   | °C/W  |

### **3.3 Recommended Operating Conditions**

| Parameter                     | Symbol         | Value        | Unit |

|-------------------------------|----------------|--------------|------|

| Supply Voltage                | Vs             | 8V ~ 40V     | V    |

| DGND pin voltage              | DGND           | Vs- ~ Vs+ -5 | V    |

| Operating ambient temperature | T <sub>A</sub> | -40 to +85   | °C   |

www.cosine-ic.com

### **3.4 Electrical Characteristics**

$(VS+=+12V, VS=0, T_{A}=+25^{\circ}C, R_{L}=50\Omega, R_{F}=1.24k\Omega, R_{G}=274\Omega, R_{B}=25k\Omega, R_{S}=2.49\Omega, unless otherwise noted)$

| Parameter                               | Symbol             | Conditions                      | Min | Тур   | Max    | Unit   |  |

|-----------------------------------------|--------------------|---------------------------------|-----|-------|--------|--------|--|

| Power Supply                            |                    |                                 |     |       |        |        |  |

| Operating voltage range                 | Vs                 |                                 | 8   | 12    | 40     | V      |  |

| DGND pin voltage                        | DGND               |                                 | Vs- | 0     | Vs+ -5 | V      |  |

|                                         |                    | Full bias<br>(BIAS1=0, BIAS2=0) |     | 23    |        |        |  |

| <b>_</b>                                |                    | Mid bias<br>(BIAS1=1, BIAS2=0)  |     | 18    |        |        |  |

| Power supply quiescent current          | la                 | Low bias<br>(BIAS1=0, BIAS2=1)  |     | 16    |        | mA     |  |

|                                         |                    | Shutdown<br>(BIAS1=1, BIAS2=1)  |     | 0.2   |        |        |  |

| Current through DGND pin                |                    | Full bias<br>(BIAS1=0, BIAS2=0) |     | 0.2   |        | μA     |  |

| + Positive power supply rejection ratio | +PSRR              | Differential                    |     | 90    |        | dB     |  |

| - Negative power supply rejection ratio | -PSRR              | Differential                    |     | 90    |        | dB     |  |

| Bias Control                            |                    |                                 |     |       |        |        |  |

| Bias control pin voltage range          |                    | With respect to DGNG            | 0   | 3.3   | 24     | V      |  |

| Diese een twee wie te wie through a la  |                    | Logic 1, with respect to DGND   | 1.9 |       |        | V      |  |

| Bias control pin logic threshold        |                    | Logic 0, with respect to DGND   |     |       | 0.8    |        |  |

|                                         |                    | BIAS1, BIAS2=0.5V<br>(logic 0)  |     | 10    |        | μA     |  |

| Bias control pin current                |                    | BIAS1, BIAS2=3.3V<br>(logic 1)  |     | 0.26  |        |        |  |

| Open loop output impedance              |                    | Shutdown<br>(BIAS1=1,BIAS2=1)   |     | 70  5 |        | MΩ  pF |  |

| Common-Mode Buffer Chara                | acteristics        | ·1                              |     |       |        |        |  |

| Common-mode offset voltage              | V <sub>CM-OS</sub> |                                 |     | ±5    |        | mV     |  |

| Common-mode output                      |                    | DC-coupled inputs               |     | 520   |        | Ω      |  |

| resistance                              |                    | AC-coupled inputs               |     | 70    |        | Ω      |  |

|                                            |                 |                                                          |         |       | 003 |        |

|--------------------------------------------|-----------------|----------------------------------------------------------|---------|-------|-----|--------|

| DC Performance                             |                 |                                                          |         |       |     |        |

| Open-loop transimpedance gain              | Z <sub>OL</sub> |                                                          |         | 100   |     | kΩ     |

| Input Offset Voltage                       | Vos             | -40 to 85°C                                              |         | ±2    | ±50 | mV     |

| Noninverting Input Bias Current            | I <sub>BP</sub> |                                                          |         | ±1    |     | μA     |

| Inverting Input Bias Current               | I <sub>BN</sub> |                                                          |         | ±2    |     | μA     |

| Input Characteristics                      | I               |                                                          |         |       | 1   |        |

| Common-Mode input Range                    | V <sub>CM</sub> |                                                          |         | ±3    |     | V      |

| Common-Mode Rejection Ratio                | CMRR            |                                                          |         | 70    |     | dB     |

| Noninverting differential input resistance |                 |                                                          |         | 10  2 |     | kΩ  pF |

| Inverting input resistance                 |                 |                                                          |         | 150   |     | Ω      |

| Output Characteristics                     | I               |                                                          | - I - I |       | 1   |        |

|                                            |                 | R∟=100Ω, Rs=0Ω                                           |         | ±8.8  |     | V      |

| Output Voltage Swing                       | Vo              | R∟=50Ω, Rs=0Ω                                            |         | ±8.1  |     | V      |

|                                            |                 | R∟=25Ω, Rs=0Ω                                            |         | ±7.1  |     | V      |

| Output Current<br>(Sourcing and Sinking)   |                 | R <sub>L</sub> =25Ω, Rs=0Ω                               |         | ±284  |     | mA     |

| Short-circuit output current               |                 |                                                          |         | 0.8   |     | А      |

| Dynamic Performance                        |                 |                                                          |         |       |     |        |

| Signal bandwidth                           | BW              | G=5V/V, R <sub>F</sub> =1.5kΩ,<br>Vo=2Vpp                |         | 20    |     | MHz    |

| Slew rate (20% to 80%)                     | SR              | Vo=16Vpp                                                 |         | 500   |     | V/µs   |

| Rise and fall time (10% to 90%)            |                 | Vo=2Vpp                                                  |         | 16    |     | ns     |

|                                            |                 | Vo=4Vpp, R <sub>L</sub> =50Ω,<br>2 <sup>nd</sup> -order, |         | -122  |     | dBc    |

| 1MHz harmonic distortion                   |                 | Vo=4Vpp, $R_L$ =50 $\Omega$ , $3^{rd}$ -order,           |         | -65   |     | dBc    |

|                                            |                 | Vo=4Vpp, RL=50Ω,<br>2 <sup>nd</sup> -order,              |         | -86   |     | dBc    |

| 6MHz harmonic distortion                   |                 | Vo=4Vpp, RL=50Ω,<br>3 <sup>rd</sup> -order,              |         | -56   |     | dBc    |

|                                            | •               | •                                                        |         |       |     | •      |

### 4. Application Notes

### 4.1 Typical Application Circuits

Figure 3. Typical Broadband PLC Configuration

Figure 3 shows a typical ac-coupled broadband PLC application circuit where a current-output digital-to-analog converter (DAC) of the PLC application-specific integrated circuit (ASIC) drives the inputs of the COS6212. Though Figure 1 shows the COS6212 interfacing with a current-output DAC, the COS6212 can just as easily be interfaced with a voltage-output DAC by using much larger terminating resistors,  $R_{T1}$  and  $R_{T2}$ .

The closed-loop gain equation for a differential line driver such as the COS6212 is given as

$$A_V = 1 + 2 \times (R_F / R_G)$$

where  $R_F = R_{F1} = R_{F2}$ . The COS6212 is a current-feedback amplifier and thus the bandwidth of the closed loop configuration is set by the value of the  $R_F$  resistor. This advantage of the current-feedback architecture allows for flexibility in setting the differential gain by choosing the value of the  $R_G$  resistor without reducing the bandwidth as is the case with voltage-feedback amplifiers.

The COS6212 is designed to provide optimal bandwidth performance with  $R_{F1} = R_{F2} = 1.24 \text{ k}\Omega$ . To configure the device in a gain of 20 V/V, the  $R_G$  resistor is chosen to be 130  $\Omega$ . Often, a key requirement for PLC applications is the out-of-band suppression specifications. The in-band frequencies carry the encoded data with a certain power level. The line driver must not generate any spurs beyond a certain power level outside the in-band spectrum. In the design requirements of this application example, the minimum out-of-band suppression specification of 35 dB means there must be no frequency spurs in the out-of-band spectrum beyond the –80-dBm/Hz power spectral density, considering the in-band power spectral density is –50 dBm/Hz.

| R <sub>B</sub> | R <sub>F</sub> | R <sub>G</sub> | Rs     | Ci     | Со     |

|----------------|----------------|----------------|--------|--------|--------|

| 10k~25 kΩ      | 1.24 kΩ        | 130Ω           | 2.49 Ω | 100 nF | 100 nF |

| Table 2. Typical External | Component Value |

|---------------------------|-----------------|

|---------------------------|-----------------|

### 4.2 Common-Mode Buffer

The COS6212 is a differential line driver that features an integrated common-mode buffer. Most common line driving applications for the COS6212 are ac-coupled applications; Therefore, the inputs must be common-mode shifted to ensure the input signals are within the common-mode specifications of the device. To maximize the dynamic range, the common-mode voltage is shifted to mid-supply in most ac-coupled applications. With the integrated common-mode buffer, no external components are required to shift the input common-mode voltage. Often, engineers choose to connect a noise-decoupling capacitor to the VCM pin. However, as shown in the common-mode voltage noise specifications, under the specified conditions and assuming the circuit is shielded from external noise sources, no difference in common-mode noise is observed with the 100-nF capacitor or without the capacitor.

### 4.3 Power Saving Modes

The COS6212 has four different functional modes set by the BIAS-1 and BIAS-2 pins. Table 1 shows the truth table for the device mode pin configuration and the associated description of each mode. If the PLC application requires switching the line driver between all four power modes and if the PLC application specific integrated circuit (ASIC) has two control bits, then the two control bits can be connected to the bias pins BIAS-1 and BIAS-2 for switching between any of the four power modes. However, most PLC applications only require the line driver to switch between one of the three active power modes and the shutdown mode. This type of 1-bit power mode control is illustrated in Figure 3, where the line driver can be switched between the full-bias and shutdown modes using just one control bit from the PLC ASIC. If switching between the mid-bias or low-bias modes and the shutdown mode is required for the application, then either the BIAS-1 or BIAS-2 pin can be connected to ground and the control pin from the PLC ASIC can be connected to the non-grounded BIAS pin.

| BIAS-1 | BIAS-2 | Function                 | Description                                                                      |

|--------|--------|--------------------------|----------------------------------------------------------------------------------|

| 0      | 0      | Full-bias mode<br>(100%) | Amplifiers on with lowest distortion possible (default state)                    |

| 1      | 0      | Mid-bias mode<br>(80%)   | Amplifiers on with power savings and a reduction in distortion performance       |

| 0      | 1      | Low-bias mode<br>(75%)   | Amplifiers on with enhanced power savings and a reduction of overall performance |

| 1      | 1      | Shutdown mode            | Amplifiers off and output is high impedance                                      |

#### Table 1. BIAS-1 and BIAS-2 Logic Table

### **4.4 Thermal Protection**

The COS6212 is designed with thermal protection that automatically puts the device in shutdown mode when the junction temperature reaches approximately 140°C. In this mode, the device behavior is the same as if the bias pins are used to power-down the device. The device resumes normal operation when the junction temperature reaches approximately 120°C. In general, the thermal shutdown condition must be avoided. If and when the thermal protection triggers, thermal cycling occurs where the device repeatedly goes in and out of thermal shutdown until the junction temperature stabilizes to a value that prevents thermal shutdown.

### 4.5 Error Flag

COS6212 feature an Error Flag, which signals an error condition when junction temperature exceed 140°C. The error flag is an open-collector output that pulls low under fault conditions. It can be connected to MCU for selecting an appropriate bias condition or input signal power.

| WWW.CO  | ISINE | ם אורי | nm |

|---------|-------|--------|----|

| WWWW.CC | 01110 | , 10.0 |    |

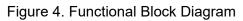

## 5. Package Information

### 5.1 QFN5X4-24L (Package Outline Dimensions)

| Symbol | <b>Dimensions in Millimeters</b> |      |      |  |  |

|--------|----------------------------------|------|------|--|--|

| Symbol | Min.                             | Тур. | Max. |  |  |

| А      | 0.80                             | 0.90 | 1.00 |  |  |

| A1     | 0.00                             | 0.02 | 0.05 |  |  |

| A3     | 0.20Ref                          |      |      |  |  |

| b      | 0.19                             | 0.24 | 0.29 |  |  |

| D      | 4.00BSC                          |      |      |  |  |

| Е      | 5.00BSC                          |      |      |  |  |

| D2     | 2.50                             | 2.65 | 2.75 |  |  |

| E2     | 3.50                             | 3.65 | 3.75 |  |  |

| e      | 0.50BSC                          |      |      |  |  |

| К      | 0.20                             | -    | -    |  |  |

| L      | 0.30                             | 0.40 | 0.50 |  |  |

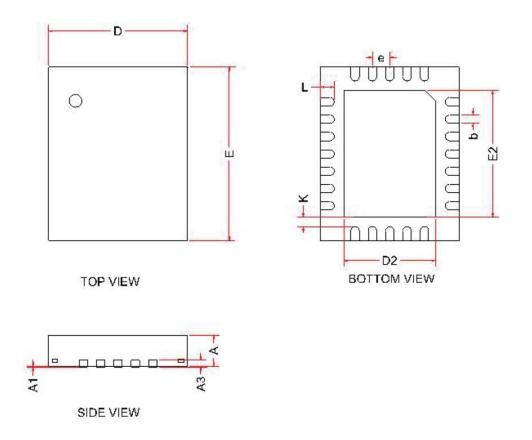

### 5.2 QFN4X4-20L (Package Outline Dimensions)

| DIM<br>Symbol | MIN.    | NDM.     | MAX. |

|---------------|---------|----------|------|

| A             | 0.70    | 0.75     | 0.80 |

|               | 0.85    | 0.90     | 0.95 |

| A1            | 0       | 0.02     | 0.05 |

| A3            | -       | 0.20 REF | -    |

| b             | 0.15    | 0.20     | 0.25 |

| D             | 4.00BSC |          |      |

| E             | 4.00BSC |          |      |

| D2            | 2.60    | 2.70     | 2.80 |

| E2            | 2.60    | 2.70     | 2.80 |

| e             | 0.50BSC |          |      |

| L             | 0.35    | 0.40     | 0.45 |

| К             | 0.20    | -        | -    |

| ممم           | 0.10    |          |      |

| bbb           | 0.07    |          |      |

| CCC           | 0.10    |          |      |

| ddd           | 0.05    |          |      |

| eee           | 0.08    |          |      |

| fff           | 0.10    |          |      |

# 6. Ordering Guide

| Device      | Package    | Package Option      | Marking<br>Information |

|-------------|------------|---------------------|------------------------|

| COS6212Q24R | QFN5X4-24L | Tape and Reel, 3000 | COS6212Q24R            |

| COS6212Q20R | QFN4X4-20L | Tape and Reel, 3000 | COS6212Q20R            |

单击下面可查看定价,库存,交付和生命周期等信息

>>COSINE(科山芯创)