# Low Quiescent Programmable-Delay Supervisory

## **Features**

- → Power-On Reset Generator with Adjustable Delay Time: 1.25ms to 10s.

- → Very Low Quiescent Current: 2.8µA Typical

- → High Threshold Accuracy: 0.5% Typ.

- → Fixed Threshold Voltages for Standard Voltage Rails from 0.9V to 5V and Adjustable Voltage Down to 0.4V are available.

- → Manual Reset ( MR ) Input.

- → Open-Drain RESET Output.

- → Temperature Range: -40°C to +125°C

- → Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- → Halogen and Antimony Free. "Green" Device (Note 3)

- → For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please contact us or your local Diodes representative.

- https://www.diodes.com/quality/product-definitions/

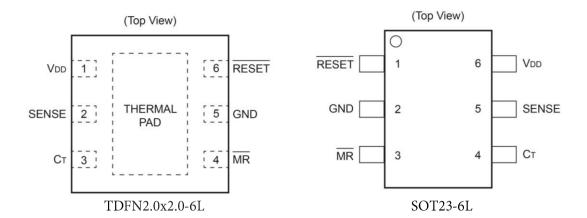

- → Package: TDFN2.0x2.0-6L and SOT23-6L

# **Applications**

- → DSP or Microcontroller Applications capacitor.

- → Notebook/Desktop Computers

- → PDAs/Hand-Held Products battery-powered applications.

- → Portable/Battery-Powered Products

- → FPGA/ASIC Applications

# **Description**

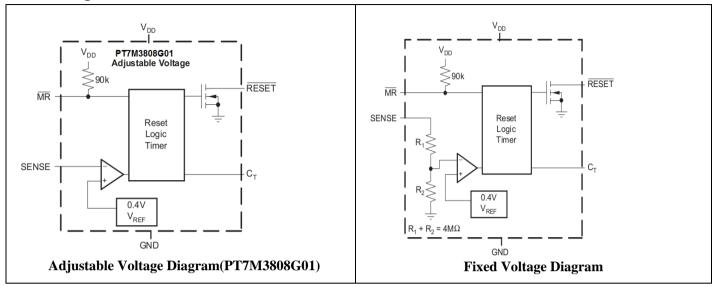

The PT7M3808G family of microprocessor supervisory circuits monitor system voltage form 0.4V to 5.0V, asserting an open-drain  $\overline{RESET}$  signal when the SENSE voltage drops below a preset threshold or when the manual reset ( $\overline{MR}$ ) pin drops to a logic low. The  $\overline{RESET}$  output remains low for the user-adjustable delay time after the SENSE voltage and manual reset ( $\overline{MR}$ ) return above the respective thresholds.

The PT7M3808G series use a precision reference to achieve 0.5% threshold accuracy for VIT  $\leq$ 3.3 V. The reset delay time can be set to 20ms by disconnecting the  $C_T$  pin, 300ms by connecting the  $C_T$  pin to  $V_{\rm DD}$  using a resister, or can be user-adjusted between 1.25ms and 10s by connecting the  $C_T$  pin to an external capacitor. The PT7M3808 has a very low typical quiescent current of 2.8uA so it is well-suited to battery-powered applications. It is available in a small SOT23 and an ultra-small 2.0x2.0 TDFN package, and is fully specified over a temperature range of -40°C to +125°C.

Notes:

<sup>1.</sup> No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

<sup>2.</sup> See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free. 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

# **Block Diagram**

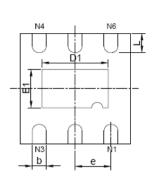

# **Pin Configuration**

**Pin Description**

| r iii Description |      |                |                                                                                                                                                                                                                                                                                                                                    |  |  |

|-------------------|------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin No            |      | Pin Name       | Description                                                                                                                                                                                                                                                                                                                        |  |  |

| SOT23             | TDFN |                |                                                                                                                                                                                                                                                                                                                                    |  |  |

| 1                 | 6    | RESET          | An open-drain output that is driven to a low impedance state when $\overline{RESET}$ is asserted. $\overline{RESET}$ will remain low (asserted) for the reset period after both SENSE is above $V_{IT}$ and $\overline{MR}$ is set to a logic high. A pull-up resistor from $10k\Omega$ to $1Mohm$ should be used on this pin, and |  |  |

|                   |      |                | allows the reset pin to attain voltages higher than $V_{\rm DD}$ .                                                                                                                                                                                                                                                                 |  |  |

| 2                 | 5    | GND            | Ground.                                                                                                                                                                                                                                                                                                                            |  |  |

| 3                 | 4    | MR             | Driving the manual reset pin ( $\overline{MR}$ ) low asserts RESET . MR is internally tied to $V_{DD}$ by a 90kohm pull-up resistor.                                                                                                                                                                                               |  |  |

| 4                 | 3    | $C_{T}$        | Reset period programming pin. Connection this pin to VDD through a $40k\Omega$ to $200k\Omega$ resistor for 300ms or leaving it open results in fixed delay times 20ms. And connecting this pin with a cap $\geq$ 100pF to ground a user-programmable delay time.                                                                  |  |  |

| 5                 | 2    | SENSE          | This pin is connected to the voltage to be monitored. If the voltage at this terminal drops below the threshold voltage VIT, then RESET is asserted.                                                                                                                                                                               |  |  |

| 6                 | 1    | $V_{ m DD}$    | pply Voltage. Place a 0.1uF ceramic capacitor close to this pin.                                                                                                                                                                                                                                                                   |  |  |

| -                 | PAD  | Thermal<br>Pad | ermal Pad. Connect to ground plane to enhance thermal performance of package.                                                                                                                                                                                                                                                      |  |  |

# **Maximum Ratings**

| Storage Temperature                                                             | -65°C to +150°C        |

|---------------------------------------------------------------------------------|------------------------|

| Operating Junction Temperature, T <sub>J</sub>                                  | 40°C to +125°C         |

| Input Voltage Range, V <sub>DD</sub>                                            | 0.3V to +7.0V          |

| C <sub>T</sub> Voltage Range, V <sub>CT</sub>                                   | 0.3V to $V_{DD}$ +0.5V |

| Other Voltage Range, $V_{\overline{RESET}}$ , $V_{\overline{MR}}$ , $V_{SENSE}$ | -0.3V to +7.0V         |

| RESET pin Current                                                               | 5mA                    |

| ESD rating, HBM                                                                 | 2kV                    |

| ESD rating, CDM                                                                 | 500V                   |

|                                                                                 |                        |

## Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

**Recommended Operation Conditions**

| Sym.            | Description                                    | <b>Test Conditions</b> | Min. | Тур. | Max.   | Unit                                                                         |

|-----------------|------------------------------------------------|------------------------|------|------|--------|------------------------------------------------------------------------------|

| VDD             | Supply Voltage                                 | -                      | 1.7  |      | 6.5    | V                                                                            |

| 17              | Input High Voltage MR                          | -                      |      | -    | VDD    | V                                                                            |

| $V_{IH}$        | Input High Voltage for Open-drain RESET, SENSE |                        | 0    |      | 6.5    | V                                                                            |

| V <sub>IL</sub> | Input Low Voltage MR.                          | -                      | -    | -    | 0.3VDD | V                                                                            |

| $T_A$           | Operating Temperature                          | -                      | -40  | -    | 125    | ${}^{\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

## **Electrical Characteristics**

Unless otherwise specified,  $-40^{\circ}\text{C} \le T_A \le 125^{\circ}\text{C}$ ,  $1.7\text{V} \le V_{DD} \le 6.5\text{V}$ ,  $R_{RESET} = 100\text{k}\Omega$ ,  $C_{RESET} = 50\text{Pf}$ , Typical values are at  $T_A = +25^{\circ}\text{C}$ .

| Symbol              | Parameter                               | Te                                                                                                  | est Conditions                                    | Min.           | Тур. | Max. | Unit      |  |

|---------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------|------|------|-----------|--|

| $V_{DD}$            | Supply voltage                          |                                                                                                     |                                                   | 1.7            | -    | 6.5  | V         |  |

| Ţ                   | Supply augrent                          | $V_{DD}$ =3.3V, RESE RESET , $C_T$ ope                                                              | $\overline{T}$ not asserted, $\overline{MR}$ , n. | -              | 2.8  | 5.0  | μΑ        |  |

| $ m I_{DD}$         | Supply current                          | $V_{DD}$ =6.5V, $\overline{RESET}$ not asserted, $\overline{MR}$ , $\overline{RESET}$ , $C_T$ open. |                                                   | -              | 3.0  | 6.0  | uA        |  |

| $V_{OL}$            | Low level output voltage                | $1.3V \le V_{DD} < 1.8V, I_0$                                                                       | <sub>OL</sub> =0.4mA                              | -              | -    | 0.3  | V         |  |

| V OL                | Low level output voltage                | $1.8V \le V_{DD} \le 6.5V, I_0$                                                                     | <sub>OL</sub> =1.0mA                              | -              | =.   | 0.4  |           |  |

| $V_{POR}$           | Power-up reset voltage *                | $V_{OL}=0.2V, I_{RE\overline{SET}}=1$                                                               | 15μΑ                                              | -              | =.   | 1.0  | V         |  |

|                     | Na action as in a insurt through ald    | PT7M3808G01                                                                                         |                                                   | -2.0 ±1.0 +2.0 |      |      |           |  |

| $V_{IT}$            | Negative-going input threshold accuracy | $V_{IT} \leq 3.3 \text{ V}$                                                                         |                                                   | -1.5           | ±0.5 | +1.5 | %         |  |

|                     |                                         | $3.3 \text{ V} < \text{V}_{\text{IT}} \leqslant 5.0 \text{ V}$                                      |                                                   | -2.0           | ±1.0 | +2.0 |           |  |

| * 7                 | PT7M3808                                | PT7M3808G01                                                                                         |                                                   | -              | 1.5  | 3.0  | 0/37      |  |

| $V_{HYS}$           | Hysteresis on V <sub>IT</sub> pin       | Fixed versions                                                                                      |                                                   |                | 1    | 2.5  | $%V_{IT}$ |  |

| $R_{\overline{MR}}$ | MR Internal pull-up resistance          |                                                                                                     |                                                   | 70             | 90   | -    | kΩ        |  |

| <b>T</b>            | T GENGE :                               | PT7M3808G01                                                                                         | $V_{SENSE} = V_{IT}$                              | -25            |      | 25   | nA        |  |

| $I_{SENSE}$         | Input current at SENSE pin              | Fixed versions                                                                                      | V <sub>SENSE</sub> =6.5V                          | -              | 1.8  | -    | μA        |  |

| $I_{OH}$            | RESET Leakage Current                   | V <sub>RESET</sub> =6.5V, RES                                                                       | SET not asserted                                  | -              |      | 300  | nA        |  |

| C                   | T                                       | C <sub>T</sub> pin                                                                                  | $V_{IN}=0V$ to $V_{DD}$                           | -              | 5    | -    | Б         |  |

| $C_{IN}$            | Input capacitance, any pin              | Other pins                                                                                          | V <sub>IN</sub> =0V to 6.5V                       | -              | 5    | -    | pF        |  |

| Symbol           | Parameter                     | Test Conditions      |                                              |             | Typ.  | Max.                 | Unit |

|------------------|-------------------------------|----------------------|----------------------------------------------|-------------|-------|----------------------|------|

| V <sub>IL</sub>  | MR logic low input            | -                    |                                              | 0           |       | $0.3V_{\mathrm{DD}}$ | V    |

| V <sub>IH</sub>  | MR logic High input           | -                    |                                              | $0.7V_{DD}$ |       | VDD                  | V    |

|                  | SENSE                         |                      | $V_{IH} = 1.05 V_{IT}, V_{IL} = 0.95 V_{IT}$ | -           | 20    | -                    | μs   |

| $t_{\mathrm{W}}$ | Input pulse width to RESET    | MR                   | $V_{IH} = 0.7 V_{DD}, V_{IL} = 0.3 V_{DD}$   | -           | 0.001 | -                    | μs   |

|                  |                               | C <sub>T</sub> =open |                                              | 12          | 20    | 28                   | ms   |

|                  | RESET delay time              | $C_T$ =VDD           |                                              | 180         | 300   | 420                  | ms   |

| $t_{\mathrm{D}}$ |                               | $C_T=100pF$          |                                              | 0.75        | 1.25  | 1.75                 | ms   |

|                  |                               | $C_T=180nF$          |                                              | 0.7         | 1.2   | 1.7                  | S    |

|                  | Propagation delay             | MR to RESET          | $V_{IH} = 0.7 V_{DD}, V_{IL} = 0.3 V_{DD}$   | -           | 150   | - ns                 |      |

| t <sub>pHL</sub> | High to low level RESET delay | SENSE to RESET       | $V_{IH} = 1.05 V_{IT}, V_{IL} = 0.95 V_{IT}$ | -           | 20    | -                    | us   |

$\begin{tabular}{ll} \textbf{Note} : The lowest supply voltage ($V_{DD}$) at which $\overline{RESET}$ becomes active. Trise($V_{DD}$) $\geqslant$15us/V. \\ \end{tabular}$

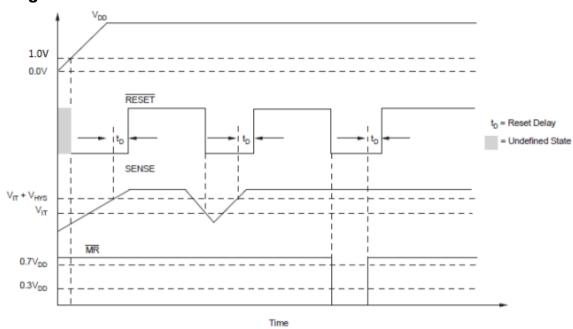

# **Timing Diagram**

## **Truth Table**

| MR | SENSE>VIT | RESET |

|----|-----------|-------|

| L  | 0         | L     |

| L  | 1         | L     |

| Н  | 0         | L     |

| Н  | 1         | Н     |

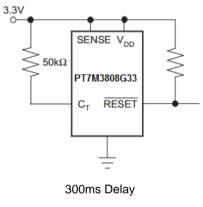

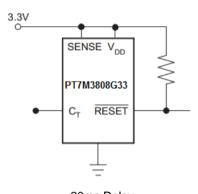

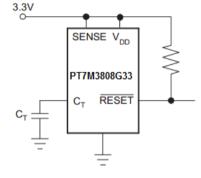

# **Typical Application Circuit**

# **Functional Description**

The PT7M3808 microprocessor supervisory product family is designed to assert a RESET signal when either the SENSE pin voltage drops below  $V_{IT}$  or the manual reset ( $\overline{MR}$ ) is driven low. The RESET output remains asserted for a user-adjustable time after both the manual reset ( $\overline{MR}$ ) and SENSE voltages return above the respective thresholds. A broad range of the voltage threshold and reset delay time adjustments are available, allowing these devices to be used in a wide array of applications. Reset threshold voltages can be factory-set from 0.82V to 3.3V or from 4.4V to 5.0V, while the PT7M3808G01 can be set to any voltage above 0.405V using an external resistor divider. Two preset delay times are also user-selectable: connecting the  $C_T$  pin to  $V_{DD}$  results in a 300ms reset delay, while leaving the  $C_T$  pin open yields a 20ms reset delay. In addition, connecting a capacitor between  $C_T$  and GND allows the designer to select any reset delay period from 1.25ms to 10s.

## **RESET Output**

The open-drain  $\overline{RESET}$  output is typically connected to the  $\overline{RESET}$  input of a microprocessor. A pull-up resistor must be used to hold this line high when  $\overline{RESET}$  is not asserted. The  $\overline{RESET}$  output is undefined for voltage below 1.0V, but this is normally not a problem since most microprocessors do not function below this voltage.  $\overline{RESET}$  remains high (unasserted) as long as  $\overline{SENSE}$  is above its threshold( $\overline{V_{IT}}$ ) and the manual reset ( $\overline{MR}$ ) is logic high. If either SENSE falls below  $\overline{V_{IT}}$  or  $\overline{MR}$  is driven low,  $\overline{RESET}$  is asserted, driving the  $\overline{RESET}$  pin to low impedance.

Once  $\overline{MR}$  is again logic high and SENSE is above  $V_{IT}$  + VHYS (the threshold hysteresis), a delay circuit is enabled which holds  $\overline{RESET}$  low for a specified reset delay period. Once the reset delay has expired, the  $\overline{RESET}$  pin goes to a high impedance state. The pull-up resistor from the open-drain  $\overline{RESET}$  to the supply line can be used to allow the reset signal for the microprocessor to have a voltage higher than  $V_{DD}$  (up to 6.5V). The pull-up resistor should be no smaller than  $10k\Omega$  as a result of the finite impedance of the  $\overline{RESET}$  line.

#### **SENSE Input**

The SENSE input provides a pin at which any system voltage can be monitored. If the voltage on this pin drops below  $V_{IT}$ , then RESET is asserted. The comparator has a built-in hysteresis to ensure smooth RESET assertions and de-assertions. It is good analog design practice to put a 1nF to 10nF bypass capacitor on the SENSE input to reduce sensitivity to transients and layout parasitic.

The PT7M3808G01 can be used to monitor any voltage rail down to 0.405V by resister divider.

## Manual Reset (MR) Input

The manual reset ( $\overline{MR}$ ) input allows a processor or other logic circuits to initiate a reset. A logic low (0.3V<sub>DD</sub>) on  $\overline{MR}$  will cause  $\overline{RESET}$  to assert. After  $\overline{MR}$  returns to a logic high and SENSE is above its reset threshold,  $\overline{RESET}$  is de-asserted after the user defined reset delay expires. Note that  $\overline{MR}$  is internally tied to V<sub>DD</sub> using a 90kohm resistor so this pin can be left unconnected if  $\overline{MR}$  will not be used. Do not apply voltage level over VDD.

## **Selecting the RESET Delay Time**

The PT7M3808 has three options for setting the RESET delay time.

- 1. A fixed 300ms typical delay time by tying  $C_T$  to  $V_{DD}$  through a resistor from  $40k\Omega$  to  $200k\Omega$ . As below Figure (a) shown.

- 2. A fixed 20ms delay time by leaving the C<sub>T</sub> pin open. As below Figure (b) shown.

- 3. A ground referenced capacitor connected to  $C_T$  for a user-defined program time between 1.25ms and 10s. The capacitor  $C_T$ should be ≥ 100pF nominal value in order for the PT7M3808xxx to recognize that the capacitor is present. The capacitor value for a given delay time can be calculated using the following equation:  $C_T(nF) = [t_D(s) - 0.5x10^{-3}(s)]x175$ . As below Figure (c) shown.

The reset delay time is determined by the time it takes an on-chip precision 220nA current source to charge the external capacitor to 1.23V. When a RESET is asserted the capacitor is discharged. When the RESET conditions are cleared, the internal current source is enabled and begins to charge the external capacitor. When the voltage on this capacitor reaches 1.23V, RESET is deasserted. Note that a low leakage type capacitor such as a ceramic should be used and the stray capacitance around this pin may cause errors in the reset delay time.

(a)

20ms Delay (b)

Delay (s) =

$$\frac{CT (nF)}{175} + 0.5 \times 10^{-3}$$

(s)

# **Part Marking**

(1) SOT23-6 (TA)

$\overline{x}X$ : Identification code

1<sup>st</sup> Y : Year

W: Date Code (Workweek)

2<sup>nd</sup> Y : Die Rev

Vertical line in front of top mark means Pin1

Bar about W means Cu wire

| Part Number     | Package Code | Package | Identification Code |

|-----------------|--------------|---------|---------------------|

| PT7M3808G01TAE  | TA           | SOT23-6 | tG                  |

| PT7M3808G09TAE  | TA           | SOT23-6 | uU                  |

| PT7M3808G12TAE  | TA           | SOT23-6 | uV                  |

| PT7M3808G125TAE | TA           | SOT23-6 | uW                  |

| PT7M3808G15TAE  | TA           | SOT23-6 | uX                  |

| PT7M3808G18TAE  | TA           | SOT23-6 | uY                  |

| PT7M3808G19TAE  | TA           | SOT23-6 | uZ                  |

| PT7M3808G25TAE  | TA           | SOT23-6 | wA                  |

| PT7M3808G30TAE  | TA           | SOT23-6 | wB                  |

| PT7M3808G33TAE  | TA           | SOT23-6 | tH                  |

| PT7M3808G50TAE  | TA           | SOT23-6 | wC                  |

## (2) TDFN-6 (ZC)

xX : Identification code

1<sup>st</sup> Y : Die Rev 2<sup>nd</sup> Y : Year

W : Date Code (Workweek) Bar about W means Cu wire

| Part Number     | Package Code | Package | Identification Code |

|-----------------|--------------|---------|---------------------|

| PT7M3808G01ZCE  | ZC           | TDFN-6  | tG                  |

| PT7M3808G09ZCE  | ZC           | TDFN-6  | uU                  |

| PT7M3808G12ZCE  | ZC           | TDFN-6  | uV                  |

| PT7M3808G125ZCE | ZC           | TDFN-6  | uW                  |

| PT7M3808G15ZCE  | ZC           | TDFN-6  | uX                  |

| PT7M3808G18ZCE  | ZC           | TDFN-6  | uY                  |

| PT7M3808G19ZCE  | ZC           | TDFN-6  | uZ                  |

| PT7M3808G25ZCE  | ZC           | TDFN-6  | wA                  |

| PT7M3808G30ZCE  | ZC           | TDFN-6  | wB                  |

| PT7M3808G33ZCE  | ZC           | TDFN-6  | tH                  |

| PT7M3808G50ZCE  | ZC           | TDFN-6  | wC                  |

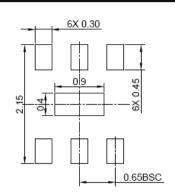

# Packaging Mechanical TDFN-6 (ZC)

TOP VIEW

BOTTOM VIEW

RECOMMENDED LAND PATTERN(unit:mm)

| PKG. DIMENSIONS(MM) |          |      |  |  |  |

|---------------------|----------|------|--|--|--|

| SYMBOL              | Min      | Max  |  |  |  |

| Α                   | 0.70     | 0.80 |  |  |  |

| A1                  | 0.00     | 0.05 |  |  |  |

| A3                  | 0.20     | REF  |  |  |  |

| D                   | 2.00 BSC |      |  |  |  |

| Е                   | 2.00     | BSC  |  |  |  |

| D1                  | 1.10     | 1.30 |  |  |  |

| E1                  | 0.60     | 0.80 |  |  |  |

| b                   | 0.20     | 0.30 |  |  |  |

| L                   | 0.27     | 0.43 |  |  |  |

| е                   | 0.65 BSC |      |  |  |  |

SIDE VIEW

**PERICOM**

DATE: 12/09/13

DESCRIPTION: 6-Pin, TDFN, 2X2

PACKAGE CODE: ZC (ZC6) DOCUMENT CONTROL #: PD-2178

REVISION: -

1. Ref: JEDEC MO-287A

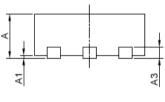

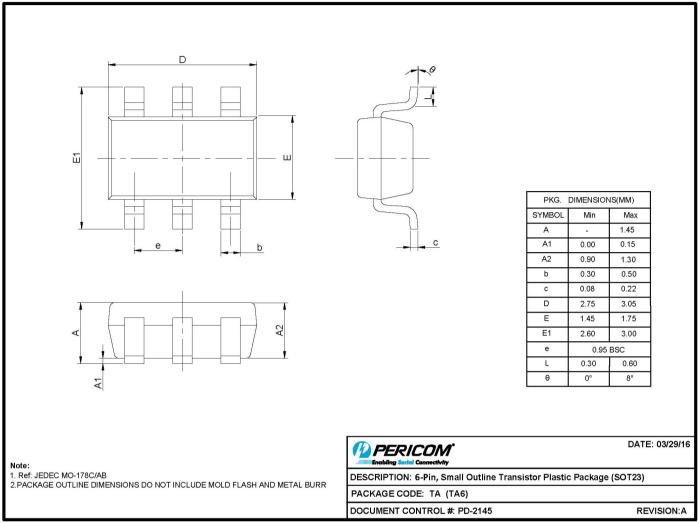

# SOT23-6 (TA)

16-0082

## For latest package info.

please check: http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/

## **Ordering Information**

| Part Numbers     | Package Code | Package Description                                     |  |  |  |  |

|------------------|--------------|---------------------------------------------------------|--|--|--|--|

| PT7M3808GxxxZCEX | ZC           | 6-pin, 2.0x2.0 (TDFN)                                   |  |  |  |  |

| PT7M3808GxxxTAEX | TA           | 6-pin, Small Outline Transistor Plastic Package (SOT23) |  |  |  |  |

#### Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

- See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.</li>

- 4. E = Pb-free and Green

- $_{5.}$  X suffix = Tape/Reel

**Function Comparison Table**

| Product      | Nominal Supply Voltage | SENSE Threshold Voltage(V <sub>IT</sub> ) |

|--------------|------------------------|-------------------------------------------|

| PT7M3808G01  | adjustable             | 0.405V                                    |

| PT7M3808G09  | 0.9V                   | 0.84V                                     |

| PT7M3808G12  | 1.2V                   | 1.12V                                     |

| PT7M3808G125 | 1.25V                  | 1.16V                                     |

| PT7M3808G15  | 1.5V                   | 1.40V                                     |

| PT7M3808G18  | 1.8V                   | 1.67V                                     |

| PT7M3808G19  | 1.9V                   | 1.77V                                     |

| PT7M3808G25  | 2.5V                   | 2.33V                                     |

| PT7M3808G30  | 3.0V                   | 2.79V                                     |

| PT7M3808G33  | 3.3V                   | 3.07V                                     |

| PT7M3808G50  | 5.0V                   | 4.65V                                     |

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2016, Diodes Incorporated www.diodes.com

PT7M3808 Document Number DS39989 Rev 3-2 www.diodes.com

# 单击下面可查看定价,库存,交付和生命周期等信息

>>Diodes Incorporated(达迩科技(美台))