AP3981C

#### PRIMARY SIDE REGULATED POWER SWITCHER

## Description

The AP3981C is a high performance power switchers integrated with a primary side regulation controller and an N-channel power MOSFET. It can be used for battery charger and adaptor applications, accurate Constant Voltage (CV) and Constant Current (CC) can be achieved without an opto-coupler and secondary control circuitry.

The AP3981C operates in Pulse Frequency Modulation (PFM) mode and peak current Amplitude Modulation (AM) mode to form a fine tune frequency curve within the whole power range. Therefore, the AP3981C can achieve high average efficiency and improve audible noise.

The AP3981C provides comprehensive protections without additional circuitry. It contains  $V_{CC}$  over voltage protection, output over voltage protection, output under voltage protection, output short circuit protection, cycle-by-cycle current limit, open loop protection, and internal over temperature protection, etc.

The AP3981C is available in SO-8 package.

### **Features**

- Primary Side Control for Eliminating Opto-Coupler

- Built-In 650V Power MOSFET

- 75mW No-Load Input Power

- Flyback Topology in DCM Operation

- External Adjustable Line Compensation for CC

- Fixed Internal Cable Compensation

- Multiple Segment AM/PFM Control Mode to Improve Audio Noise and Efficiency

- Frequency Jitter to Improve System EMI

- Capacitive Load Start-Up Capability

- Valley-On for the Higher Efficiency and Better EMI Behavior

- Multiple Protections:

- Secondary-Side Over Voltage Protection (SOVP)

- Secondary-Side Under Voltage Protection (SUVP)

- Output Short Circuit Protection (SCP)

- Transformer Saturation Protection (TSP) via Primary Peak Current Limitation

- Internal Over Temperature Protection (OTP)

- SO-8 Package

Notes:

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

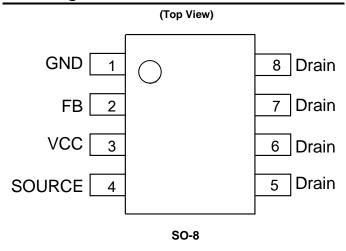

## **Pin Assignments**

## **Applications**

- Routers

- Set-Top Box (STB) Power Supply

- Network Adaptors

1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

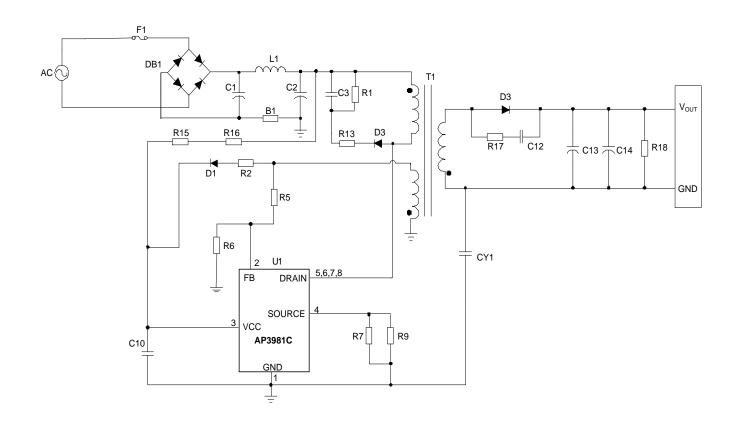

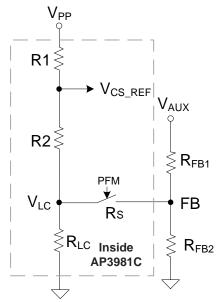

# **Typical Applications Circuit**

## **Pin Descriptions**

| Pin Number | Pin Name | Function                                                                                                                                                                                                                                                                  |

|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | GND      | The ground of the IC                                                                                                                                                                                                                                                      |

| 2          | FB       | Connect to the auxiliary winding through a divider network, used as a multi-function pin to realize output voltage sample for CV control, $t_{\rm ONS}$ detection for CC control, line voltage sense for line compensation, and FB-negative-protection detection as well. |

| 3          | VCC      | The power supply of the IC                                                                                                                                                                                                                                                |

| 4          | SOURCE   | SOURCE terminal of the integrated MOSFET                                                                                                                                                                                                                                  |

| 5, 6, 7, 8 | DRAIN    | DRAIN terminal of the integrated MOSFET                                                                                                                                                                                                                                   |

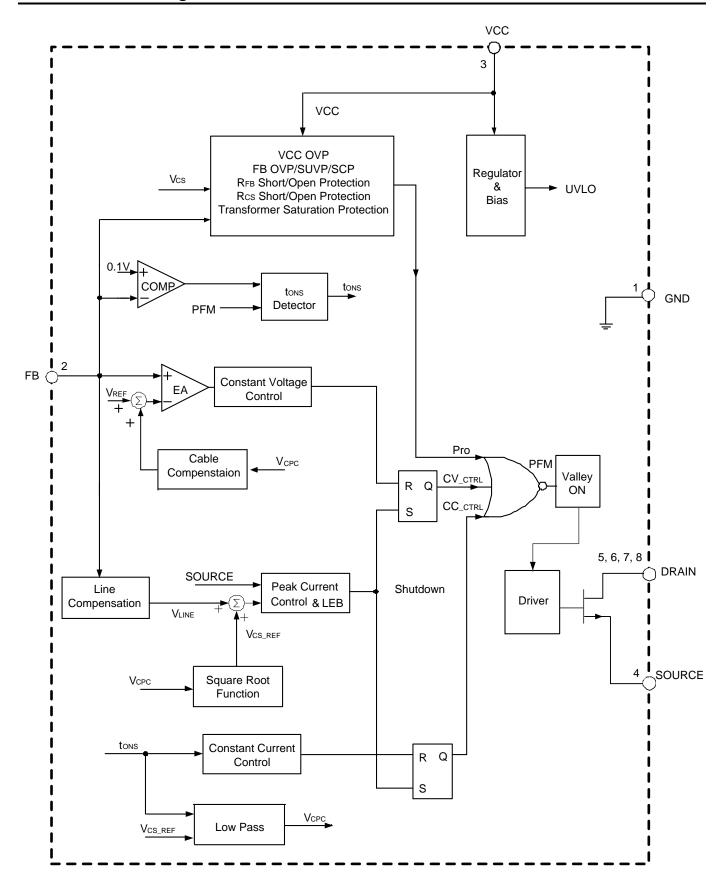

## **Functional Block Diagram**

## **Absolute Maximum Ratings** (Note 4)

| Symbol              | Parameter                                         | Rating      | Unit |

|---------------------|---------------------------------------------------|-------------|------|

| V <sub>CC</sub>     | Supply Voltage                                    | -0.3 to 35  | V    |

| V <sub>SOURCE</sub> | SOURCE Input Voltage                              | -0.3 to 8   | V    |

| V <sub>FB</sub>     | FB Input Voltage                                  | -0.3 to 8   | V    |

| V <sub>DS</sub>     | Drain-Source Voltage (T <sub>J</sub> =+25°C)      | 650         | V    |

| TJ                  | Operating Junction Temperature                    | -40 to +150 | °C   |

| T <sub>STG</sub>    | Storage Temperature                               | -65 to +150 | °C   |

| T <sub>LEAD</sub>   | Lead Temperature (Soldering, 10s)                 | +300        | °C   |

| θις                 | Thermal Resistance (Junction to Case) (Note 5)    | 3           | °C/W |

| θ <sub>JA</sub>     | Thermal Resistance (Junction to Ambient) (Note 5) | 65          | °C/W |

| _                   | ESD (Human Body Model)                            | 2000        | V    |

| _                   | ESD (Charged Device Model)                        | 1000        | V    |

Notes: 4. Stresses greater than those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to "Absolute Maximum Ratings" for extended periods can affect device reliability.

Test condition: Device mounted on FR-4 substrate PC board, 2oz copper, with 1inch² cooling area.

# **Recommended Operating Conditions**

| Symbol          | Parameter           | Min | Max | Unit |

|-----------------|---------------------|-----|-----|------|

| V <sub>CC</sub> | Supply Voltage      | 10  | 28  | ٧    |

| TA              | Ambient Temperature | -40 | +85 | °C   |

#

| Symbol                               | Parameter                                                      | Condition                                                 | Min  | Тур  | Max  | Unit |  |

|--------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------|------|------|------|------|--|

| STARTUP AND UVI                      | STARTUP AND UVLO SECTION                                       |                                                           |      |      |      |      |  |

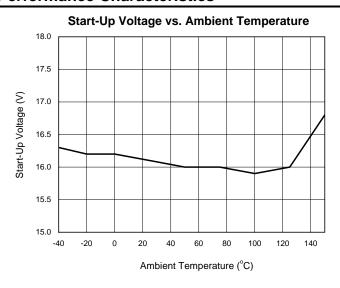

| V <sub>TH_ST</sub>                   | Startup Threshold                                              | _                                                         | 14.5 | 16   | 17.5 | V    |  |

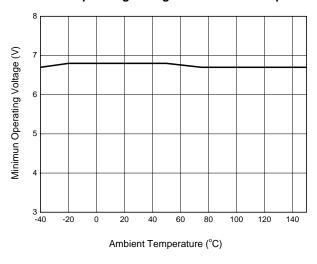

| V <sub>OPR(MIN)</sub>                | Minimum Operating Voltage                                      | _                                                         | 6.1  | 6.8  | 7.5  | V    |  |

| STANDBY CURREN                       | NT SECTION                                                     |                                                           |      |      |      |      |  |

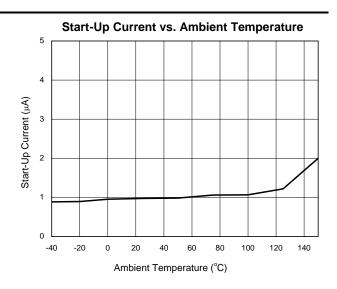

| I <sub>ST</sub>                      | Startup Current                                                | V <sub>CC</sub> =V <sub>TH_ST</sub> -1V before<br>Startup | _    | 1    | 3    | μА   |  |

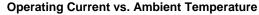

| I <sub>CC_OPR</sub>                  | Minimum Operating Current                                      | Static Current                                            | 450  | 550  | 650  | μА   |  |

| CURRENT SENSE                        | SECTION                                                        |                                                           |      |      |      |      |  |

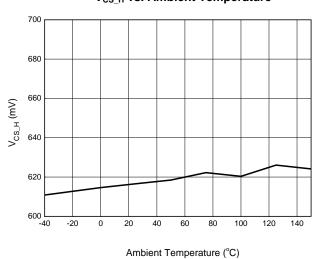

| Vcs_H                                | Peak Current Sense Threshold                                   | 40% to 100% CC Load                                       | 560  | 630  | 700  | mV   |  |

| V <sub>CS_L</sub>                    | Voltage                                                        | No Load to 2% CC Load                                     | 160  | 180  | 200  | mV   |  |

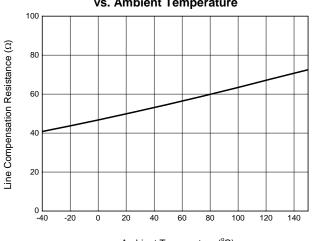

| R <sub>LINE</sub>                    | Built-In Line Compensation<br>Resistance                       | _                                                         | 45   | 55   | 65   | Ω    |  |

| t <sub>LEB</sub>                     | Leading Edge Blanking                                          | _                                                         | 370  | 470  | 570  | ns   |  |

| CONSTANT VOLTA                       | AGE SECTION                                                    |                                                           |      |      |      |      |  |

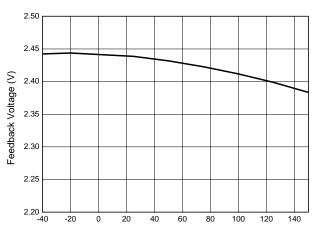

| $V_{FB}$                             | Feedback Threshold Voltage                                     | Closed Loop Test of V <sub>OUT</sub>                      | 2.35 | 2.4  | 2.45 | V    |  |

| Ratios <sub>AMPLE_L</sub>            | Sample Ratio                                                   | No Load to 2% CC Load                                     | 45   | 50   | 55   | %    |  |

| Ratio <sub>SAMPLE_H</sub>            | Sample Ratio                                                   | 40% to 100% CC Load                                       | 75   | 80   | 85   | %    |  |

| CONSTANT CURRE                       | ENT SECTION                                                    |                                                           |      |      |      |      |  |

|                                      | Below SUVP                                                     | Tested @ V <sub>FB</sub> =1V                              | _    | 0.75 | _    | _    |  |

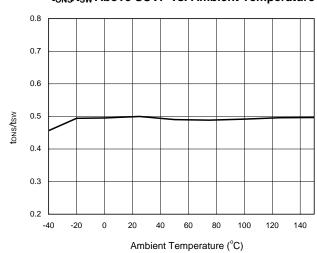

| t <sub>ONS</sub> /t <sub>SW</sub>    | Above SUVP                                                     | Tested @ V <sub>FB</sub> =2V                              | _    | 0.5  | _    | _    |  |

| FREQUENCY JITTE                      | ER                                                             |                                                           |      |      |      |      |  |

| ΔV <sub>CS</sub> /V <sub>CS</sub>    | V <sub>CS</sub> Modulation                                     | 10% Load to Full Load                                     | 1.5  | 2    | 2.5  | %    |  |

| Cable Compensation                   | on                                                             |                                                           | •    |      | •    |      |  |

| V <sub>CABLE</sub> /V <sub>OUT</sub> | Fixed Cable Compensation Ratio                                 | _                                                         | _    | 4    | _    | %    |  |

| VALLEY-ON SECTI                      | ON                                                             |                                                           | •    |      | •    | •    |  |

| t <sub>VAL-ON</sub>                  | Valid Off Time of Valley-On                                    | From the End of tons                                      | 26   | 32   | 38   | μS   |  |

| DYNAMIC SECTION                      | N .                                                            |                                                           | •    |      | •    |      |  |

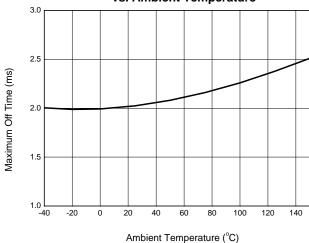

| t <sub>OFF(MAX)</sub>                | Maximum Off Time                                               | _                                                         | 1.8  | 2    | 2.2  | ms   |  |

| PROTECTION FUNCTION SECTION          |                                                                |                                                           |      |      |      |      |  |

| V <sub>FB(SOVP)</sub>                | Over Voltage Protection at FB Pin                              | _                                                         | 3.3  | 3.6  | 3.9  | V    |  |

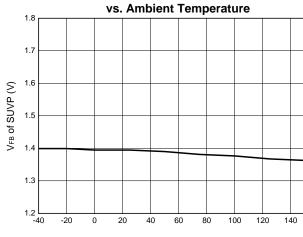

| V <sub>FB(SUVP)</sub>                | Under Voltage Protection at FB Pin                             | _                                                         | 1.22 | 1.35 | 1.48 | V    |  |

| t <sub>DELAY</sub> (SUVP)            | Delay Time of SUVP                                             | _                                                         | 116  | 128  | 140  | ms   |  |

| V <sub>FB(SCP)</sub>                 | Output Short Protection at FB Pin                              | _                                                         | 680  | 750  | 820  | mV   |  |

| t <sub>DELAY</sub> (SCP)             | Delay Time of SCP                                              | _                                                         | 58   | 64   | 70   | ms   |  |

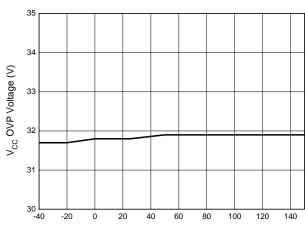

| $V_{CC(OVP)}$                        | Over Voltage Protection at VCC Pin                             | _                                                         | 29.5 | 32   | 34.5 | V    |  |

| t <sub>ONP(MAX)</sub>                | Maximum Turn-ON Time                                           | _                                                         | 12   | 16   | 20   | μs   |  |

| V <sub>CS(MIN)</sub>                 | Minimum Peak Current Sense<br>Voltage at t <sub>ONP</sub> =4µs | _                                                         | 120  | 150  | 180  | mV   |  |

| V <sub>CS(MAX)</sub>                 | Maximum CS Voltage                                             | _                                                         | 720  | 800  | 880  | mV   |  |

## Electrical Characteristics (@T<sub>A</sub> =+25°C, V<sub>CC</sub> = 15V, unless otherwise specified.) (continued)

| Symbol                | Parameter                                                     | Condition | Min  | Тур  | Max  | Unit |  |

|-----------------------|---------------------------------------------------------------|-----------|------|------|------|------|--|

| PROTECTION FU         | PROTECTION FUNCTION SECTION                                   |           |      |      |      |      |  |

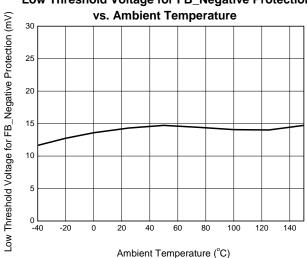

| $V_{FB\_NEG\_L}$      | Low Threshold for FB Negative Voltage Protection              | _         | 11   | 14   | 17   | mV   |  |

| V <sub>FB_NEG_H</sub> | High Threshold for FB Negative Voltage Protection             | _         | 27   | 36   | 45   | mV   |  |

| $T_{OTP}$             | Shutdown Temperature                                          | _         | +130 | +145 | +160 | °C   |  |

| T <sub>HYS</sub>      | Temperature Hysteresis                                        | _         | +27  | +30  | +33  | °C   |  |

| POWER MOSFET SECTION  |                                                               |           |      |      |      |      |  |

| BV <sub>DSS</sub>     | Integrated MOSFET Drain-Source<br>Break-Down Voltage (Note 6) | _         | 650  | _    | _    | V    |  |

| R <sub>DS(ON)</sub>   | Static Drain-Source On-Resistance                             | _         | _    | 2.8  | 3.5  | Ω    |  |

| I <sub>D</sub>        | Continuous Drain Current                                      | _         | _    | _    | 3    | А    |  |

Note: 6. The aging condition of drain-source voltage is 80% of BV<sub>DSS</sub>.

## **Performance Characteristics**

### Minimal Operating Voltage vs. Ambient Temperature

## V<sub>CS\_H</sub> vs. Ambient Temperature

## tons/tsw Above SUVP vs. Ambient Temperature

### **Performance Characteristics** (continued)

### Feedback Voltage vs. Ambient Temperature

Ambient Temperature (°C)

### V<sub>CC</sub> OVP Voltage vs. Ambient Temperature

Ambient Temperature (°C)

### **Line Compensation Resistance** vs. Ambient Temperature

Ambient Temperature (°C)

**Maximum Off Time** vs. Ambient Temperature 3.0

Low Threshold Voltage for FB\_Negative Protection

Feedback Voltage of SUVP

Ambient Temperature (°C)

## **Operation Description**

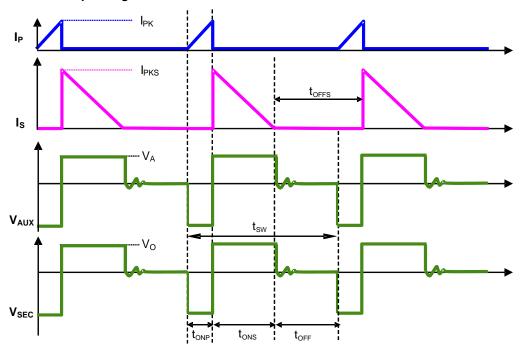

### 1. The Conventional PSR Operating Waveforms

Figure 1. The Operation Waveform of Flyback PSR System

Figure 1 shows the typical waveforms which demonstrate the basic operating principle of AP3981C application. And the parameters are defined as following.

Ip---The primary side current

Is --- The secondary side current

IPK---Peak value of primary side current

IPKS---Peak value of secondary side current

V<sub>SEC</sub>---The transient voltage at secondary winding

$V_0$ ---The output voltage

V<sub>AUX</sub>---The transient voltage at auxiliary winding

V<sub>A</sub>--- The stable voltage at auxiliary winding when rectification diode is in conducting status, which equals the sum of voltage VCC and the forward voltage drop of auxiliary diode

tsw --- The period of switching frequency

tonP --- The conduction time when primary side switch is "ON"

tons --- The conduction time when secondary side diode is "ON"

toff --- The dead time when neither primary side switch nor secondary side diode is "ON"

toFFS --- The time when secondary side diode is "OFF"

For primary-side regulation, the primary current ip(t) is sensed by a current sense resistor  $R_{CS}$  connected to pin SOURCE. The current rises up linearly at a rate of:

$$\frac{dip(t)}{dt} = \frac{\mathbf{V}_{\text{IN}}(t)}{L_{M}} \tag{1}$$

As illustrated in Figure 1, when the current ip(t) rises up to IPK, the primary MOSFET would turn off. The constant peak current is given by:

AP3981C Document number: DS41619 Rev. 2 - 2

$$I_{PK} = \frac{V_{CS}}{R_{CS}} \tag{2}$$

The energy stored in the magnetizing inductance L<sub>M</sub> each cycle is therefore:

$$Eg = \frac{1}{2} \times L_M \cdot I_{PK}^2 \tag{3}$$

So the power transferring from the input to the output is given by:

$$P = \frac{1}{2} \times L_M \times I_{PK}^2 \times f_{SW} \tag{4}$$

Where, the fsw is the switching frequency. When the peak current IPK is constant, the output power would depend on the switching frequency fsw.

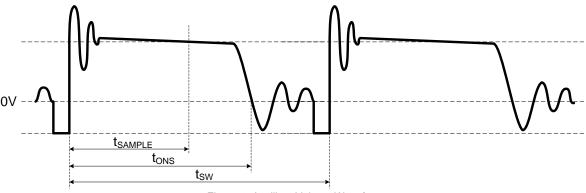

#### 2. Constant Voltage Operation

The output voltage is proportional to the auxiliary winding voltage during  $t_{ONS}$  period indicated by Formula 5, this auxiliary winding voltage is divided by resistors  $R_{FB1}$  and  $R_{FB2}$  (refer to Figure 5) before inputting to the FB pin. As Figure 2 illustrated, the AP3981C detects the FB voltage at the end of  $t_{SAMPLE}$  during  $t_{ONS}$  period, the detected voltage which reflects the output voltage is regulated to  $V_{FB}$  of 2.4V with the help of the constant voltage control block in the AP3981C. For system design, adjusting the ratio of  $R_{FB1}$  and  $R_{FB2}$  can get the target output voltage value.

$$V_{AUX} = \frac{N_{AUX}}{N_{s}} \times (Vo + Vd)$$

(5)

Figure 2. Auxiliary Voltage Waveform

### 3. Constant Current Control

In the AP3981C, Formula 6 shows the related parameters that determine the output current. To get a constant output current, the  $V_{CS}$  and  $t_{ONS}/t_{SW}$  is fixed in AP3981C during CC mode. Meanwhile, the reliable control logic is integrated within AP3981C to ensure the system swift smoothly between CC mode and CV mode.

$$I_{OUT} = \frac{1}{2} * \frac{Np}{Ns} * Ipk * \frac{t_{ONS}}{t_{SW}} = \frac{1}{2} * \frac{Np}{Ns} * \frac{V_{CS}}{R_{CS}} * \frac{t_{ONS}}{t_{SW}}$$

(6)

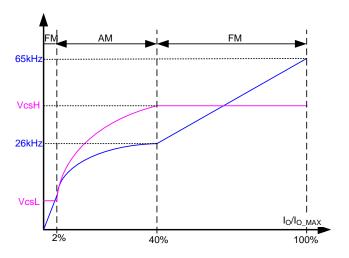

#### 4. Multiple Segment Peak Current

In the original PFM PSR system, the switching frequency decreases with the decreasing output current, which will encounter audible noise issue when switching frequency decreases below 20kHz.

In order to avoid audible noise issue and a big drop in efficiency at light load, the AP3981C uses a 3-segment primary peak current control method at CV mode, the current sense threshold voltage is piecewise defined. As shown in Figure 3, the low threshold  $V_{CS\_L}$  is set under 2% CC load, the high threshold  $V_{CS\_H}$  is set above 40% CC load. Within the range from 2% to 40%, the threshold  $V_{CS\_M}$  increases basing on the load condition, the  $V_{CS\_M}$  is carefully calculated inside the AP3981C to make the system operate at a reasonable switching frequency which rises above 20kHz at a varying slope.

Figure 3. Segment Peak Current and Operating Frequency at CV Mode

#### 5. Sample Time

As shown in Equation 5 and Figure 2, the detected auxiliary voltage reflects the output voltage. To be compatible with different system designs and avoid the turn-off ringing voltage influence on CV sampling, the  $t_{SAMPLE}$  is designed to be proportional of  $t_{ONS}$ . On the other hand, to alleviate the Vd effect on the accuracy of  $V_{OUT}$ , the sample ratio of  $t_{SAMPLE}$  to  $t_{ONS}$  varies according to load condition. The  $t_{SAMPLE}$  is usually 50% of  $t_{ONS}$  for the below 2% CC load conditions and 80% of  $t_{ONS}$  for the above 40% CC load conditions, within the range from 2% to 40% loading, the sample ratio rises linearly from 50% to 80%.

### 6. Capacitive Load Start-Up Capability

In order to achieve fast start-up for capacitive load startup applications, the AP3981C induces a two level CC point design during start up time. The output voltage rises after power on, when the detected output voltage is lower than SUVP point, the tons/tsw is set to be 0.75, which means output constant current is 1.5 times of normal output constant current. When the output voltage rises above SUVP point, the tons/tsw is switched to the normal value of 0.5.

#### 7. Leading Edge Blanking

When the power switch is turned on, a turn-on spike voltage will occur on the  $V_{CS}$  sense resistance. To avoid false-termination of the switching pulse, a fixed 470ns leading-edge blanking time is built in. During this blanking period, the current sense comparator is disabled and the primary MOSFET cannot be turned off.

#### 8. Valley Turn-On

When the off time ( $t_{OFF}$ ) is shorter than  $t_{VAL-ON}$ , the AP3981C power system can work with valley turn-on. It can reduce the switching-on power losses and achieve high overall efficiency. At the same time, because of valley turn-on the switching frequency has the random jitter feature, which will be of benefit to conductive EMI performance. The valley turn-on can also reduce the power switch turn-on spike current and then achieve the better radiative EMI performance.

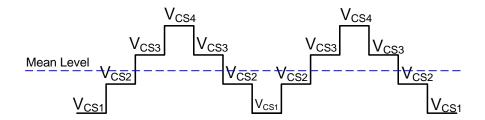

#### V<sub>CS</sub> Jitter

Even though the valley turn on function produces the random frequency jitter feature, an active frequency jitter function is added in the AP3981C. The active frequency dithering is realized by applying variation on  $V_{CS}$  reference ( $V_{CS\_REF}$ ). The  $V_{CS\_REF}$  is changed every 2 cycles and the period of variation is 12 cycles, which is shown as Figure 4. The variation between  $V_{CS4}$  and  $V_{CS1}$  is +/-2% using the mean level as a reference.

Figure 4. V<sub>CS</sub> Jitter

#### 10. Adjustable Line Compensation

In real system, there exists a delay time, from the  $V_{SOURCE}$  reach the inner  $V_{CS}$  threshold to the actual switch turn-off point. The delay time contains the propagation time of the inner comparator and the driver delay, and it does not change with line voltage. The delay time leads to different primary peak current under different line voltage, which results in different output current in CC mode.

Figure 5. Line Compensation Control Circuit

In order to alleviate the difference under the universal input voltage, the AP3981C integrates the line compensation control circuit shown as Figure 5. During the primary on stage, an inner switcher  $R_S$  switches on, the  $R_{LC}$  is much smaller compared with  $R_{FB2}$ , so the  $R_{FB2}$ 's effect on line compensation can be neglected, the proportional line voltage is detected through  $R_{FB1}$  and  $R_{LC}$  and is added to the  $V_{CS}$  threshold ( $V_{CS\_REF}$ ). The  $V_{LC}$  can be derived from the Formula 7:

$$V_{LC} = \frac{\frac{R_{FBI}}{3 * R2} * V_{PP} - V_{AUX}}{1 + \frac{R_{FBI}}{3 * R2} + \frac{R_{FBI}}{R_{LC}}}$$

(7)

The final compensated V<sub>CS</sub> is:

$$V_{CS\_REF} = \frac{1}{3} * V_{PP} + \frac{2}{3} * V_{LC}$$

(8)

In the above formulas,  $V_{PP}$  is 1.8V at CC mode,  $R_{LC}$  is  $55\Omega$ , R2 is  $60k\Omega$ , R1 is two times of R2,  $V_{AUX}$  is the auxiliary winding voltage during primary-on period, which is proportional to bus voltage. Based on the formula, we can make a conclusion that a smaller  $R_{FB1}$  results in deeper line compensation. If we know the delay time  $t_{DELAY}$ , typically 150ns in AP3981C, we can calculate the  $R_{FB1}$  as a reference for the system design.

#### 11. Protection

The AP3981C provides versatile protections to prevent the system from damage under various fault conditions. Most protections will trigger autorecovery mode in which the system will restart as soon as the V<sub>CC</sub> drops to V<sub>OPR(MIN)</sub>, when the fault conditions are removed, the system will recover to normal operation automatically.

#### V<sub>CC</sub> OVP

A  $V_{CC}$  OVP threshold is set to protect the IC from damage. When the  $V_{CC}$  OVP protection is triggered, the IC will stop outputting drive signal immediately and the system will enter auto-recovery mode.

#### **Output Over Voltage Protection (SOVP)**

As it is described above that the FB pin voltage during  $t_{ONS}$  reflects the output voltage proportionally, this voltage can be used to realize SOVP. The AP3981C set a higher threshold,  $V_{FB(OVP)}$ , to shut down the system if the sampled voltage reached the threshold continuously for 3 switching cycles, the SOVP will be triggered and the system will enter auto-recovery mode.

#### **Output Under Voltage Protection (SUVP)**

Like SOVP, the AP3981C also integrates the SUVP protection. If the detected voltage on FB pin is lower than V<sub>FB(SUVP)</sub> for 128ms, the SOVP will be triggered and the system will enter auto-recovery mode.

#### **Output Short Protection (SCP)**

A much lower threshold is set on FB pin to protect the system when output short condition occurs. If the detected FB voltage is lower than 0.78V for 64ms, the SCP will be triggered and the system will enter auto-recovery mode.

#### **Transformer Anti-Saturation Protection**

Under some fault conditions or bad system design, the transformer may approach saturation and the current increases dramatically. To avoid power device damage since of transformer saturation, the AP3981C integrates a maximum  $V_{CS}$  threshold  $V_{CS(MAX)}$  to protect the system. If there are 3 consecutive pulses where  $V_{CS}$  exceeds the threshold, the controller will shut down and enter auto-recovery mode.

#### **Over Temperature Protection (OTP)**

If the IC junction temperature exceeds the threshold of  $T_{OTP}$ , AP3981C will shut down immediately and enter auto-recovery mode. Note that even when the  $V_{CC}$  reaches  $V_{TH}$  ST, the IC will not output any drive pulse until the junction temperature falls of a hysteresis temperature of +30°C.

#### **Brown In/ Brown Out Protection**

The AP3981C detects the bus voltage at each switching cycle through FB pin during  $t_{ONP}$  period. When the  $V_{CC}$  reaches  $V_{TH\_ST}$  after power on, the AP3981C will output one switching pulse to check if the detected bus voltage on FB pin is higher than  $V_{FB\_NEG\_H}$ . If so, the system will start up normally, otherwise the AP3981C will stop outputting following pulses, then the  $V_{CC}$  will drop below  $V_{OPR(MIN)}$  and the system will repeat the process described above until the detected FB voltage is higher than  $V_{FB\_NEG\_H}$ . When the power is off or there is a ditch in bus voltage, if the detected voltage is lower than  $V_{FB\_NEG\_L}$  for 3 consecutive switching cycles, the IC will shut down and enter auto-recovery mode. This function is very useful when the bulk capacitor is open, or when the heavy load suddenly released after power off.

AP3981C 13 of 16

Document number: DS41619 Rev. 2 - 2 Downloaded From Oneyac.com

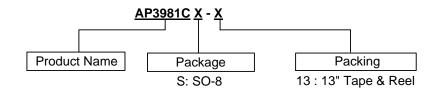

# **Ordering Information**

| Package | Part Number | Marking ID | Packing          |

|---------|-------------|------------|------------------|

| SO-8    | AP3981CS-13 | 3981C      | 4000/Tape & Reel |

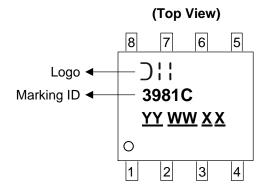

## **Marking Information**

SO-8

YY: Year: 18, 19, 20~ WW: Week: 01~52; 52

represents 52 and 53 week

$\underline{X}\,\underline{X}$  : Internal Code

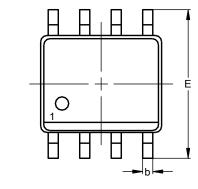

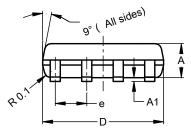

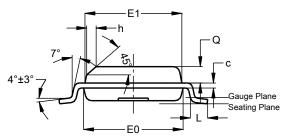

## **Package Outline Dimensions**

Please see http://www.diodes.com/package-outlines.html for the latest version.

#### (1) Package Type: SO-8

| SO-8                 |      |      |      |  |  |

|----------------------|------|------|------|--|--|

| Dim                  | Min  | Max  | Тур  |  |  |

| Α                    | 1.40 | 1.50 | 1.45 |  |  |

| A1                   | 0.10 | 0.20 | 0.15 |  |  |

| b                    | 0.30 | 0.50 | 0.40 |  |  |

| O                    | 0.15 | 0.25 | 0.20 |  |  |

| D                    | 4.85 | 4.95 | 4.90 |  |  |

| Е                    | 5.90 | 6.10 | 6.00 |  |  |

| E1                   | 3.80 | 3.90 | 3.85 |  |  |

| E0                   | 3.85 | 3.95 | 3.90 |  |  |

| е                    |      |      | 1.27 |  |  |

| h                    |      |      | 0.35 |  |  |

| Г                    | 0.62 | 0.82 | 0.72 |  |  |

| Ø                    | 0.60 | 0.70 | 0.65 |  |  |

| All Dimensions in mm |      |      |      |  |  |

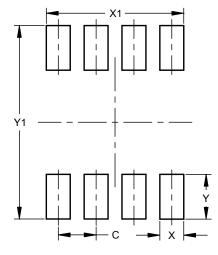

## **Suggested Pad Layout**

Please see http://www.diodes.com/package-outlines.html for the latest version.

### (1) Package Type: SO-8

| Dimensions | Value (in mm) |

|------------|---------------|

| С          | 1.27          |

| Х          | 0.802         |

| X1         | 4.612         |

| Υ          | 1.505         |

| Y1         | 6.50          |

Note:

The suggested land pattern dimensions have been provided for reference only, as actual pad layouts may vary depending on application. These dimensions may be modified based on user equipment capability or fabrication criteria. A more robust pattern may be desired for wave soldering and is calculated by adding 0.2 mm to the 'Z' dimension. For further information, please reference document IPC-7351A, Naming Convention for Standard SMT Land Patterns, and for International grid details, please see document IEC, Publication 97.

**Note:** For high voltage applications, the appropriate industry sector guidelines should be considered with regards to creepage and clearance distances between device Terminals and PCB tracking.

#### **IMPORTANT NOTICE**

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein, neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2019, Diodes Incorporated

www.diodes.com

16 of 16 AP3981C Document number: DS41619 Rev. 2 - 2

# 单击下面可查看定价,库存,交付和生命周期等信息

>>Diodes Incorporated(达迩科技(美台))