A Product Line of Diodes Incorporated

**PLL Clock Multiplier**

### Features

- → Zero ppm multiplication error

- → Input crystal frequency of 5 30 MHz

- → Input clock frequency of 1 50 MHz

- → Output clock frequencies up to 200 MHz

- ➔ Peak to Peak Jitter less than 200ps over 200ns interval (100~200MHz)

- → Low period jitter 50ps (100~200MHz)

- → 9 selectable frequencies controlled by S0, S1 pins

- → Operating voltages of 3.0 to 5.5V

- → Tri-state output for board level testing

- → Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- → Halogen and Antimony Free. "Green" Device (Note 3)

- ➔ For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please <u>contact us</u> or your local Diodes representative.

https://www.diodes.com/quality/product-definitions/

➔ Package: 8-pin, SOIC

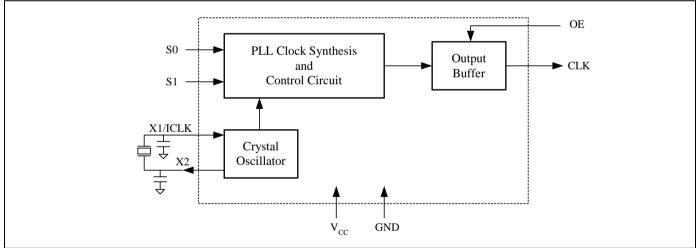

# **Block Diagram**

## Description

The PT7C4511 is a high performance frequency multiplier, which integrates Analog Phase Lock Loop techniques.

The PT7C4511 is the most cost effective way to generate a high quality, high frequency clock output from a lower frequency crystal or clock input. It is designed to replace crystal oscillators in most electronic systems, clock multiplier and frequency translation.

Using Phase-Locked-Loop (PLL) techniques, the device uses a standard fundamental mode, inexpensive crystal to produce output clocks up to 200 MHz.

The complex Logic divider is the ability to generate nine different popular multiplication factors, allowing one chip to output many common frequencies.

The device also has an Output Enable pin that tri-states the clock output when the OE pin is taken low. This product is intended for clock generation and frequency translation with low output jitter (variation in the output period).

Notes:

2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free. 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

<sup>1.</sup> No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

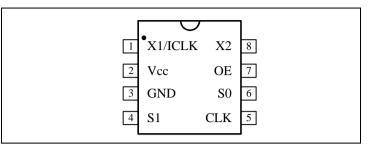

# **Pin Configuration**

### Pin Description

| Pin Name | Pin# | Туре | Description                                                                 |

|----------|------|------|-----------------------------------------------------------------------------|

| X1/ICLK  | 1    | X1   | Crystal connection or clock input.                                          |

| Vcc      | 2    | Р    | Connect to +3.3V or +5V.                                                    |

| GND      | 3    | Р    | Connect to ground.                                                          |

| S1       | 4    | T1   | Multiplier select pin, connect to GND or Vcc or floating (no connection).   |

| CLK      | 5    | 0    | Clock output per Table below.                                               |

| S0       | 6    | T1   | Multiplier select pin 0, connect to GND or Vcc or floating (no connection). |

| OE       | 7    | Ι    | Output enable, tri-state CLK output when low. Internal pull-up.             |

| X2       | 8    | XO   | Crystal connection. Leave unconnected for clock input.                      |

#### **Clock Output Table**

| <b>S1</b> | <b>S0</b> | CLK            |

|-----------|-----------|----------------|

| 0         | 0         | $\times 4$     |

| 0         | М         | ×(16/3)        |

| 0         | 1         | $\times 5$     |

| М         | 0         | ×2.5           |

| М         | М         | $\times 2$     |

| М         | 1         | $\times(10/3)$ |

| 1         | 0         | $\times 6$     |

| 1         | М         | $\times 3$     |

| 1         | 1         | $\times 8$     |

1) Note: CLK output frequency=ICLK  $\times 4$ .

2) Note: M=Leave unconnected (self-biases to Vcc/2).

## **External Components**

#### **Decoupling Capacitor**

As with any high-performance mixed-signal IC, the PT7C4511 must be isolated from system power supply noise to perform optimally. A decoupling capacitor of  $0.01\mu$ F or  $0.1\mu$ F must be connected between VCC and the GND. It must be connected close to the PT7C4511 to minimize lead inductance. No external power supply filtering is required for the PT7C4511.

#### **Series Termination Resistor**

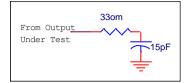

A 33 $\Omega$  terminating resistor can be used next to the CLK pin for trace lengths over one inch.

#### **Crystal Load Capacitors**

There is no on-chip capacitance build-in chip. A parallel resonant, fundamental mode crystal should be used. The device crystal connections should include pads for small capacitors from X1 to ground and from X2 to ground. These capacitors are used to adjust the stray capacitance of the board to match the nominally required crystal load capacitance. Because load capacitance can only be increased in this trimming process, it is important to keep stray capacitance to a minimum by using very short PCB traces (and no vias) between the crystal and device. Crystal capacitors, if needed, must be connected from each of the pins X1 and X2 to ground. The value (in pF) of these crystal caps should equal  $C_L*2$ . In this equation,  $C_L$ = crystal load capacitance in pF. Example: For a crystal with a 15 pF load capacitance, each crystal capacitor would be 30pF.

### **Maximum Ratings**

| Storage Temperature<br>Supply Voltage to Ground Potential (V <sub>CC</sub> ) | 0.3V to +7.0V           |

|------------------------------------------------------------------------------|-------------------------|

| Inputs (Referenced to GND)<br>Clock Output (Referenced to GND)               | -0.5V to $V_{CC}$ +0.5V |

| Junction Temperature                                                         |                         |

Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Recommended Operating Conditions**

| Symbol          | Parameter             | Conditions | Min | Тур | Max | Unit |

|-----------------|-----------------------|------------|-----|-----|-----|------|

| V <sub>CC</sub> | Supply voltage        | -          | 3.0 | -   | 5.5 | V    |

| T <sub>A</sub>  | Operating temperature | -          | -40 | -   | +85 | °C   |

### **DC Electrical Characteristics**

$(V_{CC} = 3.3V \pm 0.3V, T_A = -40 \sim 85^{\circ}C$ , unless otherwise noted)

| Symbol          | Parameter                   | Test Condition                          | Pin    | Min.      | Тур.  | Max.          | Unit |

|-----------------|-----------------------------|-----------------------------------------|--------|-----------|-------|---------------|------|

| Vcc             | Supply Voltage              | -                                       | Vcc    | 3         | 3.3   | 3.6           | V    |

| Icc             | Supply Current              | No load, 20MHz<br>crystal,100MHz output | Vcc    | -         | 12    | 20            | mA   |

| V               | Input Logic High            |                                         | ICLK   | (Vcc/2)+1 | Vcc/2 | -             | v    |

| $V_{IH}$        | Input Logic High            | -                                       | OE     | 2         | -     | -             | V    |

| V <sub>IL</sub> | Input Logic Low             | _                                       | ICLK   | -         | Vcc/2 | (Vcc/2)-<br>1 | V    |

| · IL            |                             |                                         | OE     | -         | -     | 0.8           | V    |

| V <sub>IH</sub> | Input Logic High            | -                                       | S0, S1 | Vcc-0.5   | -     | -             | V    |

| V <sub>IM</sub> | Input mid-level             | -                                       | S0, S1 | -         | Vcc/2 | -             | V    |

| V <sub>IL</sub> | Input Logic Low             | -                                       | S0, S1 | -         | -     | 0.5           | V    |

| V <sub>OH</sub> | High-level output voltage   | $I_{OH} = -12mA$                        | CLK    | 2.4       | -     | -             | V    |

| V <sub>OL</sub> | Low-level output voltage    | $I_{OL} = 12mA$                         | CLK    | -         | -     | 0.4           | V    |

| R               | Internal pull up resistance | -                                       | OE     | -         | 270   | -             | kΩ   |

| Is              | Short Circuit Current       | -                                       | CLK    | -         | ±30   | -             | mA   |

| Symbol          | Parameter        | Test Condition                          | Pin    | Min.      | Тур.  | Max.          | Unit |

|-----------------|------------------|-----------------------------------------|--------|-----------|-------|---------------|------|

| Vcc             | Supply Voltage   | -                                       | Vcc    | 4.5       | 5.0   | 5.5           | V    |

| Icc             | Supply Current   | No load, 20MHz<br>crystal,100MHz output | Vcc    | -         | 20    | 30            | mA   |

| V               | Innut Logia High |                                         | ICLK   | (Vcc/2)+1 | Vcc/2 | -             | V    |

| $V_{IH}$        | Input Logic High | -                                       | OE     | 0.65*Vcc  | -     | -             | V    |

| V <sub>IL</sub> | Input Logic Low  | _                                       | ICLK   | -         | Vcc/2 | (Vcc/2)-<br>1 | V    |

| · IL            |                  |                                         | OE     | -         | -     | 0.8           | V    |

| V <sub>IH</sub> | Input Logic High | -                                       | S0, S1 | Vcc-0.4   | -     | -             | V    |

| V <sub>IM</sub> | Input mid-level  | -                                       | S0, S1 | -         | Vcc/2 | -             | V    |

| V <sub>IL</sub> | Input Logic Low  | -                                       | S0, S1 | -         | -     | 0.4           | V    |

A Product Line of Diodes Incorporated

PT7C4511

| Symbol          | Parameter                   | Test Condition   | Pin | Min.    | Тур. | Max. | Unit |

|-----------------|-----------------------------|------------------|-----|---------|------|------|------|

| V <sub>OH</sub> | High-level output voltage   | $I_{OH} = -12mA$ | CLK | Vcc-0.5 | -    | -    | V    |

| V <sub>OL</sub> | Low-level output voltage    | $I_{OL} = 12mA$  | CLK | -       | -    | 0.4  | V    |

| R               | Internal pull up resistance | -                | OE  | -       | 270  | -    | kΩ   |

| Is              | Short Circuit Current       | -                | CLK | -       | ±70  | -    | mA   |

### **AC Electrical Characteristics**

$(V_{CC} = 3.3V \pm 0.3V, T_A = -40 \sim 85^{\circ}C$ , unless otherwise noted)

| Symbol           | Parameter                  | Test Condition                          | Pin  | Min. | Тур. | Max. | Unit |

|------------------|----------------------------|-----------------------------------------|------|------|------|------|------|

| $f_{IN}$         | Input Frequency            | -                                       | ICLK | 1    | -    | 50   | MHz  |

| f <sub>OUT</sub> | Output Frequency           | V <sub>CC</sub> : 3.0 to 3.6V           | CLK  | 20   | -    | 180  | MHz  |

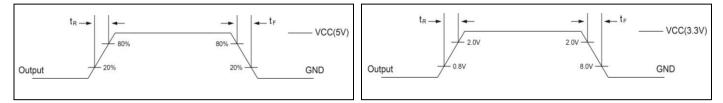

| t <sub>R</sub>   | Output clock rise time     | 0.8 to 2.0V, 15pF load                  | CLK  | -    | 1    | -    | ns   |

| t <sub>F</sub>   | Output clock fall time     | 2.0 to 0.8V, 15pF load                  | CLK  | -    | 1    | -    | ns   |

|                  |                            | At $V_{CC}$ /2, below 160MHz            | CLK  | 45   | 50   | 55   | %    |

| Duty             | Output clock duty cycle    | At V <sub>CC</sub> /2, 160MHz to 180MHz | CLK  | 40   | -    | 60   | %    |

|                  | PLL bandwidth              | -                                       | -    | 10   | -    | -    | kHz  |

|                  | Output enable time         | OE high to output on                    | -    | -    | -    | 50   | ns   |

|                  | Output disable time        | OE low to tri-rise                      | -    | -    | -    | 50   | ns   |

|                  | Period Jitter              | 70MHz~180MHz                            | CLK  | -    | 50   | 100  | ps   |

|                  | Jitter over 200ns interval | 100MHz~180MHz                           | CLK  | -    | -    | 200  | ps   |

#### $(V_{CC} = 5.0V \pm 0.5V, T_A = -40 \sim 85^{\circ}C$ , unless otherwise noted)

| Symbol           | Parameter                  | Test Condition                          | Pin  | Min. | Тур. | Max. | Unit |

|------------------|----------------------------|-----------------------------------------|------|------|------|------|------|

| f <sub>IN</sub>  | Input Frequency            | -                                       | ICLK | 1    | -    | 50   | MHz  |

| f <sub>OUT</sub> | Output Frequency           | V <sub>CC</sub> : 4.5 to 5.5V           | CLK  | 20   | -    | 200  | MHz  |

| t <sub>R</sub>   | Output clock rise time     | 20%Vcc to 80%Vcc, 15pF<br>load          | CLK  | -    | 1.2  | -    | ns   |

| t <sub>F</sub>   | Output clock fall time     | 80% Vcc to 20% Vcc, 15pF<br>load        | CLK  | -    | 1.2  | -    | ns   |

|                  |                            | At $V_{CC}$ /2, below 160MHz            | CLK  | 45   | 50   | 55   | %    |

| Duty             | Output clock duty cycle    | At V <sub>CC</sub> /2, 160MHz to 200MHz | CLK  | 40   |      | 60   | %    |

|                  | PLL bandwidth              | -                                       | -    | 10   | -    | -    | kHz  |

|                  | Output enable time         | OE high to output on                    | -    | -    | -    | 50   | ns   |

|                  | Output disable time        | OE low to tri-rise                      | -    | -    | -    | 50   | ns   |

|                  | Period Jitter 70MHz~200MHz |                                         | CLK  | -    | 50   | 100  | ps   |

|                  | Jitter over 200ns interval | nterval 100MHz~200MHz                   |      | -    | -    | 200  | ps   |

### **Test Circuits**

1>Load circuit for output clock duty cycle, rise and fall time Measurement

#### 2>Timing Definitions for output clock rise and fall time Measurement

## **Part Marking**

1st W: Die Rev Y: Date Code (Year) 2nd W: Date Code (Workweek) 1st X: Assembly Site Code 2nd X: Fab Site Code Bar above fab site code means Cu wire Bar above "T" means Fab3 of MGN

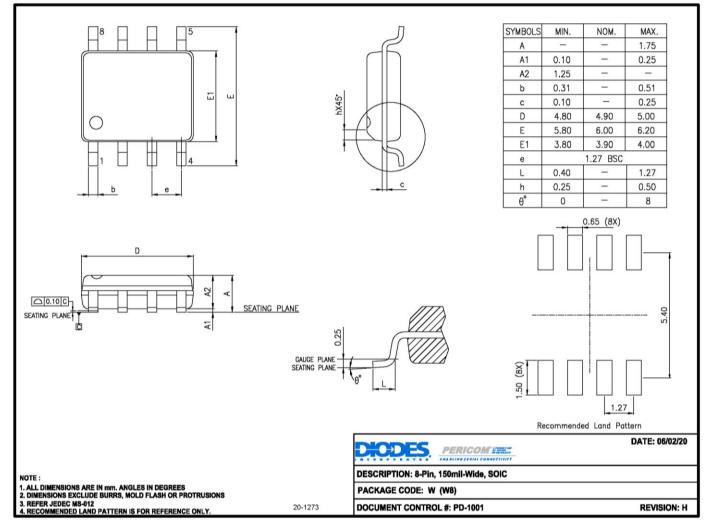

## **Packaging Mechanical**

SOIC-8 (W)

For latest package info.

please check: http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/

# **Ordering Information**

| Part Numbers | Package Code | Package Description       |

|--------------|--------------|---------------------------|

| PT7C4511WEX  | W            | 8-pin, 150mil-Wide (SOIC) |

Notes:

No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

4. E = Pb-free and Green

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

A. Life support devices or systems are devices or systems which:

1. are intended to implant into the body, or

2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2020, Diodes Incorporated www.diodes.com

单击下面可查看定价,库存,交付和生命周期等信息

>>Diodes Incorporated(达迩科技(美台))