## ULN2003V12, ULN2003F12

Multi-Channel Relay and Inductive Load Sink Driver

### Description

The ULN2003V12 and ULN2003F12 are multi-channel sink drivers comprised of 7-channel and 4-channel output stages respectively. The ULN2003V12 sink driver features 7 low output impedance drivers that minimize on-chip power dissipation and an actual low power upgrade version for popular ULN2003A family in real applications. When driving a typical 12V relay coil, a ULN2003V12 will dissipate 12 times lower power compared to ULN2003A. ULN2003F12 is a lower power variant benefiting from fewer channel integration and a better fit for applications requiring only 4-channel drivers, such as driving low voltage stepping motors, etc.

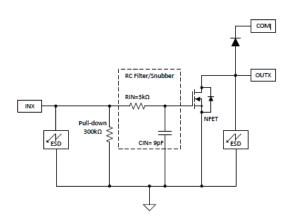

The ULN2003V12 and ULN2003F12 both support 3.3V to 5V CMOS logic input interface, thus making it compatible to a wide range of micro-controllers and other logic interfaces, and also feature an improved input interface that minimizes the input DC current drawn from the external drivers. The input RC snubber circuit integrated at ULN2003V12 and ULN2003F12 improves the performance in noisy operating conditions, and the internal pull-down resistor at input stage helps allow input logic to be tri-stated.

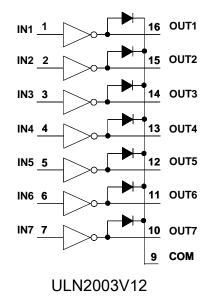

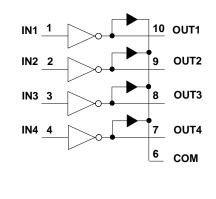

As shown in the Functional Diagram, each output of the ULN2003V12 and ULN2003F12 features an internal free-wheeling diode connected in a common-cathode configuration at the COM pin which provides flexibility of increasing current sink capability through combining several adjacent channels in parallel. Under typical conditions the ULN2003V12 can support up to 1.0A of load current when all 7channels are connected in parallel.

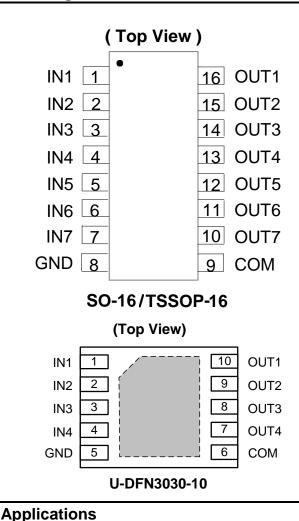

### **Pin Assignments**

Inputs Compatible with Popular Logic Types

Relay Driver Applications Stepping Motor Applications

Logic Level Shifter

### Features

- 4- and 7-Channel High Current Sink Drivers

- Supports up to 20V Output Pull-up Voltage

- Low Output VOL of 0.6V (Typical) with

- 100mA (Typ.) Current Sink per Channel at 3.3V Logic Input

- 140mA (Typ.) Current Sink per Channel at 5.0V Logic Input

Compatible to 3.3V and 5.0V Micro-Controllers and Logic

- Interface

- Internal Free-wheeling Diodes for Inductive Kick-back Protection

- Input Pull-down Resistors Allows Tri-Stating the Input Driver

Input RC-Snubber to Eliminate Spurious Operation in Noisy

- Environments

- ESD: 4kV HBM, 1kV CDM

- Available in 16-Pin SOIC, 16-Pin TSSOP and 10-Pin DFN3030

packages

- Available in "Green" Molding Compound (No Br, Sb)

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

- Notes: 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant.

- See http://www.diodes.com for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and</li>

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl <1000ppm antimony compounds.

#### 1 of 8

#### Downloaded From Oneyac.com

ULN2003V12, ULN2003F12

# **Functional Diagram**

ULN2003F12

### **Pin Descriptions**

| Pin Name    | Pin Number |         |            | Description                                     |  |

|-------------|------------|---------|------------|-------------------------------------------------|--|

| FIII Naille | SO16       | TSSOP16 | DFN3030-10 | Description                                     |  |

| IN1 ~ IN7   | 1~7        | 1~7     | 1~4        | Logic Input Pins IN1 through IN7                |  |

| GND         | 8          | 8       | 5          | Ground Reference Pin                            |  |

| COM         | 9          | 9       | 6          | Internal Free-Wheeling Diode Common Cathode Pin |  |

| OUT7 ~ OUT1 | 10~16      | 10~16   | 7~10       | Channel Output Pins OUT7 through OUT1           |  |

## **Functional Block Diagram (Single Channel)**

### **Absolute Maximum Ratings** (@T<sub>A</sub> = +25°C, unless otherwise specified.)

| Curracha a l         | Decomptor                                                     |                  | Rating  |            | Unit |

|----------------------|---------------------------------------------------------------|------------------|---------|------------|------|

| Symbol               | Parameter                                                     |                  | MIN MAX |            |      |

| V <sub>IN</sub>      | Pin2 IN1~IN7 to GND Voltage                                   |                  | -0.3    | 5.5        | V    |

| V <sub>OUT</sub>     | Pins OUT1~OUT7 to GND Voltage                                 |                  |         | 20         | V    |

| V <sub>COM</sub>     | Pin COM to GND Voltage                                        |                  |         | 20         | V    |

| 1                    | Max GND-Pin Continuous Current (+100°C $<$ T <sub>J</sub> < + | _                | 700     | mA         |      |

| I <sub>GND</sub>     | Max GND-Pin Continuous Current (TJ < +100°C)                  |                  | — 1.0   |            |      |

|                      |                                                               | 16 Pin – SOIC    | Т       | TBD        |      |

| PD                   | Total Device Power Dissipation at $T_A = +85^{\circ}C$        | 16 Pin – TSSOP   | Т       | TBD        |      |

|                      |                                                               | 10 Pin – DFN3030 | Т       | TBD        |      |

|                      | Thermal Resistance Junction-to-Ambient (Note 6)               | 16 Pin – SOIC    | Т       | TBD        |      |

| $\theta_{JA}$        |                                                               | 16 Pin – TSSOP   | Т       | BD         | °C/W |

|                      |                                                               | 10 Pin – DFN3030 | Т       | TBD        |      |

|                      |                                                               | 16 Pin – SOIC    | Т       | TBD        |      |

| $\theta_{\text{JC}}$ | Thermal Resistance Junction-to-Case (Note 7)                  | 16 Pin – TSSOP   | Т       | TBD<br>TBD |      |

|                      |                                                               | 10 Pin – DFN3030 | Т       |            |      |

| ESD                  | НВМ                                                           |                  | 4       | kV         |      |

| L3D                  | CDM —                                                         |                  |         |            | kV   |

| $T_{J}$              | Junction Temperature                                          | -55              | 150     | °C         |      |

| T <sub>STG</sub>     | Storage Temperature                                           |                  |         | 150        | °C   |

4. Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied.

Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

5. All voltage values are with respect to the emitter/substrate terminal E, unless otherwise noted.

6. Maximum power dissipation is a function of  $T_J(max)$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any allowable ambient temperature is  $P_D = (T_J(max) - T_A)/\theta_{JA}$ . Operating at the absolute maximum  $T_J$  of +150°C can affect reliability.

7. Maximum power dissipation is a function of  $T_J(max)$ ,  $\theta_{JC}$ , and  $T_A$ . The maximum allowable power dissipation at any allowable ambient temperature is  $P_D = (T_J(max) - T_C)/\theta_{JA}$ . Operating at the absolute maximum  $T_J$  of +150°C can affect reliability.

### Recommended Operating Conditions (@T<sub>A</sub> = +25°C, unless otherwise specified.)

| Symbol           | Parameter                                |             |   | TYP | Max                | Unit |

|------------------|------------------------------------------|-------------|---|-----|--------------------|------|

| Vout             | Channel Off-Stage Output Pull-Up Voltage |             |   | _   | 16                 | V    |

| V <sub>COM</sub> | COM Pin Voltage                          |             |   | _   | 16                 | V    |

| 1                | Der Channel Cantinuque Sink Current      | VINx = 3.3V | _ | _   | 100 <sup>(5)</sup> | m (  |

| IOUT(ON)         | Per Channel Continuous Sink Current      | VINx = 5.0V | _ | _   | 140 <sup>(5)</sup> | - mA |

| TJ               | Operating Junction Temperature           |             |   | _   | 125                | °C   |

# **Electrical Characteristics** ( $@T_A = +25^{\circ}C$ , unless otherwise specified.)

Specified over the recommended junction temperature range  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$  and over recommended operating conditions unless otherwise noted. Typical values are at  $T_J = +25^{\circ}C$ .

|                          | Parameter                                | Test conditions                                                                                                       | Min  | Тур. | Max  | Unit                                         |  |

|--------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|------|------|----------------------------------------------|--|

| INPUTS IN1 T             | THROUGH IN7 PARAMETERS                   |                                                                                                                       |      | •    | •    |                                              |  |

| V <sub>I(on)</sub>       | IN1~IN7 logic high input voltage         | $V_{CE} = 2V, I_C = 300mA$                                                                                            | 1.65 |      |      | V                                            |  |

| V <sub>I(OFF)</sub>      | IN1~IN7 logic low input voltage          | I <sub>1</sub> = 250μA, I <sub>C</sub> = 100mA                                                                        | _    |      | 0.6  | V                                            |  |

| I <sub>I(ON)</sub>       | IN1~IN7 ON state input current           | I <sub>F</sub> = 350mA                                                                                                | _    | 12   | 25   | uA                                           |  |

| I <sub>I(OFF)</sub>      | IN1~IN7 OFF state input leakage          |                                                                                                                       | _    |      | 250  | nA                                           |  |

| OUTPUTS O                | UT1 THROUGH OUT7 PARAMETERS              |                                                                                                                       |      | 1    | 1    | <u>.                                    </u> |  |

|                          |                                          | V <sub>INX</sub> = 3.3V, I <sub>OUTX</sub> = 20mA                                                                     |      | 0.12 | 0.15 |                                              |  |

|                          |                                          | V <sub>INX</sub> = 3.3V, I <sub>OUTX</sub> = 100mA                                                                    |      | 0.6  | 0.75 | v                                            |  |

| V <sub>OL(VCE-SAT)</sub> | OUT1~OUT7 low-level output voltage       | $V_{INX} = 5.0V, I_{OUTX} = 20mA$                                                                                     |      | 0.09 | 0.11 |                                              |  |

|                          |                                          | V <sub>INX</sub> = 5.0V, I <sub>OUTX</sub> = 140mA                                                                    |      | 0.6  | 0.75 |                                              |  |

| I <sub>OUT(ON)</sub>     | OUT1~OUT7 ON-state continuous current at | $V_{INX} = 3.3V, V_{OUTX} = 0.6V$                                                                                     | 80   | 100  | _    | ~ ^                                          |  |

|                          | $V_{OUTX} = 0.6V$                        | V <sub>INX</sub> = 5.0V, V <sub>OUTX</sub> = 0.6V                                                                     | 95   | 140  |      | mA                                           |  |

| I <sub>OUT(ON)</sub>     | OUT1~OUT7 OFF-state leakage current      | $V_{INX} = 0V, V_{OUTX} = V_{COM} = 16V$                                                                              |      | 0.5  | _    | uA                                           |  |

| SWITCHING I              | PARAMETERS                               |                                                                                                                       |      | •    | •    |                                              |  |

| t <sub>PHL</sub>         | OUT1~OUT7 logic high propagation delay   | $\begin{split} V_{\text{INX}} &= 3.3 V, \ V_{\text{pull-up}} = 12 V, \\ R_{\text{pull-up}} &= 1 k \Omega \end{split}$ |      | 50   | 70   | ns                                           |  |

| t <sub>PLH</sub>         | OUT1~OUT7 logic low propagation delay    | $\begin{split} V_{\text{INX}} &= 3.3 V,  V_{\text{pull-up}} = 12 V, \\ R_{\text{pull-up}} &= 1 k \Omega \end{split}$  |      | 121  | 140  | ns                                           |  |

| t <sub>CHANNEL</sub>     | Channel to channel delay                 | Over recommended operating conditions<br>and with same test conditions on<br>channels.                                |      | 15   | 50   | ns                                           |  |

| R <sub>PD</sub>          | IN1~IN7 input pull-down resistance       | _                                                                                                                     | 210k | 300k | 390k | Ω                                            |  |

| ζ                        | IN1~IN7 input filter time constant       | _                                                                                                                     |      | 9    |      | ns                                           |  |

| Cout                     | OUT1~OUT7 output capacitance             | $V_{INX} = 3.3V, V_{OUTX} = 0.4V$                                                                                     |      | 15   |      | pF                                           |  |

|                          | LING DIODE PARAMETERS                    |                                                                                                                       |      | •    |      |                                              |  |

| VF                       | Forward voltage drop                     | $I_{F-peak} = 140mA, VF = V_{OUTx} - V_{COM}$                                                                         |      | 1.2  | _    | V                                            |  |

| I <sub>F-peak</sub>      | Diode peak forward current               | —                                                                                                                     |      | 140  |      | mA                                           |  |

### **Performance Characteristics**

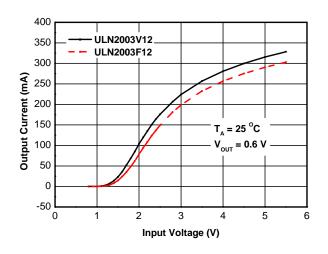

Output Current vs. Input Voltage (One Darlington)

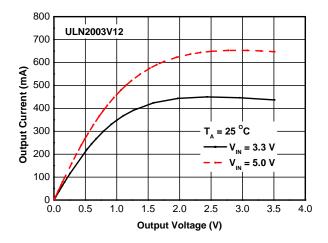

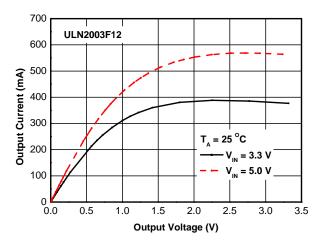

#### Output Current vs. Output Voltage

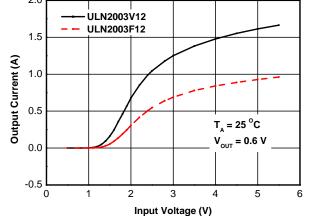

Output Current vs. Input Voltage (All Darlingtons in Parallel)

## Performance Characteristics (Cont.)

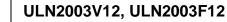

### Output Current vs. Output Voltage

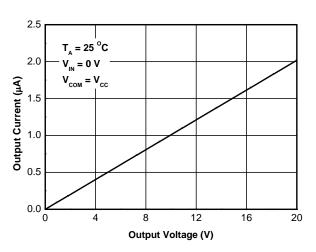

Diode Forward Voltage vs. Diode Forward Current

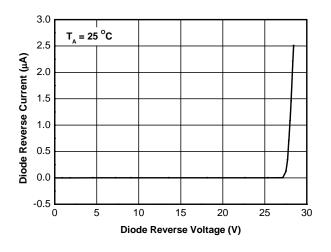

Diode Reverse Current vs. Diode Reverse Voltage

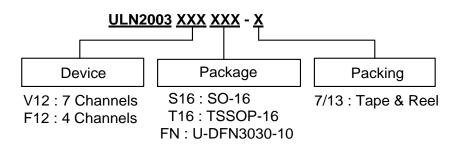

## **Ordering Information**

|      |                  |              | Packaging  | 7"/13" Tape and Reel |                    |  |

|------|------------------|--------------|------------|----------------------|--------------------|--|

|      | Device           | Package Code | (Note 11)  | Quantity             | Part Number Suffix |  |

| Pb.  | ULN2003V12S16-13 | S16          | SO-16      | 2,500/Tape & Reel    | -13                |  |

| PD   | ULN2003V12T16-13 | T16          | TSSOP-16   | 2,500/Tape & Reel    | -13                |  |

| (Pb) | ULN2003F12FN-7   | FN           | DFN3030-10 | 3,000/Tape & Reel    | -7                 |  |

Pad layout as shown on Diodes Inc. suggested pad layout document AP02001, which can be found on our website at http://www.diodes.com/datasheets/ap02001.pdf.

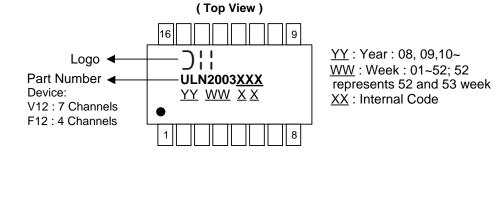

## **Marking Information**

Note:

#### (1) SO-16 and TSSOP-16

(2) DFN3030-10

( Top View ) XX YWX

$\frac{XX}{Y} : \text{Identification Code}$   $\frac{Y}{Y} : \text{Year : } 0 \sim 9$   $\frac{W}{Y} : \text{Week : } A \sim Z : 1 \sim 26 \text{ week;}$   $a \sim z : 27 \sim 52 \text{ week; } z \text{ represents}$  52 and 53 week X : Internal Code

| Part Number    | Package    | Identification Code |  |  |

|----------------|------------|---------------------|--|--|

| ULN2003F12FN-7 | DFN3030-10 | A3                  |  |  |

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2015, Diodes Incorporated

www.diodes.com

单击下面可查看定价,库存,交付和生命周期等信息

>>Diodes Incorporated(达迩科技(美台))