#### HDMI 2.0 6Gbps Limiting ReDriver with High EQ, Low Jitter and DP++ Level Shifter

#### Description

PI3HDX1204B1 is a ReDriver<sup>™</sup> device suitable for HDMI 2.0 6.0 Gbps with programmable high equalization, output swing and de-emphasis control mode. The maximum EQ of the device is +22dB @ 6Gbps and it can deliver 2x better additive jitter performance compared to the traditional ReDriver devices.

In addition, the device can support the Dual-Mode DisplayPort Level Shifter application for HDMI 2.0 compliant output signals.

The device's EQ/SW/De-emphasis settings can be configured by the pin-strapping or the I2C programming to optimize differential signal performance over various physical media.

#### Features

- → HDMI 2.0 compliant Limiting-type Redriver to compensate high insertion loss of the long TMDS signal transmission

- → Support Dual-mode DP HBR3 to HDMI 2.0 Level Shifting

- → Double the jitter performance than conventional CMOSprocess redriver

- → Input EQ support 16 steps up to +22.2dB @ 3GHz ( 6 Gbps ), 4 steps De-emphasis and 4 steps output voltage swing setting

- → Independent each channel configuration for Equalization, Output Swing and De-emphasis

- → Built-in channel activity detector with selectable input termination between 50 $\Omega$  to V<sub>DD</sub> and 200k $\Omega$  to V<sub>DD</sub>

- $\rightarrow$  Pin Strap and I<sup>2</sup>C selectable device programming mode support

- → Supply Voltage: 3.3V

- → Industrial Temperature Range: -40°C to 85°C

- → Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- → Halogen and Antimony Free. "Green" Device (Note 3)

- → For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please contact us or your local Diodes representative.

https://www.diodes.com/quality/product-definitions/

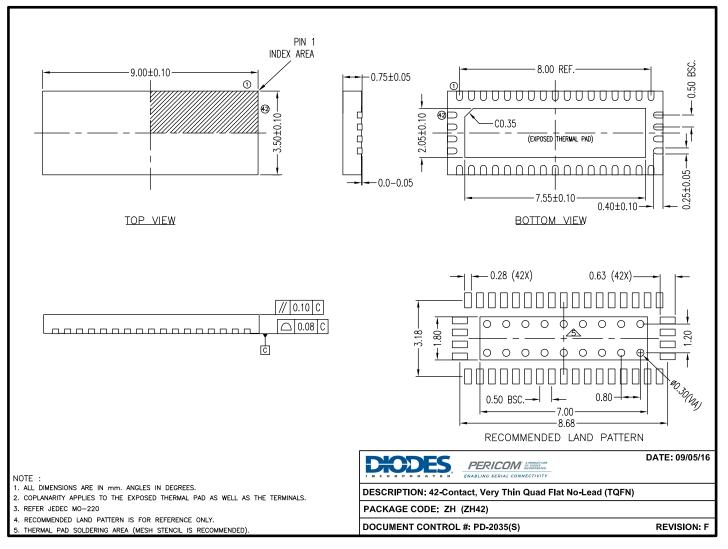

→ Packaging (Pb-free & Green): 42-contact TQFN (3.4x9mm)

#### Applications

- → Notebooks, Desktops and AIO PCs

- → HDMI Active cables

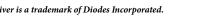

- → Internal board connection inside Video system

ReDriver is a trademark of Diodes Incorporated.

| Ordering Number   | Package<br>Code | Package Description                       |

|-------------------|-----------------|-------------------------------------------|

| PI3HDX1204B1ZHEX  | ZH              | 42-pin TQFN (3.5x9mm)                     |

| PI3HDX1204B1ZHIEX | ZH              | Industrial-temp, 42-pin TQFN<br>(3.5x9mm) |

Notes:

<1000ppm antimony compounds.

4. E = Pb-free and Green, I=Industrial

5. X suffix = Tape/Reel

1

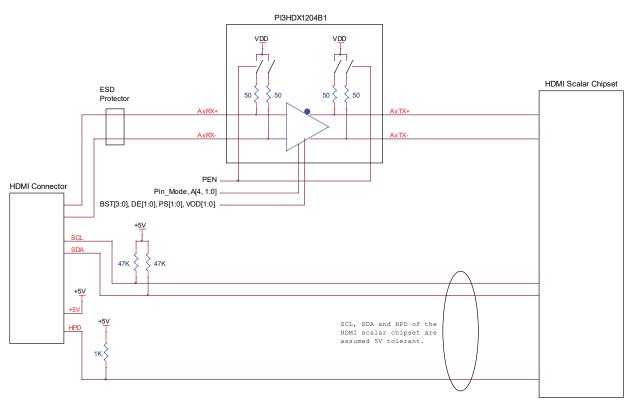

Figure 1-1 DP++ to HDMI 2.0 Level Shifter

Figure 1-2 HDMI 2.0 Active Cable Application

Figure 1-3 TMDS Connection Inside TV

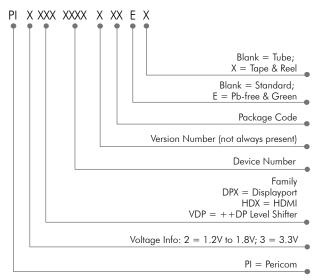

### Ordering Information

| oHS 2) & 2015/863/1  | EU (RoHS 3  | 3) compliant.   |             |           |          |

|----------------------|-------------|-----------------|-------------|-----------|----------|

| See https://www.diod | les.com/qu  | ality/lead-free | e/ for more | e informa | tion abo |

| odes Incorporated's  | definitions | of Halogen-     | and Antii   | nony-fre  | e, "Gree |

| id-free.             |             | •               |             |           |          |

|                      |             |                 |             |           |          |

<sup>1.</sup> No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (Rol

<sup>2.</sup> S out Dio

en" and Lea 3. Halogen- and Antimony-free "Green" products are defined as those which contain

<sup>&</sup>lt;900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and

## 2. General Information

| 2.1 Revi  | 2.1 Revision History |                                                                                                                                                                      |  |  |  |  |

|-----------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Date      | Revision             | Description                                                                                                                                                          |  |  |  |  |

| July 2016 | _                    | Application chapter: Updated reference schematics in application chapter. Add load switch AP2151 requirement to protect sink to source-side devices back drive.      |  |  |  |  |

| Sep 2016  | _                    | Finial datasheet release with package pin-out typo fixed - pin name 30, 37 and 38                                                                                    |  |  |  |  |

| Dec 2016  | -                    | Correct typos by removing Threshold detector VTH1/0, Output Swing Control VOD0 table in the func-<br>tional description. Those pins do not bond out in PI3HDX1204B1. |  |  |  |  |

| Jan 2017  | _                    | In Fig 6-6 sink application circuit, removed load switch and regulator.                                                                                              |  |  |  |  |

| Oct 2017  | -                    | Ch2. Similar product comparison table added.                                                                                                                         |  |  |  |  |

| Nov 2019  | 1                    | Updated Section 1 Description<br>Updated Section 6.2 Recommended Operation Conditions<br>Updated Section 6.3.5 Switching Characteristics                             |  |  |  |  |

| Nov 2019  | 2                    | Updated Section 5.1 Address Assignment                                                                                                                               |  |  |  |  |

| Dec 2019  | 3                    | Updated Section 6.3.2 Power Dissipation                                                                                                                              |  |  |  |  |

| Nov 2020  | 4                    | Updated Section 4.2.5 Output Voltage Swing Setting                                                                                                                   |  |  |  |  |

## 2.2 Similar Products Comparison

|                                | PI3HDX1204B1                                                 | PI3HDX1204E                                                                        |  |

|--------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------|--|

| Redriver Type                  | Limiting type                                                | Linear type                                                                        |  |

| EQ at 6Gbps                    | 22 dB                                                        | 10 dB                                                                              |  |

| TMDS Tr/Tf time                | Tr adjustment for short pre-channel trace application        | nel trace Followed Source Rising/Falling time                                      |  |

| Output TMDS peak-to-peak Swing | Output Swing Amplitude / Pre-Emphasis control. Blocking type | 1 0 1                                                                              |  |

| DDC Switch/Buffer              | No                                                           | No                                                                                 |  |

| HDMI1.4/2.0 Type ID            | No                                                           | No                                                                                 |  |

| Ioff Protection                | External Power Switch                                        | External Power Switch                                                              |  |

| Data Rate (Gbps)               | 6 Gbps                                                       | 6 Gbps                                                                             |  |

| Application                    | Near to Source-side device                                   | Near to Sink-side device                                                           |  |

| Availability                   | Production.                                                  | Production                                                                         |  |

|                                |                                                              | Place close to Sink Receiver, let Adaptive EQ<br>Rx-DFE to control channel signals |  |

#### Contents

| 2. | General Information                                      |     |

|----|----------------------------------------------------------|-----|

|    | 2.1 Revision History                                     |     |

|    | 2.2 Similar Products Comparison                          |     |

| 3. | Pin Configuration                                        | .4  |

| 4. | Functional Description                                   | . 6 |

|    | 4.1 Functional Block Diagram                             |     |

|    | 4.2 Function Settings                                    |     |

|    | 4.3 Output Eye Diagram Changes with Different EQ Setting |     |

| 5. | I2C Programming                                          |     |

|    | 5.1 Address Assignment                                   |     |

|    | 5.2 I <sup>2</sup> C Data Transfer Sequence              |     |

| 6. | Electrical                                               |     |

|    | 6.1 Absolute Maximum Ratings                             |     |

|    | 6.2 Recommended Operation Conditions                     |     |

|    | 6.3 DC/AC Characteristics                                |     |

|    | 6.4 I2C Bus                                              |     |

| 7. | Application/Implementation                               |     |

|    | 7.1 Source Application                                   |     |

|    | 7.2 Sink Application                                     |     |

|    | 7.3 DC/AC-coupled Application                            |     |

|    | 7.4 Product Layout Guideline                             | 24  |

|    | 7.5 General Layout Guideline                             |     |

|    | 7.6 CTS Test Report                                      |     |

| 8. | Mechanical/Packaging Information                         | 35  |

|    | 8.1 Mechanical                                           | 35  |

|    | 8.2 Part Marking Information                             |     |

|    | 8.3 Tape & Reel Materials and Design                     |     |

| 8. | Important Notice                                         | 41  |

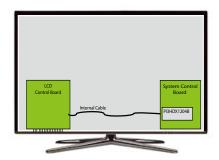

## 3. Pin Configuration

Figure 3-1 Package Pin-out (Top-Side View)

## PI3HDX1204B1

| Table 3-1. | Pin Description | ı |

|------------|-----------------|---|

|------------|-----------------|---|

| Pin #                       | Pin Name         | Туре | Description                                                                                                                                                                                        |

|-----------------------------|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Signals                |                  |      |                                                                                                                                                                                                    |

| 4<br>5                      | A0RX+<br>A0RX-   | Ι    | TMDS inputs for Channel A0, with internal 50 $\Omega$ Pull-Up and ~200k $\Omega$ Pull-Up otherwise.                                                                                                |

| 35<br>34                    | A0TX+,<br>A0TX-  | 0    | TMDS outputs for Channel A0, with internal 50 $\Omega$ Pull-Up and ~2k $\Omega$ Pull-Up otherwise.                                                                                                 |

| 7<br>8                      | A1RX+,<br>A1RX-  | Ι    | TMDS inputs for Channel A1, with internal 50 $\Omega$ Pull-Up and ~200k $\Omega$ Pull-Up otherwise.                                                                                                |

| 32<br>31                    | A1TX+,<br>A1TX-  | 0    | TMDS outputs for Channel A1, with internal 50 $\Omega$ Pull-Up and ~2k $\Omega$ Pull-Up otherwise.                                                                                                 |

| 10<br>11                    | A2RX+,<br>A2RX-  | Ι    | TMDS inputs for Channel A2, with internal 50 $\Omega$ Pull-Up and ~200k $\Omega$ Pull-Up otherwise.                                                                                                |

| 29<br>28                    | A2TX+,<br>A2TX-  | 0    | TMDS outputs for Channel A2, with internal 50 $\Omega$ Pull-Up and ~2k $\Omega$ Pull-Up otherwise.                                                                                                 |

| 13<br>14                    | A3RX+,<br>A3RX-  | Ι    | TMDS inputs for Channel A3, with internal 50 $\Omega$ Pull-Up and ~200k $\Omega$ Pull-Up otherwise.                                                                                                |

| 26<br>25                    | A3TX+,<br>A3TX-  | 0    | TMDS outputs for Channel A3, with internal 50 $\Omega$ Pull-Up and ~2k $\Omega$ Pull-Up otherwise.                                                                                                 |

| Control Signa               | ls               |      | ·                                                                                                                                                                                                  |

| 19                          | SCL              | Ι    | I <sup>2</sup> C Clock input.                                                                                                                                                                      |

| 18                          | SDA              | I/O  | I <sup>2</sup> C Data input/output.                                                                                                                                                                |

| 17,<br>16,<br>22            | A4,<br>A1,<br>A0 | Ι    | I <sup>2</sup> C programmable address bits, with internal 100k $\Omega$ Pull-Up.                                                                                                                   |

| 20                          | PEN              | Ι    | Power Enable with internal 100KΩ Pull-Up                                                                                                                                                           |

| 21                          | Pin_Mode         | Ι    | Input with internal 100k $\Omega$ Pull-Up. When HIGH, each channel is programmed by the external pin voltage. When LOW, each channel is programmed by the data stored in the I <sup>2</sup> C bus. |

| 42<br>41<br>40<br>39        | BST[3:0]         | Ι    | Inputs with internal 100k $\Omega$ Pull-Up. This pins set the amount of Equalizer Boost in all channel when Pin mode is HIGH.                                                                      |

| 23                          | VOD1             | Ι    | Inputs with internal 100k $\Omega$ Pull-Up. This pin sets the output Voltage Level in all channel when Pin mode is HIGH.                                                                           |

| 1<br>2                      | DE[1:0]          | Ι    | Inputs with internal 100k $\Omega$ Pull-Up. This pins set the output De-Emphasis Level in all channel when Pin_Mode is HIGH.                                                                       |

| 38, 37                      | NC               | NC   | No Connect                                                                                                                                                                                         |

| Power Pins                  | ·                |      |                                                                                                                                                                                                    |

| 6, 12, 30,<br>Center Pad    | GND              | GND  | Ground Pins                                                                                                                                                                                        |

| 3, 9, 15, 24,<br>27, 33, 36 | V <sub>DD</sub>  | PWR  | Power Supply Pins                                                                                                                                                                                  |

## 4. Functional Description

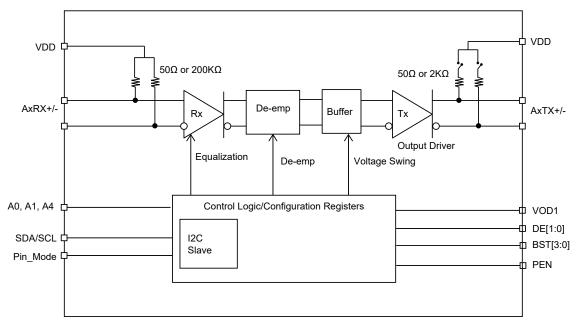

### 4.1 Functional Block Diagram

Figure 4-1 Functional Block Diagram

### 4.2 Function Settings

#### 4.2.1 Output Termination Detector

On power up or when PEN becomes true, the output resistance is set to 2K ohms, and the input resistance is set to 200K ohms. The device continually looks to detect an external 50 ohm termination resistor on a per channel basis. If no 50 ohms is detected in the first 5ms of time, the channel is continually polled with 5ms detection cycle until detection occurs.

#### 4.2.2 Power Enable Function

One pin control or I2C control, when PEN is set to low, the IC goes into power down mode, both input and output termination set to 200K and 2K respectively. Individual Channel Enabling is done through the I2C register programming.

#### 4.2.3 Equalization Setting

BST[3:0] are the selection pins for the equalization selection for each channel.

## PI3HDX1204B1

| 14010 1 1. | Tuble 4 1. Tuble 1. Equalization betting |      |      |              |              |  |  |

|------------|------------------------------------------|------|------|--------------|--------------|--|--|

| BST3       | BST2                                     | BST1 | BST0 | 6Gbps (3GHz) | 8Gbps (4GHz) |  |  |

| 0          | 0                                        | 0    | 0    | 0.25 dB      | 0.4 dB       |  |  |

| 0          | 0                                        | 0    | 1    | 0.8 dB       | 1.1 dB       |  |  |

| 0          | 0                                        | 1    | 0    | 1.1 dB       | 1.6 dB       |  |  |

| 0          | 0                                        | 1    | 1    | 2.2 dB       | 3.1 dB       |  |  |

| 0          | 1                                        | 0    | 0    | 4.1 dB       | 5.4 dB       |  |  |

| 0          | 1                                        | 0    | 1    | 7.1 dB       | 8.9 dB       |  |  |

| 0          | 1                                        | 1    | 0    | 9.0 dB       | 10.8 dB      |  |  |

| 0          | 1                                        | 1    | 1    | 10.3 dB      | 12.2 dB      |  |  |

| 1          | 0                                        | 0    | 0    | 11.8 dB      | 13.8 dB      |  |  |

| 1          | 0                                        | 0    | 1    | 13.9 dB      | 15.8 dB      |  |  |

| 1          | 0                                        | 1    | 0    | 15.3 dB      | 17.3 dB      |  |  |

| 1          | 0                                        | 1    | 1    | 16.9 dB      | 19.0 dB      |  |  |

| 1          | 1                                        | 0    | 0    | 17.9 dB      | 20.0 dB      |  |  |

| 1          | 1                                        | 0    | 1    | 19.2 dB      | 21.3 dB      |  |  |

| 1          | 1                                        | 1    | 0    | 20.5 dB      | 22.6 dB      |  |  |

| 1          | 1                                        | 1    | 1    | 22.2 dB      | 24.3 dB      |  |  |

#### Table 4-1. Table 1. Equalization Setting

#### 4.2.4 Output De-emphasis Setting

De-emphasis Setting: DE[1:0] are the selection bits for the de-emphasis value.

#### Table 4-2. Output De-emphasis Setting

| DE1 | DE0 | De-emphasis |

|-----|-----|-------------|

| 0   | 0   | 0 dB        |

| 0   | 1   | -0.5 dB     |

| 1   | 0   | -0.7 dB     |

| 1   | 1   | -1.0 dB     |

#### 4.2.5 Output Voltage Swing Setting

Swing Setting: VOD1, VOD0 are the selection bits for the output swing voltage value.

#### Table 4-3. Output Voltage Swing Setting

| VOD1 | VOD0 | Output Voltage Swing |

|------|------|----------------------|

| 0    | 0    | 0.8 Vppd             |

| 0    | 1    | 0.95 Vppd            |

| 1    | 0    | 1.15 Vppd            |

| 1    | 1    | 1.3 Vppd             |

PI3HDX1204B1

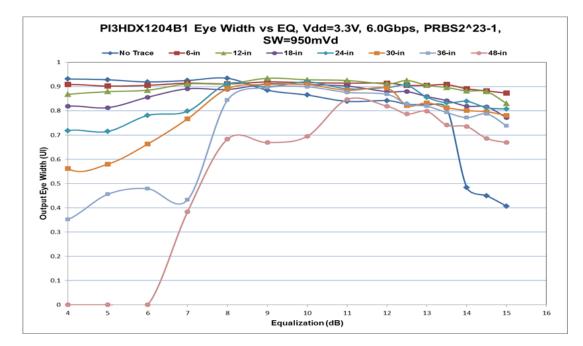

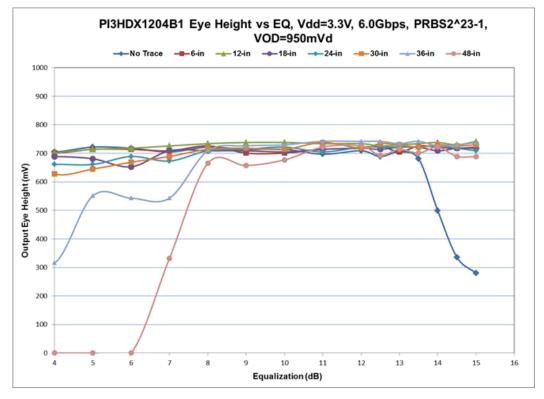

## 4.3 Output Eye Diagram Changes with Different EQ Setting

Figure 4-2 Eye Width vs. Input Equalization at Different Input trace Lengths

PI3HDX1204B1

Figure 4-3 Eye Height vs. Input Equalization at Different Input trace Lengths

## PI3HDX1204B1

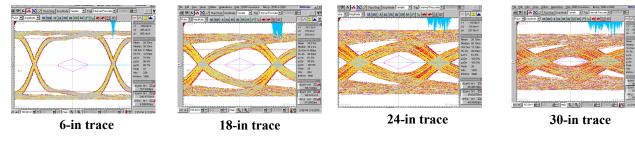

### Table 4-4. Input Eye Diagram without Trace Boards

36-in trace

Table 4-5. Output Eye Opening with Trace and Different EQ Settings, 6.0 Gbps, Vdd=3.3V, 25C

30-in trace EQ=0111(10.3dB)

12-in trace EQ=0100(4.1dB)

48-in trace EQ=1000(11.8dB)

Note: Trace Card Loss Informations is shown below

| Note: Trace Card Loss mornations is shown below. |        |       |       |  |  |  |

|--------------------------------------------------|--------|-------|-------|--|--|--|

| Frequency                                        | 3 GHz  | 6GHz  | Units |  |  |  |

| 6 inch Input Trace                               | -2.1   | -4    | dB    |  |  |  |

| 12 inch Input Trace                              | -4     | -7.5  | dB    |  |  |  |

| 18 inch Input Trace                              | -6.1   | -11.3 | dB    |  |  |  |

| 30 inch Input Trace                              | -10.14 | -18   | dB    |  |  |  |

| 36 inch Input Trace                              | -12.13 | -22   | dB    |  |  |  |

| 48 inch Input Trace                              | -16.42 | -29   | dB    |  |  |  |

18-in trace EQ=0110(9.0dB)

24-in trace EQ=0111(10.3dB)

## 5. I2C Programming

## 5.1 Address Assignment

| A6 | A5 | A4                       | A3 | A2 | A1                               | A0                                  | R/W      |

|----|----|--------------------------|----|----|----------------------------------|-------------------------------------|----------|

| 1  | 1  | Controlled by<br>Pin# A4 | 0  | 0  | Program Controlled by<br>Pin# A1 | Program<br>Controlled by<br>Pin# A0 | 1=R, 0=W |

#### **BYTE 0: Reserved**

| BYTE 1 |      |                    |                  |         |

|--------|------|--------------------|------------------|---------|

| Bit    | Туре | Power up condition | Control affected | Comment |

| [7:0]  | R    | 0                  | Not used         |         |

| BYTE 2 |      |                                 |                  |            |  |

|--------|------|---------------------------------|------------------|------------|--|

| Bit    | Туре | Power up condition              | Control affected | Comment    |  |

| 7      | R/W  | Latch from PEN input at startup | Ch3 Enable       |            |  |

| 6      | R/W  |                                 | Ch2 Enable       | 1 Eachla   |  |

| 5      | R/W  |                                 | Ch1 Enable       | 1 = Enable |  |

| 4      | R/W  |                                 | Ch0 Enable       |            |  |

| [3:0]  | R/W  | 0                               | Not used         |            |  |

| BYTE 3 |      |                                    |                  |         |

|--------|------|------------------------------------|------------------|---------|

| Bit    | Туре | Power up condition                 | Control affected | Comment |

| 7      | R/W  |                                    | BST3 Ch1         |         |

| 6      | R/W  |                                    | BST2 Ch1         |         |

| 5      | R/W  | Lately from DCT[2,0] at the streng | BST1 Ch1         |         |

| 4      | R/W  |                                    | BST0 Ch1         |         |

| 3      | R/W  | Latch from BST[3:0] at startup     | BST3 Ch0         |         |

| 2      | R/W  |                                    | BST2 Ch0         |         |

| 1      | R/W  |                                    | BST1 Ch0         |         |

| 0      | R/W  |                                    | BST0 Ch0         |         |

| BYTE 4 |      |                                |                  |         |

|--------|------|--------------------------------|------------------|---------|

| Bit    | Туре | Power up condition             | Control affected | Comment |

| 7      | R/W  |                                | BST3 Ch3         |         |

| 6      | R/W  |                                | BST2 Ch3         |         |

| 5      | R/W  | _                              | BST1 Ch3         |         |

| 4      | R/W  |                                | BST0 Ch3         |         |

| 3      | R/W  | Latch from BST[3:0] at startup | BST3 Ch2         |         |

| 2      | R/W  | -                              | BST2 Ch2         |         |

| 1      | R/W  |                                | BST1 Ch2         |         |

| 0      | R/W  |                                | BST0 Ch2         |         |

| BYTE 5 |      |                            |                  |         |

|--------|------|----------------------------|------------------|---------|

| Bit    | Туре | Power up condition         | Control affected | Comment |

| 7      | R/W  | Latch from VOD1 at startup | VOD1 Ch3         |         |

| 6      | R/W  | VOD0 = "1"                 | VOD0 Ch3         |         |

| 5      | R/W  | Latch from VOD1 at startup | VOD1 Ch2         |         |

| 4      | R/W  | VOD0 = "1"                 | VOD0 Ch2         |         |

| 3      | R/W  | Latch from VOD1 at startup | VOD1 Ch1         |         |

| 2      | R/W  | VOD0 = "1"                 | VOD0 Ch1         |         |

| 1      | R/W  | Latch from VOD1 at startup | VOD1 Ch0         |         |

| 0      | R/W  | VOD0 = "1"                 | VOD0 Ch0         |         |

| BYTE 6 |      |                               |                  |         |

|--------|------|-------------------------------|------------------|---------|

| Bit    | Туре | Power up condition            | Control affected | Comment |

| 7      | R/W  |                               | DE1 Ch3          |         |

| 6      | R/W  |                               | DE0 Ch3          |         |

| 5      | R/W  | Latch from DE[1:0] at startup | DE1 Ch2          |         |

| 4      | R/W  |                               | DE0 Ch2          |         |

| 3      | R/W  |                               | DE1 Ch1          |         |

| 2      | R/W  |                               | DE0 Ch1          |         |

| 1      | R/W  |                               | DE1 Ch0          |         |

| 0      | R/W  |                               | DE0 Ch0          |         |

**BYTE 7-9: Reserved**

**BYTE A-F: Reserved**

## PI3HDX1204B1

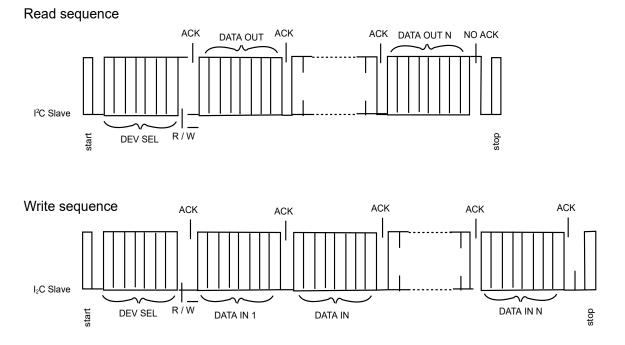

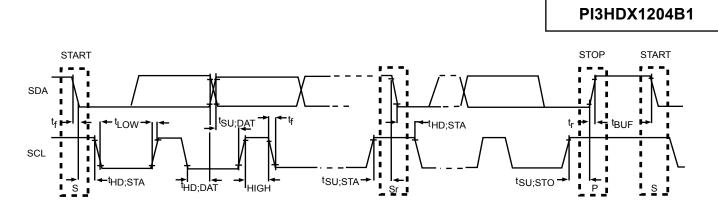

## 5.2 I<sup>2</sup>C Data Transfer Sequence

Notes:

- 1. only block read and block write from the lowest byte are supported for this application.

- 2. for some I2C application, an offset address byte will be presented at the second byte in write command, which is called dummy byte here and will be simply ignored in this application for correct interoperation.

## 6. Electrical

### 6.1 Absolute Maximum Ratings

| -3.8V |

|-------|

| 3.8V  |

| 5mA   |

| 2.1W  |

| -2 kV |

| 50 °C |

|       |

Note

(1) Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## 6.2 Recommended Operation Conditions

| Parameter                                          |                                                    |     | Тур. | Max | Units |  |

|----------------------------------------------------|----------------------------------------------------|-----|------|-----|-------|--|

| Power supply voltage (VDD to GND) <sup>(1)</sup>   |                                                    |     | 3.3  | 3.6 | V     |  |

| I2C (SDA, SCL)                                     |                                                    |     |      | 3.6 | V     |  |

| Supply Noise Tolerance up to 25 MHz <sup>(2)</sup> | Supply Noise Tolerance up to 25 MHz <sup>(2)</sup> |     |      | 100 | mVp-p |  |

| A militare Transmission                            | Industrial Temperature Range                       | -40 |      | 85  | °C    |  |

| Ambient Temperature                                | Commercial Temperature Range                       | 0   |      | 70  |       |  |

Note

(1) Typical parameters are measured at VDD =  $3.3 \pm 0.3$ V, TA =  $25^{\circ}$ C. They are for the reference purposes, and are not production-tested

(2) Allow supply noise (mVp-p sine wave) under typical condition

## 6.3 DC/AC Characteristics

#### 6.3.1 LVCMOS DC Specifications

| Symbol           | Parameter                           | Conditions | Min.             | Тур. | Max                      | Unit |

|------------------|-------------------------------------|------------|------------------|------|--------------------------|------|

| V <sub>IH</sub>  | DC input logic high                 |            | $V_{DD}/2 + 0.7$ |      | $V_{DD} + 0.3$           | V    |

| V <sub>IL</sub>  | DC input logic low                  |            | -0.3             |      | V <sub>DD</sub> /2 - 0.7 | V    |

| V <sub>OH</sub>  | At $I_{OH}$ = -200 $\mu$ A          |            | $V_{DD} + 0.2$   |      |                          | V    |

| V <sub>OL</sub>  | At $I_{OL} = -200 \mu A$            |            |                  |      | 0.2                      | V    |

| V <sub>hys</sub> | Hysteresis of Schmitt trigger input |            | 0.8              |      |                          | V    |

#### 6.3.2 Power Dissipation

| Symbol           | Parameter                | Conditions                                                         | Min. | Тур. | Max. | Units |

|------------------|--------------------------|--------------------------------------------------------------------|------|------|------|-------|

| I <sub>max</sub> |                          | PEN = 1, EQ = 0dB, De-emphasis =<br>0dB, All 4 channels 0.8V Swing |      | 265  | 325  | mA    |

|                  | Supply Current           | PEN = 1, EQ = 0dB, De-emphasis =<br>0dB, All 4 channels 1.3V Swing |      | 300  | 350  | mA    |

| I <sub>DDQ</sub> | Quiescent Supply Current | PEN=0, high speed TMDS channels disabled                           |      | 0.3  |      | mA    |

#### 6.3.3 Package Power Ratings

| Package            | Theta Ja(still air) (°C/W) | Theta Jc (°C/W) | Max. Power Dissipation Rating (Ta $\leq$ 70°) |

|--------------------|----------------------------|-----------------|-----------------------------------------------|

| 42-pin TQFN (ZH42) | 33.69                      | 15.17           | 1.63W                                         |

#### 6.3.4 TMDS Differential Pins

| Symbol             | Parameter                              | Conditions                    | Min.                 | Тур. | Max.                 | Units |

|--------------------|----------------------------------------|-------------------------------|----------------------|------|----------------------|-------|

| V <sub>OH</sub>    | Single-ended High Level Output Voltage |                               | V <sub>DD</sub> -10  |      | V <sub>DD</sub> +10  | mV    |

| VOL                | Single-ended Low Level Output Voltage  | VDD = 3.3 V,<br>Rout = 50 Ohm | V <sub>DD</sub> -600 |      | V <sub>DD</sub> -400 | mV    |

| V <sub>swing</sub> | Output Voltage Swing                   |                               | 700                  |      | 1300                 | mVppd |

| R <sub>T</sub>     | Input Termination Resistance           | $V_{IN} = 2.9V$               | 45                   | 50   | 55                   | Ohm   |

| I <sub>OZ</sub>    | Leakage Current with Hi-Z I/O          | V <sub>DD</sub> = 3.6V        |                      |      | 10                   | uA    |

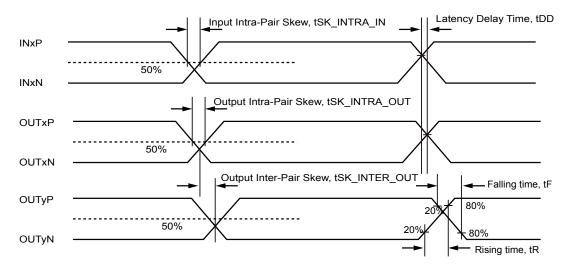

#### 6.3.5 Switching Characteristics

| Symbol                | Parameter                                       | Conditions                                | Min. | Тур. | Max. | Units |

|-----------------------|-------------------------------------------------|-------------------------------------------|------|------|------|-------|

| T <sub>pd</sub>       | Propagation Delay                               |                                           |      |      | 2000 | ps    |

| T <sub>r</sub>        | Tx Signal Rise Time (20% - 80%)                 | VDD = 3.3V, RT = 50                       |      | 40   |      | ps    |

| T <sub>f</sub>        | Tx Signal Fall Time (80% - 20%)                 | Ohm, Pre-/De-emp = $0 \text{ dB}$         |      | 40   |      | ps    |

| T <sub>sk(p)</sub>    | Pulse Skew                                      |                                           |      | 10   | 50   | ps    |

| T <sub>sk(D)</sub>    | Intra-pair Differential Skew                    |                                           |      | 23   | 50   | ps    |

| T <sub>sk(O)</sub>    | Inter-pair Differential Skew                    |                                           |      |      | 100  | ps    |

| T <sub>Jit-Clk</sub>  | Peak-to-peak Output Jitter for Clock<br>channel | Pre-/De-emp = 0 dB<br>Data Input = 6 Gbps |      | 15   | 30   | ps    |

| T <sub>Jit-Data</sub> | Peak-to-peak Output Jitter for Data channels    | HDMI Pattern, Clock<br>input = 150 MHz    |      | 18   | 50   | ps    |

| t <sub>sx</sub>       | Select to switch Output                         |                                           |      |      | 10   | ns    |

| t <sub>en</sub>       | Enable Time                                     |                                           |      |      | 200  | ns    |

| t <sub>dis</sub>      | Disable Time                                    |                                           |      |      | 10   | ns    |

#### 6.3.6 Signal Detector

| Symbol | Parameter                              | Conditions             | Min. | Тур. | Max. | Units |

|--------|----------------------------------------|------------------------|------|------|------|-------|

| Vth+   | Assert Threshold of Signal Detector    | Signal swing @ 3GHz    | 130  |      | 210  | mVppd |

| Vth-   | De-assert Threshold of Signal Detector | Signal swing @ 100 MHz | 30   |      | 110  | mVppd |

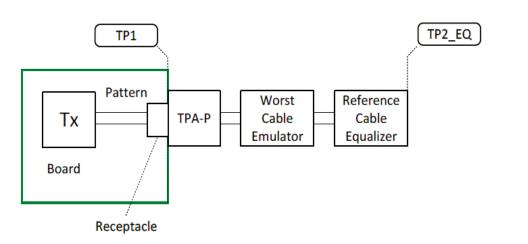

Figure 6-1 Electrical Parameter Test Setup

Figure 6-2 Intra and Inter-pair Differential Skew Definition

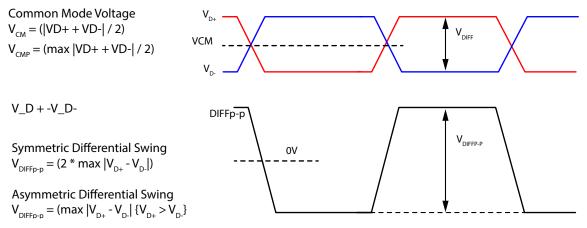

Figure 6-3 Definition of Peak-to-peak Differential Voltage

PI3HDX1204B1

Figure 6-5 HDMI Sink Test Point for Eye Diagram

## PI3HDX1204B1

#### 6.4 I2C Bus

| Symbol          | Parameter                                                                                            | Conditions                    | Min.                        | Тур. | Max                         | Units |

|-----------------|------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------|------|-----------------------------|-------|

| VDD             | Nominal Bus Voltage                                                                                  |                               | 3.0                         |      | 3.6                         | V     |

| Freq            | Bus Operation Frequency                                                                              |                               |                             |      | 400                         | kHz   |

| V <sub>IH</sub> | DC input logic high                                                                                  |                               | V <sub>DD</sub> /2<br>+ 0.7 |      | V <sub>DD</sub> + 0.3       | V     |

| V <sub>IL</sub> | DC input logic low                                                                                   |                               | -0.3                        |      | V <sub>DD</sub> /2<br>- 0.7 | V     |

| V <sub>OL</sub> | DC output logic low                                                                                  | $I_{OL} = 3mA$                |                             |      | 0.4                         | V     |

| Ipullup         | Current Through Pull-Up Resistor or Cur-<br>rent Source                                              | High Power specifi-<br>cation | 3.0                         |      | 3.6                         | mA    |

| Ileak-bus       | Input leakage per bus segment                                                                        |                               | -200                        |      | 200                         | uA    |

| Ileak-pin       | Input leakage per device pin                                                                         |                               |                             | -15  |                             | uA    |

| CI              | Capacitance for SDA/SCL                                                                              |                               |                             |      | 10                          | pF    |

| tBUF            | Bus Free Time<br>Between Stop and Start condition                                                    |                               | 1.3                         |      |                             | us    |

| tHD:STA         | Hold time after (Repeated) Start condition.<br>After this period, the first clock is gener-<br>ated. | At pull-up, Max               | 0.6                         |      |                             | us    |

| TSU:STA         | Repeated start condition setup time                                                                  |                               | 0.6                         |      |                             | us    |

| TSU:STO         | Stop condition setup time                                                                            |                               | 0.6                         |      |                             | us    |

| THD:DAT         | Data hold time                                                                                       |                               | 0                           |      |                             | ns    |

| TSU:DAT         | Data setup time                                                                                      |                               | 100                         |      |                             | ns    |

| tLOW            | Clock low period                                                                                     |                               | 1.3                         |      |                             | us    |

| tHIGH           | Clock high period                                                                                    |                               | 0.6                         |      | 50                          | us    |

| tF              | Clock/Data fall time                                                                                 |                               |                             |      | 300                         | ns    |

| tR              | Clock/Data rise time                                                                                 |                               |                             |      | 300                         | ns    |

| tPOR            | Time in which a device must be operation after power-on reset                                        |                               |                             |      | 500                         | ms    |

Note:

(1) Recommended maximum capacitance load per bus segment is 400pF.

(2) Compliant to I2C physical layer specification.

(3) Ensured by Design. Parameter not tested in production.

Figure 6-6 I2C Timing Diagram

## 7. Application/Implementation

#### Note

Information in the following applications sections is not part of the component specification, and does not warrant its accuracy or completeness. Customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

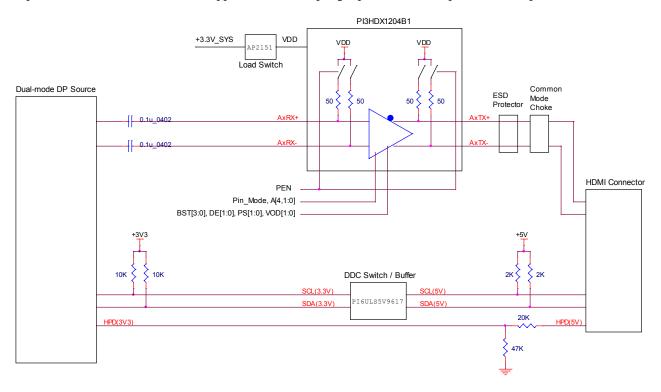

### 7.1 Source Application

PI3HDX1204B1 is designed to accept AC-coupled as well as DC-coupled main link signals. When a dual-mode DP source is connected to the input of PI3HDX1204B1 in a source application, AC coupling capacitors must be placed at the input side.

#### 7.1.1 ESD Protectors on Output TMDS

As 8kV contact ESD is commonly required, ESD protectors are implemented at the output TMDS pins of PI3HDX1204B1 for source application. ESD8104 HDMI2.0 ESD protector can be considered to protect the 3.3V TMDS paths as its reverse working voltage is 3.3V.

#### 7.1.2 Extra Component for Rise/fall Time Control

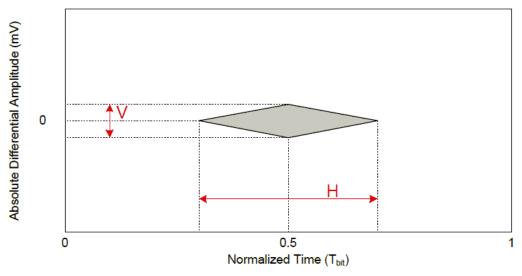

Per HDMI2.0 specification, rise/fall time of TMDS clock is kept at minimal 75ps while that of TMDS data is decreased to minimal 42.5ps if data rate is between 3.4Gbps and 6Gbps.

PI3HDX1204B1

Table 7-3 Source TMDS Electrical - 6G – T<sub>RISE</sub>, T<sub>FALL</sub> Requirements

| Reference                                                            | Requirement                                 |

|----------------------------------------------------------------------|---------------------------------------------|

| [HDMI 2.0: Table 6-2]                                                | Rise/Fall time: Data (20% to 80%): ≥42.5 ps |

| AC Characteristics for 3.4 Gbps < R <sub>bit</sub> ≤ 6.0 Gbps at TP1 | Rise/Fall time: Clock (20% to 80%): ≥75 ps  |

#### Figure 7-2 HDMI2.0 Trise/fall Requirement

PI3HDX1204B1 is designed to meet the rise/fall time of TMDS data. If output trace length is short, maybe 1" only, common-mode choke or external inductor can be considered for slowing down the rise/fall time for TMDS clock of PI3HDX1204B1.

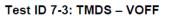

#### 7.1.3 Leakage Blockage for VOFF Test

When performing VOFF test specified in HDMI 1.4a Compliance Test Specification, each output TMDS of PI3HDX1204B1 will be pulled to 3.3V via an external 50k $\Omega$  resistor. In this case, current will pass through an internal ESD protector at the output TMDS pin of PI3HDX1204B1 and leakage will be found at VCC pin of PI3HDX1204B1.

#### Figure 7-3 HDMI VOFF Test Setup

| Test ID 7-3: TMDS – V <sub>OFF</sub>                      |                                                                                                       |  |  |  |  |  |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Reference                                                 | Requirement                                                                                           |  |  |  |  |  |

| [HDMI: Table 4-23]<br>Source DC Characteristics at<br>TP1 | TMDS single-ended standby (off) output voltage, $\bigvee_{\text{OFF}}$ must be within AVcc ±10mVolts. |  |  |  |  |  |

#### Figure 7-4 HDMI VOFF Requirement

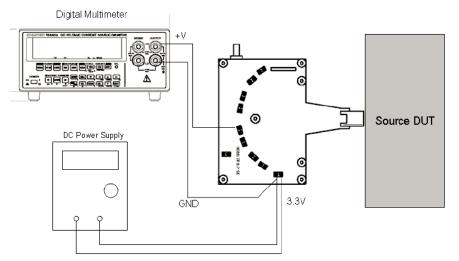

To avoid this leakage, AP2151A power switch can be employed between the main 3.3V supply on a system and the VCC power plane of PI3HDX1204B1. Below is an example borrowed from an evaluation board schematic.

## PI3HDX1204B1

Figure 7-5 Power Distribution Switch Example

## 7.2 Sink Application

PI3HDX1204B1 can also be employed in a sink application as it offers a range of equalization setting.

Figure 7-6 PI3HDX1204B1 Sink Application Circuit

#### 7.2.1 ESD Protectors on Output TMDS

ESD protector selection guidance for source and sink applications is the same.

## PI3HDX1204B1

## 7.3 DC/AC-coupled Application

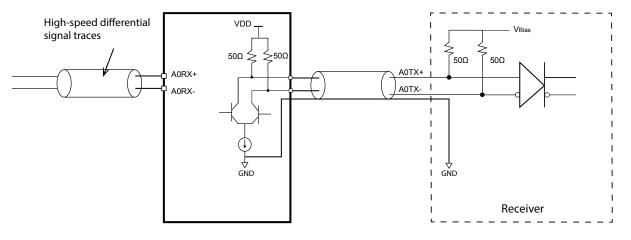

**DC-Coupled Differential Signaling Application Circuits**

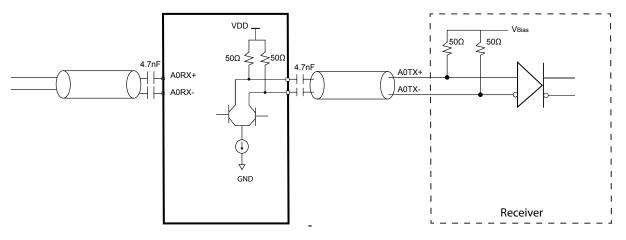

AC-Coupled Differential Signaling Application Circuits

Figure 7-7 DC/AC-coupled Application Diagram

PI3HDX1204B1

## 7.4 Product Layout Guideline

#### 7.4.1 AC Coupling Capacitor

Below is an example of placing AC coupling capacitors on high-speed channels

Figure 7-8 AC Coupling Capacitor Placement

#### 7.4.2 Output Trace Length

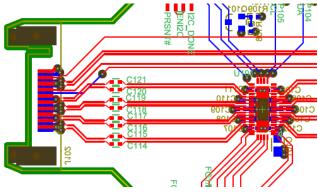

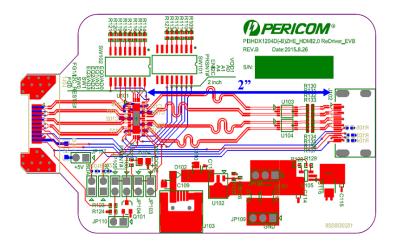

To fulfill minimal 75ps rise/fall time requirement of TMDS clock, 1.5 - 4.5" TMDS trace length between PI3HDX1204B1 and HDMI connector for source application is recommended. This trace length varies with PCB trace width, characteristics of common-mode choke/ESD protector and connector quality. If trace width is 5 mil, 2.7 - 3.3" is recommended. Isolation space should be larger than 5 mil to minimize the crosstalk so thus jitter. Below is the PI3HDX1204B1 placement on its evaluation board.

Figure 7-9 Source-side Placement near to the HDMI Connectors

#### 7.4.3 Differential Impedance (TDR)

Layout guideline especially for high-speed transmission is critical. Please refer to PI3DPxxx\_PI3HDxxx\_Layout Guideline for detailed recommendations. Differential impedance test is required for both source and sink applications per HDMI 2.0 specification.

**PI3HDX1204B1**

Table 7-17 Source TMDS Electrical - 6G – Differential Impedance Requirements

| Reference                                                           | Requirement                                              |

|---------------------------------------------------------------------|----------------------------------------------------------|

| [HDMI 2.0: Table 6-3]                                               | Through Connection Impedance∆: 100 Ω +/- 15%◊            |

| Source Impedance Characteristics for (3.4 Gbps < R <sub>bit</sub> ≤ | In single excursion is permitted out to a max/min of     |

| 6.0 Gbps) at TP1                                                    | 100 $\Omega$ +/- 25% and of a duration less than 250 ps. |

|                                                                     | Δ Impedance from TP1 to Source Termination               |

|                                                                     | Source Termination Impedance: 75 to 150 Ω                |

**Figure 7-10 HDMI2.0 Differential Impedance Requirement for Source Application** *Table 8-7 Sink TMDS Electrical - 6G – Differential Impedance Requirements*

| Reference                                                         | Requirement                                             |

|-------------------------------------------------------------------|---------------------------------------------------------|

| [HDMI 2.0: Table 6-8]                                             | Through Connection Impedance∆: 100 Ω +/- 15%◊           |

| Sink Impedance Characteristics for (3.4 Gbps < R <sub>bit</sub> ≤ | A single excursion is permitted out to a max/min of     |

| 6.0 Gbps) at TP2                                                  | 100 $\Omega$ ±25% and of duration less than 250 ps.     |

|                                                                   | Δ Impedance from TP2 to Sink Termination                |

|                                                                   | Sink Termination Impedance: 90 $\Omega$ to 110 $\Omega$ |

#### Figure 7-11 HDMI2.0 Differential Impedance Requirement for Sink Application

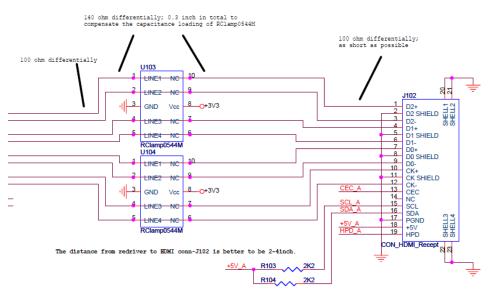

The PCB impedance immediately before and after an ESD protector must be adjusted to compensate the capacitance loading of the ESD protector. Below is an example designing RClampe0544M in PI3HDX1204B1 evaluation board. Trace impedances before and after the ESD protector are tuned to compensate the capacitance of RClamp0544M. Semtech's layout guideline is followed.

Figure 7-12 ESD Protector on PI3HDX1204B1 Source EVB

#### 7.4.4 GND via on the Thermal Pad Area

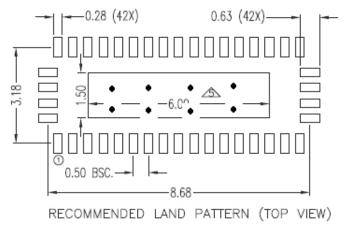

Several GND via are "MUST" required on thermal area. The via size is 12/24 mil. Below is the thermal pad via layout recommendation.

Figure 7-13 Recommended Land Patterns

PI3HDX1204B1

### 7.5 General Layout Guideline

As transmission data rate increases rapidly, any flaws and/or mis-matches on PCB layout are amplified in terms of signal integrity. Layout guideline for high-speed transmission is highlighted in this application note.

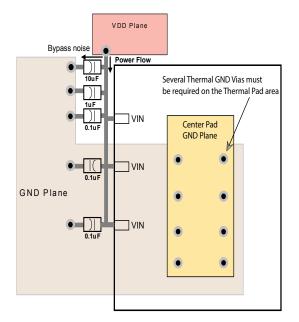

#### 7.5.1 Power and Ground

To provide a clean power supply for Pericom high-speed device, few recommendations are listed below:

- Power (VDD) and ground (GND) pins should be connected to corresponding power planes of the printed circuit board directly without passing through any resistor.

- The thickness of the PCB dielectric layer should be minimized such that the VDD and GND planes create low inductance paths.

- One low-ESR 0.1uF decoupling capacitor should be mounted at each VDD pin or should supply bypassing for at most two VDD pins. Capacitors of smaller body size, i.e. 0402 package, is more preferable as the insertion loss is lower. The capacitor should be placed next to the VDD pin.

- One capacitor with capacitance in the range of 4.7uF to 10uF should be incorporated in the power supply decoupling design as well. It can be either tantalum or an ultra-low ESR ceramic.

- A ferrite bead for isolating the power supply for Pericom high-speed device from the power supplies for other parts on the printed circuit board should be implemented.

- Several thermal ground vias must be required on the thermal pad. 25-mil or less pad size and 14-mil or less finished hole are recommended.

Figure 7-14 Decoupling Capacitor Placement Diagram

#### 7.5.2 High-speed Signal Routing

Well-designed layout is essential to prevent signal reflection:

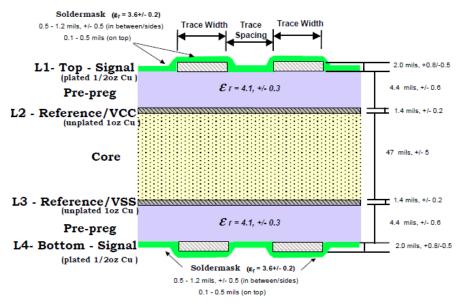

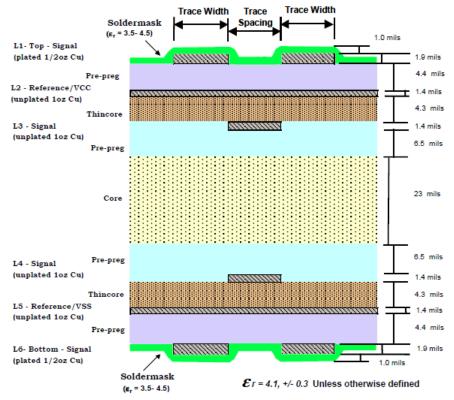

- For 90 $\Omega$  differential impedance, width-spacing-width micro-strip of 6-7-6 mils is recommended; for 100 $\Omega$  differential impedance, width-spacing-width micro-strip of 5-7-5 mils is recommended.

- Differential impedance tolerance is targeted at  $\pm 15\%$ .

| Trace and board parameters:                                                                                                                                                                                                                                                                                                                                        | Single-ended mode:                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Trace and board parameters.Trace width: $W = 6.0 \clubsuit$ milsTrace thickness: $t = 1.9 \clubsuit$ mils (1.39 oz)Trace spacing: $S = 7.0 \clubsuit$ milsDielectric (layer) thickness: $h = 4.4 \clubsuit$ mils (b=10.7 mils)Dielectric (layer) asymmetry: $50 \clubsuit$ % (h1=4.4, h2=4.4)Relative dielectric constant: $e = 4.1 \clubsuit$                     | Single-ended mode.MicrostripStriplineCharacteristic<br>impedance: $Microstrip$ $32.9$<br>$\Omega$ $\Omega$ Capacitance: $Co = 2.70$ $6.30$<br>$Differentialpf/inDelay:Tpd=137.1171.6Differentialps/inDifferential mode:mm/ns$ |

| PCB edge view                                                                                                                                                                                                                                                                                                                                                      | Differential impedance: $Z_0 = \begin{bmatrix} 90.8 \\ 90.8 \end{bmatrix} \begin{bmatrix} 62.4 \\ \Omega \end{bmatrix}$                                                                                                       |

| $ \begin{array}{c} \downarrow & \longleftarrow & W \longrightarrow S \searrow \\ \uparrow & & & & \downarrow \downarrow \\ \uparrow & & & & & \downarrow $                                                          | <ol> <li>Microstrip Zo formula accurate if 0.1<w h<2)<="" li=""> <li>Stripline Zo formula accurate if (W/b)&lt;0.35</li> <li>Stripline Zo formula accurate if (b/t)&gt;4</li> </w></li></ol>                                  |

| Trace and board parameters:Trace width: $W=5.0$ $\clubsuit$ milsTrace thickness: $t=1.9$ $\clubsuit$ mils (1.39 oz)Trace spacing: $S=7.0$ $\clubsuit$ milsDielectric (layer) thickness: $h=4.4$ $\clubsuit$ mils (b=10.7 mils)Dielectric (layer) asymmetry: $50 $ $\bigstar$ $\gtrsim$ (h1=4.4, h2=4.4)Relative dielectric constant: $\approx$ 4.11 $\diamondsuit$ | Single-ended mode:MicrostripStriplineCharacteristic $Microstrip36.7\Omegaimpedance:Zo=55.436.7\OmegaCapacitance:Co=2.475.54pf/inDelay:Tpd=137.1171.6ps/inSpeed:v=185.4148.2mm/nsDifferential mode:Microstrip\Omegaiction$     |

| PCB edge view                                                                                                                                                                                                                                                                                                                                                      | Differential<br>impedance:Microstrip<br>99.3Stripline<br>69.5 $\Omega$                                                                                                                                                        |

| $ \begin{array}{c} \downarrow & \longleftarrow & \downarrow^{t} \\ \uparrow & \uparrow_{h} \end{array} \qquad $                                                                                                                             | <ol> <li>Microstrip Zo formula accurate if 0.1<w h<2)<="" li=""> <li>Stripline Zo formula accurate if (W/b)&lt;0.35</li> <li>Stripline Zo formula accurate if (b/t)&gt;4</li> </w></li></ol>                                  |

Figure 7-15 Trace Width and Clearance of Micro-strip and Strip-line

For micro-strip, using 1/2oz Cu is fine. For strip-line in 6+ PCB layers, 1oz Cu is more preferable. ٠

Figure 7-17 6-Layer PCB Stack-up Example

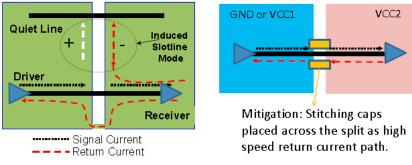

Ground referencing is highly recommended. If unavoidable, stitching capacitors of 0.1uF should be placed when reference plane is changed.

Figure 7-18 Stitching Capacitor Placement

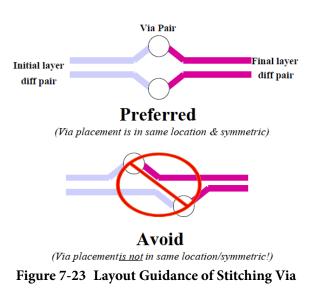

- To keep the reference unchanged, stitching vias must be used when changing layers.

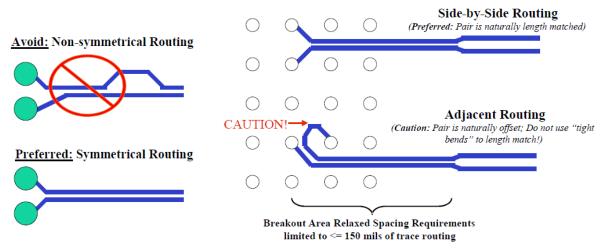

- Differential pair should maintain symmetrical routing whenever possible. The intra-pair skew of micro-strip should be less than 5 mils.

- To keep the reference unchanged, stitching vias must be used when changing layers.

- Differential pair should maintain symmetrical routing whenever possible. The intra-pair skew of micro-strip should be less than 5 mils.

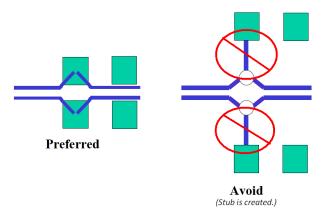

Figure 7-19 Layout Guidance of Matched Differential Pair

- For minimal crosstalk, inter-pair spacing between two differential micro-strip pairs should be at least 20 mils or 4 times the dielectric thickness of the PCB.

- Wider trace width of each differential pair is recommended in order to minimize the loss, especially for long routing. More consistent PCB impedance can be achieved by a PCB vendor if trace is wider.

- Differential signals should be routed away from noise sources and other switching signals on the printed circuit board.

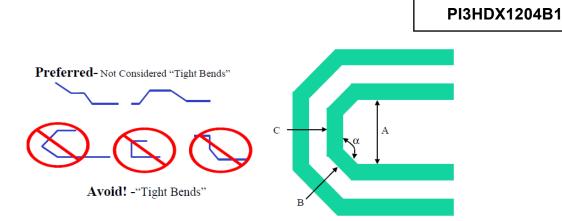

- To minimize signal loss and jitter, tight bend is not recommended. All angles  $\alpha$  should be at least 135 degrees. The inner air gap A should be at least 4 times the dielectric thickness of the PCB.

Figure 7-20 Layout Guidance of Bends

Stub creation should be avoided when placing shunt components on a differential pair.

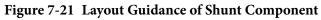

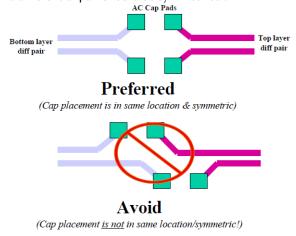

• Placement of series components on a differential pair should be symmetrical.

Figure 7-22 Layout Guidance of Series Component

• Stitching vias or test points must be used sparingly and placed symmetrically on a differential pair.

PI3HDX1204B1

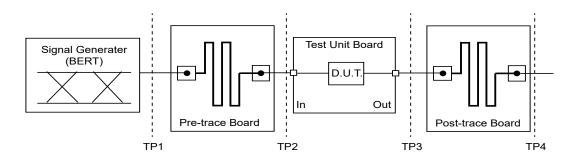

### 7.6 CTS Test Report

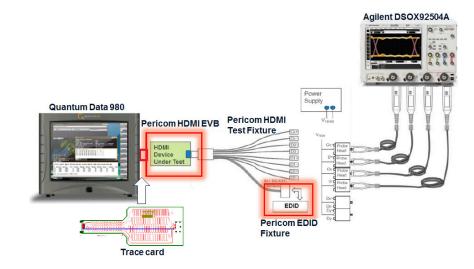

#### 7.6.1 HDMI 2.0 Compliance Test Set-up

#### Figure 7-24 HDMI 2.0 CTS Test Setup

Note: Application Trace Card Information for CTS test

| HDMI FR4 trace         | 0 in     | 6 in     | 12 in     | 18 in     | 24 in     | 30 in     | 36 in     |

|------------------------|----------|----------|-----------|-----------|-----------|-----------|-----------|

| Insertion loss @ 6Gbps | -5.91 dB | -9.75 dB | -10.47 dB | -13.05 dB | -15.87 dB | -16.97 dB | -21.20 dB |

PI3HDX1204B1

### 7.6.2 HDMI 2.0 Compliance Report

#### Fest Summary

| Index | Test Name                                              | Lanes   | Spec Range                | Meas Value   | Result |

|-------|--------------------------------------------------------|---------|---------------------------|--------------|--------|

| 1     | 7-9 : Source Clock Jitter                              | CK      | Clock Jitter < 0.25*Tbit; | 0.061*Tbit   | Pass   |

| 2     | 7-10 : Source Eye Diagram                              | CK - D0 | Data Jitter < 0.3*Tbit;   | 0.06*Tbit    | Pass   |

| 3     | 7-10 : Source Eye Diagram                              | CK - D1 | Data Jitter < 0.3*Tbit;   | 0.07*Tbit    | Pass   |

| 4     | 7-10 : Source Eye Diagram                              | CK - D2 | Data Jitter < 0.3*Tbit;   | 0.07*Tbit    | Pass   |

| 5     | 7-6 : Source Inter-Pair Skew                           | D0 - D1 | Skew < 0.2*TPixel;        | 0*TPixe1     | Pass   |

| 6     | 7-6 : Source Inter-Pair Skew                           | D1 - D2 | Skew < 0.2*TPixel;        | 0.006*TPixe1 | Pass   |

| 7     | 7-6 : Source Inter-Pair Skew                           | D2 - D0 | Skew < 0.2*TPixel;        | 0.006*TPixe1 | Pass   |

| 8     | 7-4 : Source Rise Time                                 | CK      | 75.00ps < TRISE;          | 171.37ps     | Pass   |

| 9     | 7-4 : Source Rise Time                                 | D0      | 75.00ps < TRISE;          | 149.40ps     | Pass   |

| 10    | 7-4 : Source Rise Time                                 | D1      | 75.00ps < TRISE;          | 145.49ps     | Pass   |

| 11    | 7-4 : Source Rise Time                                 | D2      | 75.00ps < TRISE;          | 150.62ps     | Pass   |

| 12    | 7-4 : Source Fall Time                                 | CK      | 75.00ps < TFALL;          | 170.68ps     | Pass   |

| 13    | 7-4 : Source Fall Time                                 | D0      | 75.00ps < TFALL;          | 148.94ps     | Pass   |

| 14    | 7-4 : Source Fall Time                                 | D1      | 75.00ps < TFALL;          | 142.33ps     | Pass   |

| 15    | 7-4 : Source Fall Time                                 | D2      | 75.00ps < TFALL;          | 144.95ps     | Pass   |

| 16    | 7-8 : Max Duty Cycle                                   | CK      | Max Duty Cycle < 60.0%;   | 50.79%       | Pass   |

| 17    | 7-8 : Min Duty Cycle                                   | CK      | 40.0% < Min Duty Cycle;   | 49.6%        | Pass   |

| 18    | 7-2 : Source Low Amplitude +(Supported Sink <= 165MHz) | CK+     | 2.700V < VL < 2.900V;     | 2.8600V      | Pass   |

| 19    | 7-2 : Source Low Amplitude +(Supported Sink <= 165MHz) | D0+     | 2.700V < VL < 2.900V;     | 2.8475V      | Pass   |

| 20    | 7-2 : Source Low Amplitude -(Supported Sink <= 165MHz) | CK-     | 2.700V < VL < 2.900V;     | 2.8425V      | Pass   |

| 21    | 7-2 : Source Low Amplitude -(Supported Sink <= 165MHz) | D0-     | 2.700V < VL < 2.900V;     | 2.8475V      | Pass   |

| 22    | 7-2 : Source Low Amplitude +(Supported Sink <= 165MHz) | D1+     | 2.700V < VL < 2.900V;     | 2.8250V      | Pass   |

| 23    | 7-2 : Source Low Amplitude +(Supported Sink <= 165MHz) | D2+     | 2.700V < VL < 2.900V;     | 2.8650V      | Pass   |

| 24    | 7-2 : Source Low Amplitude -(Supported Sink <= 165MHz) | D1-     | 2.700V < VL < 2.900V;     | 2.8275V      | Pass   |

| 25    | 7-2 : Source Low Amplitude -(Supported Sink <= 165MHz) | D2-     | 2.700V < VL < 2.900V;     | 2.8650V      | Pass   |

| 26    | 7-7 : Source Intra-Pair Skew                           | CK      | Skew < 0.15*Tbit;         | 0.015*Tbit   | Pass   |

| 27    | 7-7 : Source Intra-Pair Skew                           | D0      | Skew < 0.15*Tbit;         | 0.021*Tbit   | Pass   |

| 28    | 7-7 : Source Intra-Pair Skew                           | D1      | Skew < 0.15*Tbit;         | 0.007*Tbit   | Pass   |

| 29    | 7-7 : Source Intra-Pair Skew                           | D2      | Skew < 0.15*Tbit;         | 0.051*Tbit   | Pass   |

#### 8. Mechanical/Packaging Information

#### 8.1 Mechanical

#### For latest package info.

please check: http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/

## PI3HDX1204B1

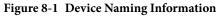

#### 8.2 Part Marking Information

Our standard product mark follows our standard part number ordering information, except for those products with a speed letter code. The speed letter code mark is placed after the package code letter, rather than after the device number as it is ordered. After electrical test screening and speed binning has been completed, we then perform an "add mark" operation which places the speed code letter at the end of the complete part number.

Figure 8-2 Device Marking Information

**PI3HDX1204B1**

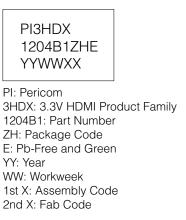

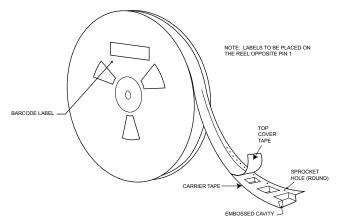

#### 8.3 Tape & Reel Materials and Design

#### **Carrier Tape**

The Pocketed Carrier Tape is made of Conductive Polystyrene plus Carbon material (or equivalent). The surface resistivity is 10<sup>6</sup>Ohm/sq. maximum. Pocket tapes are designed so that the component remains in position for automatic handling after cover tape is removed. Each pocket has a hole in the center for automated sensing if the pocket is occupied or not, thus facilitating device removal. Sprocket holes along the edge of the center tape enable direct feeding into automated board assembly equipment. See Figures 3 and 4 for carrier tape dimensions.

#### **Cover Tape**

Cover tape is made of Anti-static Transparent Polyester film. The surface resistivity is  $10^7$ Ohm/Sq. Minimum to  $10^{11}$ Ohm sq. maximum. The cover tape is heat-sealed to the edges of the carrier tape to encase the devices in the pockets. The force to peel back the cover tape from the carrier tape shall be a MEAN value of 20 to 80gm (2N to 0.8N).

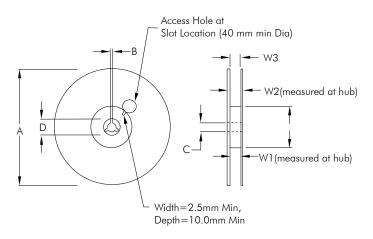

#### Reel

The device loading orientation is in compliance with EIA-481, current version (Figure 2). The loaded carrier tape is wound onto either a 13inch reel, (Figure 4) or 7-inch reel. The reel is made of Antistatic High-Impact Polystyrene. The surface resistivity  $10^7$ Ohm/sq. minimum to  $10^{11}$ Ohm/sq. max.

Figure 8-3 Tape & Reel label Information

Figure 8-4 Tape leader and Trailer Pin 1 Orientation

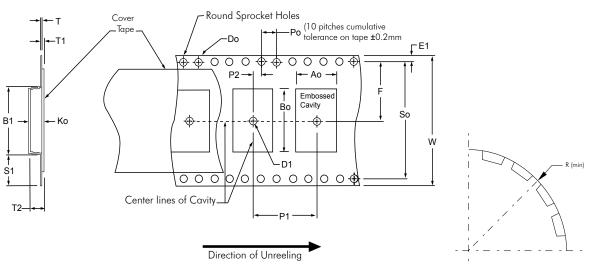

Figure 8-5 Standard Embossed Carrier Tape Dimension

#### **Constant Dimensions**

| Tape<br>Size | D0              | D1 (Min) | E1     | P0        | P2             | R<br>(See Note 2) | S1 (Min)      | T<br>(Max) | T1<br>(Max) |  |  |     |     |

|--------------|-----------------|----------|--------|-----------|----------------|-------------------|---------------|------------|-------------|--|--|-----|-----|

| 8mm          |                 | 1.0      |        |           | 2.0 ± 0.05     | 25                |               |            |             |  |  |     |     |

| 12mm         |                 |          |        |           | 2.0 ± 0.05     |                   | 0.6           |            |             |  |  |     |     |

| 16mm         | 1.5 <u>+0.1</u> | 1.5      | 1.75 ± | 4.0 ± 0.1 |                | 30                | 0.0           | 0.4        | 0.1         |  |  |     |     |

| 24mm         | <u>-0.0</u>     |          | 0.1    | 0.1 2.    | 4.0 ± 0.1      | 4.0 ± 0.1         | $4.0 \pm 0.1$ | 4.0 ± 0.1  | 2.0 ± 0.1   |  |  | 0.6 | 0.1 |

| 32mm         |                 | 2.0      |        |           |                | 50                | N/A           |            |             |  |  |     |     |

| 44mm         |                 | 2.0      |        |           | $2.0 \pm 0.15$ | 50                | (See Note 3)  |            |             |  |  |     |     |

#### Variable Dimensions

| Tape<br>Size | P <sub>1</sub>                                                                                            | B <sub>1</sub> (Max) | E <sub>2</sub> (Min) | F              | So                                  | T <sub>2</sub> (Max.) | W (Max) | A <sub>0</sub> , B <sub>0</sub> , & K <sub>0</sub> |

|--------------|-----------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------|-------------------------------------|-----------------------|---------|----------------------------------------------------|

| 8mm          | Specific per package type. Refer                                                                          | 4.35                 | 6.25                 | $3.5 \pm 0.05$ |                                     | 2.5                   | 8.3     |                                                    |

| 12mm         | to FR-0221 (Tape and Reel Pack-<br>ing Information) or visit www.<br>pericom.com/pdf/gen/tapereel.<br>pdf | 8.2                  | 10.25                | $5.5 \pm 0.05$ | N/A<br>(see note<br>4)<br>28.4± 0.1 | 6.5                   | 12.3    | See Note 1                                         |

| 16mm         |                                                                                                           | 12.1                 | 14.25                | $7.5 \pm 0.1$  |                                     | 8.0                   | 16.3    |                                                    |

| 24mm         |                                                                                                           | 20.1                 | 22.25                | $11.5 \pm 0.1$ |                                     | 12.0                  | 24.3    | See Note 1                                         |

| 32mm         |                                                                                                           | 23.0                 | N/A                  | $14.2 \pm 0.1$ |                                     | 12.0                  | 32.3    |                                                    |

| 44mm         |                                                                                                           | 35.0                 | N/A                  | $20.2\pm0.15$  | $40.4\pm0.1$                        | 16.0                  | 44.3    |                                                    |

NOTES:

(1) A0, B0, and K0 are determined by component size. The cavity must restrict lateral movement of component to 0.5mm maximum for 8mm and 12mm wide tape and to 1.0mm maximum for 16,24,32, and 44mm wide carrier. The maximum component rotation within the cavity must be limited to 200 maximum for 8 and 12 mm carrier tapes and 100 maximum for 16 through 44mm.

(2) Tape and components will pass around reel with radius "R" without damage.

(3) S1 does not apply to carrier width  $\ge$  32mm because carrier has sprocket holes on both sides of carrier where Do $\ge$ S1.

(4) So does not exist for carrier  $\leq$  32mm because carrier does not have sprocket hole on both side of carrier.

#### Reel Dimensions by Tape Size

| Tape<br>Size | А               | N (Min) <sup>(1)</sup>    | W1                | W2(Max) | W3                                                           | B (Min) | С                       | D (Min) |

|--------------|-----------------|---------------------------|-------------------|---------|--------------------------------------------------------------|---------|-------------------------|---------|

| 8mm          | 178±2.0mm       | 60 ±2.0mm or<br>100±2.0mm | 8.4 +1.5/-0.0 mm  | 14.4 mm | Shall Accom-<br>modate Tape<br>Width Without<br>Interference | 1.5mm   | 13.0<br>+0.5/-0.2<br>mm | 20.2mm  |

| 12mm         | or<br>330±2.0mm |                           | 12.4 +2.0/-0.0 mm | 18.4 mm |                                                              |         |                         |         |

| 16mm         | 330±2.0mm       | 100 ±2.0mm                | 16.4 +2.0/-0.0 mm | 22.4 mm |                                                              |         |                         |         |

| 24mm         |                 |                           | 24.4 +2.0/-0.0 mm | 30.4 mm |                                                              |         |                         |         |

| 32mm         |                 |                           | 32.4 +2.0/-0.0 mm | 38.4 mm |                                                              |         |                         |         |

| 44mm         |                 |                           | 44.4 +2.0/-0.0 mm | 50.4 mm |                                                              |         |                         |         |

| N            |                 | 0                         |                   | Т       |                                                              | E       |                         |         |

(1) If reel diameter A=178 ±2.0mm, then the corresponding hub diameter (N(min) will by 60 ±2.0mm. If reel diameter A=330±2.0mm, then the corresponding hub diameter (N(min)) will by 100±2.0mm.

## 8. Important Notice

1. DIODES INCORPORATED AND ITS SUBSIDIARIES ("DIODES") MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IM-PLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes products. Diodes products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of the Diodes products for their intended applications, (c) ensuring their applications, which incorporate Diodes products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

5. Diodes products are provided subject to Diodes' Standard Terms and Conditions of Sale (https://www.diodes.com/about/company/ terms-and-conditions/terms-and-conditions-of-sales/) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

6. Diodes products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any non-compliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

Copyright © 2020 Diodes Incorporated

www.diodes.com

单击下面可查看定价,库存,交付和生命周期等信息

>>Diodes Incorporated(达迩科技(美台))