#### SECONDARY SIDE SYNCHRONOUS RECTIFICATION SWITCHER

## **Description**

APR3415 is a secondary side Combo IC, which combines an N-Channel MOSFET and a driver circuit designed for synchronous rectification (SR) in DCM operation. It also integrates output voltage detect function for primary side control system.

The N-Channel MOSFET has been optimized for low gate charge, low  $R_{\rm DS(ON)}$ , fast switching speed and body diode reverse recovery performance.

The synchronous rectification can effectively reduce the secondary side rectifier power dissipation and provide high performance solution. By sensing MOSFET drain-to-source voltage, APR3415 can output ideal drive signal with less external components. It can provide high performance solution for 5V output voltage application.

Same as AP4341, APR3415 detects the output voltage and provides a periodical signal when the output voltage is lower than a certain threshold. By fast response to secondary side voltage, APR3415 can effectively improve the transient performance of primary side control system.

The APR3415 is available in SO-8 package.

#### **Features**

Notes:

- Synchronous Rectification for DCM Operation Flyback

- Eliminate Resonant Ring Interference

- Fast Detector of Supply Voltages

- Fewest External Components

- Totally Lead-free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

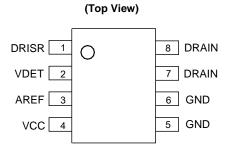

### **Pin Assignments**

SO-8

## **Applications**

- Adapters/Chargers for Cell/Cordless Phones, ADSL Modems, MP3 and Other Portable Apparatus

- Standby and Auxiliary Power Supplies

1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant.

- 2. See http://www.diodes.com/quality/lead\_free.html for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

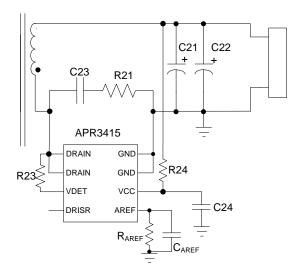

# **Typical Applications Circuit**

APR3415

Document number: DS36738 Rev. 7 - 2

1 of 13

# **Pin Descriptions**

| Pin Number | Pin Name | Function                                                                                                              |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------|

| 1          | DRISR    | Synchronous rectification MOSFET drive                                                                                |

| 2          | VDET     | Synchronous rectification sense input and dynamic function output, connected to DRAIN through a resistor              |

| 3          | AREF     | Program a voltage reference with a resistor from AREF to GND, to enable synchronous rectification MOSFET drive signal |

| 4          | VCC      | Power supply, connected with system output                                                                            |

| 5, 6       | GND      | Source pin of internal MOSFET, connected to Ground                                                                    |

| 7, 8       | DRAIN    | Drain pin of internal MOSFET                                                                                          |

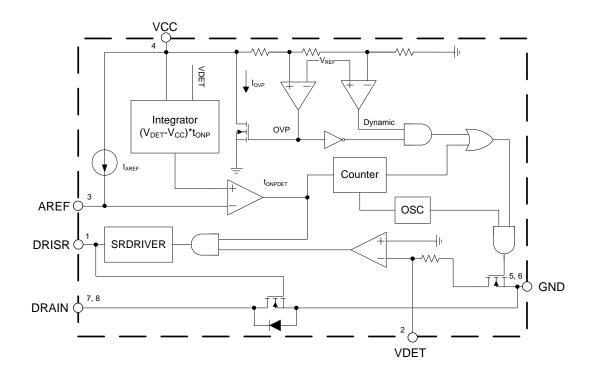

# **Functional Block Diagram**

# **Absolute Maximum Ratings** (Note 4)

| Symbol                                 | Parameter                                         | Value       | Unit |

|----------------------------------------|---------------------------------------------------|-------------|------|

| V <sub>cc</sub>                        | Supply Voltage                                    | -0.3 to 7.5 | V    |

| V <sub>DET</sub> , V <sub>DRAIN</sub>  | Voltage at VDET, DRAIN Pin                        | -2 to 50    | V    |

| V <sub>AREF</sub> , V <sub>DRISR</sub> | Voltage at AREF, DRISR Pin                        | -0.3 to 6   | V    |

| I <sub>D</sub>                         | Continuous Drain Current                          | 15          | А    |

| I <sub>DM</sub>                        | Pulsed Drain Current                              | 60          | А    |

| P <sub>D</sub>                         | Power Dissipation at T <sub>A</sub> =+25°C        | 0.7         | W    |

| $\theta_{JA}$                          | Thermal Resistance (Junction to Ambient) (Note 5) | 170         | °C/W |

| θ <sub>JC</sub>                        | Thermal Resistance (Junction to Case) (Note 5)    | 24          | °C/W |

| TJ                                     | Operating Junction Temperature                    | +150        | °C   |

| T <sub>STG</sub>                       | Storage Temperature                               | -65 to +150 | °C   |

| T <sub>LEAD</sub>                      | Lead Temperature (Soldering, 10 sec)              | +300        | °C   |

Notes:

# **Recommended Operating Conditions**

| Symbol          | Parameter           | Min | Max | Unit |

|-----------------|---------------------|-----|-----|------|

| V <sub>cc</sub> | Supply Voltage      | 3.3 | 6   | V    |

| T <sub>A</sub>  | Ambient Temperature | -40 | +85 | °C   |

<sup>4.</sup> Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to "Absolute Maximum Ratings" for extended periods may affect device reliability.

<sup>5.</sup> FR-4 substrate PC board, 2oz copper, with 1 inch² pad layout.

# **Electrical Characteristics** (@ $T_A = +25^{\circ}C$ , $V_{CC} = 5V$ , unless otherwise specified.)

| Symbol                                 | Parameter                             | Conditions                                                                                           | Min   | Тур   | Max   | Unit  |

|----------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| Supply Voltage (                       | VCC Pin )                             |                                                                                                      |       |       |       | •     |

| I <sub>STARTUP</sub>                   | Startup Current                       | V <sub>CC</sub> =V <sub>STARTUP</sub> -0.1V                                                          | _     | 100   | 150   | μΑ    |

| I <sub>OP</sub>                        | Operating Current                     | VDET pin floating V <sub>CC</sub> =V <sub>TRIGGER</sub> +20mV                                        | 40    | 100   | 150   | μΑ    |

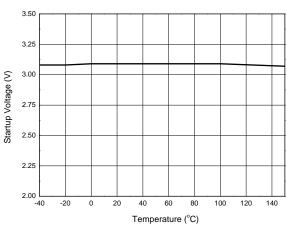

| V <sub>STARTUP</sub>                   | Startup Voltage                       | -                                                                                                    | 2.6   | 3.1   | 3.4   | V     |

| _                                      | UVLO                                  | -                                                                                                    | 2.3   | 2.8   | 3.1   | V     |

| Dynamic Output S                       | Section/Oscillator Section            |                                                                                                      | •     |       |       |       |

| $V_{TRIGGER}$                          | Internal Trigger Voltage              | -                                                                                                    | 5.25  | 5.3   | 5.35  | V     |

| _                                      | Duty Cycle                            | -                                                                                                    | 4     | 8     | 12    | %     |

| tosc                                   | Oscillation Period                    | V <sub>CC</sub> =5V                                                                                  | 18    | 30    | 37.5  | μs    |

| I <sub>TRIGGER</sub>                   | Internal Trigger Current              | $V_{\text{CC}} = V_{\text{TRIGGER}}$ , VCC/VDET pin is separately connected to a $20\Omega$ resistor | 30    | _     | 42    | mA    |

| t <sub>DIS</sub>                       | Minimum Period                        | -                                                                                                    | 18    | 30    | 37.5  | ms    |

| $V_{DIS}$                              | Discharge Voltage                     | -                                                                                                    | 5.28  | 5.44  | 5.52  | V     |

| I <sub>DIS</sub>                       | Discharge Current                     | V <sub>CC</sub> =V <sub>DIS</sub> +0.1V                                                              | 1.5   | 3     | 4.5   | mA    |

| V <sub>DIS</sub> -V <sub>TRIGGER</sub> | Trigger Discharger Gap                | -                                                                                                    | 30    | 110   | -     | mV    |

| V <sub>OVP</sub>                       | Overshoot Voltage for Discharge       | _                                                                                                    | 5.8   | 5.9   | 6.0   | V     |

| I <sub>OVP</sub>                       | Overshoot Current for Discharge       | V <sub>CC</sub> =V <sub>OVP</sub> +0.1V, VCC pin is connected to a 20Ω resistor                      | 40    | -     | 100   | mA    |

| Synchronous Vol                        | tage Detect                           |                                                                                                      |       |       |       |       |

| $V_{THON}$                             | Gate Turn On Threshold                | -                                                                                                    | 0     | _     | 1     | V     |

| $V_{THOFF}$                            | Gate Turn Off Threshold               | -                                                                                                    | -20   | -12.5 | -5    | mV    |

| t <sub>DON</sub>                       | Turn On Delay Time                    | From V <sub>THON</sub> to V <sub>DRISR</sub> =1V                                                     | -     | 70    | 130   | ns    |

| t <sub>DOFF</sub>                      | Turn Off Propagation Delay Time       | From V <sub>THOFF</sub> to V <sub>DRISR</sub> =3V                                                    | -     | 100   | 150   | ns    |

| t <sub>RG</sub>                        | Gate Turn On Rising Time              | From 1V to 3V, C <sub>L</sub> =4.7nF                                                                 | -     | 50    | 100   | ns    |

| t <sub>FG</sub>                        | Gate Turn Off Falling Time            | From 3V to 1V, C <sub>L</sub> =4.7nF                                                                 | -     | 50    | 100   | ns    |

| t <sub>LEB_S</sub>                     | Minimum On Time                       | $(V_{DET}-V_{CC})*t_{ONP}=25V\mu s$                                                                  | 0.9   | 1.8   | 2.7   |       |

| t <sub>LEB_L</sub>                     | Minimum On Time                       | (V <sub>DET</sub> -V <sub>CC</sub> )*t <sub>ONP</sub> = 50Vμs                                        | _     | _     | 6.5   | μs    |

| V <sub>DRISR_HIGH</sub>                | Drive Output Voltage                  | V <sub>CC</sub> =5V                                                                                  | 3.7   | -     | _     | V     |

| V <sub>S_MIN</sub>                     | SR Minimum Operating Voltage (Note 6) | -                                                                                                    |       | -     | 4.5   | V     |

| t <sub>OVP_LAST</sub>                  | Added OVP Discharge Time              | -                                                                                                    | _     | 2.0   | _     | ms    |

| Kqs                                    | (Note 7)                              | (V <sub>DET</sub> -V <sub>CC</sub> )*t <sub>ONP</sub> = 25Vµs                                        | 0.325 | -     | 0.515 | mA*µs |

Notes: 6. This item specifies the minimum SR operating voltage of  $V_{IN\_DC}$ ,  $V_{IN\_DC} \ge N_{PS}^* V_{S\_MIN.}$

7. This item is used to specify the value of  $\ensuremath{\mathsf{R}}_{\ensuremath{\mathsf{AREF}}}.$

## Electrical Characteristics (@TA =+25°C, unless otherwise specified. Cont.)

#### **MOSFET Static Characteristics**

| Parameters                             | Symbol               | Conditions                                                | Min | Тур | Max | Unit |

|----------------------------------------|----------------------|-----------------------------------------------------------|-----|-----|-----|------|

| Drain to Source Breakdown<br>Voltage   | V <sub>DSS(BR)</sub> | V <sub>GS</sub> =0V, I <sub>D</sub> =0.25mA               | 50  | -   | -   | V    |

| Gate Threshold Voltage                 | $V_{GS(TH)}$         | V <sub>DS</sub> =V <sub>GS</sub> , I <sub>D</sub> =0.25mA | 0.5 | 0.9 | 2   | V    |

| Zero Gate Voltage Drain<br>Current     | I <sub>DSS</sub>     | V <sub>DS</sub> =50V, V <sub>GS</sub> =0V                 | -   | -   | 1   | μΑ   |

| Gate to Source Leakage<br>Current      | I <sub>GSS</sub>     | V <sub>GS</sub> =10V, V <sub>DS</sub> =0V                 | -   | -   | ±10 | μΑ   |

| Drain to Source On-state<br>Resistance | R <sub>DS(ON)</sub>  | V <sub>GS</sub> =4.5V, I <sub>D</sub> =15A                | 12  | 17  | 30  | mΩ   |

#### **MOSFET Dynamic Characteristics**

| Parameters                               | Symbol           | mbol Conditions                                   |   | Тур  | Max | Unit |

|------------------------------------------|------------------|---------------------------------------------------|---|------|-----|------|

| Input Capacitance                        | C <sub>iss</sub> |                                                   | - | 1316 | _   |      |

| Output Capacitance                       | Coss             | V <sub>GS</sub> =0V, V <sub>DS</sub> =25V, f=1MHz | _ | 97   | _   | pF   |

| Reverse Transfer Capacitance             | C <sub>rss</sub> |                                                   | _ | 85   | _   |      |

| Gate to Source Charge                    | Qgs              |                                                   | _ | 3.2  | _   |      |

| Gate to Drain Charge (Miller<br>Charger) | Q <sub>gd</sub>  | $V_{GS}$ =0V to 10V, $V_{DD}$ =25V, $I_{D}$ =15A  | _ | 5.7  | _   | nC   |

| Total Gate Charge                        | Qg               |                                                   | _ | 15.2 | -   |      |

| Gate Resistance                          | R <sub>g</sub>   | -                                                 | - | 0.85 | 1   | Ω    |

APR3415 Document number: DS36738 Rev. 7 - 2

## **Performance Characteristics**

# Startup Voltage vs. Temperature

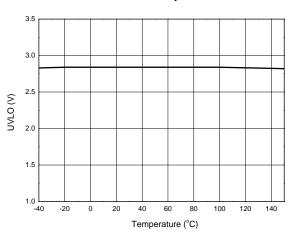

#### **UVLO vs. Temperature**

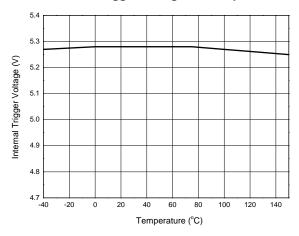

#### Internal Trigger Voltage vs. Temperature

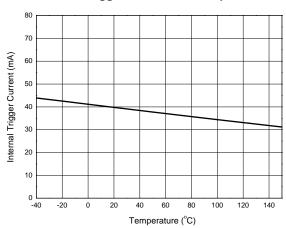

### Internal Trigger Current vs. Temperature

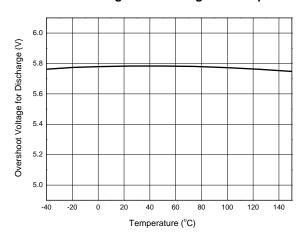

#### Overshoot Voltage for Discharge vs. Temperature

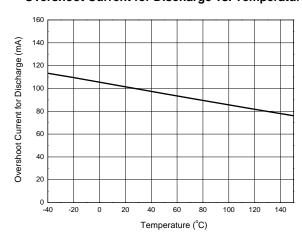

#### **Overshoot Current for Discharge vs. Temperature**

# **Performance Characteristics (Cont.)**

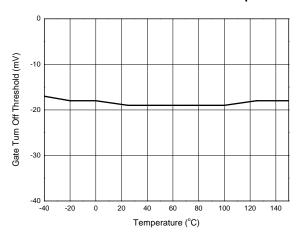

#### **Gate Turn Off Threshold vs. Temperature**

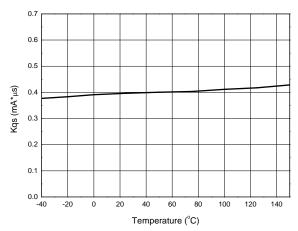

## Kqs (See Note 7) vs. Temperature

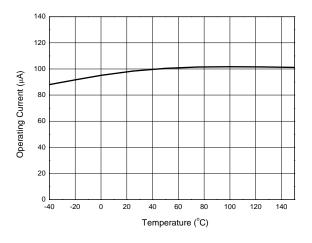

## **Operating Current vs. Temperature**

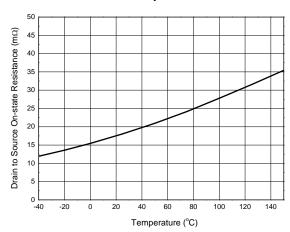

# Drain to Source On-state Resistance vs. Temperature

## **Output Voltage Detect Function Description**

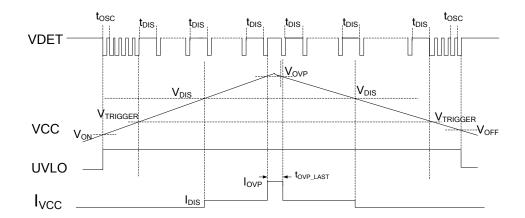

Figure 1. Typical Waveforms of APR3415

When  $V_{CC}$  is beyond power-on voltage  $(V_{ON})$ , the APR3415 starts up. The VDET pin asserts a periodical pulse and the oscillation period is  $t_{OSC}$ . When  $V_{CC}$  is beyond the trigger voltage  $(V_{TRIGGER})$ , the periodical pulse at VDET pin is discontinued. When  $V_{CC}$  is beyond the discharge voltage  $(V_{DIS})$ , the discharge circuit will be enabled, and a 3mA current  $(I_{DIS})$  will flow into VCC pin. When  $V_{CC}$  is higher than the overshoot voltage  $(V_{OVP})$ , the APR3415 will enable a discharge circuit, the discharge current  $(I_{OVP})$  will last  $t_{OVP\_LAST}$  time. After the  $t_{OVP\_LAST}$  time, APR3415 will stop the discharge current and detect VCC voltage again. If  $V_{CC}$  is still higher than  $V_{OVP}$ , the  $t_{OVP\_LAST}$  time discharge current will be enabled again. Once the OVP discharge current is asserted, the periodical pulse at VDET pin will be disabled.

When the V<sub>CC</sub> falls below the power-off voltage (V<sub>OFF</sub>), the APR3415 will shut down.

#### **Operation Description**

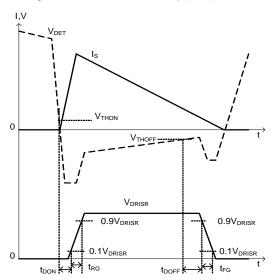

#### **MOSFET Driver**

The operation of the SR is described with timing diagram shown in Figure 2. APR3415 monitors the MOSFET drain-source voltage. When the drain voltage is lower than the turn-on threshold voltage  $V_{THON}$ , the IC outputs a positive drive voltage after a turn-on delay time ( $t_{DON}$ ). The MOSFET will turn on and the current will transfer from the body diode into the MOSFET's channel.

In the process of drain current decreasing linearly toward zero, the drain-source voltage rises synchronically. When it rises over the turn off threshold voltage  $V_{THOFF}$ , APR3415 pulls the drive signal down after a turn off delay ( $t_{DOFF}$ ).

Figure 2. Typical Waveforms of APR3415

APR3415 Document number: DS36738 Rev. 7 - 2 8 of 13

### **Operation Description (Cont.)**

#### **Minimum On Time**

When the controlled MOSFET gate is turned on, some ringing noise is generated. The minimum on-time timer blanks the  $V_{THOFF}$  comparator, keeping the controlled MOSFET on for at least the minimum on time. If  $V_{THOFF}$  falls below the threshold before minimum on time expires, the MOSFET will keep on until the end of the minimum on time.

The minimum on time is in direct proportion to the (V<sub>DET</sub>-V<sub>CC</sub>)\*t<sub>ONP</sub>. When (V<sub>DET</sub>-V<sub>CC</sub>)\*t<sub>ONP</sub>=5V\*5µs, the minimum on time is about 1.8µs.

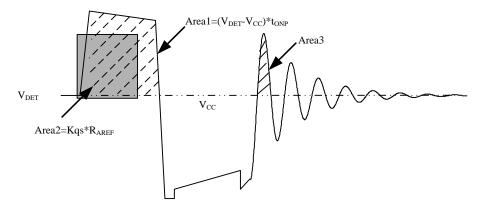

#### The Value and Meaning of AREF Resistor

As to DCM operation Flyback converter, after secondary rectifier stops conduction the primary MOSFET Drain-to-source ringing waveform is resulted from the resonant of primary inductance and equivalent switch device output capacitance. This ringing waveform probably leads to Synchronous Rectifier error conduction. To avoid this fault happening, APR3415 has a special function design by means of volt-second product detecting. From the sensed voltage of VDET pin to see, the volt-second product of voltage above VCC at primary switch on time is much higher than the volt-second product of each cycle ringing voltage above  $V_{CC}$ . Therefore, before every time Synchronous Rectifier turning on, APR3415 judges if the detected volt-second product of VDET voltage above  $V_{CC}$  is higher than a threshold and then turn on synchronous Rectifier. The purpose of AREF resistor is to determine the volt-second product threshold. APR3415 has a parameter, Kqs, which converts  $R_{AREF}$  value to volt-second product.

Area

$$2 = R_{ARFF} * Kqs$$

In general, Area1 and Area3, the value of which should be test on system, depend on system design and always are fixed after system design frozen. As to BCD PSR design, the Area1 value changes with primary peak current value and Area3 value generally keeps constant at all of conditions. So the AREF resistor design should consider the worst case, the minimum primary peak current condition. Since of system design parameter distribution, Area1 and Area3 have moderate tolerance. So Area2 should be designed between the middle of Area1 and Area3 to keep enough design margin.

Area3 < R AREF \* Kqs < Area1

Figure 3. AREF Function

#### **SR Minimum Operating Voltage**

APR3415 sets a minimum SR operating voltage by comparing the difference between  $V_{DET}$  and output voltage ( $V_{CC}$ ). The value of  $V_{DET}$ – $V_{CC}$  must be higher than its internal reference, then APR3415 will begin to integrate the area of  $(V_{DET}$ – $V_{CC})$ \* $t_{ONP}$ . If not, the area integrating will not begin and the SR driver will be disabled.

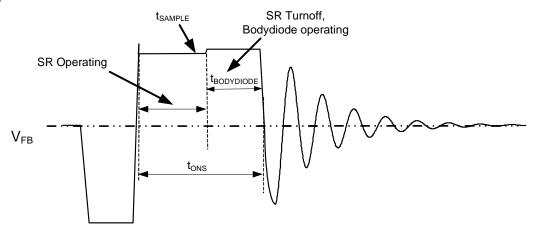

#### SR Turning off Timing Impact on PSR CV Sampling

As to synchronous rectification on Flyback power system, SR MOSFET need to turn off in advance of secondary side current decreasing to zero to avoid current flowing reversely. When SR turns off in advance, the secondary current will flow through the body diode. The SR turning off time is determined by the  $V_{THOFF}$  at a fixed system. When  $V_{THOFF}$  is more close to zero, the SR turning on time gets longer and body diode conduction time gets shorter. Since of the different voltage drop between SR MOSFET and body diode, the PSR feedback signal  $V_{FB}$  appears a voltage jump at the time of SR MOSFET turning off. If the PSR CV sampling time  $t_{SAMPLE}$  is close to even behind this voltage jump time, there will be system unstable operation issue or the lower output voltage issue.

## **Operation Description (Cont.)**

To ensure stable operating of system, it must be met:

$t_{BODYDIODE} < t_{ONS}^* (1 - t_{SAMPLE})$

Figure 4. SR Turning off Timing Impact on PSR CV Sampling

#### **Recommended Application Circuit Parameters**

The two resistors R23 and R24 are used to pass ESD test. The value of R23 and R24 should be over  $20\Omega$  and below  $47\Omega$  respectively because of the undershoot performance. The package of R23 and R24 should be at least 0805 and there isn't any trace under these two resistors.

$C_{AREF}$  is suggested to parallel with AREF resistor to keep the volt-second product threshold stable. And the recommended value of  $C_{AREF}$  is 100nF. The recommended value of C24 is 100nF.

## **Ordering Information**

| Package | Temperature Range | Part Number   | Marking ID | Packing          |

|---------|-------------------|---------------|------------|------------------|

| SO-8    | -40 to +85°C      | APR3415MTR-G1 | 3415M-G1   | 4000/Tape & Reel |

APR3415 Document number: DS36738 Rev. 7 - 2

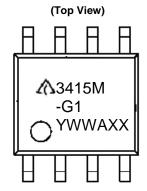

## **Marking Information**

First and Second Lines: Logo and Marking ID

Third Line: Date Code

Y: Year

WW: Work Week of Molding

A: Assembly House Code

XX: 7<sup>th</sup> and 8<sup>th</sup> Digits of Batch No.

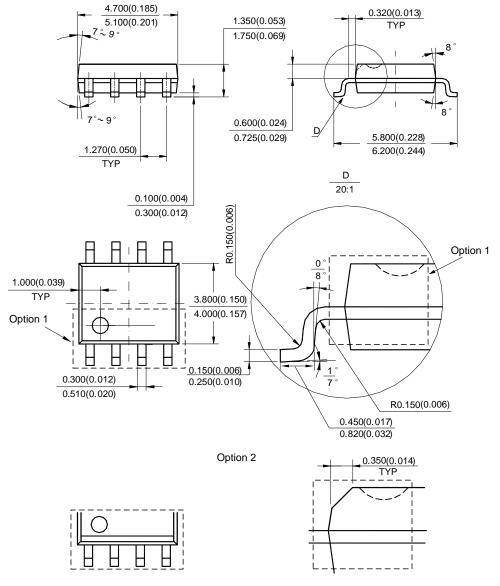

## Package Outline Dimensions (All dimensions in mm(inch).)

#### (1) Package Type: SO-8

Note: Eject hole, oriented hole and mold mark is optional.

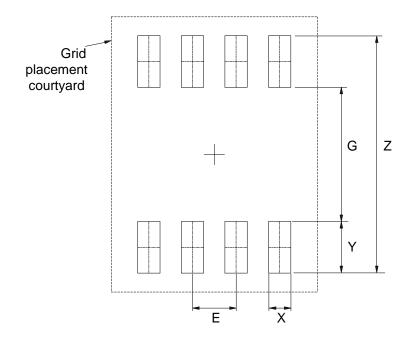

# **Suggested Pad Layout**

(1) Package Type: SO-8

| Dimensions | Z           | G           | X           | Y           | E           |

|------------|-------------|-------------|-------------|-------------|-------------|

|            | (mm)/(inch) | (mm)/(inch) | (mm)/(inch) | (mm)/(inch) | (mm)/(inch) |

| Value      | 6.900/0.272 | 3.900/0.154 | 0.650/0.026 | 1.500/0.059 | 1.270/0.050 |

June 2015

#### **IMPORTANT NOTICE**

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### **LIFE SUPPORT**

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2015, Diodes Incorporated

www.diodes.com

13 of 13 APR3415 Document number: DS36738 Rev. 7 - 2 © Diodes Incorporated

# 单击下面可查看定价,库存,交付和生命周期等信息

>>Diodes Incorporated(达迩科技(美台))