PI6ULS5V9306

### Dual Bidirectional I2C-Bus and SMBus Voltage-Level Translator

## Features

- → 2-bit Bidirectional Translator for SDA and SCL Lines in Mixed-Mode I2C-Bus Applications

- ➔ Standard-Mode, Fast-Mode, and Fast-Mode Plus I2C-Bus and SMBus Compatible

- → Less than 1.5ns Maximum Propagation Delay to Accommodate Standard Mode and Fast Mode I2C-Bus Devices and Multiple Masters

- → Allows Voltage Level Translation Between:

- 0.9V VREF1 and 1.8V, 2.5V, 3.3V, or 5V VREF2

- 1.2V VREF1 and 1.8V, 2.5V, 3.3V, or 5V VREF2

- 1.5V VREF1 and 2.5V, 3.3V, or 5V VREF2

- 1.8V VREF1 and 3.3V or 5V VREF2

- 2.5V VREF1 and 5V VREF2

- 3.3V VREF1 and 5V VREF2

- ➔ Provides Bidirectional Voltage Translation with no Direction Pin

- → Low 3.5Ω ON-State Connection Between Input and Output Ports Provides Less Signal Distortion

- → Open-Drain I2C-Bus I/O Ports (SCL1, SDA1, SCL2, and SDA2)

- → 5V Tolerant I2C-Bus I/O Ports to Support Mixed-Mode Signal Operation

- → High-Impedance SCL1, SDA1, SCL2, and SDA2 Pins for EN = LOW

- → Lock-up Free Operation for Isolation when EN = LOW

- ➔ Flow through Pinout for Ease of Printed-Circuit Board Trace Routing

- → ESD Protection Exceeds 4KV HBM per JESD22-A114

- → Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- → Halogen and Antimony Free. "Green" Device (Note 3)

- ➔ For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please <u>contact us</u> or your local Diodes representative.

- https://www.diodes.com/quality/product-definitions/

- ➔ Package: TDFN2x3-8(ZE), MSOP-8(U), SOIC-8(W), UQFN1.6x1.6-8(XT)

## Description

The PI6ULS5V9306 is a dual bidirectional I<sup>2</sup>C-bus and SMBus voltage-level translator with an enable (EN) input. It is operational from 1.0V to 3.3V (VREF1) and 1.8V to 5.5V (VREF2).

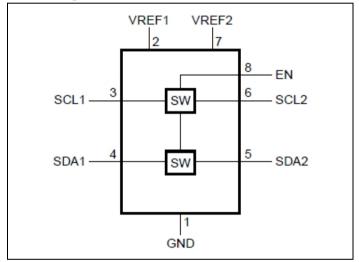

The PI6ULS5V9306 allows bidirectional voltage translations between 1.0V and 5V without the use of a direction pin. The low ON-state resistance (Ron) of the switch allows connections to be made with minimal propagation delay. When EN is HIGH, the translator switch is on, and the SCL1 and SDA1 I/O are connected to the SCL2 and SDA2 I/O respectively, allowing bidirectional data flow between ports. When EN is LOW, the translator switch is off, and a high-impedance state exists between ports.

#### **Block Diagram**

#### **Figure.1 Block Diagram**

| EN | Function     |

|----|--------------|

| Н  | SCL1 = SCL2; |

| п  | SDA1 = SDA2  |

| L  | disabled     |

Notes:

1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.</li>

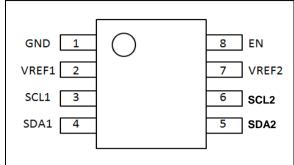

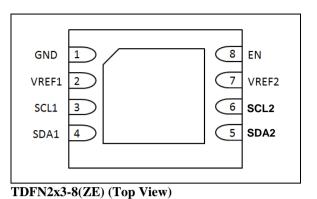

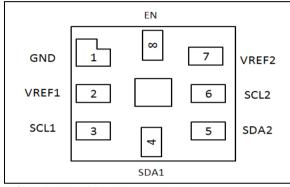

**Pin Configuration**

UQFN1.6x1.6-8(XT) (Top View)

# **Pin Description**

| Pin# | Name  | Description                                                                 |  |  |

|------|-------|-----------------------------------------------------------------------------|--|--|

| 1    | GND   | Ground (0V)                                                                 |  |  |

| 2    | VREF1 | ow-voltage side reference supply voltage for SCL1 and SDA1                  |  |  |

| 3    | SCL1  | Serial clock, low-voltage side; connect to VREF1 through a pullup resistor  |  |  |

| 4    | SDA1  | Serial data, low-voltage side; connect to VREF1 through a pullup resistor   |  |  |

| 5    | SDA2  | Serial data, high-voltage side; connect to VREF2 through a pullup resistor  |  |  |

| 6    | SCL2  | Serial clock, high-voltage side; connect to VREF2 through a pullup resistor |  |  |

| 7    | VREF2 | High-voltage side reference supply voltage for SCL2 and SDA2                |  |  |

| 8    | EN    | Switch enable input; connect to VREF2 and pullup through a high resistor    |  |  |

# **Maximum Ratings**

| Storage Temperature              | -65°C to +150°C |

|----------------------------------|-----------------|

| Reference Voltage <sup>(2)</sup> | -0.5V to +6.0V  |

| Reference Bias Voltage           |                 |

| DC Input Voltage                 | -0.5V to +6.0V  |

| Control Input Voltage (EN)       | -0.5V to+6.0V   |

| Channel Current (DC)             |                 |

| Input Clamping Current           | 50mA            |

| ESD: HBM Mode                    | 4000V           |

Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Recommended Operation Conditions**

Vcc = 2.7V to 5.5V; GND = 0V;  $T_A = -40^{\circ}C$  to +85°C; unless otherwise specified.

| Symbol              | Parameter                             | Test Conditions        | Min. | Typ. | Max. | Unit |

|---------------------|---------------------------------------|------------------------|------|------|------|------|

| V <sub>I/O</sub>    | Voltage on an Input/Output Pin        | SCL1, SDA1, SCL2, SDA2 | 0    |      | 5    | V    |

| V <sub>REF1</sub>   | Reference Voltage <sup>(1)</sup>      | VREF1                  | 0    |      | 5    | V    |

| V <sub>REF2</sub>   | Reference Bias Voltage <sup>(2)</sup> | VREF2                  | 0    |      | 5    | V    |

| V <sub>I(EN)</sub>  | Input Voltage on Pin EN               | _                      | 0    |      | 5    | V    |

| I <sub>(pass)</sub> | Pass Switch Current                   | _                      |      |      | 64   | mA   |

| T <sub>A</sub>      | Ambient Temperature                   | —                      | -40  | —    | 85   | °C   |

### **DC Electrical Characteristics**

$T_A = -40$ °C to +85°C; unless otherwise specified.

| Parameter            | Description                                       | Test Conditio                             | Test Conditions <sup>(1)</sup> |    | <b>Typ.</b> <sup>(2)</sup> | Max  | Unit |

|----------------------|---------------------------------------------------|-------------------------------------------|--------------------------------|----|----------------------------|------|------|

| Input and (          | Dutput SDAB and SCLB                              | •                                         |                                | •  |                            |      | •    |

| V <sub>IK</sub>      | Input Clamping Voltage                            | $I_{I} = -18mA; V_{I}$                    | I(EN) = 0V                     | —  | _                          | -1.2 | V    |

| I <sub>IH</sub>      | HIGH-Level Input Current                          | $V_{I} = 5V; V_{I(EN)}$                   | = 0V                           |    |                            | 5    | μA   |

| C <sub>i(EN)</sub>   | Input Capacitance on pin EN                       | $V_I = 3V \text{ or } 0V$                 |                                |    | 11                         |      | pF   |

| C <sub>io(off)</sub> | Off-State Input/Output Capacitance (SCLn, SDAn)   | $V_0 = 3V \text{ or } 0V$                 | $V; V_{I(EN)} = 0V$            | _  | 4                          |      | pF   |

| C <sub>io(on)</sub>  | On-State Input/Output Capacitance<br>(SCLn, SDAn) | $V_0 = 3V \text{ or } 0V; V_{I(EN)} = 3V$ |                                | _  | 10.5                       |      | pF   |

|                      |                                                   | $V_{I} = 0V;$ $I_{O} = 64mA$              | $V_{I(EN)}\!=\!4.5V$           |    | 3.5                        | 5.5  | Ω    |

|                      |                                                   |                                           | $V_{I(EN)} = 3V$               |    | 4.7                        | 7.0  | Ω    |

|                      |                                                   |                                           | $V_{I(EN)} = 2.3V$             |    | 6.3                        | 9.5  | Ω    |

| Ron                  | ON-State Resistance <sup>(2)</sup>                |                                           | $V_{I(EN)}\!=\!1.5V$           |    | 60                         | 140  | Ω    |

|                      | (SCLn, SDAn)                                      | $V_{I} = 2.4V;$                           | $V_{I(EN)} \!= 4.5 V$          | 1  | 6                          | 15   | Ω    |

|                      |                                                   | $I_0 = 15 \text{mA}$                      | $V_{I(EN)} = 3V$               | 20 | 60                         | 140  | Ω    |

|                      |                                                   | $V_{I} = 1.7V;$<br>$I_{O} = 15mA$         | $V_{I(EN)} \!=\! 2.3V$         | 20 | 60                         | 140  | Ω    |

1. All typical values are at  $T_A = 25$  °C.

2. Measured by the voltage drop between the SCL1 and SCL2 or SDA1 and SDA2 terminals at the indicated current through the switch. ON-state resistance is determined by the lowest voltage of the two terminals.

## **Dynamic Characteristics**

$T_A = -40^{\circ}$ C to  $+85^{\circ}$ C; unless otherwise specified. Values guaranteed by design.

| Symbol            | Parameter                                                   | Conditions                                            | C <sub>L</sub> = | 50pF | $C_L = 30 pF$ |     | $C_L = 15 pF$ |     | Unit |

|-------------------|-------------------------------------------------------------|-------------------------------------------------------|------------------|------|---------------|-----|---------------|-----|------|

| Symbol            | 1 ai ainetei                                                |                                                       |                  | Max  | Min           | Max | Min           | Max | Omt  |

| Dynamic C         | Characteristics (Transla                                    | ating Down)                                           |                  |      |               |     |               |     |      |

| $V_{I(EN)} = 3.3$ | $SV; V_{IH} = 3.3V; V_{IL} =$                               | $0V; V_{M} = 1.15V$                                   |                  |      |               |     |               |     |      |

| t <sub>PLH</sub>  | LOW-to-HIGH<br>Propagation Delay                            | From (Input) SCL2 or SDA2<br>to (Output) SCL1 or SDA1 | 0                | 0.8  | 0             | 0.6 | 0             | 0.3 | ns   |

| t <sub>PHL</sub>  | HIGH-to-LOW<br>Propagation Delay                            | From (Input) SCL2 or SDA2<br>to (Output) SCL1 or SDA1 | 0                | 1.2  | 0             | 1   | 0             | 0.5 | ns   |

| $V_{I(EN)} = 2.5$ | $V_{I(EN)} = 2.5V; V_{IH} = 2.5V; V_{IL} = 0V; V_M = 0.75V$ |                                                       |                  |      |               |     |               |     |      |

| t <sub>PLH</sub>  | LOW-to-HIGH<br>Propagation Delay                            | From (Input) SCL2 or SDA2<br>to (Output) SCL1 or SDA1 | 0                | 1    | 0             | 0.7 | 0             | 0.4 | ns   |

| t <sub>PHL</sub>  | HIGH-to-LOW<br>Propagation Delay                            | From (Input) SCL2 or SDA2<br>to (Output) SCL1 or SDA1 | 0                | 1.3  | 0             | 1   | 0             | 0.6 | ns   |

| Dynamic           | Characteristics (Tran                                       | slating up)                                           |                  | •    |               | •   |               | •   |      |

| $V_{I(EN)} = 3.3$ | $SV; V_{IH} = 2.3V; V_{IL} =$                               | $0V; V_{T} = 3.3V; V_{M} = 1.15V; R_{L} =$            | 300Ω             |      |               |     |               |     |      |

| t <sub>PLH</sub>  | LOW-to-HIGH<br>Propagation Delay                            | From (Input) SCL1 orSDA1<br>to (output) SCL2 or SDA2  | 0                | 0.9  | 0             | 0.6 | 0             | 0.4 | ns   |

| t <sub>PHL</sub>  | HIGH-to-LOW<br>Propagation Delay                            | From (Input) SCL1 or SDA1<br>to (Output) SCL2 or SDA2 | 0                | 1.4  | 0             | 1.1 | 0             | 0.7 | ns   |

| $V_{I(EN)} = 2.5$ | $V; V_{IH} = 1.5V; V_{IL} =$                                | $0V; V_T = 2.5V; V_M = 0.75V; R_L =$                  | 300Ω             |      |               |     |               |     |      |

| t <sub>PLH</sub>  | LOW-to-HIGH<br>Propagation Delay                            | From (Input) SCL1 orSDA1<br>to (Output) SCL2 or SDA2  | 0                | 1    | 0             | 0.6 | 0             | 0.4 | ns   |

| t <sub>PHL</sub>  | HIGH-to-LOW<br>Propagation Delay                            | From (Input) SCL1 or SDA1<br>to (Output) SCL2 or SDA2 | 0                | 1.3  | 0             | 1.3 | 0             | 0.8 | ns   |

B. All input pulses are supplied by generators having the following characteristics: PRR

C. The outputs are measured one at a time, with one transition per measurement.

isured one at a unie, with one transition per measurement.

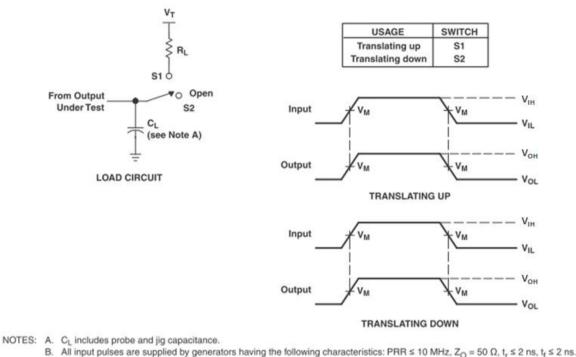

#### Figure 2. Load Circuit for Outputs

## **Functional Description**

The PI6ULS5V9306 can also be used to run two buses—one at 400kHz operating frequency and the other at 100kHz operating frequency. If the two buses are operating at different frequencies, the 100kHz bus must be isolated when the 400kHz operation of the other bus is required. If the master is running at 400kHz, the maximum system operating frequency may be less than 400kHz because of the delays added by the translator.

As with the standard I<sup>2</sup>C-bus system, pullup resistors are required to provide the logic HIGH levels on the translator's bus. The PI6ULS5V9306 has a standard open-collector configuration of the I<sup>2</sup>C-bus. Each side of the translator must have a pullup resistor though the size of these pullup resistors depends on the system. The device is designed to work with standard mode, fast mode, and fast mode plus I<sup>2</sup>C-bus devices in addition to SMBus devices.

When the SDA1 or SDA2 port is LOW, the clamp is in the ON-state and a low-resistance connection exists between the SDA1 and SDA2 ports. When the higher voltage is on the SDA2 port, and the SDA2 port is HIGH, the voltage on the SDA1 port is limited to the voltage set by VREF1. When the SDA1 port is HIGH, the SDA2 port is pulled to the drain pullup supply voltage (VDPU) by the pullup resistors. This functionality allows a seamless translation between higher and lower voltages selected by the user without requiring directional control. The SCL1/SCL2 channel also functions as the SDA1/SDA2 channel.

All channels have the same electrical characteristics, and there is minimal deviation from one output to another in voltage or propagation delay. This is a benefit over discrete transistor voltage translation solutions because the fabrication of the switch is symmetrical. The translator provides excellent ESD protection to lower voltage devices, and at the same time protects less ESD-resistant devices

www.diodes.com 5 December 2019 © Diodes Incorporated

# **Application Information**

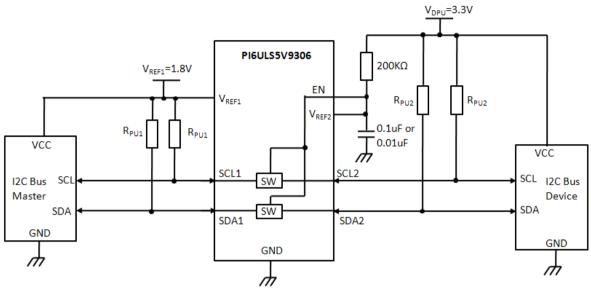

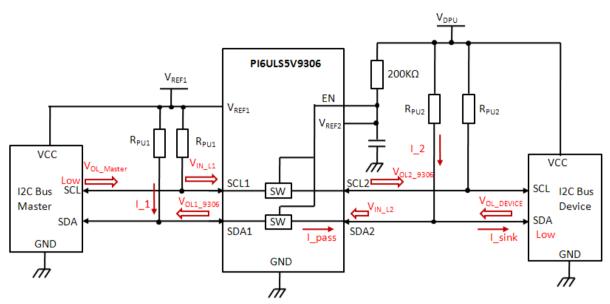

Figure 3. Typical Open-Drain Application Circuit (Switch Always Enabled)

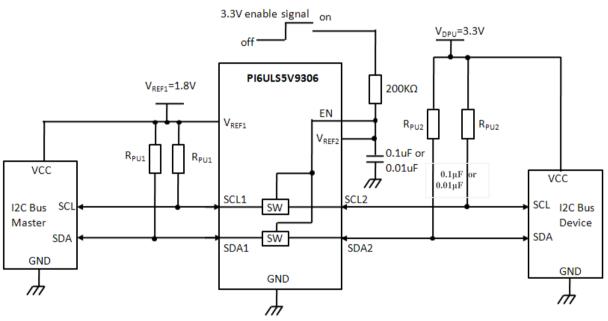

Figure 4. Typical Open-Drain Application Circuit (Switch Enabled Control)

# **Open-Drain Application**

For the bidirectional clamping configuration (higher voltage to lower voltage or lower voltage to higher voltage), the EN input must be connected to VREF2 and both pins pulled to high-side VDPU through a pullup resistor (typically 200k $\Omega$ ). This allows VREF2 to regulate the EN input. A filter capacitor on VREF2 is recommended.

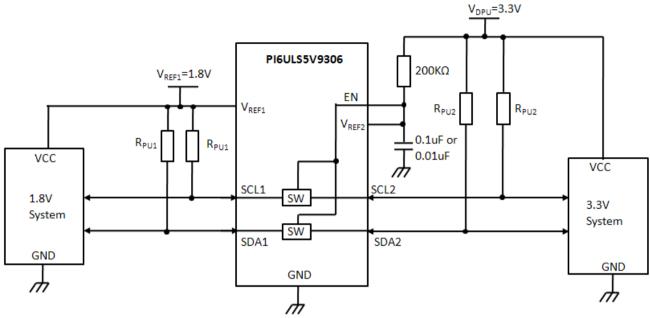

Figure 5. Typical Push-Pull Application Circuit (Switch Enabled Control)

## **Push-Pull Application**

If used in push-pull system, the pullup resistors on REF side are also required. The data must be unidirectional, or the outputs must be 3-stateable and controlled by some direction-control mechanism to prevent high-to-low contentions in either direction.

# **Operating Voltage**

Refer to Figure 2

| Symbol | Description                              | Min         | Typ <sup>(1)</sup> | Max | Unit |

|--------|------------------------------------------|-------------|--------------------|-----|------|

| VDPU   | Ref2 Side Pullup Voltage on $200k\Omega$ | VREF1 + 0.6 | 2.1                | 5   | V    |

| EN     | Enable Input Voltage                     | VREF1 + 0.6 | 2.1                | 5   | V    |

| VREF1  | Reference Voltage                        | 0           | 1.5                | 4.4 | V    |

| IPASS  | Pass Switch Current                      | 14          |                    |     | mA   |

| IREF   | Reference-Transistor Current             |             |                    | 5   | μA   |

| TA     | Operating Free-Air Temperature           | -40         |                    | 85  | °C   |

## The Pass-Through Current: I\_pass

I\_pass is determined by the pullup and the low voltage added on the PI6LS5V9306.

In Figure 6, I\_pass equals (V<sub>REF1</sub>-V<sub>OL1\_9306</sub>)/R<sub>PU1</sub>.

When V\_IN is 0V, the PI6ULS5V9306 can support as large as 64mA pass-through current in theory, but it is recommend to limit the I\_pass in 15mA.

Figure 6. Typical Open-Drain Application Circuit

(1) The Sink Current: I\_sink

The device sinks the total current from both pullup resistors. For example, in figure below, when the SDA2 is pulled low by the I2C device, the sink current of the I2C device is  $I_sink = Ipass+I_2=I_1+I_2$ . The same thing happens when I2C master pulls low the I2C bus. The I\_sink should not be larger than the tolerance of the I2C devices.

(2)  $V_{\rm IL}\!,\!V_{\rm OL}$  of the External Drive and  $V_{\rm OL}$  of PI6ULS5V9306

In normal application, the  $V_{IL}$  of external devices should always be larger than the  $V_{OL}$  of PI6ULS5V9306. The value of PI6ULS5V9306's  $V_{OL}$  is determined by the pass-through current and the low voltage added on the SDA, SCL pins. The  $V_{OL_{9306}} = V_{IN_{L}} + V_{UP}$  ( $V_{UP}$  is mainly determined by the I\_pass, which is always less than 0.35V).

## (3) Low VREF Application

The PI6ULS5V9306 can support very-low Vref1 application in theory, but it is recommended no lower than 0.9V. Because when VREF1 is less than 1.8V, the  $V_{OL}$  of REF1 side is a concern in system. For example, in Figure 6, if VREF1 = 0.9V, VDPU = 3.3V, the  $V_{IL}$  of the REF1 side I2C master is normally 0.3 × VREF1 = 0.25V, but the  $V_{OL}$  of REF2 side can up to 0.1 × VDPU=0.36V. The system designer must make sure this situation does not happen. A limit for the  $V_{OL}$  of REF2 side devices is required then.

The following table shows the requirements for  $V_{OL}$  of VREF2 side devices when using PI6ULS5V9306. Figure 6 shows the requirement for  $V_{OL\_DEVICE}$ .

| The V <sub>OL</sub> Requirement of V <sub>REF2</sub> Side External Devices<br>(Temp = 25°C, Assume the V <sub>IL</sub> of V <sub>REF1</sub> Side Devices is $0.3 \times V_{REF1}$ ) |        |        |                 |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|-----------------|--|--|--|

| I_pass ≤3mA 10mA 15mA                                                                                                                                                               |        |        |                 |  |  |  |

| V <sub>REF1</sub>                                                                                                                                                                   |        |        |                 |  |  |  |

| 0.9V                                                                                                                                                                                | ≤0.15V | ≤0.1V  | Not Recommended |  |  |  |

| 1.2V                                                                                                                                                                                | ≤0.2V  | ≤0.15V | Not Recommended |  |  |  |

| 1.5V                                                                                                                                                                                | ≤0.3V  | ≤0.25V | ≤0.2V           |  |  |  |

| 1.8V                                                                                                                                                                                | ≤0.4V  | ≤0.35V | ≤0.3V           |  |  |  |

## **Pullup Resistors and Minimum Values**

Sizing the pullup resistor on an open-drain bus is specific to the individual application and is dependent on the following driver characteristics:

- The driver sink current

- The VOL of driver

- The V<sub>OL</sub> of the PI6ULS5V9306

- The V<sub>IL</sub> of the driver

- Frequency of operation

The following tables can be used to estimate the pullup resistor value in different use cases so that the minimum resistance for the pullup resistor can be found.

The tables below show suggested minimum values of pullup resistors for the PI6ULS5V9306 with typical voltage translation levels and drive currents. The calculated values assume that both drive currents are the same.

$V_{OL} = V_{IL} = 0.1 \times VCC$  and accounts for a 5% VCC tolerance of the supplies, 1 % resistor values. Note that the resistor chosen in the final application should be equal to or larger than the values shown in the table to ensure that the pass voltage is less than 10% of the VCC voltage, and the external driver should be able to sink the total current from both pullup resistors.

| A Side |                                                                                |                                                                                    | B Side                                                                                           |                                                                                                         |                                                                                                      |

|--------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

|        | 1.5V                                                                           | 1.8V                                                                               | 2.5V                                                                                             | 3.3V                                                                                                    | 5.0V                                                                                                 |

| 0.9V   | $\begin{aligned} R_{RPU1} &= 859\Omega \\ R_{RPU2} &= 859\Omega \end{aligned}$ | $\begin{aligned} R_{RPU1} &= 970\Omega \\ R_{RPU2} &= 970\Omega \end{aligned}$     | $\begin{aligned} R_{RPU1} &= none \\ R_{RPU2} &= 896\Omega \\ or both 1.23k\Omega \end{aligned}$ | $\begin{split} R_{RPU1} &= none \\ R_{RPU2} &= 1.19 k\Omega \\ or both 1.53 k\Omega \end{split}$        | $R_{RPU1} = none$<br>$R_{RPU2} = 1.82k\Omega$<br>or both 2.16k $\Omega$                              |

| 1.2V   | _                                                                              | $\begin{split} R_{RPU1} &= 1.07 k \Omega \\ R_{RPU2} &= 1.07 k \Omega \end{split}$ | $K_{\rm DDU2} \equiv \delta \delta \Omega Q$                                                     |                                                                                                         | $R_{RPU1} = none$ $R_{RPU2} = 1.81k\Omega$ or both 2.26kΩ                                            |

| 1.5V   | _                                                                              | _                                                                                  | $R_{RPU1} = none$ $R_{RPU2} = 875\Omega$ or both 1.43kΩ                                          | $ \begin{array}{l} R_{RPU1} = none \\ R_{RPU2} = 1.17 k\Omega \\ or \ both \ 1.73 k\Omega \end{array} $ | $\begin{aligned} R_{RPU1} &= none \\ R_{RPU2} &= 1.8 k\Omega \\ or both 2.36 k\Omega \end{aligned}$  |

| 1.8V   | _                                                                              | _                                                                                  | $\begin{split} R_{RPU1} &= 1.53 k \Omega \\ R_{RPU2} &= 1.53 k \Omega \end{split}$               | $\begin{split} R_{RPU1} &= none \\ R_{RPU2} &= 1.16 k\Omega \\ or both 1.82 k\Omega \end{split}$        | $\begin{aligned} R_{RPU1} &= none \\ R_{RPU2} &= 1.79 k\Omega \\ or both 2.46 k\Omega \end{aligned}$ |

| 2.5V   | _                                                                              | _                                                                                  | _                                                                                                | $\begin{split} R_{RPU1} &= 2.06 k \Omega \\ R_{RPU2} &= 2.06 k \Omega \end{split}$                      | $\begin{split} R_{RPU1} &= none \\ R_{RPU2} &= 1.77 k\Omega \\ or both 2.69 k\Omega \end{split}$     |

| 3.3V   | _                                                                              | _                                                                                  |                                                                                                  | _                                                                                                       | $\begin{split} R_{RPU1} &= none \\ R_{RPU2} &= 1.74 k\Omega \\ or both 2.96 k\Omega \end{split}$     |

Pullup Resistor Minimum Values, 3mA Driver Sink Current for PI6ULS5V9306

A Side B Side 1.5V 1.8V 2.5V 3.3V 5.0V 0.9V  $R_{RPU1} = 258\Omega$  $R_{RPU1} = 291\Omega$  $R_{RPU1} = none$  $R_{RPU1} = none$  $R_{RPU1} = none$  $R_{RPU2} = 258\Omega$  $R_{RPU2} = 291\Omega$  $R_{RPU2} = 269\Omega$  $R_{RPU2} = 358\Omega$  $R_{RPU2} = 546\Omega$ or both  $369\Omega$ or both  $458\Omega$ or both  $646\Omega$  $\overline{R_{RPU1}} = 321\Omega$ 1.2V  $R_{RPU1} = none$  $R_{RPU1} = none$  $R_{RPU1} = none$  $R_{RPU2} = 266\Omega$  $R_{RPU2} = 321\Omega$  $R_{RPU2} = 355\Omega$  $R_{RPU2} = 543\Omega$ or both  $677\Omega$ or both  $399\Omega$ or both  $488\Omega$ 1.5V  $R_{RPU1} = none$  $R_{RPU1} = none$  $R_{RPU1} = none$  $R_{RPU2} = 263\Omega$  $R_{RPU2} = 352\Omega$  $R_{RPU2} = 540\Omega$ or both  $429\Omega$ or both  $518\Omega$ or both  $707\Omega$ 1.8V  $R_{RPU1}\,{=}\,460\Omega$  $R_{RPU1} = none$  $R_{RPU1} = none$  $R_{RPU2}\!=348\Omega$  $R_{RPU2}\,{=}\,460\Omega$  $R_{RPU2}\!=537\Omega$ or both  $548\Omega$ or both  $737\Omega$ 2.5V  $R_{RPU1} = 619\Omega$  $\overline{R}_{RPU1} = none$ \_\_\_\_ \_\_\_\_  $R_{RPU2} = 619\Omega$  $R_{RPU2} = 521\Omega$ or both  $808\Omega$ 3.3V  $R_{RPU1} = none$  $R_{RPU2}\!=522\Omega$ or both  $889\Omega$

#### Pullup Resistor Minimum Values, 10mA Driver Sink Current for PI6ULS5V9306

Pullup Resistor Minimum Values, 15mA Driver Sink Current for PI6ULS5V9306

| A Side |                                                                            |                                                                                | B Side                                                                                         |                                                                                                 |                                                                                                 |

|--------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

|        | 1.5V                                                                       | 1.8V                                                                           | 2.5V                                                                                           | 3.3V                                                                                            | 5.0V                                                                                            |

| 0.9V   | $\begin{split} R_{RPU1} &= 172\Omega \\ R_{RPU2} &= 172\Omega \end{split}$ | $\begin{aligned} R_{RPU1} &= 194\Omega \\ R_{RPU2} &= 194\Omega \end{aligned}$ | $\begin{aligned} R_{RPU1} &= none \\ R_{RPU2} &= 179\Omega \\ or both 246\Omega \end{aligned}$ | $\begin{aligned} R_{RPU1} &= none \\ R_{RPU2} &= 238\Omega \\ or both 305\Omega \end{aligned}$  | $R_{RPU1} = none$ $R_{RPU2} = 364\Omega$ or both 431\Omega                                      |

| 1.2V   |                                                                            | $\begin{aligned} R_{RPU1} &= 214\Omega \\ R_{RPU2} &= 214\Omega \end{aligned}$ | $\begin{split} R_{RPU1} &= none \\ R_{RPU2} &= 177\Omega \\ or both \ 266\Omega \end{split}$   | $\begin{array}{l} R_{RPU1} = none \\ R_{RPU2} = 236\Omega \\ or \ both \ 325\Omega \end{array}$ | $\begin{aligned} R_{RPU1} &= none \\ R_{RPU2} &= 362\Omega \\ or both 451\Omega \end{aligned}$  |

| 1.5V   | _                                                                          |                                                                                | $\begin{aligned} R_{RPU1} &= none \\ R_{RPU2} &= 175\Omega \\ or both 286\Omega \end{aligned}$ | $\begin{array}{l} R_{RPU1} = none \\ R_{RPU2} = 234\Omega \\ or \ both \ 345\Omega \end{array}$ | $R_{RPU1} = none$ $R_{RPU2} = 360\Omega$ or both 471\Omega                                      |

| 1.8V   | _                                                                          | _                                                                              | $\begin{aligned} R_{RPU1} &= 306\Omega \\ R_{RPU2} &= 306\Omega \end{aligned}$                 | $\begin{array}{l} R_{RPU1} = none \\ R_{RPU2} = 232\Omega \\ or \ both \ 366\Omega \end{array}$ | $\begin{array}{l} R_{RPU1} = none \\ R_{RPU2} = 358\Omega \\ or \ both \ 492\Omega \end{array}$ |

| 2.5V   | _                                                                          | _                                                                              | _                                                                                              | $\begin{aligned} R_{RPU1} &= 413\Omega \\ R_{RPU2} &= 413\Omega \end{aligned}$                  | $\begin{aligned} R_{RPU1} &= none \\ R_{RPU2} &= 354\Omega \\ or both 539\Omega \end{aligned}$  |

| 3.3V   | _                                                                          | _                                                                              | _                                                                                              | _                                                                                               | $R_{RPU1} = none$ $R_{RPU2} = 348\Omega$ or both 593 $\Omega$                                   |

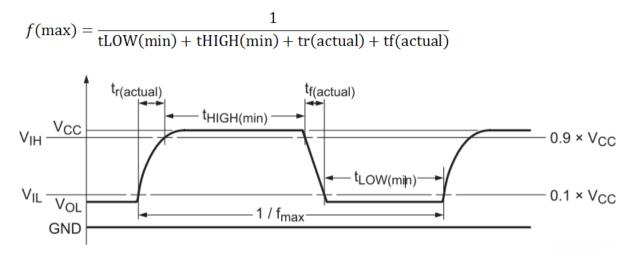

#### **Maximum Frequency Application**

The maximum frequency is limited by the minimum pulse width LOW and HIGH as well as rise time and fall time.

The rise and fall times are dependent upon translation voltages, the drive strength, the total node capacitance (CL), and the pullup resistors (RPU) that are present on the bus. The node capacitance is the addition of the PCB trace capacitance and the device capacitance that exists on the bus.

Because of the dependency of the external components, PCB layout and the different device operating states the calculation of rise and fall times is complex and has several inflection points along the curve.

The main component of the rise and fall times is the RC time constant of the bus line when the device is in its two primary operating states: when device is in the ON state and it is low-impedance and when the device is OFF isolating the A-side from the B-side.

There are some basic guidelines to follow that will help maximize the performance of the device:

- Keep trace length to a minimum by placing the PI6ULS5V9306 close to the processor.

- The signal round trip time on trace should be shorter than the rise or fall time of signal to reduce reflections.

- The faster the edge of the signal, the higher the chance for ringing.

- The higher drive strength controlled by the pullup resistor (up to 15mA), the higher the frequency the device can use.

The system designer must design the pullup resistor value based on external current drive strength and limit the node capacitance (minimize the wire, stub, connector, and trace length) to get the desired operation frequency result.

# **Part Marking**

W Package Cu

Z: Die Rev Y: Date Code (Year) W: Date Code (Workweek) 1st X: Assembly Site Code 2nd X: Wafer Fab Site Code Bar above fab code means Cu wire

Note: Bar above "I" means Fab3 og MGN

ZE Package

J: Assembly Site Code G: Fab Site Code XX: Date Code (Year & Workweek) Bar above "A" means Fab3 of MGN W Package Au

Z: Die Rev AB: Date Code (Year & Workweek) K: Assembly Site Code G: Wafer Fab Site Code

Z: Die Rev Y: Date Code (Year) W: Date Code (Workweek) 1st X: Assembly Site Code 2nd X: Wafer Fab Site Code Bar above fab code means Cu wire

Y: Year W: Workweek

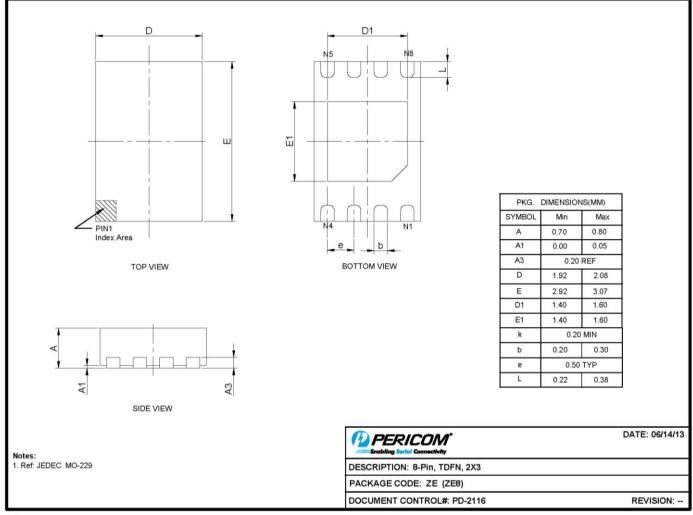

# **Packaging Mechanical**

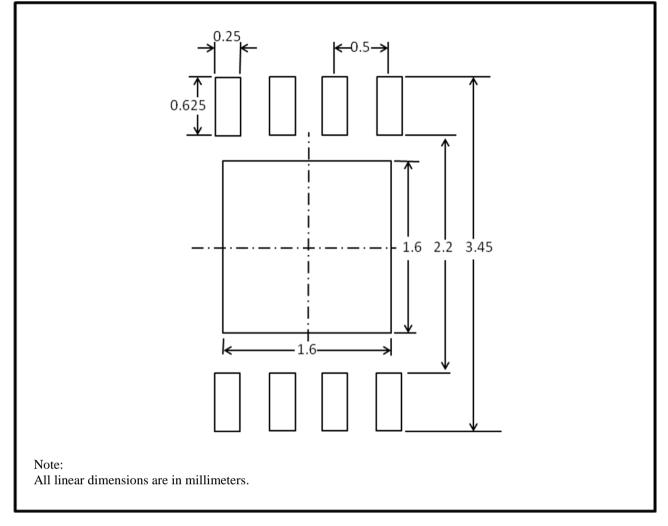

TDFN-8 (ZE)

13-0155

# **Recommended Land Pattern for TDFN2x3-8L**

PI6ULS5V9306

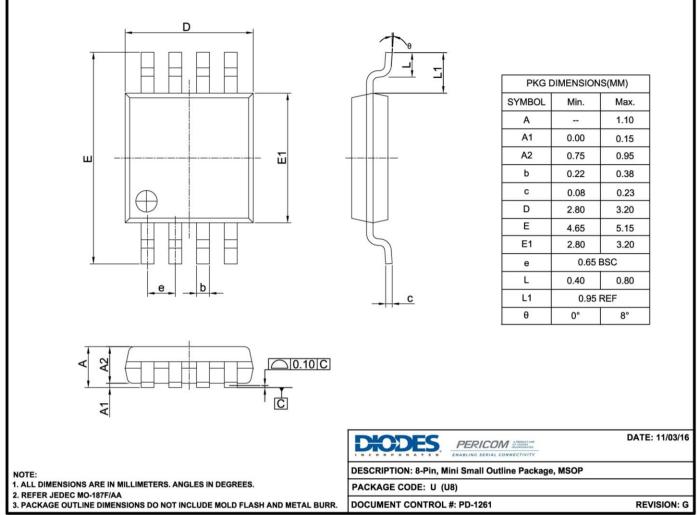

### MSOP-8(U)

16-0242

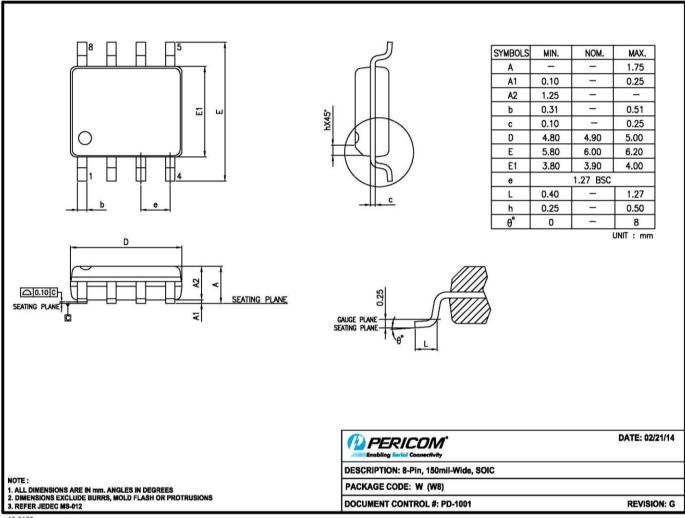

SOIC-8(W)

15-0103

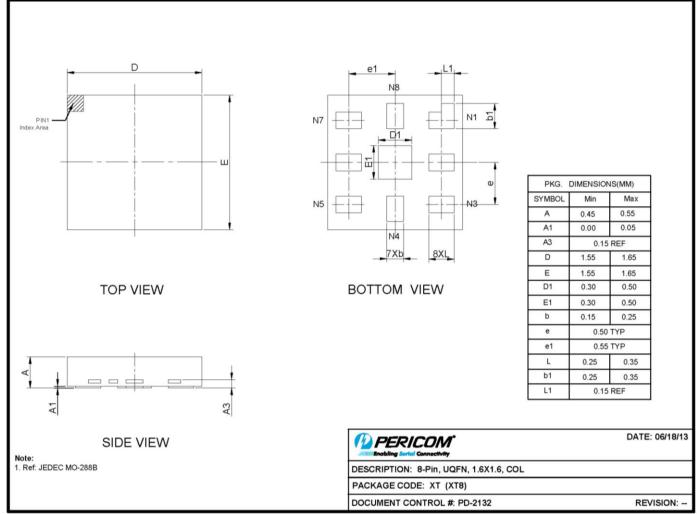

UQFN-8 (XT)

13-0171

#### For latest package information:

See http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/.

# **Ordering Information**

| Part Number      | Package Code | Package Description                                                                                                     |

|------------------|--------------|-------------------------------------------------------------------------------------------------------------------------|

| PI6ULS5V9306ZEEX | ZE           | 8-Pin, 2X3 (TDFN)                                                                                                       |

| PI6ULS5V9306UEX  | U            | 8-Pin, Mini Small Outline Package (MSOP)                                                                                |

| PI6ULS5V9306WEX  | W            | 8-Pin,150 mil Wide (SOIC)                                                                                               |

| PI6ULS5V9306XTEX | XT           | 8-pin, 1.6x1.6, COL (UQFN)<br>*Not Recommend for New Design. Please contact with local Diodes Sales<br>representatives. |

Notes:

1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

4. E = Pb-free and Green

5. X suffix = Tape/Reel

#### PI6ULS5V9306

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

A. Life support devices or systems are devices or systems which:

1. are intended to implant into the body, or

2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the

failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2019, Diodes Incorporated www.diodes.com 单击下面可查看定价,库存,交付和生命周期等信息

>>Diodes Incorporated(达迩科技(美台))