### **Description**

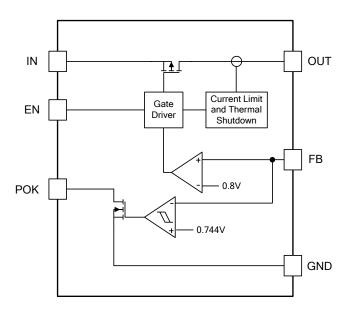

The AP7165 is a 600mA, adjustable output voltage, ultra-low dropout linear regulator. The device includes pass element, error amplifier, band-gap reference, current limit and thermal shutdown circuitry. The device is turned on when EN pin is set to logic high level. A Power-OK (POK) output is available for power sequence control.

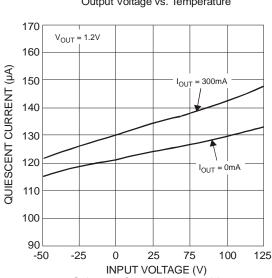

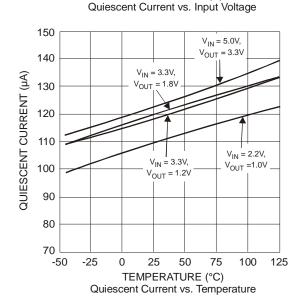

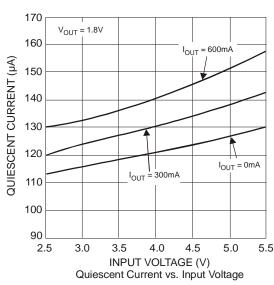

The characteristics of the low dropout voltage and low quiescent current make it suitable for low to medium power applications, for example, laptop computers, audio and video applications, and battery powered devices. The typical quiescent current is approximately 125µA.

Built-in current-limit and thermal-shutdown functions prevent IC from damage in fault conditions. The AP7165 are available in U-DFN3030-10 and SO-8EP packages.

#### **Features**

- Wide input voltage range: 2.2V 5.5V

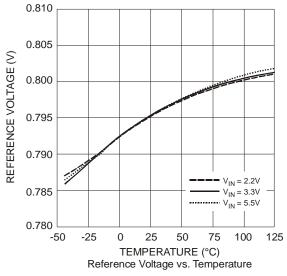

- 300mV very low dropout at 500mA load

- Very low quiescent current (I<sub>Q</sub>): 125µA typical

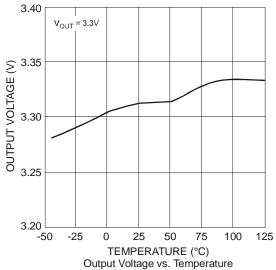

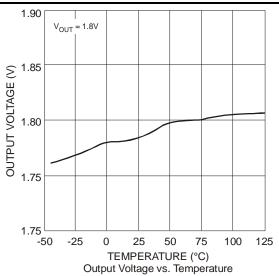

- ± 2.5% total accuracy over line, load and temperature

- Adjustable output voltage range: 0.8V to 5.0V

- Very fast transient response

- High PSRR

- Accurate voltage regulation

- Current limiting and short circuit protection

- Thermal shutdown protection

- Stable with any type output capacitor ≥ 4.7µF

- Ambient temperature range -40°C to +85°C

- U-DFN3030-10 and SO-8EP: Available in "Green"

Molding Compound (No Br, Sb)

- Lead Free Finish/RoHS Compliant (Note 1)

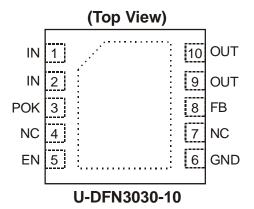

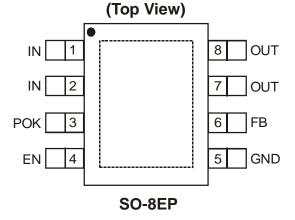

### **Pin Assignments**

## **Applications**

- Servers and laptops

- Smart phone and PDA

- MP3/MP4

- Bluetooth headset

- Low and medium power applications

- FPGA and DSP core or I/O power

Notes: 1. EU Directive 2002/95/EC (RoHS). All applicable RoHS exemptions applied. Please visit our website at http://www.diodes.com/products/lead\_free.html.

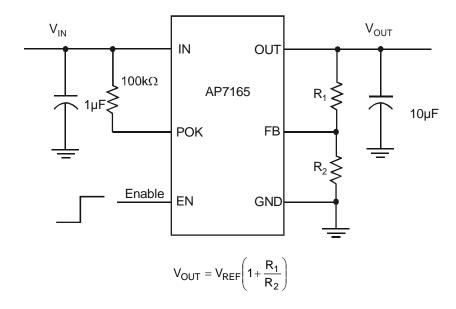

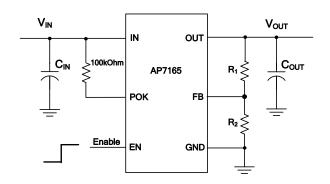

# **Typical Application Circuit**

# **Pin Descriptions**

| N    | Pin #              |      | Description.                                                                                                    |  |

|------|--------------------|------|-----------------------------------------------------------------------------------------------------------------|--|

| Name | U-DFN3030-10 SO-8E |      | Description                                                                                                     |  |

| IN   | 1, 2               | 1, 2 | Voltage input pins, to be tied together externally. Bypass to ground through at least 1µF capacitor.            |  |

| POK  | 3                  | 3    | Power-OK output, active-high open-drain.                                                                        |  |

| EN   | 5                  | 4    | Enable input, active high.                                                                                      |  |

| GND  | 6                  | 5    | Ground.                                                                                                         |  |

| FB   | 8                  | 6    | Output feedback.                                                                                                |  |

| OUT  | 9, 10              | 7, 8 | Voltage output pins, to be tied together externally. Bypass to ground through at least 4.7µF ceramic capacitor. |  |

| NC   | 4, 7               | NA   | No connection.                                                                                                  |  |

## **Functional Block Diagram**

## **Absolute Maximum Ratings**

| Symbol          | Parameter                       |                          | Ratings              | Unit |

|-----------------|---------------------------------|--------------------------|----------------------|------|

| ESD HBM         | Human Body Model ESD Protection |                          | 4                    | KV   |

| ESD MM          | Machine Model ESD Protection    |                          | 300                  | V    |

| V <sub>IN</sub> | Input Voltage                   |                          | 7                    | ٧    |

|                 | OUT, FB, POK, EN Voltage        |                          | V <sub>IN</sub> +0.3 | V    |

|                 | Continuous Load Current         |                          | Internal Limited     |      |

| $T_{Jmax}$      | Maximum Junction Temperature    |                          | 150                  | °C   |

| T <sub>ST</sub> | Storage Temperature Range       |                          | -65 ~ +150           | °C   |

| В               | Dower Dissipation               | U-DFN3030-10 (Note 2, 4) | 3.1                  | W    |

| P <sub>D</sub>  | Power Dissipation               | SO-8EP (Note 2, 5)       | 4.0                  | W    |

Notes: 2. Ratings apply to ambient temperature at 25°C

# **Recommended Operating Conditions**

| Symbol           | Parameter                     | Min | Max | Unit |

|------------------|-------------------------------|-----|-----|------|

| V <sub>IN</sub>  | Input voltage                 | 2.2 | 5.5 | V    |

| I <sub>OUT</sub> | Output Current                | 0   | 600 | mA   |

| T <sub>A</sub>   | Operating Ambient Temperature | -40 | +85 | °C   |

### **Electrical Characteristics**

$(T_A = 25^{\circ}C, V_{IN} = V_{OLIT} + 1V, C_{IN} = 1\mu F, C_{OLIT} = 10\mu F, V_{FN} = V_{IN}, unless otherwise stated)$

| Symbol                                         | Parameter                               | Test Conditions                                                            | Min  | Тур.  | Max  | Unit             |

|------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------|------|-------|------|------------------|

| IQ                                             | Input Quiescent Current                 | I <sub>OUT</sub> = 0                                                       | _    | 125   | 170  | μΑ               |

| I <sub>SHDN</sub>                              | Input Shutdown Current                  | $V_{EN} = 0V$ , $I_{OUT} = 0$ (Note 3)                                     | -1   | 0.01  | +1   | μΑ               |

| $V_{ROPOUT}$                                   | Dropout Voltage                         | $V_{OUT} \ge 1.5V$ , $I_{OUT} = 500$ mA                                    |      | 300   | 400  | mV               |

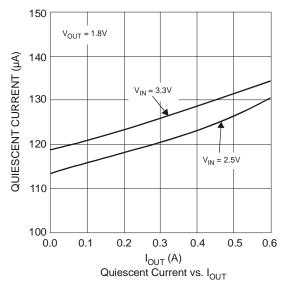

| $V_{REF}$                                      | FB reference voltage                    |                                                                            |      | 0.8   |      | ٧                |

| I <sub>FB</sub>                                | FB leakage                              |                                                                            | _    | 0.01  | 1    | μΑ               |

| V <sub>OUT</sub>                               | Output Voltage Total Accuracy           | Over line, load and temperature                                            | -2.5 |       | +2.5 | %                |

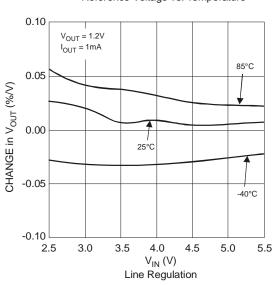

| $\frac{\Delta V_{OUT}}{\Delta V_{IN}}/V_{OUT}$ | Line Regulation                         | $V_{IN} = V_{OUT} + 1V$ to 5.5V,<br>$I_{OUT} = 1$ mA                       |      | 0.015 |      | %/V              |

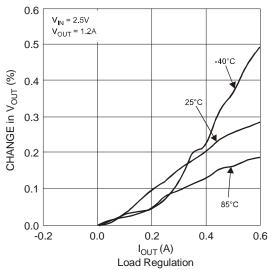

| ΔV <sub>OUT</sub> / V <sub>OUT</sub>           | Load Regulation                         | I <sub>OUT</sub> from 1mA to 500mA                                         | -1.0 |       | +1.0 | %                |

| t <sub>ST</sub>                                | Start-up Time, from EN high to POK high | $V_{EN} = 0V \text{ to } 2.0V,$<br>$I_{OUT} = 100\text{mA}, V_{IN} = 3.3V$ |      | 170   |      | μs               |

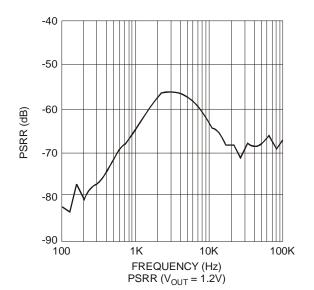

| PSRR                                           | Power Supply Rejection Ratio            | 1kHz, $V_{IN} = 3.3V$ ,<br>$V_{OUT} = 1.2V$ , $I_{OUT} = 0$ mA             |      | 60    |      | dB               |

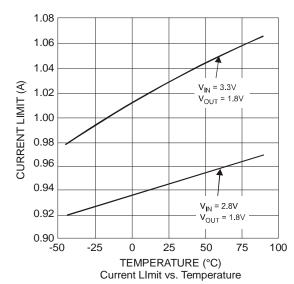

| I <sub>LIMIT</sub>                             | Current limit                           | $V_{OUT} = 1.8V$ , $R_{OUT} = 0.5\Omega$                                   | 600  | 950   |      | mA               |

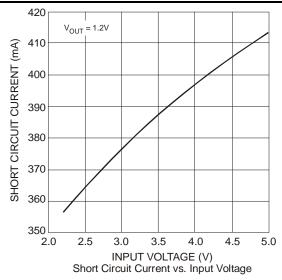

| I <sub>SHORT</sub>                             | Short-circuit Current                   | V <sub>IN</sub> = 3.3V, V <sub>OUT</sub> < 0.2V                            |      | 380   |      | mA               |

| V <sub>IL</sub>                                | EN Input Logic Low Voltage              |                                                                            |      |       | 0.4  | V                |

| V <sub>IH</sub>                                | EN Input Logic High Voltage             |                                                                            | 1.4  |       |      | V                |

| I <sub>EN</sub>                                | EN Input leakage                        | V <sub>EN</sub> = 0V or 5.5V                                               | _    | 0.01  | 1    | μΑ               |

| V <sub>OL</sub>                                | POK output low voltage                  | Force 2mA                                                                  |      | 100   | 200  | mV               |

| V <sub>POK_TH_UP</sub>                         | Output voltage (rising) POK threshold   | FB (or OUT for fixed version) rising                                       | 87%  | 92%   | 97%  | V <sub>ref</sub> |

| V <sub>POK_Hys</sub>                           | Output voltage POK hysteresis           |                                                                            |      | 4%    |      | $V_{ref}$        |

| POK deglitch                                   |                                         | $V_{IN} = 3.3V, V_{OUT} = 1.2V$                                            |      | 150   |      | μs               |

| I <sub>POK_LK</sub>                            | POK leakage current                     | V <sub>POK</sub> = 5.5V                                                    |      | 0.01  | 1    | μA               |

| T <sub>SHDN</sub>                              | Thermal shutdown threshold              |                                                                            |      | 150   |      | °C               |

| T <sub>HYS</sub>                               | Thermal shutdown hysteresis             |                                                                            |      | 25    |      | °C               |

| $	heta_{JA}$                                   | Thermal Resistance Junction-to-         | U-DFN3030-10 (Note 4)                                                      |      | 40    |      | °C/W             |

| - 77                                           | Ambient                                 | SO-8EP (Note 5)                                                            |      | 27    |      | °C/W             |

| $	heta_{\sf JC}$                               | Thermal Resistance                      | U-DFN3030-10 (Note 4)                                                      |      | 9     |      | °C/W             |

| -30                                            | Junction-to- Case                       | SO-8EP (Note 5)                                                            |      | 4     |      | °C/W             |

Notes:

AP7165 4 of 15 March 2012 © Diodes Incorporated Document number: DS31270 Rev. 7 - 2 Downloaded From Oneyac.com

<sup>3.</sup> POK pin must be disconnected from IN pin.

4. Test condition for U-DFN3030-10: Device mounted on FR-4 2-layer board, 2oz copper, with minimum recommended pad on top layer and 6 vias to bottom layer 1.0"x1.5" ground plane.

<sup>5.</sup> Test condition for SO-8EP: Device mounted on 2" x 2" FR-4 substrate PCB, 2oz copper, with minimum recommended pad on top layer and thermal vias to bottom layer ground plane.

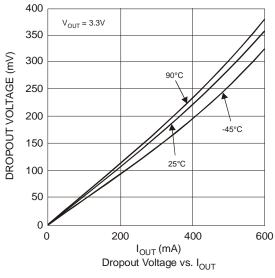

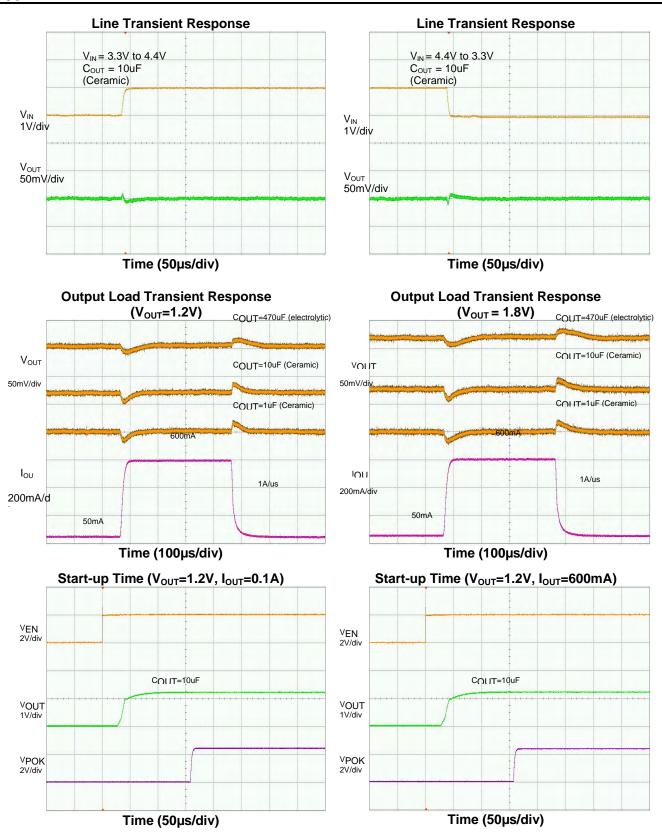

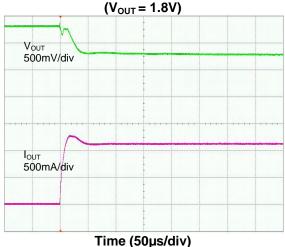

# **Typical Performance Characteristics**

## **Typical Performance Characteristics (cont.)**

## **Typical Performance Characteristics (cont.)**

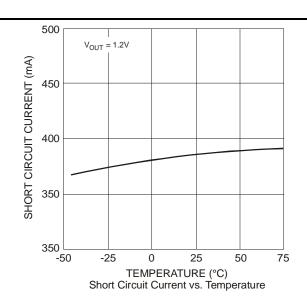

## Typical Performance Characteristics (cont.)

# **Current Limit Protection**

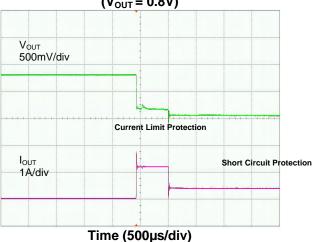

**Current Limit & Short Circuit Protection**  $(V_{OUT} = 0.8V)$

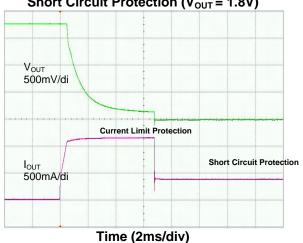

## Short Circuit Protection (Vout = 1.8V)

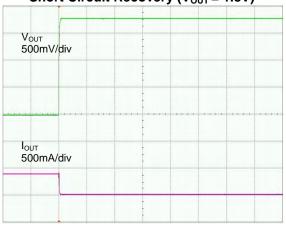

Short Circuit Recovery (Vout = 1.8V)

Time (50µs/div)

### **Application Notes**

#### **Input Capacitor**

A 1 $\mu F$  ceramic capacitor is recommended to connect between IN and GND pins to decouple input power supply glitch and noise. The amount of the capacitance may be increased without limit. A lower ESR (Equivalent Series Resistance) capacitor allows the use of less capacitance, while higher ESR type requires more capacitance. This input capacitor should be located as close as possible to the device to assure input stability and less noise. For PCB layout, a wide copper trace is required for both IN and GND.

#### **Output Capacitor**

The output capacitor is required to stabilize and help the transient response of the LDO. The AP7165 is designed to have excellent transient response for most applications with a small amount of output capacitance. The AP7165 is stable for all available types and values of output capacitors  $\geq 4.7 \mu F.$  The device is also stable with multiple capacitors in parallel, which can be of any type of value. Additional capacitance helps to reduce undershoot and overshoot during transient. This capacitor should be placed as close as possible to OUT and GND pins for optimum performance.

#### **Adjustable Operation**

The AP7165 provides output voltage from 0.8V to 5.0V through external resistor divider as shown below.

The output voltage is calculated by:

$$V_{\text{OUT}} = V_{\text{REF}} \left( 1 + \frac{R_1}{R_2} \right)$$

Where  $V_{REF} = 0.8V$  (the internal reference voltage).

Rearranging the equation will give the following equation to find the approximate resistor divider values:

$$R_1 = R_2 \left( \frac{V_{OUT}}{V_{REF}} - 1 \right)$$

To maintain the stability of the internal reference voltage,  $R_2$  needs to be kept smaller than  $250k\Omega$ .

#### **No Load Stability**

Other than external resistor divider, no minimum load is required to keep the device stable. The device will remain stable and regulated in no load condition.

#### **ENABLE/SHUTDOWN Operation**

The AP7165 is turned on by setting the EN pin high, and is turned off by pulling it low. If this feature is not used, the EN pin should be tied to IN pin to keep the regulator output on at all time. To ensure proper operation, the signal source used to drive the EN pin must be able to swing above and below the specified turn-on/off voltage thresholds listed in the Electrical Characteristics section under  $V_{\rm IL}$  and  $V_{\rm IH}$ .

#### **POWER-OK**

The Power-Ok (POK) pin is an active high open-drain output. It can be connected to any 5.5V or lower rail through an external pull-up resistor. The recommended sink current of POK pin is up to 4mA, so the pull-up resistor for POK should be in the range of  $10k\Omega$  to  $1M\Omega$ . If output voltage monitoring is not needed, the POK pin can be left floating.

#### **Current Limit Protection**

When output current at OUT pin is higher than current limit threshold, the current limit protection will be triggered and clamp the output current to approximately 950mA (600A min) to prevent over-current and to protect the regulator from damage due to overheating.

#### **Short Circuit Protection**

When OUT pin is short-circuited to GND or OUT pin voltage is less than 200mV, short circuit protection will be triggered and clamp the output current to approximately 380mA. This feature protects the regulator from overcurrent and damage due to overheating.

### **Application Notes (cont.)**

#### **Low Quiescent Current**

The AP7165, consuming only around 125µA for all input range and output loading, provides great power saving in portable and low power applications.

### Wide Output Range

The AP7165, with a wide output range of 0.8V to 5.0V. provides a versatile solution for many portable and low power applications.

#### **Thermal Shutdown Protection**

Thermal protection disables the output when the junction temperature rises to approximately +150°C, allowing the device to cool down. When the junction temperature reduces to approximately +125°C the output circuitry is enabled again. Depending on power dissipation, thermal resistance, and ambient temperature, the thermal protection circuit may cycle on and off. This cycling limits the heat dissipation of the regulator, protecting it from damage due to overheating.

#### **Power Dissipation**

The device power dissipation and proper sizing of the thermal plane that is connected to the thermal pad is critical to avoid thermal shutdown and ensuring reliable operation. Power dissipation of the device depends on input voltage and load conditions and can be calculated bv:

$$P_D = (V_{IN} - V_{OUT})xI_{OUT}$$

The AP7165 is available in the U-DFN3030-10 and SO-8EP packages, both with exposed pad, which is the primary conduction path for heat to the printed circuit board (PCB). The pad can be connected to ground or be left floating; however, to ensure the device will not overheat, it should be attached to an appropriate amount of copper PCB area.

However, the maximum power dissipation that can be handled by the device depends on the maximum junction to ambient thermal resistance, maximum ambient temperature, and maximum device junction temperature, which can be approximated by the equation below:

$$P_{D}(max@T_{A}) = \frac{(+145^{\circ}C - T_{A})}{R_{\theta JA}}$$

10 of 15 AP7165 March 2012 © Diodes Incorporated Document number: DS31252 Rev. 7 - 2

-13

### 600mA LOW DROPOUT REGULATOR WITH POK

2500/Tape & Reel

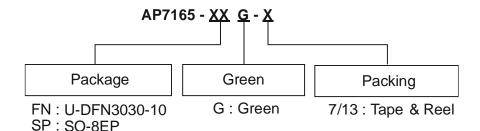

### **Ordering Information**

|          |              | Deckers Pooksging |                       | Tube     |                       | 7"/13" Tape and Reel |                    |

|----------|--------------|-------------------|-----------------------|----------|-----------------------|----------------------|--------------------|

|          | Device       | Package<br>Code   | Packaging<br>(Note 2) | Quantity | Part Number<br>Suffix | Quantity             | Part Number Suffix |

| <b>,</b> | AP7165-FNG-7 | FN                | U-DFN3030-10          | NA       | NA                    | 3000/Tape & Reel     | -7                 |

NA 6. Pad layout as shown on Diodes Inc. suggested pad layout document AP02001, which can be found on our website at http://www.diodes.com/datasheets/ap02001.pdf.

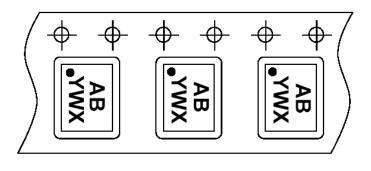

## **Marking Information**

### (1) U-DFN3030-10

AP7165-SPG-13

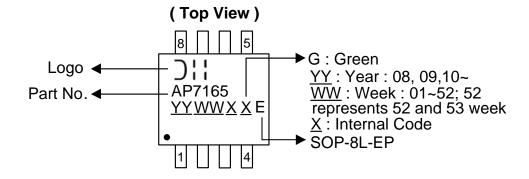

## (Top View)

SO-8EP

XXYWX XX: Identification Code

Y: Year: 0~9

<u>W</u>: Week: A~Z: 1~26 week;

NA

a~z: 27~52 week; z represents

52 and 53 week X: A~Z: Green

| Part Number | Package      | Identification Code |

|-------------|--------------|---------------------|

| AP7165      | U-DFN3030-10 | B2                  |

### (2) SO-8EP

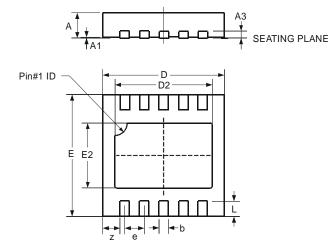

## **Package Outline Dimensions**

### (1) Package Type: U-DFN3030-10

| J                    | U-DFN3030-10 |      |       |  |  |  |  |

|----------------------|--------------|------|-------|--|--|--|--|

| Dim                  | Min          | Max  | Тур   |  |  |  |  |

| Α                    | 0.57         | 0.63 | 0.60  |  |  |  |  |

| A1                   | 0            | 0.05 | 0.02  |  |  |  |  |

| А3                   | _            | _    | 0.15  |  |  |  |  |

| b                    | 0.20         | 0.30 | 0.25  |  |  |  |  |

| D                    | 2.90         | 3.10 | 3.00  |  |  |  |  |

| D2                   | 2.30         | 2.50 | 2.40  |  |  |  |  |

| е                    | _            | _    | 0.50  |  |  |  |  |

| Е                    | 2.90         | 3.10 | 3.00  |  |  |  |  |

| E2                   | 1.50         | 1.70 | 1.60  |  |  |  |  |

| L                    | 0.25         | 0.55 | 0.40  |  |  |  |  |

| z                    |              |      | 0.375 |  |  |  |  |

| All Dimensions in mm |              |      |       |  |  |  |  |

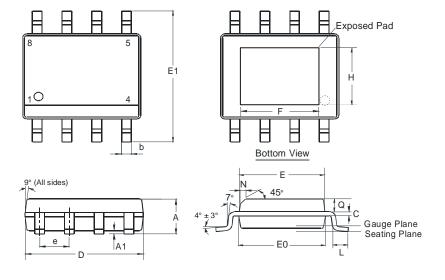

## (2) Package Type: SO-8EP

| SO-8EP (SOP-8L-EP)   |      |      |      |  |

|----------------------|------|------|------|--|

| Dim                  | Min  | Max  | Тур  |  |

| Α                    | 1.40 | 1.50 | 1.45 |  |

| <b>A1</b>            | 0.00 | 0.13 | 1    |  |

| þ                    | 0.30 | 0.50 | 0.40 |  |

| С                    | 0.15 | 0.25 | 0.20 |  |

| D                    | 4.85 | 4.95 | 4.90 |  |

| E                    | 3.80 | 3.90 | 3.85 |  |

| E0                   | 3.85 | 3.95 | 3.90 |  |

| E1                   | 5.90 | 6.10 | 6.00 |  |

| е                    | -    | -    | 1.27 |  |

| F                    | 2.75 | 3.35 | 3.05 |  |

| I                    | 2.11 | 2.71 | 2.41 |  |

| L                    | 0.62 | 0.82 | 0.72 |  |

| N                    | -    | -    | 0.35 |  |

| Ø                    | 0.60 | 0.70 | 0.65 |  |

| All Dimensions in mm |      |      |      |  |

Notes:

7. All dimensions are in millimeters. Angles are in degrees. 8. Coplanarity applies to the exposed heat sink slug as well as the terminals.

# **Suggested Pad Layout**

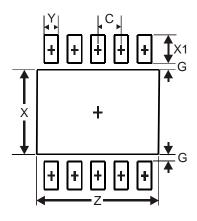

## (1) Package Type: U-DFN3030-10

| <b>Dimensions</b> | Value (in mm) |

|-------------------|---------------|

| Z                 | 2.60          |

| G                 | 0.15          |

| Х                 | 1.80          |

| X1                | 0.60          |

| Y                 | 0.30          |

| С                 | 0.50          |

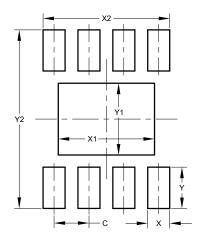

## (2) Package Type: SO-8EP

| Dimensions | Value<br>(in mm) |

|------------|------------------|

| С          | 1.270            |

| Х          | 0.802            |

| X1         | 3.502            |

| X2         | 4.612            |

| Υ          | 1.505            |

| Y1         | 2.613            |

| Y2         | 6.500            |

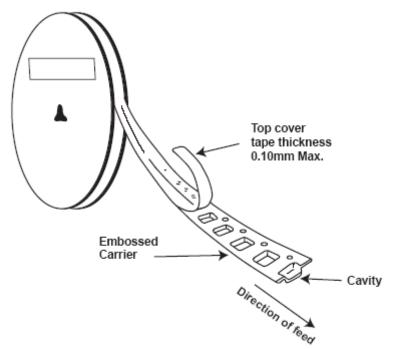

# **Taping Orientation (Note 9)**

### For U-DFN3030-10

Notes: 9.The taping orientation of the other package type can be found on our website at http://www.diodes.com/datasheets/ap02007.pdf.

14 of 15

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2012, Diodes Incorporated

www.diodes.com

15 of 15 AP7165 March 2012 © Diodes Incorporated Document number: DS31252 Rev. 7 - 2

# 单击下面可查看定价,库存,交付和生命周期等信息

>>Diodes Incorporated(达迩科技(美台))