### **DESCRIPTION OF PIN FUNCTIONS**

| V <sub>DD</sub> | Positive supply connection (5 volts). Both pins to be connected. To be decoupled with a 100nF capacitor to $V_{\mbox{SS}}.$ |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------|

| V <sub>SS</sub> | Negative supply connection; system ground (0 volts). Both pins to be connected.                                             |

| BG              | Bias Generator output. To be decoupled with a 100nF capacitor to $V_{SS}.$                                                  |

| BI              | Bias inputs for internal circuitry, both to be connected to BG. (or external supply referenced to $V_{SS}$ )                |

| PD              | Active low. This feature can be used to reduce power consumption for applications that have a standby mode.                 |

| FI1,FI2         | Filter input, FI1 or FI2 depending on filter configuration.                                                                 |

| FO              | Filter output for all configurations.                                                                                       |

| LO              | Local Oscillator signal input.                                                                                              |

| MXI             | Mixer signal input.                                                                                                         |

| MXO             | Mixer signal output.                                                                                                        |

| C1, RC1         | Phase advance network nodes. Values R and C set centre frequency, fo.                                                       |

| R2, RC2         | Phase retard network nodes. Values R and C set centre frequency, fo.                                                        |

| GP1,2,3         | Loop gain programming nodes.                                                                                                |

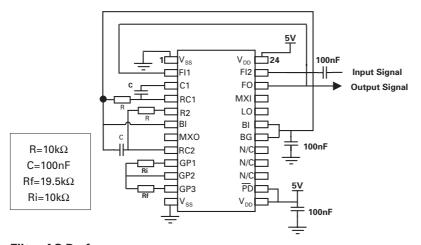

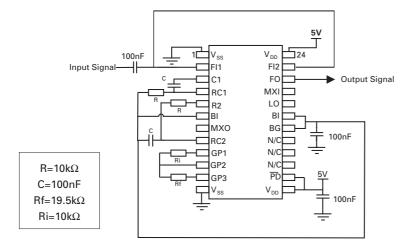

#### **CONNECTION DIAGRAM**

| 1 | V <sub>ss</sub> |      |  |

|---|-----------------|------|--|

|   | FI1             | FI2  |  |

|   | C1              | FO   |  |

|   | RC1             | мхі  |  |

|   | R2              | LO   |  |

|   | BI              | ві 🗖 |  |

|   | MXO             | BG   |  |

|   | RC2             | N/C  |  |

|   | GP1             | N/C  |  |

|   | GP2             | N/C  |  |

|   | GP3             | PD   |  |

|   | V <sub>ss</sub> |      |  |

ISSUE 3 - JANUARY 2002

#### FILTER CONFIGURATIONS AND RESPONSES

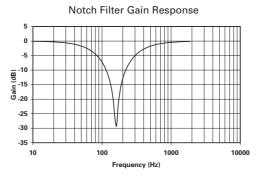

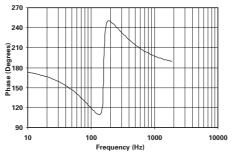

### **Notch Filter**

### Filter AC Performance

| £  | 1                     |  |

|----|-----------------------|--|

| f₀ | $= 2\pi RC$           |  |

| Q  | $\propto (R_f / R_i)$ |  |

Where R, Ri and Rf  $\geq$ 10k $\Omega$  and C  $\geq$  50 pF

See "Designing for a Value of  $\ensuremath{\mathsf{Q}}$  " for more details.

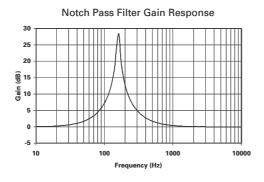

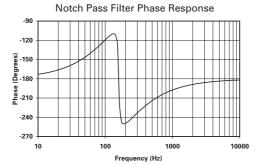

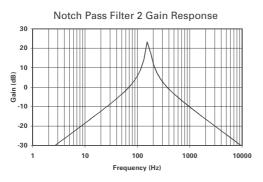

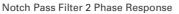

Typical responses for the circuit with component values shown in circuit diagram.

ISSUE 3 - JANUARY 2002

### FILTER CONFIGURATIONS AND RESPONSES (continued)

## Filter AC Performance

| $f_{\alpha} =$ |           |

|----------------|-----------|

| <i>Io</i> =    | 2πRC      |

| <i>Q</i> ~     | (Rf / Ri) |

Where R, Ri and Rf  ${\geq}10k\Omega$  and C  ${\geq}$  50 pF

See "Designing for a Value of  $\ensuremath{\mathsf{Q}}$  " for more details.

Typical responses for the circuit with component values shown in circuit diagram.

ISSUE 3 - JANUARY 2002

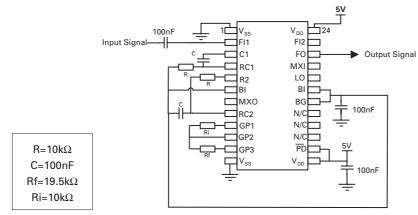

#### FILTER CONFIGURATIONS AND RESPONSES (continued)

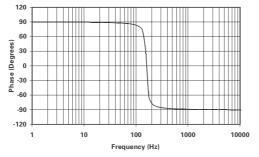

### Notch Filter (with attenuating skirts)

### Filter AC Performance

$$f_o = \frac{1}{2\pi RC}$$

$$Q \propto (R_f / R_i)$$

Where R, Ri and Rf  $\geq$  10k $\Omega$  and C  $\geq$  50 pF

See "Designing for a Value of  $\ensuremath{\mathsf{Q}}$  " for more details.

The skirt 'roll off' away from the peak is -20dB/decade regardless of chosen Q.

Typical responses for the circuit with component values shown in circuit diagram.

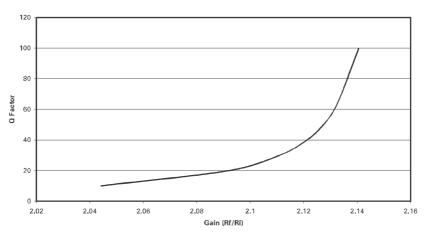

#### DESIGNING FOR A VALUE OF Q

As mentioned on the configuration pages, there is a proportional, but non-linear relationship between the ratio of Rf and Ri, and  $\Omega$ .

These resistors define the gain of an inverting amplifier that determines the peak value gain and therefore the Q of the filter,Q is defined as:

$$Q = \frac{t_o}{-3dB \ Bandwidth}$$

This value of required gain is critical. As the maximum value of Q is approached, too much gain will cause the filter to oscillate at the centre frequency, fo. A small reduction of gain will cause the value of Q to fall significantly. Therefore, for high values of Q or tight tolerances of lower values of Q, the resistor ratio must be trimmed as shown.

Frequency dependant effects must be accounted for in determining the appropriate gain. As the frequency increases because of internal phase shift effects the effective circuit gain reduces and thus QFactor reduces.

The frequency effect is not a problem for circuits where the for remains constant, as the phase shifts are accounted for permanently. For designs where  $\Omega$  is high and fo is to be 'swept', care must be taken that a gain appropriate at the highest frequency does not cause oscillation at the lowest.

Ballowestepsdorregtypisettvagluesoropograint vaquased for several example conditions:

#### Example1

Example2

$\begin{array}{ll} fo = 140 kHz, & R = 10 k\Omega, \ C = 100 pF \\ Q = 15, & Rf/Ri = 37 k\Omega \ / \ 18 k\Omega => 2.055 \end{array}$

It can be seen from these examples that the higher Q example actually has a lower inverting amplifier gain. As mentioned before, the frequency will affect the value of gain. The Q Factor v Frequency graph illustrates this effect.

These examples show that the gain required is nominally 2. For the specified range of  $\Omega$ : 0.5 to 50 (values up to 250 are obtainable), the gain values vary from 1.9 to 2.5 correspondingly.

Due to internal gain errors, when the absolute value of  $\Omega$  is increased, the device to device variation in  $\Omega$  will also increase.

Q Factor V Feedback Gain

This diagram shows the exponential relationship between gain and Q Factor. (fo = 140 kHz)

# FILTERING HIGHER FREQUENCIES USING THE MIXER

Frequencies above 150 kHz cannot be filtered directly; the mixer enables the notch pass filter to function up to 700kHz.

The signal to be filtered is mixed with another frequency (local oscillator), chosen so that the difference (intermediate) frequency equals the filter's centre frequency, fo. The local oscillator signal waveform can be of any shape (sine, square, etc.) but must be approximately 50% duty cycle.

#### Example

Input frequency = 300 kHz, Local Oscillator (LO) frequency = 250 kHz,

Output (IF) Frequency = 50 kHz.

If the bandwidth of the 50 kHz filter were 1 kHz, the filter's Q factor would be:

50/1 = 50.

The bandwidth of the filter is still 1 kHz when 300 kHz is applied to the mixer's input, but now the Q factor is:

300/1 = 300.

ISSUE 3 - JANUARY 2002

The mixer provides a Q factor improvement equal to the ratio of the input frequency and the intermediate frequency.

The effective centre frequency can also be externally controlled by changing the LO frequency. This allows frequency tuning, trimming or sweeping while employing fixed resistors and capacitors for the filter.

As the LO signal can be a square wave, this allows 'fo' to be controlled using a microcontroller or microprocessor.

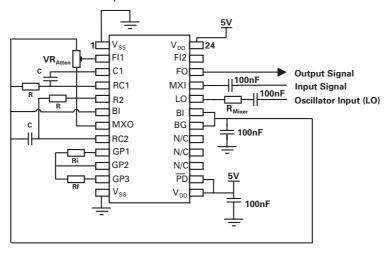

# MIXER CONFIGURATION WITH NOTCH PASS FILTER (with attenuating skirts)

The mixer can only be used with this filter configuration, as the other types have 0dB stop bands. The mixer output 'MXO' becomes the input of the filter.

As the gain of the notch filter changes with Q, the output of the mixer must be attenuated by some factor (VR<sub>Atten</sub>). This will prevent the filter from being overdriven and allows the user to set the required output level.

**Note:** As the local oscillator input, LO has a low input impedance (60  $\Omega$ ), it will often be necessary to increase it for driving circuitry. As the input voltage required is low (around 5 mV pk-pk min.), a series resistor 'R<sub>Mixer</sub>' can be inserted. A value of 1 k $\Omega$  per 100mV (pk) oscillator signal input will be suitable.

#### **Application Note**

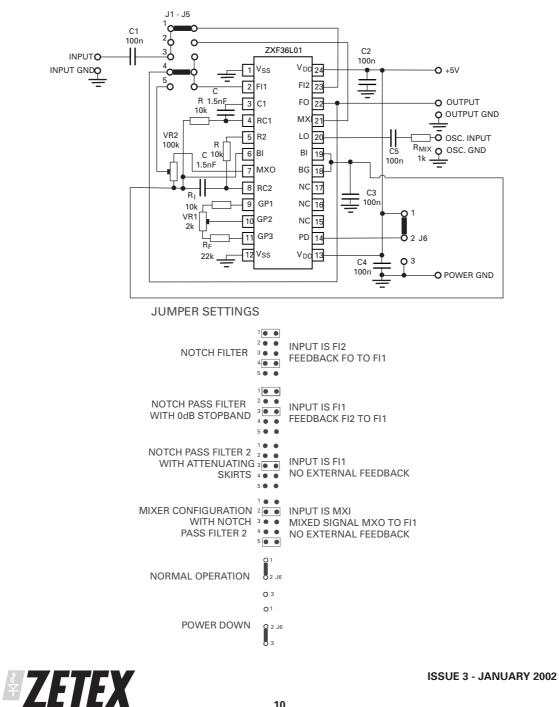

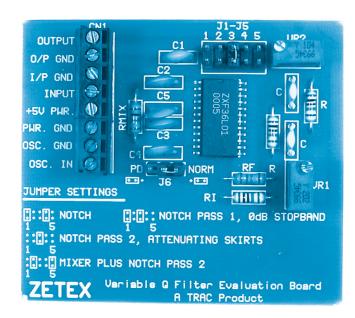

An assembled evaluation PCB is available from Zetex Plc, part code: ZXF36L01-EVB. It provides a fast and easy way of testing the filter configurations mentioned in this datasheet. This board is configured for 10kHz operation.

## **Evaluation**

An evaluation board (ZXF36L01-EVB) is available to assist with in-system or stand-alone performance evaluation. The board can be set, by simple jumper links, to perform any of the filter characteristic responses. The mixer can be selected in conjunction with the notch pass filter 2 functions.

Evaluation boards can be purchased from our catalogue distributors.

Digi-Key North America (www.digikey.com) Tel:1-800344-4539

Europe - Farnell (www.farnell.com) Tel:44-113-263-6311

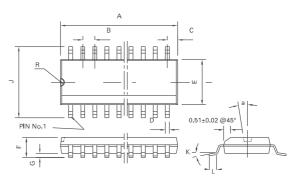

| PACKAGE DIMENSION |             |       |        |       |

|-------------------|-------------|-------|--------|-------|

| DIM               | Millimetres |       | Inches |       |

|                   | Min         | Max   | Min    | Max   |

| А                 | 15.20       | 15.40 | 0.598  | 0.606 |

| В                 | 1.27        | -     | 0.05   | -     |

| С                 | 0.66        | -     | 0.026  | -     |

| D                 | 0.36        | 0.46  | 0.014  | 0.018 |

| E                 | 7.40        | 7.60  | 0.291  | 0.299 |

| F                 | 2.44        | 2.64  | 0.096  | 0.104 |

| G                 | 0.10        | 0.30  | 0.004  | 0.012 |

| Н                 | 0°          | 7°    | 0°     | 7°    |

| I                 | 0.23        | 0.28  | 0.009  | 0.011 |

| J                 | 10.11       | 10.51 | 0.398  | 0.414 |

| К                 | 0°          | 8°    | 0°     | 8°    |

| L                 | 0.51        | 1.01  | 0.02   | 0.04  |

| R                 | 0.63        | 0.89  | 0.025  | 0.035 |

| а                 | 7°BSC       |       | 7°BSC  |       |

#### **PACKAGE OUTLINE**

SOIC 24 LEAD

#### © Zetex plc 2001

| Zetex plc                   | Zetex GmbH                  | Zetex Inc                 | Zetex (Asia) Ltd            |

|-----------------------------|-----------------------------|---------------------------|-----------------------------|

| Fields New Road             | Streitfeldstraße 19         | 700 Veterans Memorial Hwy | 3701-04 Metroplaza, Tower 1 |

| Chadderton                  | D-81673 München             | Hauppauge, NY11788        | Hing Fong Road              |

| Oldham, OL9 8NP             |                             |                           | Kwai Fong                   |

| United Kingdom              | Germany                     | USA                       | Hong Kong                   |

| Telephone (44) 161 622 4422 | Telefon: (49) 89 45 49 49 0 | Telephone: (631) 360 2222 | Telephone: (852) 26100 611  |

| Fax: (44) 161 622 4420      | Fax: (49) 89 45 49 49 49    | Fax: (631) 360 8222       | Fax: (852) 24250 494        |

These offices are supported by agents and distributors in major countries world-wide.

This publication is issued to provide outline information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose or form part of any order or contract or be regarded as a representation relating to the products or services concerned. The Company reserves the right to alter without notice the specification, design, price or conditions of supply of any product or service.

For the latest product information, log on to www.zetex.com

单击下面可查看定价,库存,交付和生命周期等信息

>>Diodes Incorporated(达迩科技(美台))