# DisplayPort 1.4 HBR3 Linear Redriver with Latency-Free, DP Transparent Link Training support

### Description

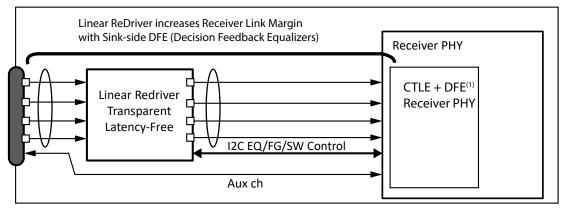

PI3DPX1203B is the DisplayPort 1.4 compliant, up to 4 channel, 8.1 Gbps HBR3 Linear Redriver with Link Training transparency support. Displayport source-side and sink-side devices communicate through the AUX transaction between the source and the sink-side devices.

Input Equalization, Voltage Swing and Flat Gain control can be configured with pin-strapping or I2C programing to optimized Main Link high speed signals over a variety of physical medium by reducing inter-symbol interference. Pericom's Linear Redriver technology can deliver 2 times better additive jitters performance than traditional Redrivers.

Linear Equalizer always provide very flexible component placement, cascade connection and easy adjustment after the Redriver location changes during the product development events.

#### Features

- ➔ Compliant with VESA DisplayPort 1.4 specification up to 8.1 Gbps Link Rate

- → Latency-free for the variable video frame rate support

- → Dual mode DisplayPort support

- ➔ Linear Redriver allows flexible placement with DP Main Link boost setting

- ➔ Ideal for DP Alt Type-C Source and Sink-side application with PD Controllers with Aux Link Training Transparent Mode support

- → Linear Equalizer increases Link Margin with Sink-side DFE (Decision Feedback Equalizer)

- ➔ Independent Main Link channel configuration for 4-bit Equalization, 2-bit Voltage Output swing and 2-bit Flat Gain control

- ➔ Pin strap or I2C programmable for device configuration setting

- → Intra- and Inter-Channel Polarity Swap support

- → I2C Address selectable for configuration register access

- → Low Stand-by power consumption

- → Power supply voltage: 3.3V

- → Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- → Halogen and Antimony Free. "Green" Device (Note 3)

# Applications

- → Notebook, Desktop, AIO PC

- ➔ Display Monitors

- ➔ Active Adaptors, Dongles, Docking

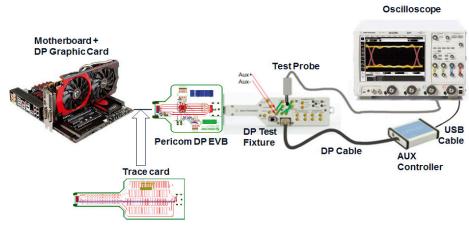

Figure 1-1 DP1.4 HBR3 Redriver in the NB PC

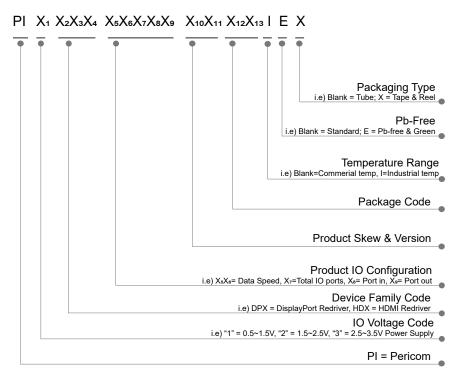

# **Ordering Information**

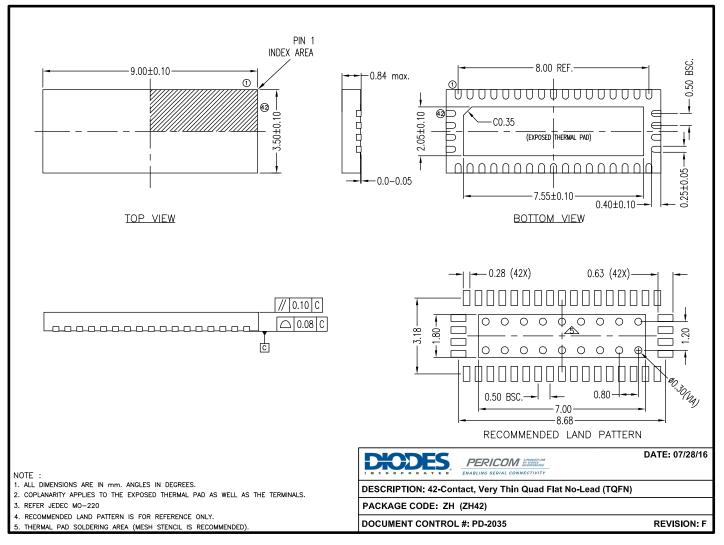

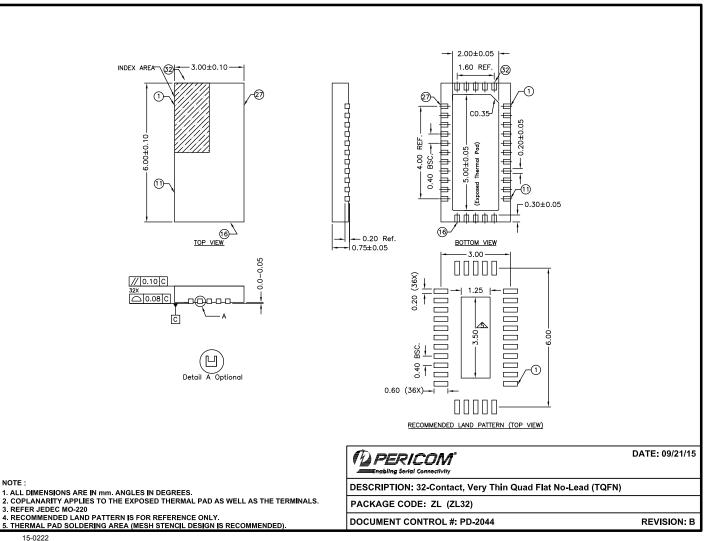

| Ordering Number  | Package<br>Code | Package Description                                                                |

|------------------|-----------------|------------------------------------------------------------------------------------|

| PI3DPX1203BZLEX  | ZL              | 32-pin, Very Thin Quad Flat<br>No-Lead (TQFN) (3X6mm)                              |

| PI3DPX1203BZHEX  | ZH              | 42-pin, Very Thin Quad Flat<br>No-Lead (TQFN) (3.5x9mm)                            |

| PI3DPX1203BZHIEX | ZH              | Industrial Temperature, 42-pin,<br>Very Thin Quad Flat No-Lead<br>(TQFN) (3.5x9mm) |

Notes:

1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

4. E = Pb-free and Green

5. X suffix = Tape/Reel

# 2. General Information

# 2.1 Revision History

| Revision  | Description of Changes                                                                                                                                                                                                        |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oct 2016  | Ch2. 32-pin TQFN package added. Improve EQ , Stand-by power consumption from PI3DPX1203 DP1.4 Linear Redriver. Support I2C slave programming mode.                                                                            |

| Feb 2017  | Ch5. DP1.4 CTS compliance test report added                                                                                                                                                                                   |

| Mar 2017  | Ch2. ZH42 pin-out typo fixed. Pin6, 12, 30 changed to NC.<br>Ch4. No index Byte support<br>Ch5. Gp, GF-gain, V1dB_4G typical value updated                                                                                    |

| May 2017  | Ch5. power consumption; IDDQ = typ 0.2uA, max 1mA; IDD = typ 243mA, max =290mA.<br>Ch5. Power-up timing diagram, PRSNT# application schematics added                                                                          |

| Jun 2017  | In 42-pin package, clarified NC and DNC pins                                                                                                                                                                                  |

| Jul 2017  | Application reference schematic updated to support HPD IRQ                                                                                                                                                                    |

| Dec 2017  | Package marking added (p42).                                                                                                                                                                                                  |

| Jul 2018  | Ordering Information<br>Deleted Section 2.3 Related Products<br>Features<br>Section 4.4 Output -14dB Compressing Setting<br>Section 4.5 EQ Setting<br>Section 6.4 AX/DC Characteristics<br>Figure 6-6 Peaking Gain Definition |

| Sept 2019 | Part Marking                                                                                                                                                                                                                  |

# 2.2 Similar Products Comparison

|                 | PI3DPX1203B                                                                                        | PI3DPX1203                  |

|-----------------|----------------------------------------------------------------------------------------------------|-----------------------------|

| Key Features    | New silicon. Improved IDDQ = 0.2mA and IDD<br>together.<br>Optimized setting for the DP 1.4 speed. | Old version. IDDQ = 2mA typ |

| Package Pin-out | Drop in compatible with PI3DPX1203 version                                                         |                             |

# Contents

| 1. | Pro | oduct Summary                            | . 1 |

|----|-----|------------------------------------------|-----|

| 2. | Gei | neral Information                        | . 2 |

|    | 2.1 | Revision History                         | . 2 |

|    |     | Similar Products Comparison              |     |

| 3. | Pin | Configuration                            | . 4 |

|    | 3.1 | Package Pin-out (Top View)               | . 4 |

|    | 3.2 | Pin Description                          | . 5 |

| 4. | Fur | nctional Description                     | . 8 |

|    |     | Functional Block Diagram                 |     |

|    | 4.2 | Power-Down Mode                          | . 9 |

|    |     | Flat Gain Setting                        |     |

|    | 4.4 | Output -1 dB Compression Setting         | 10  |

|    | 4.5 | EQ Setting                               | 10  |

| 5. | I2C | C Programming                            | 12  |

|    | 5.1 | I2C Registers                            | 12  |

|    | 5.2 | I2C Operation                            | 15  |

| 6. | Ele | ctrical Specification                    | 17  |

|    | 6.1 | Absolute Maximum Ratings                 | 17  |

|    | 6.2 | Recommended Operating Conditions         | 17  |

|    |     | Power Consumption                        |     |

|    | 6.4 | AC/DC Characteristics                    | 18  |

| 7. |     | plications                               |     |

|    |     | Reference Schematic                      |     |

|    | 7.2 | Reference Schematic for HPD_IRQ MST Mode | 25  |

|    | 7.3 | Sink-side Application                    | 27  |

|    |     | Output Swing and Gain Information        |     |

|    | 7.5 | Output Eye diagram, Trace length and EQ  | 29  |

|    | 7.6 | General Power and Ground Guideline       | 30  |

|    | 7.7 | High-speed signal Routing                | 31  |

|    | 7.8 | CTS Compliant Test Report                | 36  |

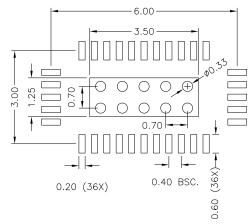

| 8. |     | chanical/Packaging Information           |     |

|    | 8.1 | Mechanical Outline                       | 39  |

|    | 8.2 | Part Marking Information                 | 41  |

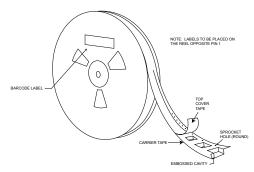

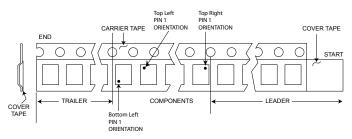

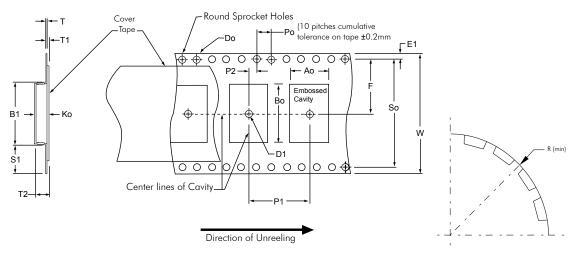

|    | 8.3 | Tape & Reel Materials and Design         | 42  |

| 9. | Imj | portant Notice                           | 45  |

# 3. Pin Configuration

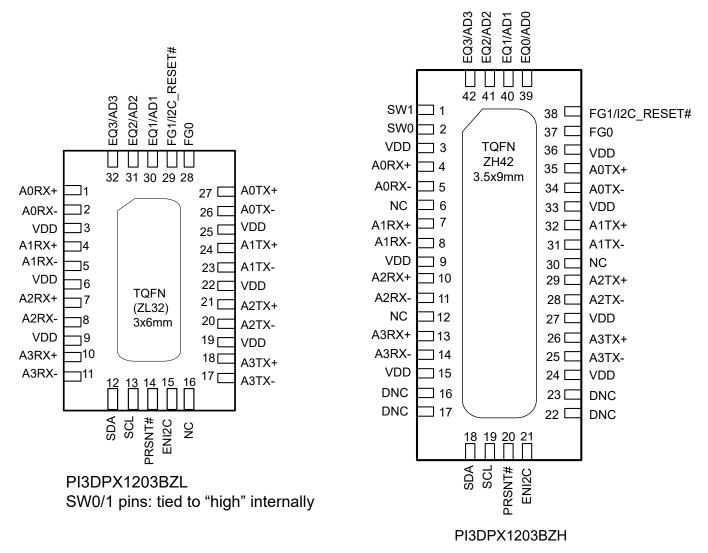

#### 3.1 Package Pin-out (Top View)

Figure 3-1 32/42-pin package pin-out

Note: The polarity (+/-) of each high speed pairs can use interchangeably. Output pins of polarity and data channel will always follow the input polarity and data channel assignment changes.

### 3.2 Pin Description

#### 32-pin package

| Pin #                  | Pin Name            | Туре | Description                                                                                                                                                                                                                                                                                 |  |  |

|------------------------|---------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Data Signals           |                     |      |                                                                                                                                                                                                                                                                                             |  |  |

| 1<br>2                 | A0RX+<br>A0RX-      | Ι    | CML differential positive/negative input for Channel A0, with internal 50 $\Omega$ Pull-Up and ~200k $\Omega$ Pull-Up otherwise.                                                                                                                                                            |  |  |

| 27<br>26               | A0TX+,<br>A0TX-     | 0    | CML differential positive/negative outputs for Channel A0, with internal 50 $\Omega$ Pull-Up and ~2k $\Omega$ Pull-Up otherwise.                                                                                                                                                            |  |  |

| 4 5                    | A1RX+,<br>A1RX-     | Ι    | CML differential positive/negative inputs for Channel A1, with internal 50 $\Omega$ Pull-Up and ~200k $\Omega$ Pull-Up otherwise.                                                                                                                                                           |  |  |

| 24<br>23               | A1TX+,<br>A1TX-     | 0    | CML differential positive/negative outputs for Channel A1, with internal 50 $\Omega$ Pull-Up and ~2k $\Omega$ Pull-Up otherwise.                                                                                                                                                            |  |  |

| 7<br>8                 | A2RX+,<br>A2RX-     | Ι    | CML differential positive/negative inputs for Channel A2, with internal 50 $\Omega$ Pull-Up and ~200k $\Omega$ Pull-Up otherwise.                                                                                                                                                           |  |  |

| 21<br>20               | A2TX+,<br>A2TX-     | 0    | CML differential positive/negative outputs for Channel A2, with internal 50 $\Omega$ Pull-Up and ~2k $\Omega$ Pull-Up otherwise.                                                                                                                                                            |  |  |

| 10<br>11               | A3RX+,<br>A3RX-     | I    | CML differential positive/negative inputs for Channel A3, with internal 50 $\Omega$ Pull-Up and ~200k $\Omega$ Pull-Up otherwise.                                                                                                                                                           |  |  |

| 18<br>17               | A3TX+,<br>A3TX-     | 0    | CML differential positive/negative outputs for Channel A3, with internal 50 $\Omega$ Pull-Up and ~2k $\Omega$ Pull-Up otherwise.                                                                                                                                                            |  |  |

| <b>Control Signals</b> | -                   |      |                                                                                                                                                                                                                                                                                             |  |  |

| 12                     | SDA                 | I/O  | I <sup>2</sup> C Serial Data line                                                                                                                                                                                                                                                           |  |  |

| 13                     | SCL                 | I/O  | I <sup>2</sup> C Serial Clock line                                                                                                                                                                                                                                                          |  |  |

|                        |                     |      | Cable Present Detect input. This pin has internal 100K $\Omega$ pull-up.                                                                                                                                                                                                                    |  |  |

| 14                     | PRSNT#              | Ι    | When High, a cable is not present, and the device is put in lower power mode.                                                                                                                                                                                                               |  |  |

|                        |                     |      | When Low, the device is enabled and in normal operation.                                                                                                                                                                                                                                    |  |  |

| 15                     | ENI2C               | Ι    | I2C Enable pin.<br>Tied to VDD = Register access I2C Slave mode<br>Tied to GND = Pin mode                                                                                                                                                                                                   |  |  |

| 32,31,30               | EQ[3:1]             | Ι    | EQ Control pin. Inputs with internal $100k\Omega$ pull-up.<br>This pins set the amount of Equalizer Boost in all channels when ENI2C is low.                                                                                                                                                |  |  |

|                        | AD[3:1]             | Ι    | Address bits control pins for I2C programming with internal 100k $\Omega$ pull-up.                                                                                                                                                                                                          |  |  |

| 29                     | FG1/I2C_RE-<br>SET# | Ι    | <ul> <li>Shared pin for Gain Control bit-1 and I2C Reset pin. Inputs with internal 100kΩ pull up resistor.</li> <li>(1) Sets the output flat gain level bit-1 on all channels when ENI2C is Low.</li> <li>(2) I2C Reset pin. Active Low to reset the registers to default state.</li> </ul> |  |  |

| 28                     | FG0                 | Ι    | Flat Gain control bit-0 pin. Inputs with internal $100k\Omega$ pull up resistor.<br>Sets the output flat gain level on all channels when ENI2C is low.                                                                                                                                      |  |  |

| 16                     | NC                  | NC   | Not connect                                                                                                                                                                                                                                                                                 |  |  |

| Power Pins             |                     |      |                                                                                                                                                                                                                                                                                             |  |  |

| 3,6,9,19,22,25         | VDD                 | PWR  | 3.3V Power supply pins                                                                                                                                                                                                                                                                      |  |  |

| Center Pad             | GND                 | GND  | D Exposed Ground pad.                                                                                                                                                                                                                                                                       |  |  |

#### 42-pin package

| Pin #        | Pin Name            | Туре | Description                                                                                                                                                                                                                                                                                     |  |

|--------------|---------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Data Signals |                     |      |                                                                                                                                                                                                                                                                                                 |  |

| 4<br>5       | A0RX+<br>A0RX-      | I    | CML differential positive/negative input for Channel A0, with internal 50 $\Omega$ Pull-Up and ~200k $\Omega$ Pull-Up otherwise.                                                                                                                                                                |  |

| 35<br>34     | A0TX+,<br>A0TX-     | 0    | CML differential positive/negative outputs for Channel A0, with internal 50 $\Omega$ Pull-Up and ~2k $\Omega$ Pull-Up otherwise.                                                                                                                                                                |  |

| 7<br>8       | A1RX+,<br>A1RX-     | Ι    | CML differential positive/negative inputs for Channel A1, with internal 50 $\Omega$ Pull-Up and ~200k $\Omega$ Pull-Up otherwise.                                                                                                                                                               |  |

| 32<br>31     | A1TX+,<br>A1TX-     | 0    | CML differential positive/negative outputs for Channel A1, with internal 50 $\Omega$ Pull-Up and ~2k $\Omega$ Pull-Up otherwise.                                                                                                                                                                |  |

| 10<br>11     | A2RX+,<br>A2RX-     | Ι    | CML differential positive/negative inputs for Channel A2, with internal 50 $\Omega$ Pull-Up and ~200k $\Omega$ Pull-Up otherwise.                                                                                                                                                               |  |

| 29<br>28     | A2TX+,<br>A2TX-     | 0    | CML differential positive/negative outputs for Channel A2, with internal 50 $\Omega$ Pull-Up and ~2k $\Omega$ Pull-Up otherwise.                                                                                                                                                                |  |

| 13<br>14     | A3RX+,<br>A3RX-     | Ι    | CML differential positive/negative inputs for Channel A3, with internal 50 $\Omega$ Pull-Up and ~200k $\Omega$ Pull-Up otherwise.                                                                                                                                                               |  |

| 26<br>25     | A3TX+,<br>A3TX-     | 0    | CML differential positive/negative outputs for Channel A3, with internal 50 $\Omega$ Pull-Up and ~2k $\Omega$ Pull-Up otherwise.                                                                                                                                                                |  |

| Control Sign | als                 |      |                                                                                                                                                                                                                                                                                                 |  |

| 19           | SCL                 | I/O  | I2C Serial Clock line                                                                                                                                                                                                                                                                           |  |

| 18           | SDA                 | I/O  | I2C Serial Data line                                                                                                                                                                                                                                                                            |  |

| 20           | PRSNT#              | I    | Cable Present Detect input.<br>This pin has internal $100K\Omega$ pull-up. When High, a cable is not present, and the device is put in lower power mode.<br>When Low, the device is enabled and in normal operation.                                                                            |  |

| 21           | ENI2C               | I    | I2C Enable pin.<br>Tie to VDD = Register access I2C Slave mode<br>Tie to GND = Pin mode                                                                                                                                                                                                         |  |

| 39,40,41,42  | EQ[3:0]             | I    | EQ Control pin.<br>Inputs with internal $100k\Omega$ pull-up. This pins set the amount of Equalizer Boost in all channel when ENI2C is LOW.                                                                                                                                                     |  |

|              | AD[3:0]             | Ι    | I2C address bits control pins for programming with internal 100k $\Omega$ pull-up.                                                                                                                                                                                                              |  |

| 1,2          | SW[1:0]             | Ι    | Output Swing control pins.         Inputs with internal 100kΩ pull-up.         This pin sets the output Voltage Level in all channel when ENI2C is LOW.                                                                                                                                         |  |

| 37           | FG0                 | I    | Gain Control pin bit 0<br>Inputs with internal $100k\Omega$ pull up resistor. Sets the output flat gain level on all channels<br>when ENI2C is low.                                                                                                                                             |  |

| 38           | FG1/I2C_RE-<br>SET# | I    | <ul> <li>Shared pin for Flat Gain control bit-1 or I2C Reset pin. Inputs with internal 100kΩ pull up resistor.</li> <li>(1) Sets the output flat gain level bit-1 on all channels when ENI2C is Low.</li> <li>(2) I2C Reset pin. Active Low to reset the registers to default state.</li> </ul> |  |

#### 42-pin package cont.

| Pin #                       | Pin Name   | Туре | Description                  |  |  |

|-----------------------------|------------|------|------------------------------|--|--|

| 6,12,30                     | NC         |      | No Connect ( Don't care) pin |  |  |

| 16, 17, 22, 23              | DNC        |      | Do Not Connect pin           |  |  |

| Power Pins                  | Power Pins |      |                              |  |  |

| 3, 9, 15, 24,<br>27, 33, 36 | VDD        | PWR  | 3.3V Power Supply pins       |  |  |

| Center Pad                  | GND        | GND  | Exposed Ground pad.          |  |  |

# 4. Functional Description

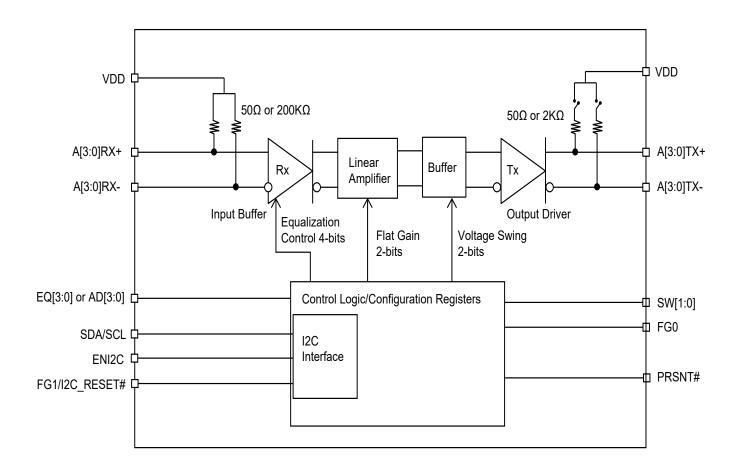

# 4.1 Functional Block Diagram

Figure 4-1 PI3DPX1203B Block Diagram

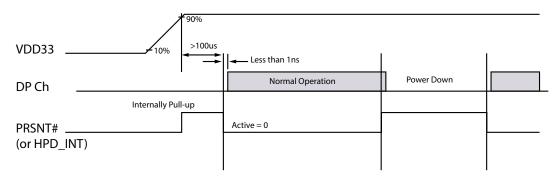

#### 4.2 Power-Down Mode

Power Enable function: One pin control or I2C control, when PRSNT# is set to high, the IC goes into power down mode, both input and output termination set to 200K and high impedance respectively. Individual channel enabling is done through the I2C register programming.

| PRSNT# | Description                                                  | Input Termination<br>Resistor | Output Termination<br>Resistor |

|--------|--------------------------------------------------------------|-------------------------------|--------------------------------|

| Н      | Power-down mode. PRSNT# is internally pull-up 100 k $\Omega$ | 200 kΩ pull-up                | Hi-Z (2 k $\Omega$ pull-up)    |

| L      | Active Low for normal operation                              | 50 Ω pull-up                  | 50 Ω pull-up                   |

Figure 4-2 Power-up sequence recommendation

#### 4.3 Flat Gain Setting

Flat Gain Control 2 bits FG[1:0] are the selection bits for the DC value.

| ,          | Table 4-1. | Flat Gain | a 2 bits Control | Set | tting |

|------------|------------|-----------|------------------|-----|-------|

| - <b>г</b> |            |           | 1                | -   |       |

| FG1 | FG0 | Gain (dB) | Notes                                                                                                                                    |

|-----|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0   | -3.5      |                                                                                                                                          |

| 0   | 1   | -1.5      |                                                                                                                                          |

| 1   | 0   | 0.5       | Keep 0.5dB Gain setting for most application cases. Try other setting for the long cable/<br>transmission line when 0.5dB does not work. |

| 1   | 1   | 2.5       |                                                                                                                                          |

#### 4.4 Output -1 dB Compression Setting

Swing Control 2 bits SW[1:0] control the linearity of the output voltage

| SW1 | SW0 | mVppd @ 8.1 Gbps<br>(Internally 100KΩ Pull-up) | Notes                                                                     |  |  |

|-----|-----|------------------------------------------------|---------------------------------------------------------------------------|--|--|

| 0   | 0   | 920mV                                          |                                                                           |  |  |

| 0   | 1   | 1040mV                                         | <ul> <li>Recommend setting for fixed DP swing like embedded DP</li> </ul> |  |  |

| 1   | 0   | 1280mV                                         | DP spec max swing = 1.2Vdiff                                              |  |  |

| 1   | 1   | 1370mV                                         | Reserved for the non-standard DP application                              |  |  |

#### Table 4-2. Output Swing -1dB Compression 2 bits Setting

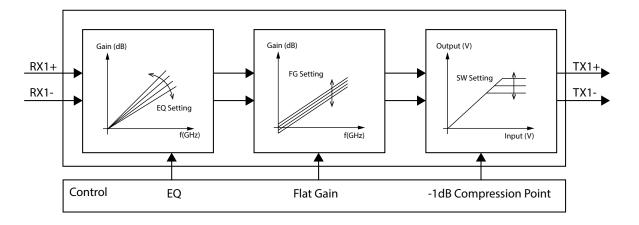

#### 4.5 EQ Setting

Input EQ control 4 bits EQ[3:0] are the selection pins for the equalization selection for each Main Link channel.

| EQ3 | EQ2 | EQ1 | EQ0 | 2.7 Gbps Input EQ(dB) | 5.4 Gbps Input EQ(dB) | 8.1 Gbps Input EQ(dB) |

|-----|-----|-----|-----|-----------------------|-----------------------|-----------------------|

| 0   | 0   | 0   | 0   | 2.3                   | 3.2                   | 3.9                   |

| 0   | 0   | 0   | 1   | 2.4                   | 3.5                   | 4.4                   |

| 0   | 0   | 1   | 0   | 2.5                   | 3.8                   | 4.9                   |

| 0   | 0   | 1   | 1   | 2.6                   | 4.1                   | 5.5                   |

| 0   | 1   | 0   | 0   | 2.7                   | 4.5                   | 6.0                   |

| 0   | 1   | 0   | 1   | 2.9                   | 4.8                   | 6.5                   |

| 0   | 1   | 1   | 0   | 3.0                   | 5.1                   | 6.9                   |

| 0   | 1   | 1   | 1   | 3.1                   | 5.5                   | 7.4                   |

| 1   | 0   | 0   | 0   | 3.2                   | 5.8                   | 7.8                   |

| 1   | 0   | 0   | 1   | 3.4                   | 6.1                   | 8.3                   |

| 1   | 0   | 1   | 0   | 3.5                   | 6.4                   | 8.7                   |

| 1   | 0   | 1   | 1   | 3.7                   | 6.7                   | 9.0                   |

| 1   | 1   | 0   | 0   | 3.8                   | 7.0                   | 9.4                   |

| 1   | 1   | 0   | 1   | 4.0                   | 7.4                   | 9.8                   |

| 1   | 1   | 1   | 0   | 4.1                   | 7.6                   | 10.1                  |

| 1   | 1   | 1   | 1   | 4.3                   | 7.9                   | 10.4                  |

#### Table 4-3. Input Equalizer 4 bits Setting

Figure 4-3 Illustration of EQ, Gain and -1dB Compression Point setting

# 5. I2C Programming

# 5.1 I2C Registers

#### Table 5-1. I2C Address assignment

| A6 | A5 | A4 | A3  | A2  | A1  | A0                                         | R/W      |

|----|----|----|-----|-----|-----|--------------------------------------------|----------|

| 1  | 1  | 1  | AD3 | AD2 | AD1 | 1 for ZL32 package<br>AD0 for ZH42 package | 1=R, 0=W |

#### Table 5-2. I2C Programming Register definition

#### BYTE 0

| Bit | Туре     | Power up condition | Description | Control affected | Comment |

|-----|----------|--------------------|-------------|------------------|---------|

| 7:0 | Reserved |                    |             |                  |         |

#### BYTE 1

| Bit | Туре     | Power up condition | Description | Control affected | Comment |

|-----|----------|--------------------|-------------|------------------|---------|

| 7:0 | Reserved |                    |             |                  |         |

#### BYTE 2

| Bit | Туре | Power up condition | Description   | Control affected | Comment        |  |

|-----|------|--------------------|---------------|------------------|----------------|--|

| 7   | R/W  | 0                  | A3 Power down |                  |                |  |

| 6   | R/W  | 0                  |               | A2 Power down    |                |  |

| 5   | R/W  | 0                  |               | A1 Power down    |                |  |

| 4   | R/W  | 0                  | A0 Power down |                  | 1 = Power down |  |

| 3   | R/W  | 0                  |               |                  |                |  |

| 2   | R/W  | 0                  |               |                  |                |  |

| 1   | R/W  | 0                  | Reserved      |                  |                |  |

| 0   | R/W  | 0                  |               |                  |                |  |

#### BYTE 3

| Bit | Туре | Power up condition | Description              | Control affected | Comment     |

|-----|------|--------------------|--------------------------|------------------|-------------|

| 7   | R/W  | 0                  |                          | EQ3              |             |

| 6   | R/W  | 0                  |                          | EQ2              |             |

| 5   | R/W  | 0                  |                          | EQ1              | Equalizer   |

| 4   | R/W  | 0                  | Channel AO configuration | EQ0              |             |

| 3   | R/W  | 0                  | Channel A0 configuration | FG1              | Elat asia   |

| 2   | R/W  | 0                  |                          | FG0              | - Flat gain |

| 1   | R/W  | 0                  |                          | SW1              | Service     |

| 0   | R/W  | 0                  |                          | SW0              | Swing       |

#### BYTE 4

| Bit | Туре | Power up condition | Description                | Control affected | Comment     |  |

|-----|------|--------------------|----------------------------|------------------|-------------|--|

| 7   | R/W  | 0                  |                            | EQ3              |             |  |

| 6   | R/W  | 0                  |                            | EQ2              | <b>P</b> 1' |  |

| 5   | R/W  | 0                  |                            | EQ1              | Equalizer   |  |

| 4   | R/W  | 0                  |                            | EQ0              |             |  |

| 3   | R/W  | 0                  | - Channel A1 configuration | FG1              |             |  |

| 2   | R/W  | 0                  |                            | FG0              | Flat gain   |  |

| 1   | R/W  | 0                  |                            | SW1              | Suria a     |  |

| 0   | R/W  | 0                  |                            | SW0              | Swing       |  |

#### BYTE 5

| Bit | Туре | Power up condition | Description              | Control affected | Comment     |

|-----|------|--------------------|--------------------------|------------------|-------------|

| 7   | R/W  | 0                  |                          | EQ3              |             |

| 6   | R/W  | 0                  |                          | EQ2              | <br>        |

| 5   | R/W  | 0                  |                          | EQ1              | - Equalizer |

| 4   | R/W  | 0                  |                          | EQ0              |             |

| 3   | R/W  | 0                  | Channel A2 configuration | FG1              | Plat and a  |

| 2   | R/W  | 0                  |                          | FG0              | - Flat gain |

| 1   | R/W  | 0                  |                          | SW1              | Courin a    |

| 0   | R/W  | 0                  |                          | SW0              | Swing       |

#### BYTE 6

| Bit | Туре | Power up condition | Description              | Control affected | Comment   |

|-----|------|--------------------|--------------------------|------------------|-----------|

| 7   | R/W  | 0                  |                          | EQ3              |           |

| 6   | R/W  | 0                  |                          | EQ2              | F 1'      |

| 5   | R/W  | 0                  |                          | EQ1              | Equalizer |

| 4   | R/W  | 0                  |                          | EQ0              |           |

| 3   | R/W  | 0                  | Channel A3 configuration | FG1              | Elat asia |

| 2   | R/W  | 0                  |                          | FG0              | Flat gain |

| 1   | R/W  | 0                  | 1                        | SW1              | Curin a   |

| 0   | R/W  | 0                  |                          | SW0              | Swing     |

#### BYTE 7

| Bit | Туре     | Power up condition | Description | Control affected | Comment |

|-----|----------|--------------------|-------------|------------------|---------|

| 7:0 | Reserved |                    |             |                  |         |

#### 5.2 I2C Operation

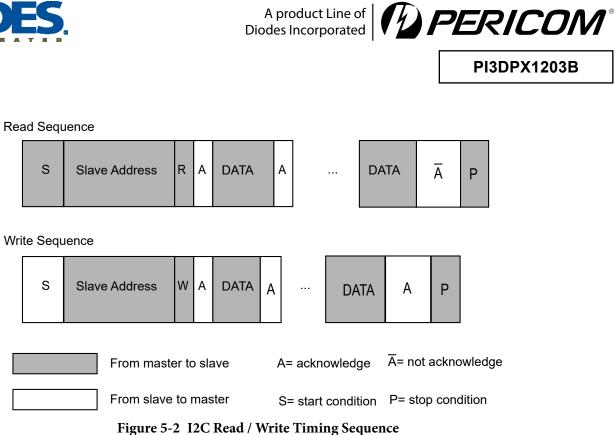

The integrated I2C interface operates as a slave device mode. Standard I2C mode (100 Kbps) is supported with 7-bit addressing and data byte format 8-bit.

The device supports Read/Write. The bytes must be accessed in sequential order from the lowest to the highest byte with the ability to stop after any complete byte has been transferred. Address bits A3 to A0 are programmable to support multiple chips environment. The Data is loaded until a Stop sequence is issued.

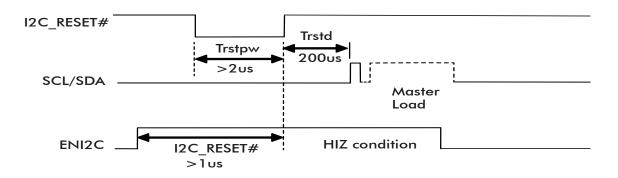

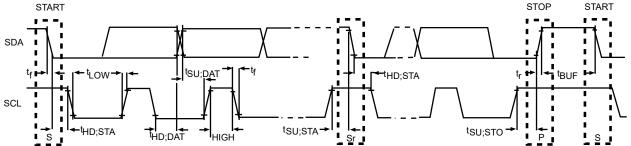

Figure 5-1 I2C Reset, Enable and SCL/SDA Timing Diagram

#### **Transferring Data**

Every byte put on the SDA line must be 8-bit long. Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit (MSB) first (see the I2C Data Transfer diagram). It will never hold the clock line SCL LOW to force the master into a wait state.

#### Acknowledge

Data transfer with acknowledge is required from the master. When the master releases the SDA line (HIGH) during the acknowledge clock pulse, it will pull down the SDA line during the acknowledge clock pulse so that it remains stable LOW during the HIGH period of this clock pulse as indicated in the I2C Data Transfer diagram. It will generate an acknowledge after each byte has been received.

#### Data Transfer

A data transfer cycle begins with the master issuing a start bit. After recognizing a start bit, it will watch the next byte of information for a match with its address setting. When a match is found it will respond with a read or write of data on the following clocks. Each byte must be followed by an acknowledge bit, except for the last byte of a read cycle which ends with a stop bit. Data is transferred with the most significant bit (MSB) first.

#### **Start & Stop Conditions**

A HIGH to LOW transition on the SDA line while SCL is HIGH indicates a START condition. A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition.

# 6. Electrical Specification

#### 6.1 Absolute Maximum Ratings

| Supply Voltage to Ground Potential | -0.5 V to +4.6 V |

|------------------------------------|------------------|

| DC SIG Voltage                     |                  |

| Output Current                     |                  |

| Power Dissipation Continuous       |                  |

| ESD, HBM                           |                  |

| Storage Temperature                |                  |

| Maximum Junction temperature       |                  |

Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### 6.2 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

| Parameter                                  | Min.                                          | Тур.               | Max | Units |       |

|--------------------------------------------|-----------------------------------------------|--------------------|-----|-------|-------|

| Power supply voltage (VDD to GND)          |                                               |                    | 3.3 | 3.6   | V     |

| Supply Noise Tolerance (from 100KHz to 10M | Supply Noise Tolerance (from 100KHz to 10MHz) |                    |     |       | mVp-p |

| Operating free-air temperature (TA)        | Commercial Temperature                        | 0                  |     | 70    | °C    |

|                                            | Industrial Temperature                        | -40 <sup>(1)</sup> |     | 85    | °C    |

Note:

(1) I-temp is design guarantee, not production tested.

# 6.3 Power Consumption

Over operating free-air temperature range (unless otherwise noted)

| Symbol           | Parameter                      | Conditions                                                                        | Min. | Тур. | Max | Units |

|------------------|--------------------------------|-----------------------------------------------------------------------------------|------|------|-----|-------|

| V <sub>DD</sub>  | Power supply voltage           |                                                                                   | 3.0  | 3.3  | 3.6 | V     |

| I <sub>DD</sub>  | Operation power supply current | SW[1:0]=10 ( 1.2V <sub>DIFF</sub> swing @8Gbps, 0dB pre-emphasis)                 |      | 243  | 290 | mA    |

| I <sub>DDQ</sub> | Standby power supply current   | All other control pins are open. Disabled<br>I2C master mode & I2C internal clock |      | 0.2  | 1   | mA    |

Note: Power consumption varies with the different Gain / Output Swing (-1dB Compression Point) setting.

| Control Setting | Gain (dB) | Voltage Swing<br>Limit (mV) | IDD(mA) |

|-----------------|-----------|-----------------------------|---------|

| FG/SW=0000      | -3.5      | 920                         | 211     |

| FG/SW=0001      | -3.5      | 1040                        | 228     |

| FG/SW=0010      | -3.5      | 1280                        | 245     |

| FG/SW=0100      | -2.5      | 920                         | 263     |

| FG/SW=0101      | -2.5      | 1040                        | 228     |

| FG/SW=0110      | -2.5      | 1280                        | 245     |

| FG/SW=1000      | +0.5      | 920                         | 211     |

### 6.4 AC/DC Characteristics

#### 6.4.1 LVCMOS I/O DC Specifications

| Symbol           | Parameter                           | Conditions | Min.      | Тур. | Max       | Units |

|------------------|-------------------------------------|------------|-----------|------|-----------|-------|

| V <sub>IH</sub>  | DC input logic HIGH                 |            | VDD/2+0.7 |      | VDD+0.3   | V     |

| V <sub>IL</sub>  | DC input logic LOW                  |            | -0.3      |      | VDD/2-0.7 | V     |

| V <sub>OH</sub>  | At IOH = -200 μA                    |            | VDD+0.2   |      |           | V     |

| V <sub>OL</sub>  | At IOL = -200 μA                    |            |           |      | 0.2       | V     |

| V <sub>HYS</sub> | Hysteresis of Schmitt trigger input |            | 0.8       |      |           | V     |

#### 6.4.2 Main Link Differential

Over operating free-air temperature range (unless otherwise noted)

| Symbol                      | Parameter                                                        | Conditions                                                   | Min.      | Тур.                        | Max.      | Units |  |

|-----------------------------|------------------------------------------------------------------|--------------------------------------------------------------|-----------|-----------------------------|-----------|-------|--|

| C <sub>RX</sub>             | RX AC coupling capacitance                                       |                                                              |           | 220                         |           | nF    |  |

|                             | Input return loss <sup>(2)</sup>                                 | 10 MHz to 4.1 GHz differential                               |           | -13.0                       |           | dB    |  |

| S11                         | Input return loss                                                | 1 GHz to 4.1 GHz common mode                                 |           | -5.0                        |           | db    |  |

| S22                         | Output return loss <sup>(2)</sup> 10 MHz to 4.1 GHz differen     |                                                              |           | -15                         |           | ۹Ŀ    |  |

| 322                         | Output feturn loss >                                             | 1 GHz to 4.1 GHz common mode                                 |           | -6.0                        |           | dB    |  |

| D                           | DC single-ended input impedance                                  |                                                              |           | 50                          |           | Ω     |  |

| R <sub>IN</sub>             | DC Differential Input Impedance                                  |                                                              |           | 100                         |           | 12    |  |

| R <sub>OUT</sub>            | DC single-ended output imped-<br>ance                            |                                                              |           | 50                          |           | Ω     |  |

| 001                         | DC Differential output Impedance                                 |                                                              |           | 100                         |           |       |  |

| Z <sub>RX-HIZ</sub>         | DC input impedance during reset<br>or power down                 |                                                              |           | 200                         |           | kΩ    |  |

| V <sub>RX-</sub><br>DIFFp-p | Peak to peak differential input voltage                          | For HBR3                                                     |           | 0.2 <sup>(1)</sup>          | 1.2       | Vppd  |  |

|                             | Input Source common-mode noise                                   | DC - 200MHz                                                  |           |                             | 150       | mVpp  |  |

| t <sub>PD</sub>             | Latency                                                          | From input to output                                         |           | 0.5                         |           | ns    |  |

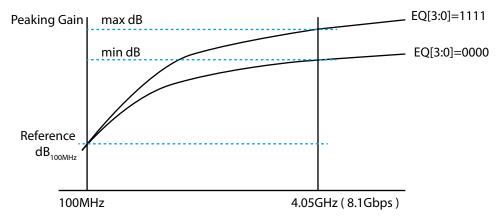

| G <sub>p</sub>              | Peaking gain: Compensation at<br>4 GHz, relative to 100 MHz, 100 | EQ[3:0] = 1111<br>EQ[3:0] = 1000<br>EQ[3:0] = 0000           |           | 10.4<br>7.8<br>3.9          |           | dB    |  |

|                             | mVp-p sine wave input                                            | Variation around typical                                     | -3        |                             | +3        | dB    |  |

| G <sub>F-gain</sub>         | Flat gain: 100 MHz, EQ[3:0] =<br>1000, SW[1:0] = 10              | FG[1:0] = 11<br>FG[1:0] = 10<br>FG[1:0] = 01<br>FG[1:0] = 00 |           | +2.5<br>0.5<br>-1.5<br>-3.5 |           | dB    |  |

|                             |                                                                  | Variation around typical                                     | -3        |                             | +3        | dB    |  |

|                             | Frequency Response Gain curve 1-5                                | 5GHz with 18-inch FR4, FG=10                                 | Pls refer | the Freq/Ga<br>below        | ain curve | dB    |  |

| Symbol                   | Parameter                                               | Conditions                                                   | Conditions                                      |     | Тур.                        | Max. | Units             |

|--------------------------|---------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------|-----|-----------------------------|------|-------------------|

| V <sub>1dB_100M</sub>    | -1 dB compression point of output<br>swing (at 100 MHz) | SW[1:0] = 11<br>SW[1:0] = 10<br>SW[1:0] = 01<br>SW[1:0] = 00 |                                                 |     | 1370<br>1280<br>1040<br>920 |      | mVppd             |

| V <sub>Coup</sub>        | Channel isolation (Note 1)                              | 100MHz to 4GHz                                               |                                                 |     | 25                          |      | dB                |

|                          |                                                         | 100MHz to 4GHz,<br>EQ<3:0> = 0000                            |                                                 | 0.5 |                             |      |                   |

| V <sub>noise_input</sub> | Input-referred noise                                    | 100MHz to 4GHz, FG<1:0> = 11,<br>EQ<3:0> = 1010              |                                                 |     | 0.4                         |      | mV <sub>RMS</sub> |

| V <sub>noise_out-</sub>  | V · · · · (Neth 2)                                      |                                                              | 100MHz to 4GHz, FG<1:0> = 11,<br>EQ<3:0> = 0000 |     | 0.7                         |      |                   |

| put                      | Output-referred noise (Note 2)                          | 100MHz to 4GHz, FG<br>EQ<3:0> = 1010                         |                                                 |     | 0.8                         | 1.6  | mV <sub>RMS</sub> |

|                          | Deterministic Jitter                                    | Data Rate =<br>8Gbps<br>FGx[1:0] = 10                        | EQ = 0000<br>EQ = 1010<br>EQ = 1111             |     |                             |      | UIp-p             |

Note:

(1) Channel Isolation measured using a vector-network analyzer (VNA) with -15dBm power level applied to the adjacent input. The VNA detects the signal at the output of the victim channel. All other inputs and outputs are terminated with  $50\Omega$ .

(2) Guaranteed by design and characterization.

(3) Please refer more data in the VIN / VOUT plot. VOUT changes withe EQ and FG setting. Both the ReDriver and the Sink device system should be carefully designed to ensure sink-device compliance.

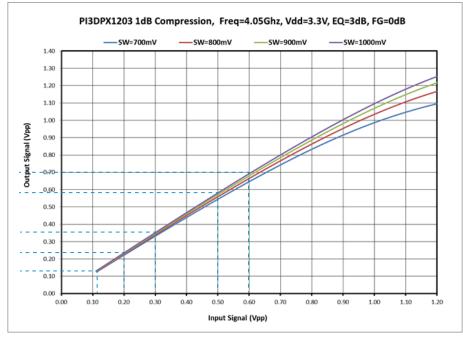

Figure 6-1 1dB Compression(Voltage Sweep) between 0 to 600mV Inputs @ 8Gbps

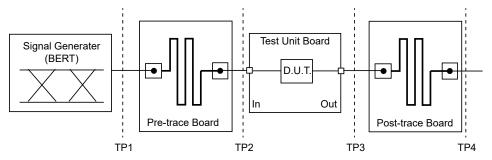

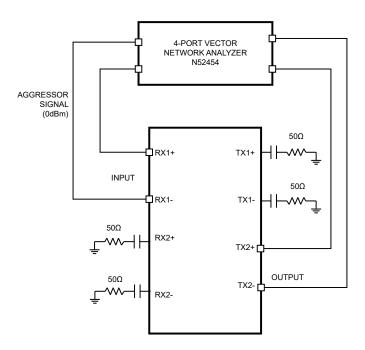

Figure 6-2 AC Electrical Measurement Test Setup

Figure 6-3 Channel-Isolation Test Configuration

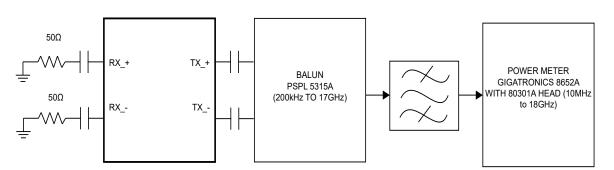

Figure 6-4 Noise Test Configuration

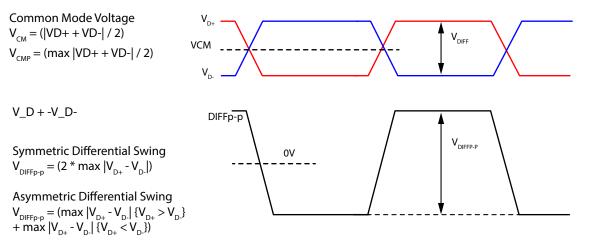

Figure 6-5 Definition of Differential Voltage and Differential Voltage Peak-to-Peak

Figure 6-6 Definition of Peaking Gain relative to 100 MHz, 100 mVp-p sine wave input

#### 6.4.3 SCL/SDA Specification for I2C BUS

Over operating free-air temperature range (unless otherwise noted)

| Symbol                | Parameter                                                                                            | Conditions               | Min.             | Тур. | Max                         | Units |

|-----------------------|------------------------------------------------------------------------------------------------------|--------------------------|------------------|------|-----------------------------|-------|

| SDA and SC            | CL I/O for I2C-bus                                                                                   |                          |                  |      |                             |       |

| V <sub>DD</sub>       | Nominal Bus Voltage                                                                                  |                          | 3.0              |      | 3.6                         | V     |

| V <sub>IH</sub>       | DC input logic HIGH                                                                                  |                          | $V_{DD}/2 + 0.7$ |      | V <sub>DD</sub> + 0.3       | V     |

| V <sub>IL</sub>       | DC input logic LOW                                                                                   |                          | -0.3             |      | V <sub>DD</sub> /2 -<br>0.7 | V     |

| V <sub>OL</sub>       | DC output logic LOW                                                                                  | $I_{OL} = 3mA$           |                  |      | 0.4                         | V     |

| t <sub>OF</sub>       | Output fall time from VIHmin to VIL-<br>max with bus cap. 10-400pF                                   |                          |                  |      | 250                         | ns    |

| AC/DC Spe             | cifications - SCL/SDA for I2C BUS                                                                    |                          |                  |      |                             |       |

| I <sub>PU</sub>       | Current Through Pull-Up Resistor<br>or Current Source                                                | High Power specification | 3.0              |      | 3.6                         | mA    |

| I <sub>leak-bus</sub> | Input leakage per bus segment                                                                        |                          | -200             |      | 200                         | uA    |

| Ileak-pin             | Input leakage per device pin                                                                         |                          |                  | -15  |                             | uA    |

| CI                    | Capacitance for SDA/SCL                                                                              |                          |                  |      | 10                          | pF    |

| f <sub>SCLK</sub>     | Bus Operation Frequency                                                                              |                          |                  | 100  |                             | KHz   |

| tBUF                  | "Bus Free Time Between Stop and Start condition"                                                     |                          | 1.3              |      |                             | us    |

| tHD:STA               | Hold time after (Repeated) Start condi-<br>tion. After this period, the first clock is<br>generated. | At Ipull-up, Max         | 0.6              |      |                             | us    |

| tSU:STA               | Repeated start condition setup time                                                                  |                          | 0.6              |      |                             | us    |

| tSU:STO               | Stop condition setup time                                                                            |                          | 0.6              |      |                             | us    |

| tHD:DAT               | Data hold time                                                                                       |                          | 0                |      |                             | ns    |

| tSU:DAT               | Data setup time                                                                                      |                          | 100              |      |                             | ns    |

| tLOW                  | Clock Low period                                                                                     |                          | 1.3              |      |                             | us    |

| tHIGH                 | Clock High period                                                                                    |                          | 0.6              |      | 50                          | us    |

| tF                    | Clock/Data fall time                                                                                 |                          |                  |      | 300                         | ns    |

| tR                    | Clock/Data rise time                                                                                 |                          |                  |      | 300                         | ns    |

| tPOR                  | "Time in which a device must be opera-<br>tion after power-on reset"                                 |                          |                  |      | 500                         | ms    |

Note:

(1) Recommended value.

(2) Recommended maximum capacitance load per bus segment is 400pF.

(3) Compliant to I2C physical layer specification.

(4) Ensured by Design. Parameter not tested in production.

Figure 6-7 I<sup>2</sup>C Timing Diagram

# 7. Applications

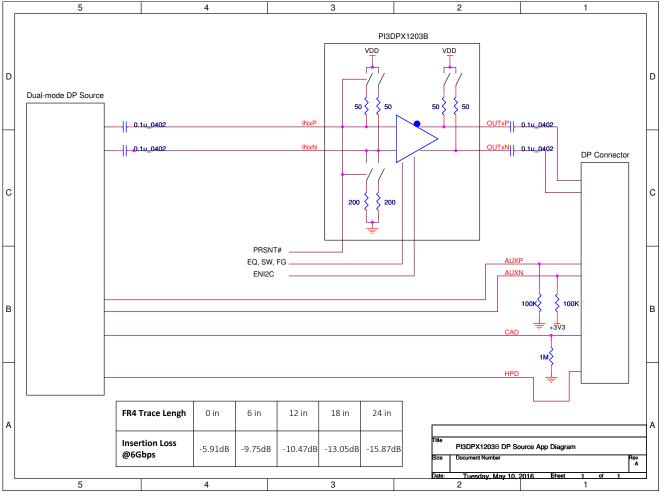

# 7.1 Reference Schematic

- Determine the loss profile between transmitter and receiver. •

- Based upon the loss profile and signal swing, determine the optimal equalization settings.

- Select appropriate voltage output swing.

- If required, select the correct differential pair polarity.

- To set voltage logic levels on configuration pins, use a 5-k $\Omega$  pull-up for high level, tie pin to GND for low level, and place a 5-k $\Omega$  pull-up and 5-k $\Omega$  pull-down for HiZ.

Figure 7-1 Source side DP Redriver Connection Diagram

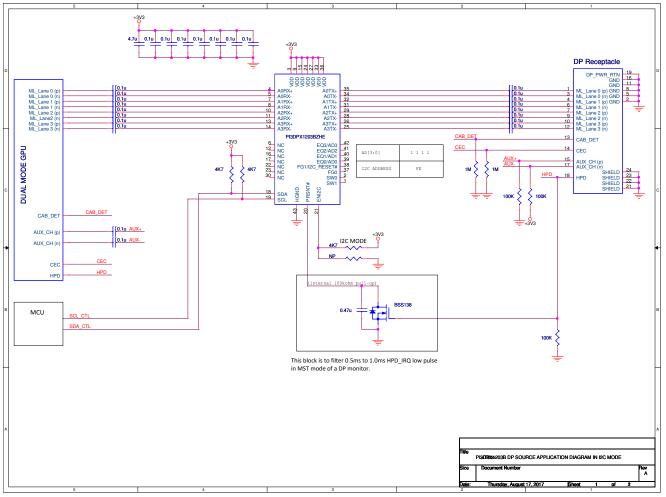

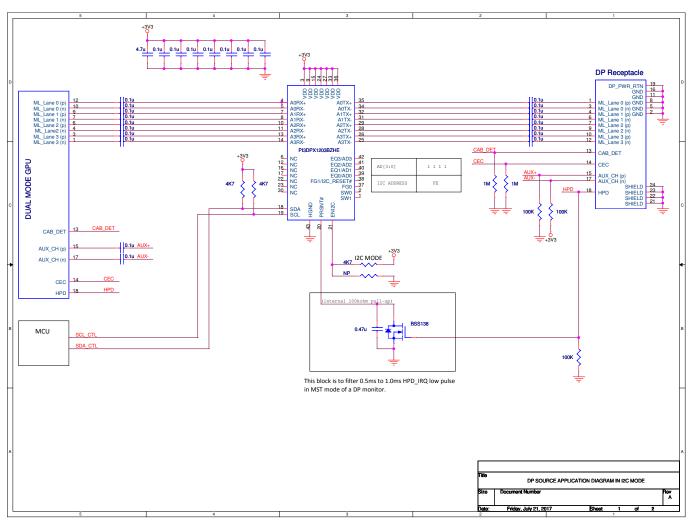

# 7.2 Reference Schematic for HPD\_IRQ MST Mode

Figure 7-2 DP Source Application in Pin Mode

Figure 7-3 DP Source Application in I2C Mode

#### 7.3 Sink-side Application

Note

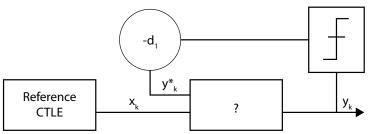

(1) The HBR3 receiver equalizer includes a CTLE cascaded with a one-tap adaptive DFE with a feedback coefficient limited to < 50mV. The DFE behavior is described below.

$$y_{k} = x_{k} - d_{1}^{*} \operatorname{sgn}(y_{k} - 1)$$

$y_k$  is the DFE differential output voltage

- $y_{k}^{*}$  is the decision function output voltage  $x_{k}$  is the differential input voltage after CTLE

- d, is the feedback coefficient

k is the UI sample

**Decision Function**

Reference HBR3 Receiver Equalizer DFE

#### Figure 7-4 Linear Redriver Linking with Sink-side Receiver CTLE+DFE

#### 7.4 Output Swing and Gain Information

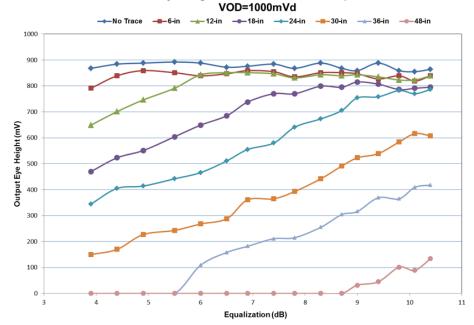

Figure 7-5 Eye Width vs EQ, Output\_Swing =1000mV, Gain=+0.5dB (Input Swing=1000mVd) PI3DPX1203B Eye Height vs EQ, Vdd=3.3V, 8.1Gbps, PRBS2^23-1,

Figure 7-6 Eye Height vs EQ, Output Swing =1000mV, Gain=+2.5dB (Vin =800mVdiff)

| A product Line of<br>Diodes Incorporated | PER | RICOM |

|------------------------------------------|-----|-------|

|------------------------------------------|-----|-------|

# 7.5 Output Eye diagram, Trace length and EQ

Condition: Output Eye Opening with Input Equalization, 8.1 Gbps, Vdd=3.3V, 25C, Using PRBS 2^23-1 pattern, Input Swing=800mVd, Output Swing=1000mV

#### No Trace, EQ=3.9dB

12-in, EQ = 6.0dB

18-in, EQ=7.4dB

24-in, EQ=8.7dB

30-in, EQ = 10.4dB

36-in, EQ= 10.4dB

8-33I

HEIT

Figure 7-7 Output Eye Diagram at FG 0.5dB

Note:

#### Table 7-1. Trace card insertion loss profile is shown below.

| Frequency           | 3 GHz  | 6GHz | Units |

|---------------------|--------|------|-------|

| 6 inch Input Trace  | -1.43  | -4   | dB    |

| 12 inch Input Trace | -6.1   | -11  | dB    |

| 18 inch Input Trace | -8.34  | -15  | dB    |

| 30 inch Input Trace | -10.14 | -18  | dB    |

| 36 inch Input Trace | -12.13 | -22  | dB    |

| 48 inch Input Trace | -16.42 | -29  | dB    |

Figure 7-8 Trace Board Photo

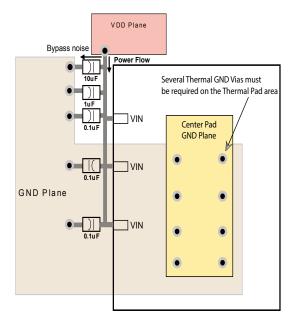

# 7.6 General Power and Ground Guideline

To provide a clean power supply for high-speed device, few recommendations are listed below:

- Power (VDD) and ground (GND) pins should be connected to corresponding power planes of the printed circuit board directly • without passing through any resistor.

- The thickness of the PCB dielectric layer should be minimized such that the VDD and GND planes create low inductance paths.

- One low-ESR 0.1uF decoupling capacitor should be mounted at each VDD pin or should supply bypassing for at most two VDD pins. Capacitors of smaller body size, i.e. 0402 package, is more preferable as the insertion loss is lower. The capacitor should be placed next to the VDD pin.

- One capacitor with capacitance in the range of 4.7uF to 10uF should be incorporated in the power supply decoupling design as well. It can be either tantalum or an ultra-low ESR ceramic.

- A ferrite bead for isolating the power supply for Pericom high-speed device from the power supplies for other parts on the printed circuit board should be implemented.

- Several thermal ground vias must be required on the thermal pad. 25-mil or less pad size and 14-mil or less finished hole are recommended.

Figure 7-9 Decoupling Capacitor Placement Diagram

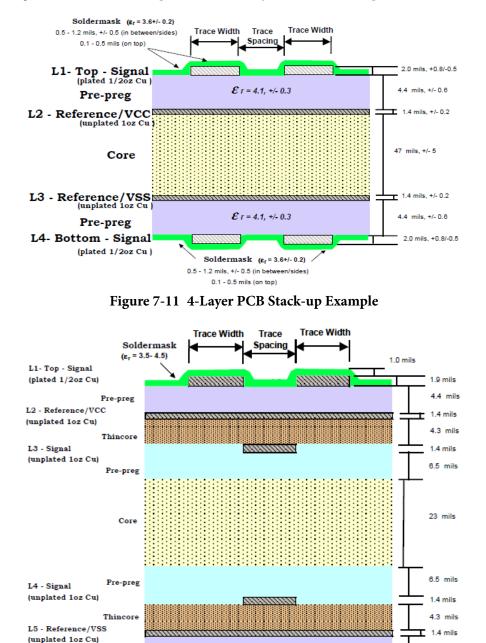

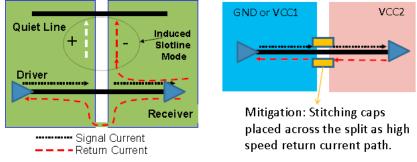

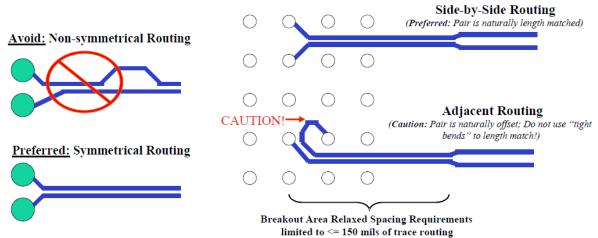

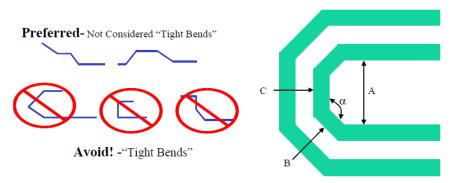

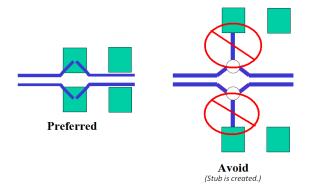

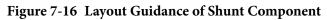

### 7.7 High-speed signal Routing

Well-designed layout is essential to prevent signal reflection:

- For 90Ω differential impedance, width-spacing-width micro-strip of 6-7-6 mils is recommended; for 100Ω differential impedance, • width-spacing-width micro-strip of 5-7-5 mils is recommended.

- Differential impedance tolerance is targeted at  $\pm 15\%$ . •

| Trace and board parameters:                                                                                                                                                                                                                                                          | Single-ended mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Trace width: W= 6.0 🚖 mils                                                                                                                                                                                                                                                           | Characteristic Microstrip Stripline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Trace thickness: t = 1.9 🚖 mils (1.39 oz)                                                                                                                                                                                                                                            | impedance: $Z_{0=}$ 50.7 32.9 $\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |