16 Output LVPECL Fanout Buffer

#### **Features**

- → 16 Differential LVPECL outputs

- → 2 Selectable reference inputs support either single-ended or differential

- → Up to 2GHz output frequency

- → Ultra low additive phase jitter: < 0.01 ps (typ) (differential 156.25MHz, 12KHz to 20MHz integration range)

- → Low skew between outputs

- → Low delay from input to output

- → Separate Input output supply voltage for level shifting

- $\rightarrow$  2.5V / 3.3V power supply

- → Industrial temperature support

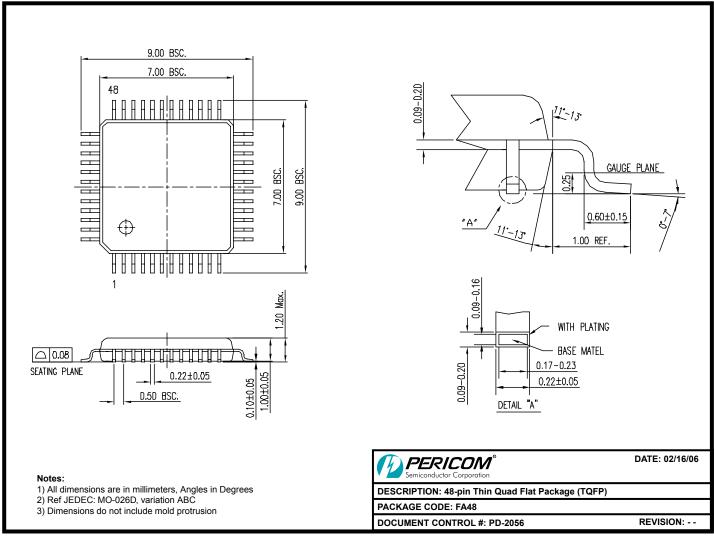

- → TQFP-48 package

### **Description**

The PI6C5912016-01 is a high performance LVPECL fanout buffer device which supports up to 2GHz frequency. This device is ideal for systems that need to distribute low jitter LVPECL clock signals to multiple destinations.

### **Applications**

- → Networking systems including switches and routers

- → High frequency backplane based computing and telecom platforms

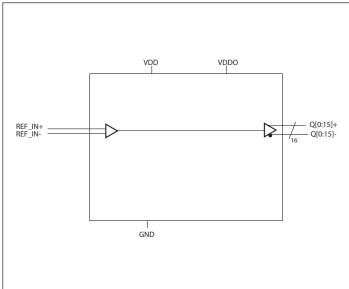

## **Block Diagram**

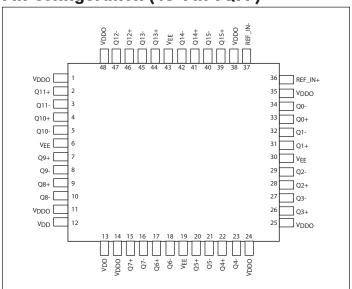

### Pin Configuration (48-Pin TQFP)

### **Pin Description**

| Pin #                         | Pin Name                     | Type   | Description                                                  |

|-------------------------------|------------------------------|--------|--------------------------------------------------------------|

| 1, 11, 14, 24, 25, 35, 38, 48 | $V_{\scriptscriptstyle DDO}$ | Power  | Output power supply                                          |

| 2, 3                          | Q11+, Q11-                   | Output | LVPECL output pair 11.                                       |

| 4, 5                          | Q10+, Q10-                   | Output | LVPECL output pair 10.                                       |

| 6, 19, 30, 43                 | $V_{\text{EE}}$              | Power  | Negative power supply                                        |

| 7, 8                          | Q9+, Q9-                     | Output | LVPECL output pair 9.                                        |

| 9, 10                         | Q8+, Q8-                     | Output | LVPECL output pair 8.                                        |

| 12, 13                        | VDD                          | Power  | Core power supply                                            |

| 15, 16                        | Q7+, Q7-                     | Output | LVPECL output pair 7.                                        |

| 17, 18                        | Q6+, Q6-                     | Output | LVPECL output pair 6.                                        |

| 20, 21                        | Q5+, Q5-                     | Output | LVPECL output pair 5.                                        |

| 22, 23                        | Q4+, Q4-                     | Output | LVPECL output pair 4.                                        |

| 26, 27                        | Q3+, Q3-                     | Output | LVPECL output pair 3.                                        |

| 28, 29                        | Q2+, Q2-                     | Output | LVPECL output pair 2.                                        |

| 31, 32                        | Q1+, Q1-                     | Output | LVPECL output pair 1.                                        |

| 33, 34                        | Q0+, Q0-                     | Output | LVPECL output pair 0.                                        |

| 36, 37                        | REF_IN+                      | Innut  | Reference input. Accepts Differential or Single Ended inputs |

| 30, 37                        | REF_IN-                      | Input  | Reference input. Accepts Differential of Single Ended inputs |

| 39, 40                        | Q15+, Q15-                   | Output | LVPECL output pair 15.                                       |

| 41, 42                        | Q14+, Q14-                   | Output | LVPECL output pair 14.                                       |

| 44, 45                        | Q13+, Q13-                   | Output | LVPECL output pair 13.                                       |

| 46, 47                        | Q12+, Q12-                   | Output | LVPECL output pair 12.                                       |

| Thermal Pad*                  | -                            | -      | Thermal pad. Connect to ground.                              |

<sup>\*</sup>Package type dependent. Only certain packages have thermal pad

#### **Function Table**

| Symbol                | Parameter               | <b>Test Condition</b> | Min. | Тур. | Max. | Units |

|-----------------------|-------------------------|-----------------------|------|------|------|-------|

| C <sub>IN</sub>       | Input Capcitance        |                       |      | 2    |      | pF    |

| R <sub>PULLDOWN</sub> | Input Pulldown Resistor |                       |      | 50   |      | kΩ    |

| R <sub>PULLUP</sub>   | Input Pullup Resistor   |                       |      | 50   |      | kΩ    |

### Maximum Ratings (Above which the useful life may be impaired. For user guidelines, not tested)

| Storage temperature55 to +150°C                                                 |

|---------------------------------------------------------------------------------|

| Supply Voltage to Ground Potential (V $_{\rm DD,}$ V $_{\rm DDO}$ )0.5 to +4.6V |

| Inputs (Referenced to GND)0.5 to $\rm V_{\rm DD} {+} 0.5 \rm V$                 |

| Clock Output (Referenced to GND)0.5 to $\rm V_{\rm DD} + 0.5 \rm V$             |

| Latch up200mA                                                                   |

| ESD Protection (Input)2000 V min (HBM)                                          |

| ESD Protection (Input)1000 V min (CDM)                                          |

|                                                                                 |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Power Supply Characteristics and Operating Conditions**

| Symbol                                 | Parameter                     | <b>Test Condition</b> | Min.  | Тур. | Max.  | Units |  |

|----------------------------------------|-------------------------------|-----------------------|-------|------|-------|-------|--|

| 37                                     | Core Supply Voltage           |                       | 3.135 | 3.3  | 3.465 | V     |  |

| $V_{\mathrm{DD}}$                      |                               |                       | 2.375 | 2.5  | 2.625 | V     |  |

|                                        |                               |                       | 3.135 | 3.3  | 3.465 | V     |  |

| V <sub>DDO</sub> Output Supply Voltage | Output Supply Voltage         |                       | 2.375 | 2.5  | 2.625 | V     |  |

| $I_{EE}$                               | Supply Internal Current       |                       |       |      | 125   | A     |  |

| $I_{\mathrm{DD}}$                      | Core Power Supply Current     |                       |       |      | 30    | m A   |  |

| T <sub>A</sub>                         | Ambient Operating Temperature |                       | -40   |      | 85    | °C    |  |

## **DC Electrical Specifications - Differential Inputs**

| Symbol             | Parameter                             |                         | Min.      | Тур. | Max.                  | Units |

|--------------------|---------------------------------------|-------------------------|-----------|------|-----------------------|-------|

| I <sub>IH</sub>    | Input High current                    | Input = V <sub>DD</sub> |           |      | 100                   | uA    |

| $I_{IL}$           | Input Low current                     | Input = GND             | -100      |      |                       | uA    |

| V <sub>IH</sub>    | Input high voltage                    |                         |           |      | V <sub>DD</sub> +0.3  | V     |

| V <sub>IL</sub>    | Input low voltage                     |                         | -0.3      |      |                       | V     |

| V <sub>ID</sub>    | Input Differential Amplitude<br>PK-PK |                         | 0.1       |      |                       | V     |

| V <sub>CM</sub>    | Common model input voltage            |                         | GND + 0.5 |      | V <sub>DD</sub> -0.85 | V     |

| ISO <sub>MUX</sub> | MUX isolation                         |                         |           | -89  |                       | dBc   |

### **DC Electrical Specifications - LVCMOS Inputs**

| Symbol          | Parameter          | Conditions                 | Min. | Тур. | Max.                 | Units |

|-----------------|--------------------|----------------------------|------|------|----------------------|-------|

| $I_{IH}$        | Input High current | Input = V <sub>DD</sub>    |      |      | 50                   | uA    |

| $I_{IL}$        | Input Low current  | Input = GND                | -50  |      |                      | uA    |

| V <sub>IH</sub> | Input high voltage | $V_{\mathrm{DD}}$ =3.3 $V$ | 2.0  |      | V <sub>DD</sub> +0.3 | V     |

| V <sub>IL</sub> | Input low voltage  | $V_{\mathrm{DD}}$ =3.3V    | -0.3 |      | 0.8                  | V     |

| V <sub>IH</sub> | Input high voltage | V <sub>DD</sub> =2.5V      | 1.7  |      | V <sub>DD</sub> +0.3 | V     |

| V <sub>IL</sub> | Input low voltage  | V <sub>DD</sub> =2.5V      | -0.3 |      | 0.7                  | V     |

# **DC Electrical Specifications- LVPECL Outputs**

| Parameter       | Description         | Conditions                 | Min.                  | Тур. | Max.                   | Units |

|-----------------|---------------------|----------------------------|-----------------------|------|------------------------|-------|

| V <sub>OH</sub> | Output High voltage |                            | V <sub>DDO</sub> -1.4 |      | V <sub>DDO</sub> -0.9  | V     |

| Vol             | Output Low voltage  | $V_{\mathrm{DD}}$ =2.5 $V$ | V <sub>DDO</sub> -1.9 |      | V <sub>DDO</sub> -1.25 | V     |

|                 |                     | V <sub>DD</sub> =3.3V      | V <sub>DDO</sub> -2.2 |      | V <sub>DDO</sub> -1.25 | V     |

# **AC Electrical Specifications – Differential Inputs**

| Parameter         | Description                             | Conditions                                           | Min. | Тур. | Max. | Units |

|-------------------|-----------------------------------------|------------------------------------------------------|------|------|------|-------|

| F <sub>IN</sub>   | Clock input frequency                   |                                                      |      |      | 2000 | MHz   |

| V <sub>INPP</sub> | Differential Input peak to peak voltage | $1.5 \text{GHz} \le F_{\text{IN}} \le 2 \text{ GHz}$ | 0.2  |      | 1.5  | V     |

|                   |                                         | $F_{IN} \le 1.5 \text{ GHz}$                         | 0.1  |      | 1.5  | V     |

| ER                | Input Edge Rate                         |                                                      | 1.5  |      |      | V/ns  |

## **AC Electrical Specifications – LVCMOS Inputs**

| Parameter         | Description                             | Conditions                                           | Min. | Тур. | Max. | Units |

|-------------------|-----------------------------------------|------------------------------------------------------|------|------|------|-------|

| F <sub>IN</sub>   | Clock input frequency                   |                                                      |      |      | 200  | MHz   |

| V <sub>INPP</sub> | Differential Input peak to peak voltage | $1.5 \text{GHz} \le F_{\text{IN}} \le 2 \text{ GHz}$ | 0.2  |      | 1.5  | V     |

|                   |                                         | $F_{IN} \le 1.5 \text{ GHz}$                         | 0.1  |      | 1.5  | V     |

| ER                | Input Edge Rate                         |                                                      | 1.5  |      |      | V/ns  |

## **AC Electrical Specifications – LVPECL Outputs**

| Parameter             | Description                    | Conditions                   | Min.                 | Typ. | Max.                 | Units |

|-----------------------|--------------------------------|------------------------------|----------------------|------|----------------------|-------|

| F <sub>OUT</sub>      | Clock output frequency         | LVPECL                       |                      |      | 2000                 | MHz   |

| $T_{\rm r}$           | Output rise time               | From 20% to 80%              |                      | 150  |                      | ps    |

| T <sub>f</sub>        | Output fall time               | From 80% to 20%              |                      | 150  |                      | ps    |

| Todc                  | Output duty cycle              |                              | 48                   |      | 52                   | %     |

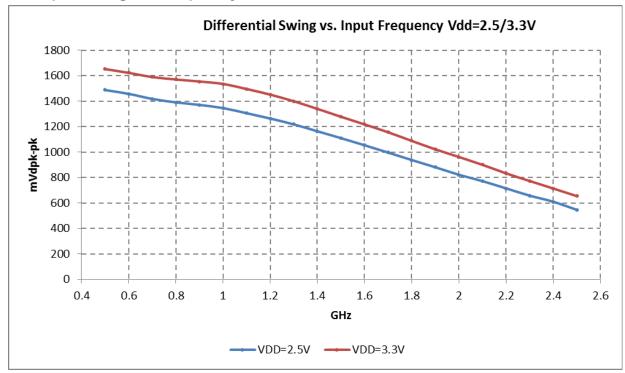

| 3.7                   | Output swing Cinals and d      | @1GHz to ≤2GHz               | 200                  |      | 850                  | mV    |

| $V_{PP}$              | Output swing Single-ended      | @ ≤1GHz                      | 450                  |      | 950                  | mV    |

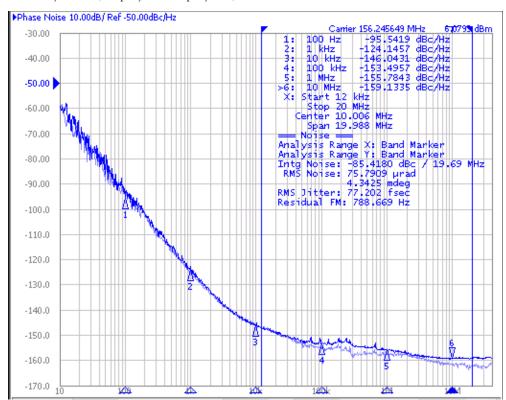

|                       | Buffer additive jitter RMS     | 156.25MHz, 12kHz to<br>20MHz |                      | 0.01 | 0.08                 | ps    |

| $T_j$                 |                                | 156.25MHz, 10kHz to<br>1MHz  |                      | 0.01 | 0.08                 | ps    |

| $T_{SK}$              | Output Skew                    |                              |                      | 13   | 30                   | ps    |

| T <sub>PD</sub>       | Propagation Delay              |                              |                      |      | 750                  | ps    |

| Tod                   | Valid to HiZ                   |                              |                      |      | 100                  | ns    |

| T <sub>OE</sub>       | HiZ to valid                   |                              |                      |      | 100                  | ns    |

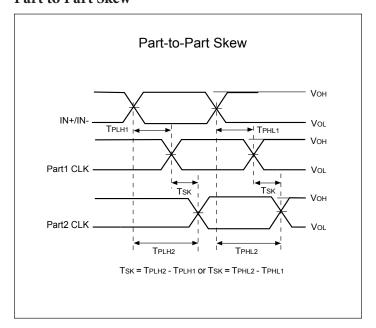

| T <sub>P2P Skew</sub> | Part to Part Skew <sup>1</sup> |                              | -50                  |      | 50                   | ps    |

| $V_{REF\_AC}$         | Input bias voltage             | $I_{AC} = 2mA$               | V <sub>DD</sub> -1.6 |      | V <sub>DD</sub> -1.1 | V     |

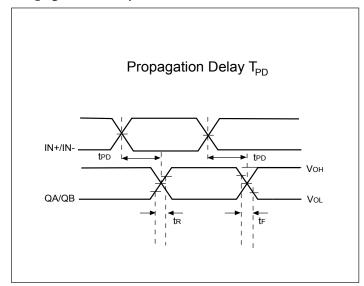

### **Propagation Delay**

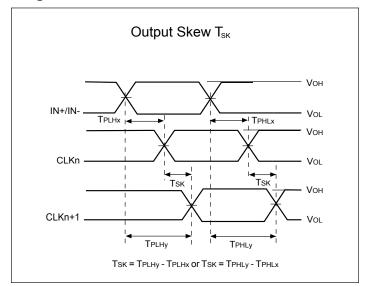

### **Output Skew**

#### Part to Part Skew

## LVPECL Output Swing vs. Frequency

### **Phase Noise and Additive Jitter**

Output phase noise (Dark Blue) vs Input Phase noise (light blue) Additive jitter =  $\sqrt{\text{(Output jitter}^2 - Input jitter}^2)}$

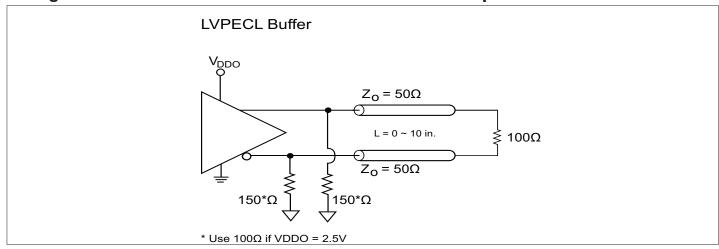

### **Configuration Test Load Board Termination for LVPECL Outputs**

### **Application Information**

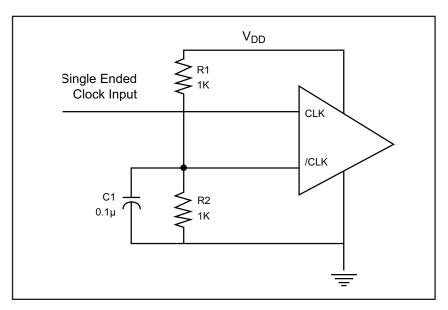

#### Wiring the differential input to accept single ended levels

Figure 1 shows how the differential input can be wired to accept single ended levels. The reference voltage  $V_REF = V_{DD}/2$  is generated by the bias resistors R1, R2 and C1. This bias circuit should be located as close as possible to the input pin. The ratio of R1 and R2 might need to be adjusted to postion the  $V_REF$  in the center of the input voltage swing. For example, if the input clock swing is only 2.5V and  $V_{DD} = 3.3$ V,  $V_REF$  should be 1.25V and R1/R2 = 0.609.

Figure 1. Single-ended input to Differential input device

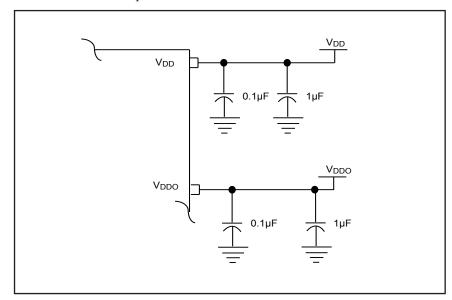

### **Power Supply Filtering Techniques**

As in any high speed analog circuitry, the power supply pins are vulnerable to random noise. To achieve optimum jitter performance, power supply isolation is required. All power pins should be individually connected to the power supply plane through vias, and  $0.1\mu F$  an  $1\mu F$  bypass capacitors should be used for each pin.

### **Thermal Information**

| Symbol           | Description                            | Condition |           |

|------------------|----------------------------------------|-----------|-----------|

| $\Theta_{ m JA}$ | Junction-to-ambient thermal resistance | Still air | 56.6 °C/W |

| $\Theta_{ m JC}$ | Junction-to-case thermal resistance    |           | 12.8 °C/W |

## **Part Marking**

FA Package

Top mark not available at this time. To obtain advance information regarding the top mark, please contact your local sales representative.

Downloaded From Oneyac.com

### Packaging Mechanical: 48-TQFP (FA)

06-0182

#### For latest package info.

please check: http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/

### **Ordering Information**

| Ordering Code       | Package Code | Package Type                          | Operating Temperature |

|---------------------|--------------|---------------------------------------|-----------------------|

| PI6C5912016-01FAIEX | FA           | 48-pin, Thin Quad Flat Package (TQFP) | -40 °C to 85 °C       |

#### Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

- 2. See http://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free. Thermal characteristics can be found on the company web site at www.diodes.com/design/support/packaging/

- 3. E = Pb-free and Green

- 4. X suffix = Tape/Reel

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2016, Diodes Incorporated

www.diodes.com

# 单击下面可查看定价,库存,交付和生命周期等信息

>>Diodes Incorporated(达迩科技(美台))