A Product Line of Diodes Incorporated

#### Low-Voltage Translating 16-Bit I2C-Bus I/O Expander

## Description

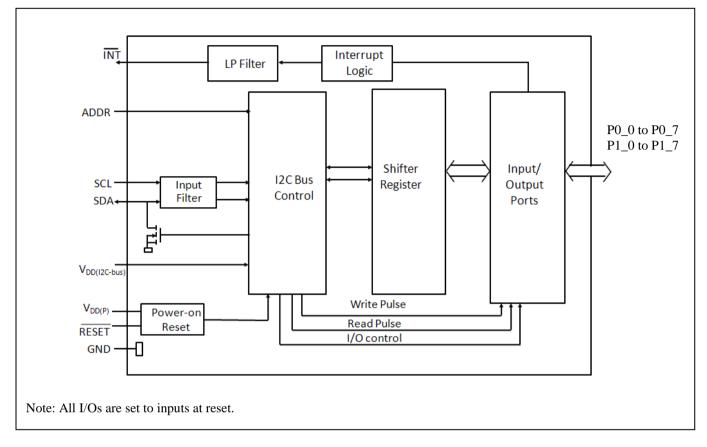

The PI4IOE5V6416AQ is a 16-bit general-purpose I/O expander that provides remote I/O expansion for most microcontroller families via the  $I^2$ C-bus interface.

The device provides a simple solution when additional I/Os are needed while keeping interconnections to a minimum; such as in sensors, push buttons, keypads, and battery-powered mobile applications for interfacing.

The PI4IOE5V6416AQ can operate from 1.65V to 5.5V on the GPIO-port side and 1.65V to 5.5V on the SDA/SCL side. This allows the PI4IOE5V6416AQ to interface with nextgeneration microprocessors and microcontrollers on the SDA/SCL side, where supply levels are dropping down to conserve power.

The bidirectional voltage-level translation in the PI4IOE5V6416AQ is provided through  $V_{DD(I2C\_bus)}$ .  $V_{DD(I2C\_bus)}$  should be connected to the  $V_{DD}$  of the external SCL/SDA lines. The voltage level on the GPIO-port of the PI4IOE5V6416AQ is determined by  $V_{DD(P)}$ .

At power on, the I/Os are configured as inputs; however, the system master can enable the I/Os as either inputs or outputs by writing to the I/O direction bits. The data for each input or output is kept in the corresponding Input or Output register. All registers can be read by the system master.

The PI4IOE5V6416AQ has an open-drain interrupt  $(\overline{INT})$  output pin that goes LOW when the input state of a GPIOport changes from the input-state default register value. The device also has an interrupt masking feature by which the user can mask the interrupt from an individual GPIO-port.

## Features

- → Operation power supply voltage from 1.65V to 5.5V

- → Allows bidirectional voltage-level translation and GPIO expansion between:

- 1.8/2.5/3.3/5V SCL/SDA and 1.8/2.5/3.3/5V Port

- → Low standby current consumption:

- 1.5 $\mu$ A typical at 5V V<sub>DD</sub>

- 1 $\mu$ A typical at 3.3V V<sub>DD</sub>

- → 400kHz I<sup>2</sup>C-bus interface

- → Compliant with the I<sup>2</sup>C-bus fast and standard modes

- → Programmable push-pull/open-drain output stages

- ➔ Programmable output drive strength and pull-up/down resistor

- → Power-on reset

- → Active LOW open-drain interrupt output

- ➔ Active LOW reset input

- → Latch-up tested (exceeds 100mA)

- → Support AEC-Q100 (Grade 2)

- → Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- → Halogen and Antimony Free. "Green" Device (Note 3)

- → The PI4IOE5V6416AQ is suitable for automotive applications requiring specific change control; the part is AEC-Q100 qualified, PPAP capable, and manufactured in IATF 16949certified facilities.

https://www.diodes.com/quality/product-definitions

- ➔ Packaging (Pb-free & Green):

- 24-Pin TSSOP (L)

Notes: 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.</li>

# **Pin Configuration**

| INT 1          | 0 | 24 VDD(P) |

|----------------|---|-----------|

| VDD(I2C-bus) 2 |   | 23 SDA    |

| RESET 3        |   | 22 SCL    |

| P0_0 4         |   | 21 ADDR   |

| P0_1 5         |   | 20 P1_7   |

| P0_2 6         |   | 19 P1_6   |

| P0_3 7         |   | 18 P1_5   |

| P0_4 8         |   | 17 P1_4   |

| P0_5 9         |   | 16 P1_3   |

| P0_6 10        |   | 15 P1_2   |

| P0_7 11        |   | 14 P1_1   |

| Vss 12         |   | 13 P1_0   |

|                |   | d.        |

## **Pin Description**

| Pin Name                 | Pin# | Description                                                                                                            |

|--------------------------|------|------------------------------------------------------------------------------------------------------------------------|

| INT                      | 1    | Interrupt output. Connect to $V_{DD(I2C-bus)}$ or $V_{DD(P)}$ through a pull-up resistor.                              |

| V <sub>DD(I2C_bus)</sub> | 2    | Supply voltage of I2C-bus. Connect directly to the VDD of the external I2C master. Provides voltage-level translation. |

| RESET                    | 3    | Active LOW reset input. Connect to $V_{DD(I2C-bus)}$ through a pull-up resistor if no active connection is used.       |

| P0_0                     | 4    | Port 0 input/output 0.                                                                                                 |

| P0_1                     | 5    | Port 0 input/output 1.                                                                                                 |

| P0_2                     | 6    | Port 0 input/output 2.                                                                                                 |

| P0_3                     | 7    | Port 0 input/output 3.                                                                                                 |

| P0_4                     | 8    | Port 0 input/output 4.                                                                                                 |

| P0_5                     | 9    | Port 0 input/output 5.                                                                                                 |

| P0_6                     | 10   | Port 0 input/output 6.                                                                                                 |

| P0_7                     | 11   | Port 0 input/output 7.                                                                                                 |

| V <sub>SS</sub>          | 12   | Ground                                                                                                                 |

| P1_0                     | 13   | Port 1 input/output 0.                                                                                                 |

| P1_1                     | 14   | Port 1 input/output 1.                                                                                                 |

| P1_2                     | 15   | Port 1 input/output 2.                                                                                                 |

| P1_3                     | 16   | Port 1 input/output 3.                                                                                                 |

| P1_4                     | 17   | Port 1 input/output 4.                                                                                                 |

| P1_5                     | 18   | Port 1 input/output 5.                                                                                                 |

| P1_6                     | 19   | Port 1 input/output 6.                                                                                                 |

| P1_7                     | 20   | Port 1 input/output 7.                                                                                                 |

| ADDR                     | 21   | Address input. Connect directly to V <sub>DD(P)</sub> or ground.                                                       |

| SCL                      | 22   | Serial clock bus. Connect to V <sub>DD(12C-bus)</sub> through a pull-up resistor.                                      |

| SDA                      | 23   | Serial data bus. Connect to V <sub>DD(I2C-bus)</sub> through a pull-up resistor.                                       |

| V <sub>DD(P)</sub>       | 24   | Supply voltage of PI4IOE5V6416AQ for Port P.                                                                           |

## **Maximum Ratings**

| Power supply                           | 0.5V to +6.0V |

|----------------------------------------|---------------|

| Voltage on an I/O pin (Input / Output) | 0.5V to +6.0V |

| Input current                          | ±20mA         |

| Output current on an I/O pin           | ±50mA         |

| Supply current through VDD (P)         |               |

| Ground supply current                  | 200mA         |

| Operation temperature                  | 40~105°C      |

| Storage temperature                    |               |

| Maximum Junction Temperature, Tj (max) |               |

| ESD (HBM)                              | 2kV           |

|                                        |               |

Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **Recommended Operating Conditions**

| Symbol                   | Parameter                              | Conditions | Min. | Тур. | Max.               | Unit |

|--------------------------|----------------------------------------|------------|------|------|--------------------|------|

| V <sub>DD(12C-bus)</sub> | I <sup>2</sup> C-bus supply voltage    | -          | 1.65 | -    | 5.5                | v    |

| V <sub>DD(P)</sub>       | GPIO port supply voltage               | -          | 1.65 | -    | 5.5                | V    |

| V <sub>IN</sub>          | Input voltage on ADDR,<br>P1_7 to P0_0 | -          | 0    | -    | V <sub>DD(P)</sub> | V    |

|                          | Input voltage on SCL, SDA,<br>RESET    | -          | 0    | -    | $V_{DD(I2C\_BUS)}$ | V    |

| I <sub>OH</sub>          | High-Level Output Current              | -          | -    | -    | 10                 | mA   |

| I <sub>OL</sub>          | Low-Level Output Current               | -          | -    | -    | 25                 | mA   |

A Product Line of Diodes Incorporated

## **Static Characteristics**

| V |               | 1 65 V to 5 5 | V· Temp = $-40$               | $^{\circ}$ C to +105 $^{\circ}$ C | unless of | nerwise specified.  | Typical  | values are at T | lemp = 25                   | °C |

|---|---------------|---------------|-------------------------------|-----------------------------------|-----------|---------------------|----------|-----------------|-----------------------------|----|

| • | DD(12C_bus) — | 1.05 1 10 5.5 | $\mathbf{v}$ , remp = $\pm 0$ | C to $+105$ C,                    | unicss ou | iei wise specificu. | i ypicai | values are at 1 | $i \operatorname{cmp} = 25$ | С. |

|   |               |               |                               |                                   |           |                     |          |                 |                             |    |

| Symbol              | Parameter                            | Condi                                                      | tion                          | Min.                                            | Тур. | Max.                            | Unit |

|---------------------|--------------------------------------|------------------------------------------------------------|-------------------------------|-------------------------------------------------|------|---------------------------------|------|

| Power su            | pply                                 |                                                            |                               |                                                 |      |                                 |      |

|                     |                                      |                                                            | V <sub>DD(P)</sub> =3.6-5.5V  |                                                 | 1.5  | 7                               |      |

|                     |                                      | Standby mode I/O =<br>inputs; f <sub>SCL</sub> = 0 kHz     | V <sub>DD(P)</sub> =2.3-3.6V  | ] - [                                           | 1    | 3.2                             |      |

|                     |                                      | inputs, isci – o kitz                                      | V <sub>DD(P)</sub> =1.65-2.3V |                                                 | 0.5  | 10                              |      |

|                     |                                      |                                                            | V <sub>DD(P)</sub> =3.6-5.5V  |                                                 | 10   | 25                              |      |

| I <sub>DD</sub>     | Supply current                       | Standby mode I/O =<br>inputs; f <sub>SCL</sub> = 400 kHz   | V <sub>DD(P)</sub> =2.3-3.6V  | ] - [                                           | 6.5  | 15                              | μΑ   |

|                     |                                      |                                                            | V <sub>DD(P)</sub> =1.65-2.3V |                                                 | 4    | 9                               |      |

|                     |                                      | Active mode I/O =                                          | V <sub>DD(P)</sub> =3.6-5.5V  |                                                 | 60   | 125                             |      |

|                     |                                      | inputs; $f_{SCL} = 400 \text{ kHz}$ ,                      | V <sub>DD(P)</sub> =2.3-3.6V  | -                                               | 40   | 75                              |      |

|                     |                                      | continuous register read                                   | V <sub>DD(P)</sub> =1.65-2.3V |                                                 | 20   | 45                              |      |

| $I_{\rm off}$       | Power off leakage current<br>at GPIO | $V_{DD(I2C\_BUS)} = 0V, V_{I}$<br>0V to 5.5V               | -                             | -                                               | 100  | nA                              |      |

| V <sub>POR</sub>    | Power-on reset voltage               | Rising                                                     |                               | -                                               | 1.1- | 1.4                             | v    |

| V POR               | rower-on reset voltage               | Falling                                                    |                               | 0.5                                             | -    | -                               | v    |

| T <sub>d(rst)</sub> | Reset time                           | Time of V <sub>DD(P)</sub> drop to successful Power-on res |                               | 1                                               | -    | -                               | μs   |

| Input SC            | L, input/output SDA                  |                                                            |                               |                                                 |      |                                 |      |

| $V_{I\!L}$          | Low level input voltage              | -                                                          |                               | -0.5                                            | -    | 0.3<br>V <sub>DD(I2C-bus)</sub> | V    |

| V <sub>IH</sub>     | High level input voltage             | -                                                          |                               | 0.7<br>V <sub>DD(I2C-bus)</sub>                 | -    | 5.5                             | V    |

| I <sub>OL</sub>     | SDA Low level output current         | V <sub>OL</sub> =0.4 V                                     |                               | 3                                               | -    | -                               | mA   |

| IL                  | Leakage current                      | $V_{IN} = V_{DD(I2C\_bus)}$ or V                           | SS                            | -1                                              | -    | 1                               | μΑ   |

| Ci                  | Input capacitance                    | $V_{IN} = V_{SS}$                                          |                               | -                                               | 7    | 8                               | pF   |

| Interrupt           | INT                                  |                                                            |                               |                                                 |      | · · ·                           |      |

| I <sub>OL</sub>     | Low level output current             | $V_{OL}=0.4V$                                              |                               | 3                                               | -    | -                               | mA   |

| Co                  | Output capacitance                   | -                                                          |                               | -                                               | 7    | 8                               | pF   |

| Select inp          | outs ADDR and <b>RESET</b>           |                                                            |                               |                                                 |      |                                 |      |

|                     | RESET Low level input voltage        | -                                                          |                               | -0.5                                            | -    | 0.3<br>V <sub>DD(I2C-bus)</sub> |      |

| V <sub>IL</sub>     | ADDR Low level input<br>voltage      | -                                                          |                               | -0.5                                            | -    | 0.3<br>V <sub>DD(P)</sub>       | V    |

|                     | RESET High level input<br>voltage    | -                                                          |                               | 0.7<br>V <sub>DD(I2C-bus)</sub>                 | -    | 5.5                             |      |

| $V_{IH}$            | ADDR High level input<br>voltage     | -                                                          |                               | $\begin{array}{c} 0.7 \\ V_{DD(P)} \end{array}$ | -    | 5.5                             | V    |

| IL                  | Input leakage current                | -                                                          |                               | -1                                              | -    | 1                               | μΑ   |

| Ci                  | Input capacitance                    | -                                                          |                               | -                                               | 6    | 7                               | pF   |

A Product Line of Diodes Incorporated

PI4IOE5V6416AQ

| Symbol               | Parameter                     | Condition                                                                                                                                                                         | Min.                   | Тур. | Max.             | Unit |

|----------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------------------|------|

| I/Os                 |                               |                                                                                                                                                                                   | · · ·                  |      | · · · ·          |      |

| V <sub>IL</sub>      | Low-level input voltage       | P0 – P7                                                                                                                                                                           | -0.5                   | -    | $+0.3*V_{DD(P)}$ | V    |

| VIH                  | High-level input voltage      | P0 – P7                                                                                                                                                                           | 0.7*V <sub>DD(P)</sub> | -    | 5.5              | V    |

| V                    | High-level output voltage     | $I_{OH} = -2.5mA; CCX.X=00b$<br>$I_{OH} = -5mA; CCX.X=01b$<br>$I_{OH} = -7.5mA; CCX.X=10b$<br>$I_{OH} = -10mA; CCX.X=11b$                                                         | -                      | -    | -                |      |

| V <sub>OH</sub>      |                               | $V_{DD(P)} = 1.65 V$                                                                                                                                                              | 1.1                    | -    | -                |      |

|                      |                               | $V_{DD(P)} = 2.3 V$                                                                                                                                                               | 1.7                    | -    | -                | v    |

|                      |                               | $V_{DD(P)} = 3 V$                                                                                                                                                                 | 2.5                    |      |                  | v    |

|                      |                               | $V_{DD(P)} = 4.5 V$                                                                                                                                                               | 4.0 -                  |      | -                |      |

|                      |                               | $I_{OL} = 2.5 \text{mA}; \text{CCX.X}=00b$<br>$I_{OL} = 5 \text{mA}; \text{CCX.X}=01b$<br>$I_{OL} = 7.5 \text{mA}; \text{CCX.X}=10b$<br>$I_{OL} = 10 \text{mA}; \text{CCX.X}=11b$ | -                      | -    | -                |      |

| V <sub>OL</sub>      | Low-level output voltage      | V <sub>DD(P)</sub> = 1.65 V                                                                                                                                                       | -                      | -    | 0.5              |      |

|                      |                               | $V_{DD(P)} = 2.3 V$                                                                                                                                                               | -                      | -    | 0.3              | v    |

|                      |                               | $V_{DD(P)} = 3 V$                                                                                                                                                                 | -                      | -    | 0.25             | v    |

|                      |                               | $V_{DD(P)} = 4.5 V$                                                                                                                                                               | -                      | -    | 0.2              |      |

| I <sub>IH</sub>      | High-level input current      | P port; $V_I = V_{DD(P)}$                                                                                                                                                         | -                      | -    | 1                | μΑ   |

| I <sub>IL</sub>      | Low-level input current       | P port; $V_I = V_{SS}$                                                                                                                                                            | -                      | -    | 1                | μΑ   |

| R <sub>pu(int)</sub> | Internal pull-up resistance   | Input/Output                                                                                                                                                                      | 50                     | 100  | 150              | kΩ   |

| R <sub>pd(int)</sub> | Internal pull-down resistance | Input/Output                                                                                                                                                                      | 50                     | 100  | 150              | kΩ   |

PI4IOE5V6416AQ

# **Dynamic Characteristics**

| a l l                       | <b>D</b> (                                                        | Standard | l mode I <sup>2</sup> C | Fast mo                | de I <sup>2</sup> C | <b>T</b> T •4 |

|-----------------------------|-------------------------------------------------------------------|----------|-------------------------|------------------------|---------------------|---------------|

| Symbol                      | Parameter                                                         | Min      | Max                     | Min                    | Max                 | Unit          |

| $\mathbf{f}_{\mathrm{SCL}}$ | SCL clock frequency                                               | 0        | 100                     | 0                      | 400                 | kHz           |

| t <sub>BUF</sub>            | Bus free time between a STOP and START condition                  | 4.7      | -                       | 1.3                    | -                   | μs            |

| t <sub>HD;STA</sub>         | Hold time (repeated) START condition                              | 4.0      | -                       | 0.6                    | -                   | μs            |

| t <sub>SU;STA</sub>         | Set-up time for a repeated START condition                        | 4.7      | -                       | 0.6                    | -                   | μs            |

| t <sub>SU;STO</sub>         | Set-up time for STOP condition                                    | 4.0      | -                       | 0.6                    | -                   | μs            |

| t <sub>VD;ACK</sub>         | Data valid acknowledge time                                       | -        | 3.45                    | -                      | 0.9                 | μs            |

| t <sub>HD;DAT</sub>         | Data hold time                                                    | 0        | -                       | 0                      | -                   | ns            |

| t <sub>VD;DAT</sub>         | Data valid time                                                   | -        | 3.45                    | -                      | 0.9                 | ns            |

| t <sub>SU;DAT</sub>         | Data set-up time                                                  | 250      | -                       | 100                    | -                   | ns            |

| t <sub>LOW</sub>            | LOW period of the SCL clock                                       | 4.7      | -                       | 1.3                    | -                   | μs            |

| t <sub>HIGH</sub>           | HIGH period of the SCL clock                                      | 4.0      | -                       | 0.6                    | -                   | μs            |

| t <sub>f</sub>              | Fall time of both SDA and SCL signals                             | -        | 300                     | 20 x<br>(VDD/5.<br>5V) | 300                 | ns            |

| t <sub>r</sub>              | Rise time of both SDA and SCL signals                             | -        | 1000                    | 20                     | 300                 | ns            |

| t <sub>SP</sub>             | Pulse width of spikes that must be suppressed by the input filter | 0        | 50                      | 0                      | 50                  | ns            |

| Interrupt                   | timing                                                            |          |                         |                        |                     |               |

| $t_{V(INT)}$                | Valid time on pin INT                                             | -        | 1                       | -                      | 1                   | μs            |

| t <sub>RST(INT)</sub>       | Reset time on pin INT                                             | -        | 1                       | -                      | 1                   | μs            |

| Reset time                  | ing                                                               |          |                         |                        |                     |               |

| t <sub>w(rst)</sub>         | Reset pulse width                                                 | 30       | -                       | 30                     | -                   | ns            |

| t <sub>rst_rec</sub>        | Reset recovery time                                               | 200      | -                       | 200                    | -                   | ns            |

| t <sub>rst</sub>            | Reset time                                                        | 600      | -                       | 600                    | -                   | ns            |

| P Port tin                  | ning                                                              |          |                         |                        |                     |               |

| $t_{V(Q)}$                  | Data output valid time (from SCL to P Port)                       | -        | 400                     | -                      | 400                 | ns            |

| t <sub>SU(D)</sub>          | Data input setup time (from P Port to SCL)                        | 0        | -                       | 0                      | -                   | ns            |

| t <sub>h(D)</sub>           | Data input hold time (from P Port to SCL)                         | 300      | -                       | 300                    | -                   | ns            |

## **Block Diagram**

## **Functional Description**

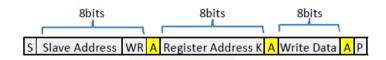

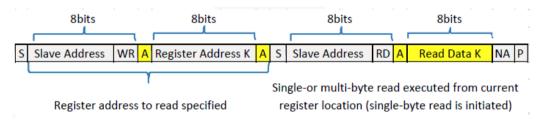

### I<sup>2</sup>C Read /Write Procedures

Figure 1 and Figure 2 illustrate compatible I<sup>2</sup>C write and read sequences.

#### Figure 1. I<sup>2</sup>C Write Sequence

Note : if register is not specified , the master reads from the current register

#### Figure 2. I<sup>2</sup>C Read Sequence

### a. Slave Address

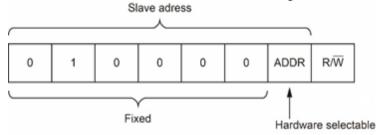

The address of the PI4IOE5V6416AQ is shown in Figure 3.

#### Figure 3. PI4IOE5V6416AQ Address

ADDR is the hardware address package pin and is held to either HIGH (logic 1) or LOW (logic 0) to assign one of the two possible slave addresses. The last bit of the slave address  $(\overline{R/W})$  defines the operation (read or write) to be performed. A HIGH (logic 1) selects a read operation, while a LOW (logic 0) selects a write operation.

### **b.** Register Address

Following the successful acknowledgement of the address byte, the bus master sends a register address, which is stored in the Pointer register in the PI4IOE5V6416AQ. The data byte state the operation (read or write) and the internal registers (Input, Output, Polarity Inversion, Configuration, or the extended features of the device). This register is write only.

A Product Line of Diodes Incorporated

#### **Table 1: Interface Definition**

|           |           | Regis | ster A    | ddres     | s Bits    |           |           |                                           |                                                |                  |

|-----------|-----------|-------|-----------|-----------|-----------|-----------|-----------|-------------------------------------------|------------------------------------------------|------------------|

| <b>B7</b> | <b>B6</b> | B5    | <b>B4</b> | <b>B3</b> | <b>B2</b> | <b>B1</b> | <b>B0</b> | Register                                  | Protocol                                       | Power-up default |

| 0         | 0         | 0     | 0         | 0         | 0         | 0         | 0         | Input port 0                              | read byte                                      | XXXX XXXX        |

| 0         | 0         | 0     | 0         | 0         | 0         | 0         | 1         | Input port 1                              | read byte                                      | XXXX XXXX        |

| 0         | 0         | 0     | 0         | 0         | 0         | 1         | 0         | Output port 0                             | read/write byte                                | 1111 1111        |

| 0         | 0         | 0     | 0         | 0         | 0         | 1         | 1         | Output port 1                             | read/write byte                                | 1111 1111        |

| 0         | 0         | 0     | 0         | 0         | 1         | 0         | 0         | Polarity Inversion port 0                 | read/write byte                                | 0000 0000        |

| 0         | 0         | 0     | 0         | 0         | 1         | 0         | 1         | Polarity Inversion port 1                 | read/write byte                                | 0000 0000        |

| 0         | 0         | 0     | 0         | 0         | 1         | 1         | 0         | Configuration port 0                      | read/write byte                                | 1111 1111        |

| 0         | 0         | 0     | 0         | 0         | 1         | 1         | 1         | Configuration port 1                      | read/write byte                                | 1111 1111        |

| 0         | 1         | 0     | 0         | 0         | 0         | 0         | 0         | Output drive strength register 0          | read/write byte                                | 1111 1111        |

| 0         | 1         | 0     | 0         | 0         | 0         | 0         | 1         | Output drive strength register 0          | read/write byte                                | 1111 1111        |

| 0         | 1         | 0     | 0         | 0         | 0         | 1         | 0         | Output drive strength register 1          | tput drive strength register 1 read/write byte |                  |

| 0         | 1         | 0     | 0         | 0         | 0         | 1         | 1         | Output drive strength register 1          | t drive strength register 1 read/write byte    |                  |

| 0         | 1         | 0     | 0         | 0         | 1         | 0         | 0         | Input latch register 0 read/write byte    |                                                | 0000 0000        |

| 0         | 1         | 0     | 0         | 0         | 1         | 0         | 1         | Input latch register 1                    | read/write byte                                | 0000 0000        |

| 0         | 1         | 0     | 0         | 0         | 1         | 1         | 0         | Pull-up/pull-down enable<br>register 0    | read/write byte                                | 0000 0000        |

| 0         | 1         | 0     | 0         | 0         | 1         | 1         | 1         | Pull-up/pull-down enable<br>register 1    | read/write byte                                | 0000 0000        |

| 0         | 1         | 0     | 0         | 1         | 0         | 0         | 0         | Pull-up/pull-down selection register 0    | read/write byte                                | 1111 1111        |

| 0         | 1         | 0     | 0         | 1         | 0         | 0         | 1         | Pull-up/pull-down<br>selection register 1 | read/write byte                                | 1111 1111        |

| 0         | 1         | 0     | 0         | 1         | 0         | 1         | 0         | Interrupt mask register 0                 | read/write byte                                | 1111 1111        |

| 0         | 1         | 0     | 0         | 1         | 0         | 1         | 1         | Interrupt mask register 1                 |                                                |                  |

| 0         | 1         | 0     | 0         | 1         | 1         | 0         | 0         | Interrupt status register 0               | read byte                                      | 0000 0000        |

| 0         | 1         | 0     | 0         | 1         | 1         | 0         | 1         | Interrupt status register 1               | read byte                                      | 0000 0000        |

| 0         | 1         | 0     | 0         | 1         | 1         | 1         | 1         | Output port configuration register        | read/write byte                                | 0000 0000        |

### c. Register Description

#### i. Input Port Register Pair (00h, 01h)

The Input port registers (registers 0 and 1) reflect the incoming logic levels of the pins, regardless of whether the pin is defined as an input or an output by the Configuration register. The Input port registers are read only; writes to these registers have no effect. The default value 'X' is determined by the externally applied logic level.

#### Table 2. Input port 0 register (address 00h)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Name    | I0.7 | I0.6 | I0.5 | I0.4 | I0.3 | I0.2 | I0.1 | I0.0 |

| Default | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

#### Table 3. Input port 1 register (address 01h)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Name    | I1.7 | I1.6 | I1.5 | I1.4 | I1.3 | I1.2 | I1.1 | I1.0 |

| Default | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

#### ii. Output Port Register Pair (02h, 03h)

The Output port registers (registers 2 and 3) shows the outgoing logic levels of the pins defined as outputs by the Configuration register. Bit values in these registers have no effect on pins defined as inputs. In turn, reads from these registers reflect the value that was written to these registers, not the actual pin value.

#### Table 4. Output port 0 register (address 02h)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Name    | O0.7 | O0.6 | O0.5 | O0.4 | O0.3 | O0.2 | O0.1 | O0.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

#### Table 5. Output port 1 register (address 03h)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Name    | O1.7 | 01.6 | 01.5 | O1.4 | 01.3 | O1.2 | 01.1 | O1.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

#### iii. Polarity Inversion Register Pair (04h, 05h)

The Polarity inversion registers (registers 4 and 5) allow polarity inversion of pins defined as inputs by the Configuration register. If a bit in these registers is set (written with '1'), the corresponding port pin's polarity is inverted in the input register. If a bit in this register is cleared (written with a '0'), the corresponding port pin's polarity is retained

#### Table 6. Polarity inversion port 0 register (address 04h)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Name    | N0.7 | N0.6 | N0.5 | N0.4 | N0.3 | N0.2 | N0.1 | N0.0 |

| Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

### Table 7. Polarity inversion port 1 register (address 05h)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Name    | N1.7 | N1.6 | N1.5 | N1.4 | N1.3 | N1.2 | N1.1 | N1.0 |

| Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

#### iv. Configuration Register Pair (06h, 07h)

The Configuration registers (registers 6 and 7) configure the direction of the I/O pins. If a bit in these registers is set to 1, the corresponding port pin is enabled as a high-impedance input. If a bit in these registers is cleared to 0, the corresponding port pin is enabled as an output.

#### Table 8. Configuration port 0 register (address 06h)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Name    | C0.7 | C0.6 | C0.5 | C0.4 | C0.3 | C0.2 | C0.1 | C0.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

#### Table 9. Configuration port 1 register (address 07h)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Name    | C1.7 | C1.6 | C1.5 | C1.4 | C1.3 | C1.2 | C1.1 | C1.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

#### v. Output Drive Strength Register Pairs (40h, 41h, 42h, 43h)

The Output drive strength registers control of the output drive level of the GPIO. Each GPIO can be configured independently to a certain output current level by two register control bits. For example Port 0.7 is controlled by register 41 CC0.7 (bits [7:6]), Port 0.6 is controlled by register 41 CC0.6 (bits [5:4]). The output drive level of the GPIO is programmed 00b = 0.25, 01b = 0.5, 10b = 0.75 or 11b = 1 of the drive capability of the I/O. See Section 9.2 "Output drive strength control" for more details.

#### Table 10. Current control port 0 register (address 40h)

| Bit     | 7  | 6     | 5 | 4   | 3     | 2 | 1     | 0 |

|---------|----|-------|---|-----|-------|---|-------|---|

| Name    | CC | CC0.3 |   | 0.2 | CC0.1 |   | CC0.0 |   |

| Default | 1  | 1     | 1 | 1   | 1     | 1 | 1     | 1 |

#### Table 11. Current control port 0 register (address 41h)

| Bit     | 7 | 6   | 5  | 4    | 3     | 2 | 1     | 0 |

|---------|---|-----|----|------|-------|---|-------|---|

| Name    |   | 0.7 | CC | 20.6 | CC0.5 |   | CC0.4 |   |

| Default | 1 | 1   | 1  | 1    | 1     | 1 | 1     | 1 |

#### Table 12. Current control port 1 register (address 42h)

| Bit     | 7 | 6   | 5 | 4    | 3  | 2   | 1  | 0   |

|---------|---|-----|---|------|----|-----|----|-----|

| Name    |   | 1.3 |   | 21.2 | CC | 1 1 | CC | 1.0 |

| Default | 1 | 1   | 1 | 1    | 1  | 1   | 1  | 1   |

#### Table 13. Current control port 1 register (address 43h)

| Bit     | 7 | 6    | 5     | 4 | 3     | 2 | 1     | 0 |

|---------|---|------|-------|---|-------|---|-------|---|

| Name    |   | 21.7 | CC1.6 |   | CC1.5 |   | CC1.4 |   |

| Default | 1 | 1    | 1     | 1 | 1     | 1 | 1     | 1 |

#### vi. Input Latch Register Pair (44h, 45h)

The input latch registers (registers 44 and 45) enable and disable the input latch of the I/O pins. These registers are effective only when the pin is configured as an input port. When an input latch register bit is 0, the corresponding input pin state is not latched. A state change in the corresponding input pin generates an interrupt. A read of the input register clears the interrupt. If the input goes back to its initial logic state before the input port register is read, then the interrupt is cleared.

When an input latch register bit is 1, the corresponding input pin state is latched. A change of state of the input generates an interrupt and the input logic value is loaded into the corresponding bit of the input port register (registers 0 and 1). A read of the input port register clears the interrupt. If the input pin returns to its initial logic state before the input port register is read, then the interrupt is not cleared and the corresponding bit of the input port register keeps the logic value that initiated the interrupt.

For example, if the P0\_4 input was as logic 0 and the input goes to logic 1 then back to logic 0, the input port 0 register will capture this change and an interrupt is generated (if unmasked). When the read is performed on the input port 0 register, the interrupt is cleared, assuming there were no additional input(s) that have changed, and bit 4 of the input port 0 register will read '1'. The next read of the input port register bit 4 register should now read '0'.

An interrupt remains active when a non-latched input simultaneously switches state with a latched input and then returns to its original state. A read of the input register reflects only the change of state of the latched input and also clears the interrupt. The interrupt is not cleared if the input latch register changes from latched to non-latched configuration.

If the input pin is changed from latched to non-latched input, a read from the input port register reflects the current port logic level. If the input pin is changed from non-latched to latched input, the read from the input register reflects the latched logic level.

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Name    | L0.7 | L0.6 | L0.5 | L0.4 | L0.3 | L0.2 | L0.1 | L0.0 |

| Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

### Table 14. Input latch port 0 register (address 44h)

#### Table 15. Input latch port 1 register (address 45h)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Name    | L1.7 | L1.6 | L1.5 | L1.4 | L1.3 | L1.2 | L1.1 | L1.0 |

| Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

#### vii. Pull-up/Pull-down Enable Register Pair (46h, 47h)

These registers allow the user to enable or disable pull-up/pull-down resistors on the I/O pins. Setting the bit to logic 1 enables the selection of pull-up/pull-down resistors. Setting the bit to logic 0 disconnects the pull-up/pull-down resistors from the I/O pins. Also, the resistors will be disconnected when the outputs are configured as open-drain outputs. Use the pull-up/pull-down registers to select either a pull-up or pull-down resistor.

PI4IOE5V6416AQ

#### Table 16. Pull-up/pull-down enable port 0 register (address 46h)

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| Name    | PE0.7 | PE0.6 | PE0.5 | PE0.4 | PE0.3 | PE0.2 | PE0.1 | PE0.0 |

| Default | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

#### Table 17. Pull-up/pull-down enable port 1 register (address 47h)

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| Name    | PE1.7 | PE1.6 | PE1.5 | PE1.4 | PE1.3 | PE1.2 | PE1.1 | PE1.0 |

| Default | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

#### viii. Pull-up/pull-down Selection Register Pair (48h, 49h)

The I/O port can be configured to have pull-up or pull-down resistor by programming the pull-up/pull-down selection register. Setting a bit to logic 1 selects a 100 k pull-up resistor for that I/O pin. Setting a bit to logic 0 selects a 100 k pull-down resistor for that I/O pin. If the pull-up/down feature is disconnected, writing to this register will have no effect on I/O pin. Typical value is 100 k with minimum of 50 k and maximum of 150 k.

#### Table 18. Pull-up/pull-down selection port 0 register (address 48h)

| Bit     | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

| Name    | PUD0.7 | PUD0.6 | PUD0.5 | PUD0.4 | PUD0.3 | PUD0.2 | PUD0.1 | PUD0.0 |

| Default | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

#### Table 19. Pull-up/pull-down selection port 1 register (address 49h)

| Bit     | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

| Name    | PUD1.7 | PUD1.6 | PUD1.5 | PUD1.4 | PUD1.3 | PUD1.2 | PUD1.1 | PUD1.0 |

| Default | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

#### ix. Interrupt Mask Register Pair (4Ah, 4Bh)

Interrupt mask registers are set to logic 1 upon power-on, disabling interrupts during system start-up. Interrupts may be enabled by setting corresponding mask bits to logic 0. If an input changes state and the corresponding bit in the Interrupt mask register is set to 1, the interrupt is masked and the interrupt pin will not be asserted. If the corresponding bit in the Interrupt mask register is set to 0, the interrupt pin will be asserted. When an input changes state and the resulting interrupt is masked (interrupt mask bit is 1), setting the input mask register bit to 0 will cause the interrupt pin to be asserted. If the interrupt mask bit of an input that is currently the source of an interrupt is set to 1, the interrupt pin will be de-asserted.

#### Table 20. Interrupt mask port 0 register (address 4Ah) bit description

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Name    | M0.7 | M0.6 | M0.5 | M0.4 | M0.3 | M0.2 | M0.1 | M0.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

#### Table 21. Interrupt mask port 1 register (address 4Bh) bit description

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Name    | M1.7 | M1.6 | M1.5 | M1.4 | M1.3 | M1.2 | M1.1 | M1.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

#### x. Interrupt Status Register Pair (4Ch, 4Dh)

These read-only registers are used to identify the source of an interrupt. When read, a logic 1 indicates that the corresponding input pin was the source of the interrupt. A logic 0 indicates that the input pin is not the source of an interrupt. When a corresponding bit in the interrupt mask register is set to 1 (masked), the interrupt status bit will return logic 0.

#### Table 22. Interrupt status port 0 register (address 4Ch) bit description

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Name    | S0.7 | S0.6 | S0.5 | S0.4 | S0.3 | S0.2 | S0.1 | S0.0 |

| Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

#### Table 23. Interrupt status port 1 register (address 4Dh) bit description

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Name    | S1.7 | S1.6 | S1.5 | S1.4 | S1.3 | S1.2 | S1.1 | S1.0 |

| Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

#### xi. Output Port Configuration Register (4Fh)

The output port configuration register selects port-wise push-pull or open-drain I/O stage. A logic 0 configures the I/O as push-pull. A logic 1 configures the I/O as open-drain and the recommended command sequence is to program this register (4Fh) before the configuration register (06h and 07h) sets the port pins as outputs. ODEN0 configures Port  $0_x$  and ODEN1 configures Port  $1_x$ .

Table 24. Output port configuration register (address 4Fh)

| Bit     | 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0     |

|---------|---|----------|---|---|---|---|---|-------|

| Name    |   | Reserved |   |   |   |   |   | ODEN0 |

| Default | 0 | 0        | 0 | 0 | 0 | 0 | 0 | 0     |

### d. I/O Port

When an I/O is configured as an input, the pull-up FET and pull-down FET are off, which creates a high-impedance input. If the I/O is configured as an output, there are low impedance paths between the I/O pin and either  $V_{DD(P)}$  or  $V_{SS}$  depending on the state of the Output Port Register. The external voltage applied to this I/O pin should not exceed the recommended levels for proper operation. Pull-up/down FETs series with resistors are enabled accordingly to the Pull-up or Pull-down Select Register and the Pull-up or Pull-down Enable Register. When the GPIO-port is set as an output, the input buffers are disabled such that the bus is allowed to float.

#### e. Power-on Reset

When power is applied to  $V_{DD(P)}$ , an internal power-on reset holds the PI4IOE5V6416AQ in a reset condition until  $V_{DD(P)}$  has reached  $V_{POR}$ . At that point, the reset condition is released and the PI4IOE5V6416AQ registers will initialize to their default states.

### f. Reset Input (RESET)

The  $\overline{\text{RESET}}$  input can be asserted to initialize the system while keeping  $V_{DD(P)}$  at its operating level. A reset can be accomplished by holding the  $\overline{\text{RESET}}$  pin low for a minimum of t<sub>W</sub>. The PI4IOE5V6416AQ registers are changed to their default state once RESET is low (0). Only when RESET is high (1), GPIO registers can be accessed by the I<sup>2</sup>C pin. This input requires a pull-up resistor to  $V_{DD(I2C\_bus)}$ , if no active connection is used.

## g. Interrupt Output (INT)

The  $\overline{INT}$  pin is a LOW-asserted open-drain output and requires an external pull-up resistor. The PI4IOE5V6416AQ signals an interrupt to the processor when an event occurs, removing the need for the processor to continuously poll the PI4IOE5V6416AQ registers.

An interrupt is generated by any rising or falling edge of the port inputs in the Input mode. The interrupt is reset when data on the port changes back to the original value or when data is read from the port that generated the interrupt. A pin configured as an output cannot cause an interrupt. If the state of the pin does not match the contents of the Input Port register, changing an I/O from an output to an input may cause a false interrupt to occur. When using the input latch feature, the input pin state is latched. The interrupt is reset only when data is read from the port that generated the interrupt. The reset occurs in the Read mode at the acknowledge (ACK) or not acknowledge (NACK) bit after the rising edge of the SCL signal.

## **Part Marking**

PI4IOE5V 6416AQ2LE YYWWXX

YY: Date Code (Year) WW: Date Code (Workweek) 1st X: Assembly Site Code 2nd X: Wafer Fab Site Code Bar above Fab Code means Cu wire

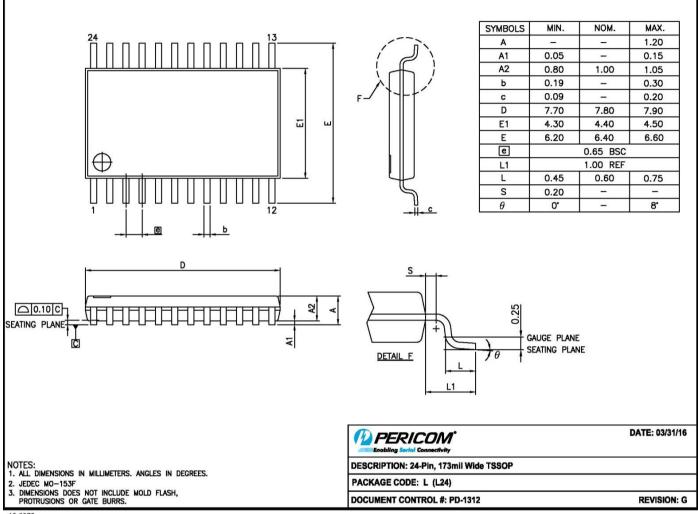

## **Packaging Mechanical**

24-TSSOP (L)

16-0075

#### For latest package info.

please check: http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/

## **Ordering Information**

| Part Number        | Package Code | Package Description         |

|--------------------|--------------|-----------------------------|

| PI4IOE5V6416AQ2LEX | L            | 24-Pin, 173mil Wide (TSSOP) |

#### Notes:

1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

- 4. Q = Automotive Compliant

- 5. 2 = AEC-Q100 Grade level

- E = Pb-free and Green

- 7. X suffix = Tape/Reel

PI4IOE5V6416AQ

#### IMPORTANT NOTICE

1. DIODES INCORPORATED AND ITS SUBSIDIARIES ("DIODES") MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes products. Diodes products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of the Diodes products for their intended applications, (c) ensuring their applications, which incorporate Diodes products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

5. Diodes products are provided subject to Diodes' Standard Terms and Conditions of Sale (https://www.diodes.com/about/company/terms-and-conditions/termsand-conditions-of-sales/) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

6. Diodes products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

Copyright © 2021 Diodes Incorporated

www.diodes.com

单击下面可查看定价,库存,交付和生命周期等信息

>>Diodes Incorporated(达迩科技(美台))