AP3785T

#### PRIMARY SIDE REGULATED SWITCHING MODE POWER SUPPLY CONTROLLER

## **Description**

The AP3785T is a high performance AC/DC power supply controller for battery charger and adapter applications. It can meet less than 10mW standby power for "Super Star" charger criteria. The device uses Pulse Frequency Modulation (PFM) method to build discontinuous conduction mode (DCM) flyback power supplies.

The AP3785T provides accurate constant voltage (CV), constant current (CC) and outstanding dynamic performance without requiring an opto-coupler. It also eliminates the need of loop compensation circuitry while maintaining stability.

The AP3785T is equipped with both cable drop compensation function to meet various cables with different lengths and gauges and adjustable line voltage compensation function.

When AP3785T is used with AP4341 or synchronous rectifier series (for example APR343 + MOSFET, APR3415, APR34330), better under-shoot performance and higher conversion efficiency can be achieved.

The AP3785T has internal over temperature protection for itself, and also provides dedicated pin for external over temperature protection.

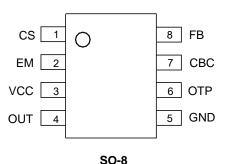

This IC is available in SO-8 package.

## **Applications**

- Adapter/Chargers for Shaver, Cell/Cordless Phones, PDAs, MP3 and Other Portable Apparatus

- Standby and Auxiliary Power Supplies

### **Pin Assignments**

#### (Top View)

#### **Features**

- Primary Side Control for Eliminating Opto-coupler

- 10mW No-load Input Power

- Flyback Topology in DCM Operation

- External Adjustable Line Compensation for CC

- External Adjustable Cable Compensation for CV

- Multiple PWM/PFM Control Mode to Improve Audio Noise and Efficiency

- V<sub>CS</sub> Jitter to Reduce System EMI

- Valley-on for the Higher Efficiency and Better EMI

- Multiple Protections:

- Over Voltage Protection (OVP)

- Output Short Circuit Protection (SCP)

- Transformer Saturation Protection (TSP) via Primary Peak Current Limitation

- OTP and External Over Temperature Protection (OTP)

- Matching AP4341 with Schottky or APR343/APR3415 Synchronous Rectifier Solution

- SO-8 Package

- Totally Lead-free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant.

- See http://www.diodes.com/quality/lead\_free.html for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

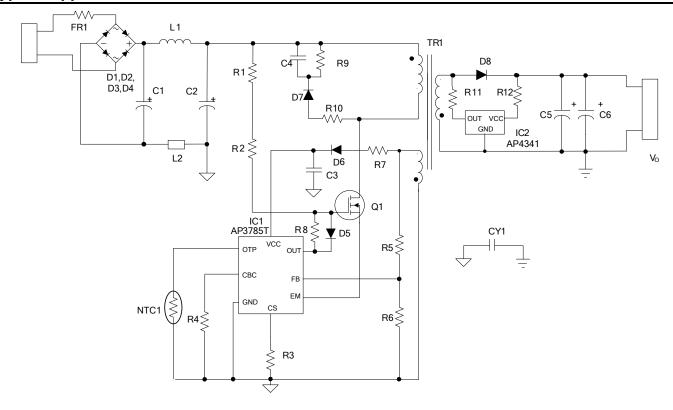

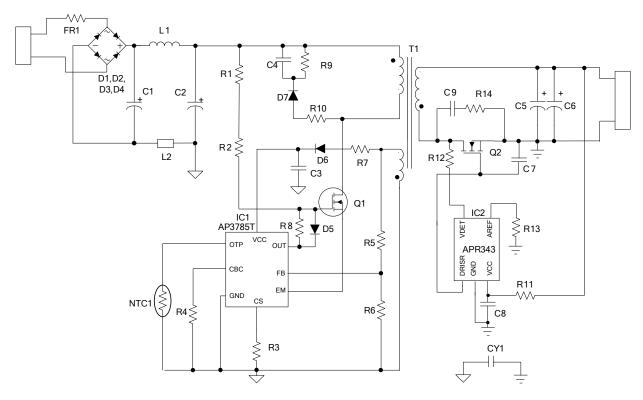

## **Typical Applications Circuit** (Note 4)

With Schottky (Vout=5V/1A or 2A)

With Synchronous Rectifier (Vout=5V/2A)

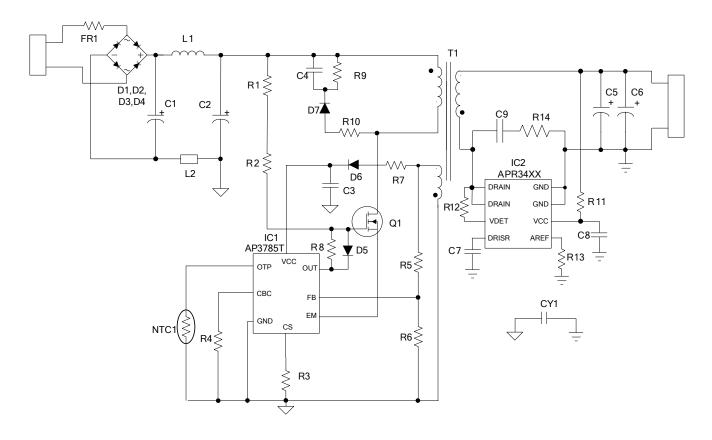

# Typical Applications Circuit (Note 4, Cont.)

With Synchronous Rectifier (i.e. APR34330 for Vour=5V/1.5A, APR3415 for Vour=5V/2A and APR34309 for Vour=5V/3A)

Note 4: If the OTP pin is not connected to the NTC resistor, the external OTP function will not work and the IC can still work normally with internal OTP.

## **Pin Descriptions**

| Pin Number | Pin Name | Function                                                                                                                                                    |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | CS       | Sense primary side current for turning off the external power MOSFET and deliver a voltage proportional to the line voltage for compensation from FB pin    |

| 2          | EM       | Connected to the source of external power MOSFET                                                                                                            |

| 3          | VCC      | The power supply for the IC. In order to get the correct operation of the IC, a capacitor with low ESR should be placed as close as possible to the VCC pin |

| 4          | OUT      | Turn on and turn off the external power MOSFET                                                                                                              |

| 5          | GND      | The ground of the IC                                                                                                                                        |

| 6          | ОТР      | The external over temperature protection                                                                                                                    |

| 7          | CBC      | This pin connects a resistor to GND for output cable voltage drop compensation                                                                              |

| 8          | FB       | Voltage feedback. The CV and CC regulation are realized based on the voltage sampling of this pin                                                           |

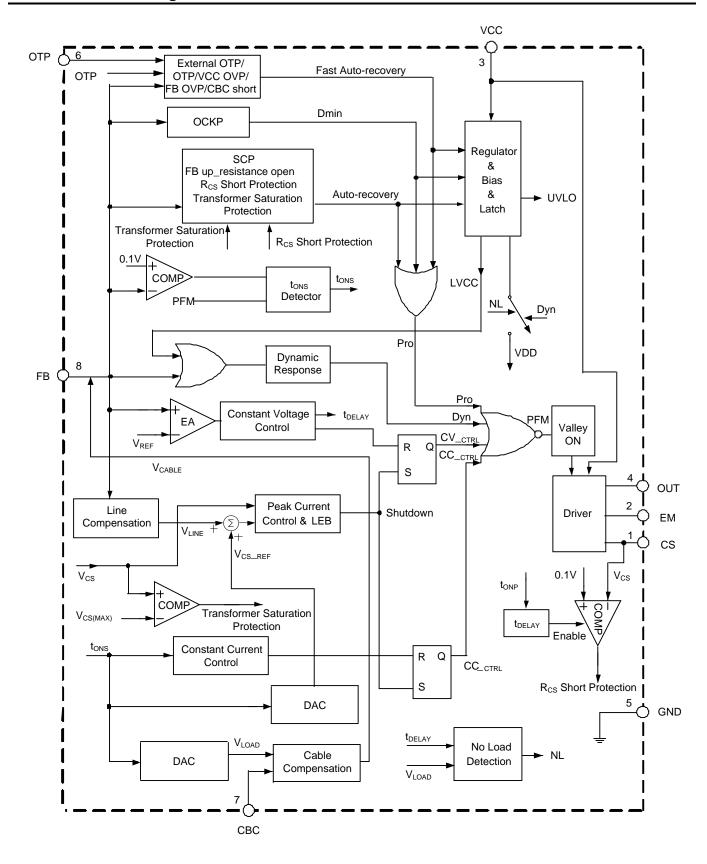

## **Functional Block Diagram**

## **Absolute Maximum Ratings** (Note 5)

| Symbol            | Parameter                                         | Rating      | Unit |

|-------------------|---------------------------------------------------|-------------|------|

| V <sub>cc</sub>   | Voltage at VCC to GND                             | -0.3 to 30  | V    |

| -                 | Voltage at OUT, EM to GND                         | -0.3 to 22  | V    |

| -                 | Voltage at CS, CBC,OTP to GND                     | -0.3 to 7.4 | V    |

| $V_{FB}$          | FB Input Voltage                                  | -0.7 to 7.4 | V    |

| TJ                | Operating Junction Temperature                    | -40 to +150 | °C   |

| T <sub>STG</sub>  | Storage Temperature                               | -65 to +150 | °C   |

| T <sub>LEAD</sub> | Lead Temperature (Soldering, 10 sec)              | +300        | °C   |

| $\theta_{JC}$     | Thermal Resistance (Junction to Case)             | 20          | °C/W |

| $\theta_{JA}$     | Thermal Resistance (Junction to Ambient) (Note 6) | 100         | °C/W |

| -                 | ESD (Human Body Model)                            | 4000        | V    |

| -                 | ESD (Machine Model)                               | 200         | V    |

Notes: 5. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to "Absolute Maximum Ratings" for extended periods may affect device reliability.

6. The device is mounted on FR-4 substrate PCB, 2 oz copper, with 1 inch<sup>2</sup> pad.

## Electrical Characteristics (@Vcc=15V, TA=+25°C, unless otherwise specified.)

| Symbol                   | Parameter                  | Conditions                                             | Min | Тур  | Max | Unit |  |  |

|--------------------------|----------------------------|--------------------------------------------------------|-----|------|-----|------|--|--|

| STARTUP AND              | STARTUP AND UVLO SECTION   |                                                        |     |      |     |      |  |  |

| V <sub>TH_ST</sub>       | Startup Threshold          | -                                                      | 11  | 13   | 15  | V    |  |  |

| V <sub>OPR(MIN)</sub>    | Minimum Operating Voltage  | -                                                      | 5.5 | 5.9  | 6.3 | V    |  |  |

| STANDBY CUR              | STANDBY CURRENT SECTION    |                                                        |     |      |     |      |  |  |

| I <sub>ST</sub>          | Startup Current            | V <sub>CC</sub> =V <sub>TH_ST</sub> -1V before startup | 0   | 0.2  | 0.6 |      |  |  |

| I <sub>CC_NL</sub>       | Standby Current            | At no load                                             | 5   | 17.5 | 30  | μΑ   |  |  |

| I <sub>CC_OPR</sub>      | Operating Current          | Static current                                         | 350 | 450  | 550 |      |  |  |

| DRIVING OUTP             | DRIVING OUTPUT SECTION     |                                                        |     |      |     |      |  |  |

| $V_{GATE}$               | Gate Voltage               | -                                                      | 9   | 10.5 | 12  | V    |  |  |

| I <sub>SOURCE_PEAK</sub> | Peak Driver Source Current | -                                                      | 15  | 20.5 | 26  | mA   |  |  |

| R <sub>DS(ON)</sub>      | Sink Resistance            | -                                                      | 2   | 2.3  | 2.6 | Ω    |  |  |

## **Electrical Characteristics** (Cont.) (@V<sub>CC</sub>=15V, T<sub>A</sub>=+25°C, unless otherwise specified.)

| Symbol                                             | Parameter                                     | Conditions                           | Min  | Тур  | Max  | Unit |  |  |

|----------------------------------------------------|-----------------------------------------------|--------------------------------------|------|------|------|------|--|--|

| OPERATING FREQUENCY SECTION (NL MODE TO FULL LOAD) |                                               |                                      |      |      |      |      |  |  |

| f <sub>S(MAX)</sub>                                | The Maximum Operating Frequency               | 100% full load                       | _    | _    | 80   | kHz  |  |  |

| t <sub>sample_H</sub>                              |                                               | 40% to 100% full load                | 4.8  | 5.2  | 5.7  | μS   |  |  |

| t <sub>sample_L</sub>                              | Sample Time                                   | NL Mode to 8% full load              | 2.4  | 2.7  | 3.0  | μS   |  |  |

| OPERATING FI                                       | REQUENCY SECTION (NL MODE)                    | L                                    | l .  | l .  |      |      |  |  |

| V <sub>CBC(EN)</sub>                               | CBC Pin Voltage to Enter NL Mode              | -                                    | 55   | 60   | 65   | mV   |  |  |

| t <sub>OFF(EN)</sub>                               | Off Time to Enter NL Mode                     | From the end of t <sub>ONS</sub>     | 168  | 224  | 280  | μS   |  |  |

| t <sub>OFF(EX)</sub>                               | Off Time to Exit NL Mode                      | From the end of t <sub>ONS</sub>     | 168  | 224  | 280  | μS   |  |  |

| FREQUENCY J                                        | ITTER                                         | 1                                    | •    |      | •    |      |  |  |

| $\Delta V_{CS}/V_{CS}$                             | V <sub>CS</sub> Modulation                    |                                      | 4.5  | 5    | 5.5  | %    |  |  |

| f <sub>MOD</sub>                                   | V <sub>CS</sub> Modulation Frequency          | NL to full load                      | 1.8  | 2    | 2.2  | kHz  |  |  |

| CURRENT SEN                                        | ISE SECTION                                   | L                                    | l .  | l .  |      |      |  |  |

| V <sub>CS_H</sub>                                  | Peak Current Sense Threshold                  | 40% to 100% full load                | 537  | 565  | 593  | mV   |  |  |

| V <sub>CS_L</sub>                                  | Voltage                                       | 0% to 8% full load                   | 243  | 255  | 267  | mV   |  |  |

| R <sub>LINE</sub>                                  | Built-in Line Compensation Resistor           | (Note 8)                             | 108  | 120  | 132  | Ω    |  |  |

| t <sub>LEB</sub>                                   | Leading Edge Blanking                         | -                                    | 400  | 625  | 850  | ns   |  |  |

| CONSTANT VC                                        | DLTAGE SECTION                                |                                      | l    | l    | l    |      |  |  |

| $V_{FB}$                                           | Feedback Threshold Voltage                    | Closed loop test of V <sub>OUT</sub> | 2.45 | 2.50 | 2.55 | V    |  |  |

| V <sub>CBC(MAX)</sub>                              | Maximum CBC Voltage for Cable Compensation    | -                                    | 1.4  | 1.45 | 1.5  | V    |  |  |

| CONSTANT CU                                        | IRRENT SECTION                                | L                                    | l .  | l .  |      |      |  |  |

| t <sub>ONS</sub> /t <sub>SW</sub>                  | Secondary Winding Conduction Duty             | Tested @ V <sub>FB</sub> =2V         | _    | 4/8  | _    | _    |  |  |

| VALLEY-ON SE                                       | ,                                             |                                      | l    | l    |      |      |  |  |

| t <sub>VAL-ON</sub>                                | Valid Off Time of Valley-on                   | From the end of t <sub>ONS</sub>     | 20   | 27   | 34   | μS   |  |  |

| DYNAMIC SEC                                        | TION                                          |                                      | I    | I    |      |      |  |  |

| V <sub>TRIGGER</sub>                               | Trigger Voltage for Dynamic Function          | _                                    | 40   | 62.5 | 85   | mV   |  |  |

| t <sub>DELAY</sub>                                 | Delay Time for Dynamic Function               | From the end of t <sub>ONS</sub>     | 99   | 127  | 155  | μS   |  |  |

| $V_{UV_{H}}$                                       | Under Voltage of FB Pin for V <sub>CS_H</sub> | -                                    | 2.23 | 2.27 | 2.32 | V    |  |  |

|                                                    | PROTECTION FUNCTION                           |                                      |      |      |      |      |  |  |

| V <sub>FB(OVP)</sub>                               | Over Voltage Protection at FB Pin             | -                                    | 3.5  | 3.75 | 4    | V    |  |  |

| V <sub>CC(OVP)</sub>                               | Over Voltage Protection at VCC Pin            | -                                    | 27   | 28.5 | 30   | V    |  |  |

| t <sub>ONP(MAX)</sub>                              | Maximum Turn-on Time                          | -                                    | 14   | 18   | 22   | μS   |  |  |

| t <sub>OFF(MAX)</sub>                              | Maximum Off Time                              | -                                    | 11   | 14   | 17   | ms   |  |  |

# **Electrical Characteristics** (Cont.) (@V<sub>CC</sub>=15V, T<sub>A</sub>=+25°C, unless otherwise specified.)

| Symbol                | Parameter                                                   | Conditions               | Min  | Тур  | Max  | Unit |

|-----------------------|-------------------------------------------------------------|--------------------------|------|------|------|------|

| V <sub>CS(MIN)</sub>  | Minimum Peak Current Sense Voltage at t <sub>ONP(MAX)</sub> | -                        | 135  | 150  | 165  | mV   |

| $V_{\text{EM(MAX)}}$  | Maximum EM Voltage for Transformer Saturation Protection    | (Note 7)                 | 1.8  | 2    | 2.2  | V    |

| $V_{FB(SCP)}$         | Short Circuit Protection                                    | V <sub>FB</sub> @ Hiccup | 1.57 | 1.61 | 1.65 | V    |

| t <sub>SCP(MIN)</sub> | Minimum Typical Time under V <sub>FB(SCP)</sub>             | -                        | 32   | 43   | 54   | ms   |

| t <sub>SCP(MAX)</sub> | Maximum Typical Time under V <sub>FB(SCP)</sub>             | -                        | 43   | 57   | 71   | ms   |

| V <sub>OTP</sub>      | External OTP Shutdown Threshold                             | -                        | 0.49 | 0.52 | 0.55 | V    |

| V <sub>OTP_REC</sub>  | External OTP Recovery Threshold                             | -                        | 0.99 | 1.05 | 1.11 | V    |

| I <sub>OTP</sub>      | External OTP Shutdown Current                               | -                        | 94   | 102  | 110  | μA   |

| T <sub>OTP</sub>      | Shutdown Temperature                                        | -                        | +125 | +135 | +145 | °C   |

| T <sub>HYS</sub>      | Temperature Hysteresis                                      | -                        | +37  | +40  | +43  | °C   |

Notes: 7. These parameters are not 100% tested, guaranteed by design and characterization.

8. Line compensation voltage on CS reference:  $\Delta V_{CS\_REF} = 0.35 \times \frac{R_{LINE}}{R_{FB1} + R_{LINE}} \times V_{AUX}$

## **Operation Principle Description**

### 1. Start-up Circuit

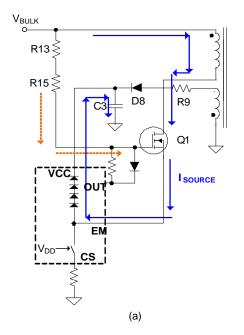

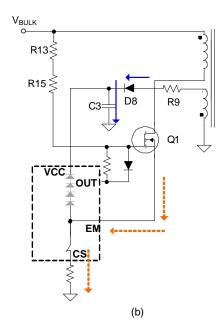

Figure 1. Start-up Circuit

### Figure 1 (a) shows the Startup Phase

- Before V<sub>CC</sub> reaches V<sub>TH(ST)</sub>, V<sub>DD</sub> is zero and EM to CS pin is open.

- C3 is charged by I<sub>SOURCE</sub>.

- The resistance of R13 and R15 should be high enough to reduce the power dissipation.

Figure 1 (b) shows the Normal Operation Phase

- When V<sub>CC</sub> reaches V<sub>TH(ST)</sub>, V<sub>DD</sub> is high and EM to CS pin is short.

- The voltage of EM pin is lower than 1V so that the four diodes in chip are open.

- C3 is supplied by Aux. winding of transformer.

#### 2. Operation Mode

The typical application circuit of AP3785T is a conventional Flyback converter with a 3-winding transformer---primary winding ( $N_P$ ), secondary winding ( $N_S$ ) and auxiliary winding ( $N_{AUX}$ ), as shown in typical application with AP4341. The auxiliary winding is used for providing VCC supply voltage for IC and sensing the output voltage feedback signal to FB pin.

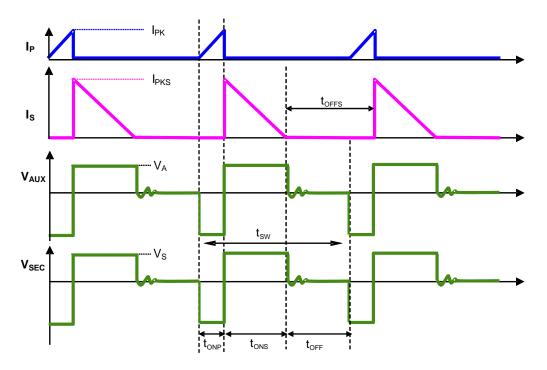

Figure 2 shows the typical waveforms which demonstrate the basic operating principle of AP3785T application. And the parameters are defined as following.

- I<sub>P</sub>---The primary side current

- Is --- The secondary side current

- I<sub>PK</sub>---Peak value of primary side current

- I<sub>PKS</sub>---Peak value of secondary side current

- V<sub>SEC</sub>---The transient voltage at secondary winding

- V<sub>S</sub>---The stable voltage at secondary winding when rectification diode is in conducting status, which equals the sum of output voltage V<sub>O</sub>

and the forward voltage drop of diode

- V<sub>AUX</sub>---The transient voltage at auxiliary winding

- V<sub>A</sub>--- The stable voltage at auxiliary winding when rectification diode is in conducting status, which equals the sum of voltage V<sub>CC</sub> and the

forward voltage drop of auxiliary diode

- tsw ---The period of switching frequency

- t<sub>ONP</sub> ---The conduction time when primary side switch is "ON"

- tons --- The conduction time when secondary side diode is "ON"

- toff --- The dead time when neither primary side switch nor secondary side diode is "ON"

- toffs --- The time when secondary side diode is "OFF"

Figure 2. The Operation Waveform of Flyback PSR System

#### 3. Constant Voltage Operation

As to constant-voltage (CV) operation mode, the AP3785T detects the auxiliary winding voltage at FB pin to regulate the output voltage. The auxiliary winding voltage is coupled with secondary side winding voltage, so the auxiliary winding voltage during the conduction time of secondary rectification diode D1 is:

$$V_{AUX} = \frac{N_{AUX}}{N_{s}} \times (V_{OUT} + Vd)$$

(1)

Where Vd is the diode forward voltage drop.

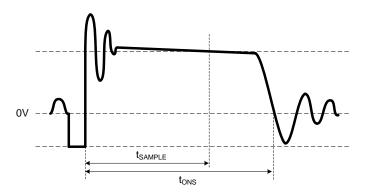

Figure 3. Auxiliary Voltage Waveform

The voltage detection point is at the  $t_{SAMPLE}$  of the D1 on-time. The voltage detection point is changed with the different primary peak current. The CV loop control function of AP3785T then generates a D1 off-time to regulate the output voltage.

#### 4. Constant Current Operation

The AP3785T can work in constant-current (CC) mode. Figure 2 shows the secondary current waveforms.

In CC operation mode, the CC control loop of AP3785T will keep a fixed proportion between D1 on-time  $t_{\text{ONS}}$  and D1 off-time  $t_{\text{OFFS}}$ . The fixed proportion is

$$\frac{t_{ONS}}{t_{OFFS}} = \frac{4}{4} \tag{2}$$

The relationship between the output current and secondary peak current I<sub>PKS</sub> is given by:

$$I_{OUT} = \frac{1}{2} \times I_{PKS} \times \frac{t_{ONS}}{t_{ONS} + t_{OFFS}}$$

(3)

As to tight coupled primary and secondary winding, the secondary peak current is

$$I_{PKS} = \frac{N_P}{N_S} \times I_{PK} \tag{4}$$

Thus the output constant-current is given by:

$$I_{OUT} = \frac{1}{2} \times \frac{N_{P}}{N_{S}} \times I_{PK} \times \frac{t_{ONS}}{t_{ONS} + t_{OFFS}} = \frac{2}{8} \times \frac{N_{P}}{N_{S}} \times I_{PK}$$

(5)

Therefore, AP3785T can realize CC mode operation by constant primary peak current and fixed diode conduction duty cycle.

#### 5. Multiple Segment Peak Current

As to the original PFM PSR system, the switching frequency decreases with decreasing of output current, which will encounter audible noise issue since switching frequency decreases to audio frequency range, about less than 20kHz.

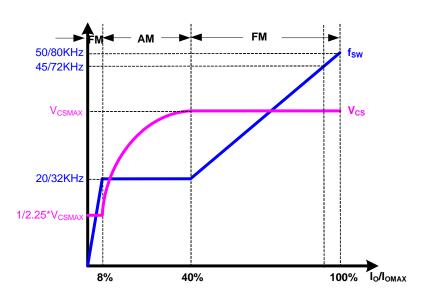

In order to avoid audible noise issue, AP3785T uses 3-segment primary peak current control method at constant voltage (CV) mode, the current sense threshold voltage is multiple segments with different loading, as shown in Figure 4, which are  $V_{CS\_H}$  for high load, varied  $V_{CS\_M}$  for medium load and  $V_{CS\_L}$  for light load. In no load and ultra light load condition (NL mode), the current reference is also  $V_{CS\_L}$ . But the operation in NL mode is different, which will be described in next section.

At constant current (CC) mode, the peak current is still V<sub>CS</sub> H when V<sub>O</sub>> V<sub>FB(SCP)</sub>, if not, the peak current is 2/3\* V<sub>CS</sub> H.

It can be seen from the following figure that with multiple segment peak current control, AP3785T power system can keep switching frequency above 20kHz from light load to heavy load and guarantee the audible noise free performance, and the maximum system switching frequency is not less than 50kHz.

Figure 4. Segment Peak Current and Operating Frequency at CV Mode

#### 6. Operating Frequency

For primary-side regulation, the primary current ip(t) is sensed by a current sense resistor R<sub>CS</sub> (R3 as shown in Typical Applications). The current rises up linearly at a rate of:

$$\frac{\operatorname{dip}(t)}{\operatorname{dt}} = \frac{V_{\text{IN}}(t)}{L_{\text{M}}} \tag{6}$$

As illustrated in Figure 2, when the current ip(t) rises up to I<sub>PK</sub>, the switch Q1 turns off. The constant peak current is given by:

$$I_{PK} = \frac{V_{CS}}{R_{CS}} \tag{7}$$

The energy stored in the magnetizing inductance  $L_{\text{M}}$  each cycle is therefore:

$$Eg = \frac{1}{2} \times L_{M} \cdot I_{PK}^{2}$$

(8)

So the power transferring from the input to the output is given by:

$$P = \frac{1}{2} \times L_{M} \times I_{PK}^{2} \times f_{SW}$$

(9)

$$\eta \times \frac{1}{2} \times L_{P} \times I_{PK}^{2} \times f_{SW} = P_{O} = V_{O} \times I_{O}$$

$$\tag{10}$$

Where,  $f_{SW}$  is the switching frequency,  $\eta$  is the transferring efficiency.

In AP3785T, the high load mode and light load mode adopt the frequency modulation (FM), and the middle load mode uses the amplitude modulation (AM).

During FM, the peak current  $I_{PK}$  is constant, the output power depends on the switching frequency  $f_{SW}$ .

During AM, the frequency is fixed,  $V_{CS\_M}$  is varied. Below is the analysis of  $V_{CS\_M}$ . The square root equation can be got from the following equation:

$$\eta \times \frac{1}{2} \times L_{P} \times I_{PK}^{2} \times f_{SW} = \eta \times \frac{1}{2} \times L_{P} \times \left(\frac{V_{CS}}{R_{CS}}\right)^{2} \times f_{SW} = V_{O} \times I_{O}$$

(11)

So,

$$V_{CS} = \sqrt{\frac{2 \cdot R_{CS}^2 \cdot V_O \cdot I_O}{\eta \cdot L_p \cdot f_{SW}}}$$

(12)

During AM, the frequency is fixed, assume  $V_0$  and  $\eta$  are constants, then

$$V_{CS} = k \cdot \sqrt{I_O}$$

(  $k = \sqrt{\frac{2 \cdot R_{CS}^2 \cdot V_O}{\eta \cdot L_p \cdot f_{SW}}}$  ) (13)

#### 7. NL Mode Operation (Typical Application with APR3415)

At no load and ultra light load, the AP3785T works at no load mode (NL mode) and the output voltage is detected by APR3415. In order to achieve ultra low standby power at NL mode, the static current is reduced to I<sub>CC\_NL</sub>.

- The conditions of exiting NL mode--- $V_{CBC}$ >  $V_{CBC(EN)}$  or  $t_{OFF}$ <  $t_{OFF(EX)}$

- The conditions of entering NL mode--  $V_{CBC}$ <  $V_{CBC(EN)}$  and  $t_{OFF}$  $\geq t_{OFF(EN)}$

At NL mode, the internal reference voltage  $V_{DD}$  is pulled to ground. For normal NL working state, when the APR3415 detects the output voltage is lower than its trigger voltage. The APR3415 VDET pin emits a periodical pulse current. This pulse current will generate a pulse voltage on feedback winding through the transformer coupling. When the FB pin detects this pulse ( $>V_{TRIGGER}$  is valid), the AP3785T re-establishes the  $V_{DD}$  and turns on primary switch to provide one energy pulse to supply output terminal and primary VCC voltage.

#### 8. Leading Edge Blanking

When the power switch is turned on, a turn-on spike will occur on the sense-resistor. To avoid false-termination of the switching pulse, a leading-edge blanking (from power MOSFET on) is built in. During this blanking period, the current sense comparator is disabled and the gate driver can't be switched off.

#### 9. Valley Turn-on

When the off time ( $t_{OFF}$ ) is lower than  $t_{VAL-ON}$ , AP3785T power system can work with valley turn-on. It can reduce MOSFET switching on power losses which is resulted from the equivalent output capacitance to achieve highest overall efficiency. At the same time, because of valley turn-on the switching frequency has the random jitter feature, which will be benefit for conductive EMI performance. And valley turn-on can also reduce the power switch turn on spike current and then achieve the better radiative EMI performance.

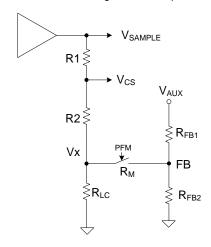

#### 10. Adjustable Line Compensation

Since there is a constant delay time from the CS pin voltage reaching the given V<sub>CS</sub> reference to the power MOSFET turning off, the real primary peak current value always has a gap with the ideal value. The gap value changes with different input line voltage, which is caused by different current rising slope, results in different system constant current value.

In order to eliminate the constant current deviation due to line voltage, the adjustable line compensation is introduced to design. The negative voltage of FB pin which is linear to the line voltage is added up to V<sub>CS</sub> reference by a certain proportion and create an adjustable compensation voltage to clear up the primary current gap, so that the excellent line regulation of output current will be achieved.

Figure 5. Adjustable Line Compensation Circuit

$$\Delta V_{\text{CS}} = -\frac{R_1}{R_1 + R_2} \cdot \frac{N_{\text{AUX}}}{N_P} \cdot \frac{R_{\text{LC}}}{R_{\text{LC}} + R_M + R_{\text{FBI}}} \cdot V_{\text{LINE}}$$

(14)

So, the AP3785T can change the line compensation capability by adjusting the upper resistor at FB pin (R<sub>FB1</sub>). Higher resistance means lower line compensation capability.

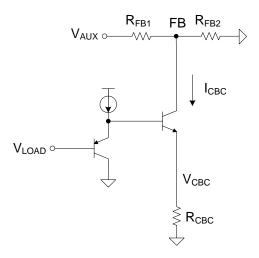

#### 11. Adjustable Cable Compensation

To meet the voltage drop of different output cables, the AP3785T can realize the adjustable cable compensation. As shown in Figure 6,  $V_{CBC}$  follows the  $V_{LOAD}$  that reflects the power system loading percentage.

Figure 6. Adjustable Cable Compensation Circuit

AP3785T Document number: DS37552 Rev. 4 - 2 12 of 18

Downloaded From Oneyac.com

If the CBC resistance ( $R_{CBC}$ ) and  $R_{FB1}$  are fixed, the current ( $I_{CBC}$ ) flowing through the CBC resistance ( $R_{CBC}$ ) also follows the changing of the  $V_{LOAD}$ :

$$I_{CBC} = \frac{V_{LOAD}}{R_{CBC}} \tag{15}$$

The voltage change ( $\Delta V_{AUX}$ ) of auxiliary winding ( $V_{AUX}$ ) is varied with the  $V_{LOAD}$ :

$$\Delta V_{\text{AUX}} = R_{\text{FBI}} \cdot I_{\text{CBC}} = \frac{R_{\text{FBI}}}{R_{\text{CBC}}} \cdot V_{\text{LOAD}}$$

(16)

The  $V_O$  changing ( $\Delta V_O$ ) which  $\Delta V_{AUX}$  reflects is also changed with  $V_{LOAD}$ :

$$\Delta V_{_{O}} \approx \frac{N_{_{S}}}{N_{_{AUX}}} \cdot \Delta V_{_{AUX}} = \frac{N_{_{S}}}{N_{_{aux}}} \cdot \frac{R_{_{FB1}}}{R_{_{CBC}}} \cdot V_{_{LOAD}} \tag{17}$$

So, the right cable compensation can be achieved by adjusting  $R_{\text{CBC.}}$  The  $43k\Omega$  resistance can ensure about 350mV cable compensation from no load to full load.

#### 12. Protection

The AP3785T has multiple built-in fault protection functions: FB over voltage protection, VCC over voltage protection, output short circuit protection, FB open circuit protection, transformer saturation protection, current sense resistor fault (short or open) protection and external over temperature protection. The different fault conditions trigger the different protection modes.

#### **Protection Mode**

The AP3785T has three protection modes: Dmin, auto-recovery and fast auto-recovery, which the operation principles are different.

When FB down-resistance short protection is triggered, the AP3785T enters the Dmin mode whereby the AP3785T immediately shuts down and keeps a duration time  $t_{OFF(MAX)}$  to output a pulse for turning on the primary switch, which is used to detect whether the fault condition is removed and provide VCC supply. If the fault condition is removed before  $V_{CC}$  decreases below  $V_{OPR(MIN)}$ , the device will enter normal operation mode. If not, the AP3785T will repeat another Dmin mode action. When  $V_{CC}$  drops below  $V_{OPR(MIN)}$ , AP3785T will enter the restart process, and VCC voltage changes between  $V_{TH(ST)}$  and  $V_{OPR(MIN)}$  until FB down-resistance short condition is removed.

When FB open circuit protection, output short circuit protection, transformer saturation protection and current sense resistor fault (short or open) protection are triggered, the device enters the auto-recovery mode. Once the AP3785T enters the auto-recovery mode, the device shuts down immediately and doesn't signal any pulse, the VCC static current is decreased from operating current ( $I_{CC\_OPR}$ ) to standby current ( $I_{CC\_NL}$ ). Until VCC voltage drops to  $V_{OPR(MIN)}$ , the AP3785T will enter the restart process, and VCC voltage changes between  $V_{TH(ST)}$  and  $V_{OPR(MIN)}$  until the fault condition is removed. The slope of VCC voltage to discharge is very small, and the time to drop to  $V_{OPR(MIN)}$  is very long. It can decrease the average power dissipation at a fault condition.

When VCC over voltage protection, FB over voltage protection, CBC short to GND protection, internal over temperature and external over temperature protection are activated, the device enters the fast auto-recovery mode. The only difference with auto-recovery is that the VCC to discharge current is kept operating current and the system can fast restart.

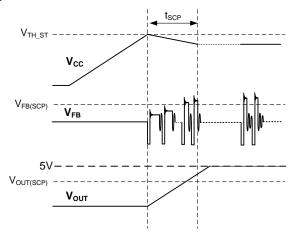

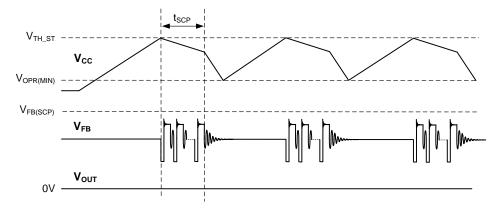

### 12.1 Short Circuit Protection (SCP)

Short Circuit Protection (SCP) detection principle is similar to the normal output voltage feedback detection by sensing FB pin voltage. When the detected FB pin voltage is below  $V_{FB(SCP)}$  for a duration of about  $t_{SCP}$ , the SCP is triggered. Then the AP3785T enters auto-recovery mode that the IC immediately shuts down and then restarts, so that the VCC voltage changes between  $V_{TH\_ST}$  and UVLO threshold until  $V_{FB(SCP)}$  condition is removed.

As to the normal system startup, the time duration of FB pin voltage below  $V_{FB(SCP)}$  should be less than  $t_{SCP}$  to avoid entering SCP mode. But for the output short condition or the output voltage below a certain level, the SCP mode will be triggered.

AP3785T Document number: DS37552 Rev. 4 - 2

Figure 7 is the AP3785T normal start-up waveform that the voltage of FB pin is above  $V_{FB(SCP)}$  during  $t_{SCP}$  after  $V_{CC}$  gets to the  $V_{TH\_ST}$ , which doesn't enter the SCP mode. As shown in Figure 8,  $V_{OUT}$  is short and the voltage of FB pin is lower than  $V_{FB(SCP)}$  during  $t_{SCP}$ , the AP3785T triggers the SCP and enters auto-recovery mode.

Figure 7. Normal Start-up

Figure 8. Short Circuit Protection (SCP) and Auto-recovery Mode

#### 12.2 Transformer Saturation Protection via Primary Peak Current Limitation

When the transformer saturation happens, the voltage of EM pin will increase promptly and be over the reference voltage  $V_{EM(MAX)}$ . If two consecutive pulses exceed the value, the device shuts down and enters into auto-recovery mode.

#### 12.3 External Over Temperature Protection (External OTP)

The AP3785T provides external over-temperature protection (OTP) by connecting a Negative-Temperature-Coefficient (NTC) resistor from OTP pin to GND. Internally, a current source  $I_{OTP}$  is injected to the OTP pin, which generates a voltage proportional to the NTC resistance. At high ambient temperature, the NTC resistance gets lower and results in the OTP pin voltage decreasing. If the OTP pin voltage drops below an internally-set threshold  $V_{OTP}$ , then the OTP is triggered, and the AP3785T shuts down immediately and enters the fast auto-recovery mode. The power system will keep fast auto-recovery mode until the ambient temperature decreases and OTP pin voltage increases over the voltage  $V_{OTP\_REC}$ , which the AP3785T can recover to normal operation.

If the OTP pin is not connected to the NTC resistor, the external OTP function will not work and the IC can still work normally with internal OTP.

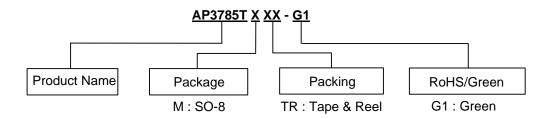

# Ordering Information

| Package | Temperature Range | Part Number   | Marking ID | Packing          |  |

|---------|-------------------|---------------|------------|------------------|--|

| SO-8    | -40 to +85°C      | AP3785TMTR-G1 | 3785TM-G1  | 4000/Tape & Reel |  |

## **Marking Information**

#### (Top View)

First and Second Lines: Logo and Marking ID

Third Line: Date Code

Y: Year

WW: Work Week of Molding A: Assembly House Code

XX: 7th and 8th Digits of Batch No.

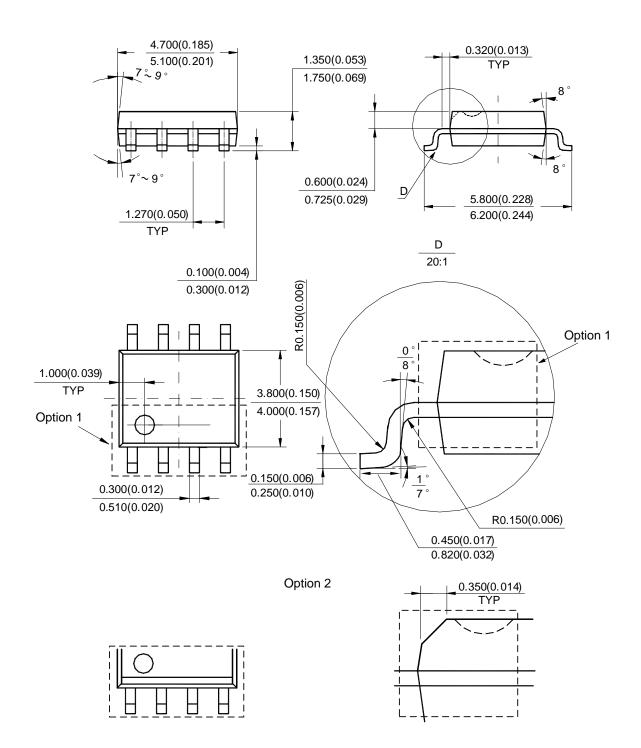

## Package Outline Dimensions (All dimensions in mm(inch).)

#### (1) Package Type: SO-8

Note: Eject hole, oriented hole and mold mark is optional.

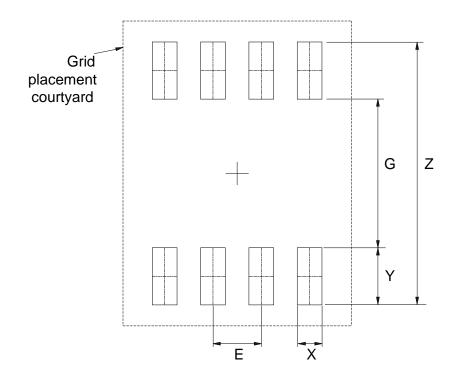

## **Suggested Pad Layout**

(1) Package Type: SO-8

| Dimensions | Z           | G           | X           | Y           | E           |

|------------|-------------|-------------|-------------|-------------|-------------|

|            | (mm)/(inch) | (mm)/(inch) | (mm)/(inch) | (mm)/(inch) | (mm)/(inch) |

| Value      | 6.900/0.272 | 3.900/0.154 | 0.650/0.026 | 1.500/0.059 | 1.270/0.050 |

#### **IMPORTANT NOTICE**

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2015, Diodes Incorporated

www.diodes.com

AP3785T Document number: DS37552 Rev. 4 - 2 18 of 18

# 单击下面可查看定价,库存,交付和生命周期等信息

>>Diodes Incorporated(达迩科技(美台))