# SPECIFICATION

#### 1. Application

1)This document is applicable to the real time clock module RX-8025T that are delivered

- to from Seiko Epson Corp.

- 2)RoHS compliant

RX-8025T contains lead in high melting type solder which is exempted in RoHS directive.

- 3)This Product supplied (and any technical information furnished, if any) by Seiko Epson Corporation shall not be used for the development and manufacture of weapon of mass destruction or for other military purposes. Making available such products and technology to any third party who may use such products or technologies for the said purposes are also prohibited.

- 4) This product listed here is designed as components or parts for electronics equipment in general consumer use. We do not expect that any of these products would be incorporated or otherwise used as a component or part for the equipment, which requires an systems, and medical equipment, the functional purpose of which is to keep extra high reliability, such as satellite, rocket and other space life.

#### 2. Product No. / Model

The product No. of this Real Time Clock Module is X1B0002810005. The model is RX - 8025T VerD

#### 3. Packing

It is subject to the packing standard of Seiko Epson Corp.

#### 4. Warranty

Defective parts which are originated by us are replaced free of charge in case defects are found within 12 months after delivery.

#### 5. Amendment and abolishment

Amendment and/or abolishment of this specification are subject to the agreement of both parties.

#### 6. Contents

| Item No. | Item                                         | Page    |

|----------|----------------------------------------------|---------|

| 1        | Block diagram                                | 2       |

| 2        | Terminal description                         | 3       |

| 3        | Absolute maximum ratings                     | 4       |

| 4        | Recommend operating conditions               | 4       |

| 5        | Frequency characteristics                    | 4       |

| 6        | Electrical characteristics                   | 5 to 6  |

| 7        | Register table                               | 7 to 10 |

| 8        | External Dimensions / Marking Layout         | 11      |

| 9        | Environmental and mechanical characteristics | 12      |

| 10       | Application note                             | 13      |

Downloaded From Oneyac.com

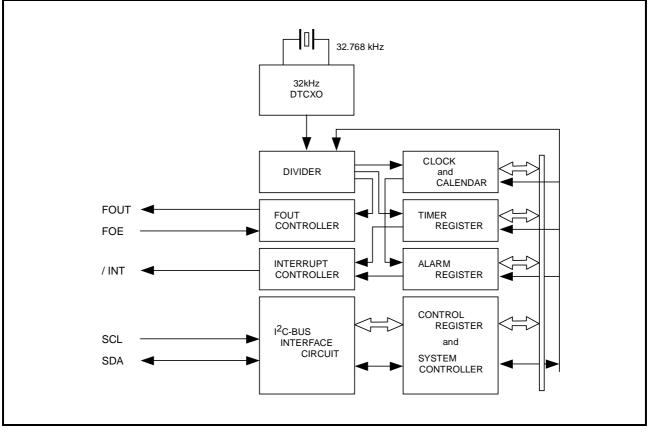

#### 1. Block Diagram

## 2. Terminal description

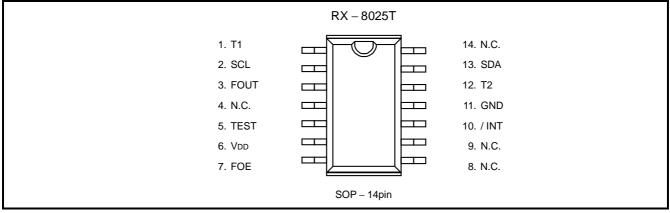

#### 2.1. Terminal connections

#### 2.2. Pin Functions

| Signal<br>name | I/O    | Function                                                                                                                                                                                                                                                                                                      |

|----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T1             | Input  | * Use by the manufacture for testing. ( Do not connect externally.)                                                                                                                                                                                                                                           |

| SCL            | Input  | This is the serial clock input pin for I <sup>2</sup> C Bus communications.                                                                                                                                                                                                                                   |

| FOUT           | Output | This is the C-MOS output pin with output control provided via the FOE pin.<br>When FOE = "H" (high level), this pin outputs a 32.768 kHz signal.<br>When output is stopped, the FOUT pin = "Hi-Z"( high impedance ).                                                                                          |

| TEST           | Input  | * Use by the manufacture for testing. ( Do not connect externally.)                                                                                                                                                                                                                                           |

| Vdd            | _      | This pin is connected to a positive power supply.                                                                                                                                                                                                                                                             |

| FOE            | Input  | This is an input pin used to control the output mode of the FOUT pin.<br>When this pin's level is high, the FOUT pin is in output mode. When it is low, output via the<br>FOUT pin is stopped.                                                                                                                |

| / INT          | Output | This pins is used to output alarm signals, timer signals, time update signals, and other signals. This pin is an open drain pin.                                                                                                                                                                              |

| GND            | -      | This pin is connected to a ground.                                                                                                                                                                                                                                                                            |

| T2             | _      | * Use by the manufacture for testing. ( Do not connect externally.)                                                                                                                                                                                                                                           |

| SDA            | I/O    | This pin's signal is used for input and output of address, data, and ACK bits, synchronized with the serial clock used for I <sup>2</sup> C communications. Since the SDA pin is an N-ch open drain pin during output, be sure to connect a suitable pull-up resistance relative to the signal line capacity. |

| N.C.           | _      | This pin is not connected to the internal IC.<br>Leave N.C. pins open or connect them to GND or VDD.                                                                                                                                                                                                          |

Note: Be sure to connect a bypass capacitor rated at least 0.1  $\mu F$  between VDD and GND.

### 3 Absolute Maximum Ratings

| 3. Absolute Maximum Ratings |        |                                              |                    |      |  |  |  |  |  |

|-----------------------------|--------|----------------------------------------------|--------------------|------|--|--|--|--|--|

| ltem                        | Symbol | Condition                                    | Rating             | Unit |  |  |  |  |  |

| Supply voltage              | Vdd    | Between VDD and GND                          | –0.3 to +6.5       | V    |  |  |  |  |  |

| Input voltage (1)           | VIN1   | FOE pin                                      | GND-0.3 to VDD+0.3 | V    |  |  |  |  |  |

| Input voltage (2)           | VIN2   | SCL and SDA pins                             | GND-0.3 to +6.5    | V    |  |  |  |  |  |

| Output voltage (1)          | VOUT1  | FOUT pin                                     | GND-0.3 to VDD+0.3 | V    |  |  |  |  |  |

| Output voltage (2)          | Vout2  | SDA and /INT pins                            | GND-0.3 to +6.5    | V    |  |  |  |  |  |

| Storage temperature         | Tstg   | When stored separately,<br>without packaging | -55 to +125        | °C   |  |  |  |  |  |

## 4. Recommended Operating Conditions

| 4. Recommended Operating Conditions |        |                                     |      |      |      |      |  |  |

|-------------------------------------|--------|-------------------------------------|------|------|------|------|--|--|

| Item                                | Symbol | Condition                           | Min. | Тур. | Max. | Unit |  |  |

| Operating supply voltage            | Vdd    | Interface voltage                   | 1.6  | 3.0  | 5.5  | V    |  |  |

| Temp. compensation voltage          | Vтем   | Temperature compensation<br>voltage | 2.2  | 3.0  | 5.5  | V    |  |  |

| Clock supply voltage                | Vclk   | _                                   | 1.6  | 3.0  | 5.5  | V    |  |  |

| Operating temperature               | Topr   | No condensation                     | -40  | +25  | +85  | °C   |  |  |

### 5. Frequency Characteristics

| 5. Frequency Characteristics      |        |                                      |                                                                  |                                                |                          |              |                              |  |

|-----------------------------------|--------|--------------------------------------|------------------------------------------------------------------|------------------------------------------------|--------------------------|--------------|------------------------------|--|

| Item                              | Symbol |                                      | Condition                                                        | Rating                                         | Unit                     |              |                              |  |

| Frequency tolerance               | ∆f /f  | UC                                   | Ta = 0 to +50 °C, VDD = 3.0 V<br>Ta = -30 to +70 °C, VDD = 3.0 V | ± 3.8 <sup>(*1)</sup><br>± 5.0 <sup>(*2)</sup> | × 10 <sup>-6</sup>       |              |                              |  |

| Frequency/voltage characteristics | f /V   | Ta = +2                              | $^{\circ}$ C, VDD = 2.2 V to 5.5 V                               | ± 1.0 Max.                                     | imes 10 <sup>-6</sup> /V |              |                              |  |

| Oscillation start time            | tSTA   |                                      | 25 °C, VDD = 1.6 V<br>40 to +85 ⁰C, VDD = 1.6 V to 5.5 V         | 1.0 Max.<br>3.0 Max.                           | S                        |              |                              |  |

| Aging                             | fa     | Ta = +25 °C, VDD = 3.0 V, first year |                                                                  | Ta = +25 °C, VDD = 3.0 V, first year           |                          | $\pm$ 3 Max. | imes 10 <sup>-6</sup> / year |  |

\*<sup>1)</sup> Equivalent to 10 seconds of month deviation. <sup>\*2)</sup> Equivalent to 13 seconds of month deviation.

## 6. Electrical Characteristics

| Item                        | Symbol |                                     | Min.             | Тур.               | Max.             | Unit |                       |    |

|-----------------------------|--------|-------------------------------------|------------------|--------------------|------------------|------|-----------------------|----|

| Current<br>consumption (1)  | IDD1   | fscL = 0 Hz, / INT<br>FOE = GND     | = VDD            | VDD = 5 V          |                  | 1.2  | 3.4                   | μA |

| Current<br>consumption (2)  | Idd2   | FOUT : output OF<br>Compensation in |                  | VDD = 3 V          |                  | 0.8  | 2.1                   | μΑ |

| Current<br>consumption (3)  | Idd3   | fsc∟ = 0 Hz, / INT<br>FOE = GND     | = Vdd            | VDD = 5 V          |                  | 3.0  | 7.5                   | ٨  |

| Current<br>consumption (4)  | IDD4   | FOUT :32.768 kH<br>Compensation in  | , I              | VDD = 3 V          |                  | 2.0  | 5.0                   | μA |

| Current<br>consumption (5)  | IDD5   | fscL = 0 Hz, / INT<br>FOE = GND     | = VDD            | Vdd = 5 V          |                  | 8.0  | 20.0                  | ٨  |

| Current<br>consumption (6)  | IDD6   | FOUT :32.768 kH<br>Compensation int |                  | VDD = 3 V          |                  | 5.0  | 12.0                  | μA |

| Current<br>consumption (7)  | Idd7   | fscL = 0 Hz, / INT<br>FOE = GND     | = VDD            | Vdd = 5 V          |                  | 1.15 | 2.95                  | ٨  |

| Current<br>consumption (8)  | IDD8   | FOUT : output OF<br>Compensation O  | FF(High Z)<br>FF | VDD = 3 V          |                  | 0.72 | 1.85                  | μA |

| Current<br>consumption (9)  | IDD9   | fscL = 0 Hz, / INT<br>FOE = GND     | = VDD            | Vdd = 5 V          |                  | 430  | 900                   | ٨  |

| Current<br>consumption (10) | IDD10  | FOUT : output OF<br>Compensation O  |                  | VDD = 3 V          |                  | 180  | 350                   | μA |

| High-level input            | Vін    | FOE pin                             |                  |                    | $0.8 \times VDD$ |      | VDD + 0.3             | V  |

| voltage                     | VIN    | SCL and SDA pin                     | IS               |                    | 0.7 	imes Vdd    |      | 5.5                   | v  |

| Low-level input             | VIL    | FOE pin                             |                  |                    | GND – 0.3        |      | 0.2 	imes Vdd         | V  |

| voltage                     | VIL    | SCL and SDA pin                     | IS               |                    | GND - 0.3        |      | $0.3\times\text{Vdd}$ | v  |

| High-level output           | VOH1   |                                     | VDD=5 V, IOH     | =–1 mA             | 4.5              |      | 5.0                   |    |

| /oltage                     | Voh2   | FOUT pin                            | VDD=3 V, IOH     | /dd=3 V, Iон=–1 mA |                  |      | 3.0                   | V  |

| ronago                      | Vонз   |                                     | VDD=3 V, IOH     |                    | 2.9              |      | 3.0                   |    |

|                             | VOL1   |                                     | VDD=5 V, IOL     | =1 mA              | GND              |      | GND+0.5               |    |

|                             | Vol2   | FOUT pin                            | VDD=3 V, IOL     | =1 mA              | GND              |      | GND+0.8               | V  |

| _ow-level output            | Vol3   |                                     | VDD=3 V, IOL     | =100 μA            | GND              |      | GND+0.1               |    |

| voltage                     | Vol4   | / INT pin                           | VDD=5 V, IOL     |                    | GND              |      | GND+0.25              | V  |

| -                           | Vol5   | / INT pill                          | VDD=3 V, IOL     | =1 mA              | GND              |      | GND+0.4               | v  |

|                             | Vol6   | SDA pin                             | Vdd≥2 V, Iol     | .=3 mA             | GND              |      | GND+0.4               | V  |

| nput leakage<br>current     | Ilk    | FOE, SCL, SDA J                     | pins, Vin = Vi   | DD or GND          | -0.5             |      | 0.5                   | μA |

| Dutput leakage current      | loz    | / INT, SDA, FOU <sup>-</sup>        | VDD or GND       | -0.5               |                  | 0.5  | μA                    |    |

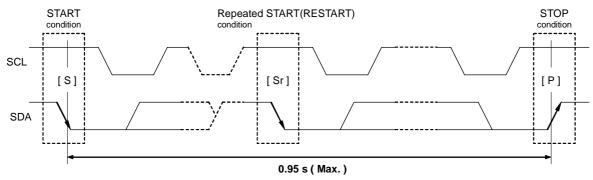

Caution: When accessing this device, all communication from transmitting the start condition to transmitting the stop condition after access **should be completed within 0.95 seconds**. If such communication requires **0.95 seconds** or longer, the I<sup>2</sup>C bus interface is reset by the internal bus timeout function.

### 7. Register table

| Address | Function           | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 | Remark     |

|---------|--------------------|-------|-------|-------|-------|-------|-------|-------|-------|------------|

| 0       | SEC                | 0     | 40    | 20    | 10    | 8     | 4     | 2     | 1     | *3         |

| 1       | MIN                | 0     | 40    | 20    | 10    | 8     | 4     | 2     | 1     | *3         |

| 2       | HOUR               | 0     | 0     | 20    | 10    | 8     | 4     | 2     | 1     | *3         |

| 3       | WEEK               | 0     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | *3         |

| 4       | DAY                | 0     | 0     | 20    | 10    | 8     | 4     | 2     | 1     | *3         |

| 5       | MONTH              | 0     | 0     | 0     | 10    | 8     | 4     | 2     | 1     | *3         |

| 6       | YEAR               | 80    | 40    | 20    | 10    | 8     | 4     | 2     | 1     | _          |

| 7       | RAM                | ٠     | •     | •     | •     | •     | •     | •     | •     | *4         |

| 8       | MIN Alarm          | AE    | 40    | 20    | 10    | 8     | 4     | 2     | 1     | -          |

| 9       | HOUR Alarm         | AE    | •     | 20    | 10    | 8     | 4     | 2     | 1     | *4         |

| А       | WEEK Alarm         | AE    | 6     | 5     | 4     | 3     | 2     | 1     | 0     | *4         |

| A       | DAY Alarm          | AE    | •     | 20    | 10    | 8     | 4     | 2     | 1     | *4         |

| В       | Timer Counter 0    | 128   | 64    | 32    | 16    | 8     | 4     | 2     | 1     | -          |

| С       | Timer Counter 1    | •     | ٠     | ٠     | •     | 2048  | 1024  | 512   | 256   | *4         |

| D       | Extension Register | TEST  | WADA  | USEL  | TE    | FSEL1 | FSEL0 | TSEL1 | TSEL0 | *1, *3, *5 |

| E       | Flag Register      | 0     | 0     | UF    | TF    | AF    | 0     | VLF   | VDET  | *1, *2, *3 |

| F       | Control Register   | CSEL1 | CSEL0 | UIE   | TIE   | AIE   | 0     | 0     | RESET | *3         |

Note When after the initial power-up or when the result of read out the VLF bit is "1", initialize all registers, before using the module. Be sure to avoid entering incorrect date and time data, as clock operations are not guaranteed when the data

or time data is incorrect.

\*1) During the initial power-up, the TEST bit is reset to "0" and the VLF bit is set to "1".

\* At this point, all other register values are undefined, so be sure to perform a reset before using the module.

\*2) Only a "0" can be written to the UF, TF, AF, VLF, or VDET bit.

\*3) Any bit marked with "o" should be used with a value of "0" after initialization.

- \*4) Any bit marked with "•"( is a RAM bit that can be used to read or write any data.

- \*5) The TEST bit is used by the manufacturer for testing. Be sure to set "0" for this bit when writing.

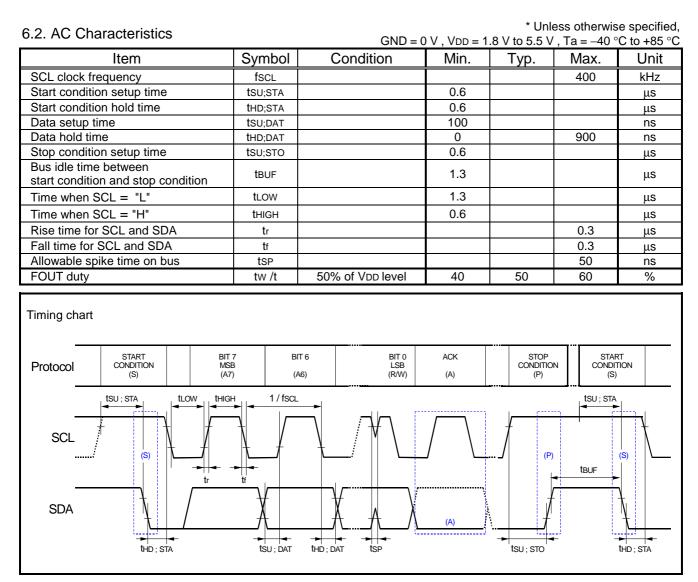

#### 7.1. Starting and stopping I<sup>2</sup>C bus communications

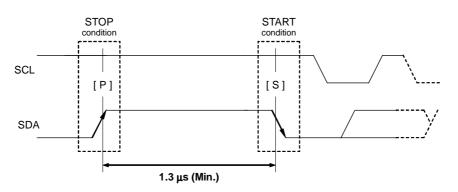

- 1) START condition, repeated START condition, and STOP condition

- (1) START condition

The SDA level changes from high to low while SCL is at high level.

- (2) STOP condition

- $\bullet$  This condition regulates how communications on the I^2C-BUS are terminated.

- The SDA level changes from low to high while SCL is at high level.

- (3) Repeated START condition (RESTART condition)

• In some cases, the START condition occurs between a previous START condition and the next STOP condition, in which case the second START condition is distinguished as a RESTART condition. Since the required status is the same as for the START condition, the SDA level changes from high to low while SCL is at high level.

- 2) Caution points

- \*1) The master device always controls the START, RESTART, and STOP conditions for communications.

- \*2) The master device does not impose any restrictions on the timing by which STOP conditions affect transmissions, so communications can be forcibly stopped at any time while in progress. (However, this is only when this RTC module is in receiver mode (data reception mode = SDA released).

- \*3) When communicating with this RTC module, the series of operations from transmitting the START condition to transmitting the STOP condition should occur **within 0.95 seconds**. (A RESTART condition may be sent between a START condition and STOP condition, but even in such cases the series of operations from transmitting the START condition to transmitting the STOP condition should still occur **within 0.95 seconds**.)

If this series of operations requires **0.95 seconds or longer**, the I<sup>2</sup>C bus interface will be automatically cleared and set to standby mode by this RTC module's bus timeout function. Note with caution that both write and read operations are invalid for communications that occur during or after this auto clearing operation. (When the read operation is invalid, all data that is read has a value of "1"). Restarting of communications begins with transfer of the START condition again

\*4) When communicating with this RTC module, wait at least 1.3 μs (see the tBUF rule) between transferring a STOP condition (to stop communications) and transferring the next START condition (to start the next round of communications).

- 7.2. Data transfers and acknowledge responses during I<sup>2</sup>C-BUS communications

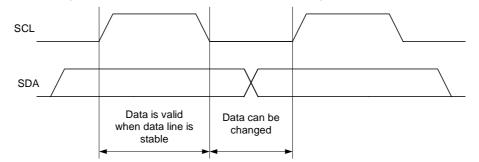

- 1) Data transfers

Data transfers are performed in 8-bit (1 byte) units once the START condition has occurred. There is no limit on the amount (bytes) of data that are transferred between the START condition and STOP condition. (However, the transfer time must be no longer than 0.95 seconds.)

The address auto increment function operates during both write and read operations. After address Fh, incrementation goes to address 0h.

Updating of data on the transmitter (transmitting side)'s SDA line is performed while the SCL line is at low level. The receiver (receiving side) receives data while the SCL line is at high level.

\* Note with caution that if the SDA data is changed while the SCL line is at high level, it will be treated as a START, RESTART, or STOP condition.

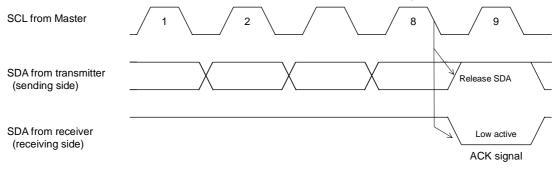

2) Data acknowledge response (ACK signal)

When transferring data, the receiver generates a confirmation response (ACK signal, low active) each time an 8-bit data segment is received. If there is no ACK signal from the receiver, it indicates that normal communication has not been established. (This does not include instances where the master device intentionally does not generate an ACK signal.)

Immediately after the falling edge of the clock pulse corresponding to the 8th bit of data on the SCL line, the transmitter releases the SDA line and the receiver sets the SDA line to low (= acknowledge) level.

After transmitting the ACK signal, if the Master remains the receiver for transfer of the next byte, the SDA is released at the falling edge of the clock corresponding to the 9th bit of data on the SCL line. Data transfer resumes when the Master becomes the transmitter.

When the Master is the receiver, if the Master does not send an ACK signal in response to the last byte sent from the slave, that indicates to the transmitter that data transfer has ended. At that point, the transmitter continues to release the SDA and awaits a STOP condition from the Master.

#### 7.3. Slave address

The I<sup>2</sup>C bus device does not include a chip select pin such as is found in ordinary logic devices. Instead of using a chip select pin, slave addresses are allocated to each device.

All communications begin with transmitting the [START condition] + [slave address (+ R/W specification)]. The receiving device responds to this communication only when the specified slave address it has received matches its own slave address.

|       | Transfer data |     |       | R/W bit |       |       |       |       |             |

|-------|---------------|-----|-------|---------|-------|-------|-------|-------|-------------|

|       |               |     | bit 6 | bit 5   | bit 4 | bit 3 | bit 2 | bit 1 | bit 0       |

| Read  | 65 h          | 0 1 |       | 1 1     | 0     | 0     | 1     | 0     | 1 (= Read)  |

| Write | 64 h          | U   |       | 1       | 0     | U     | 1     | U     | 0 (= Write) |

Slave addresses have a fixed length of 7 bits. This RTC's slave address is **[0110 010\*]**. An R/W bit ("\*" above) is added to each 7-bit slave address during 8-bit transfers.

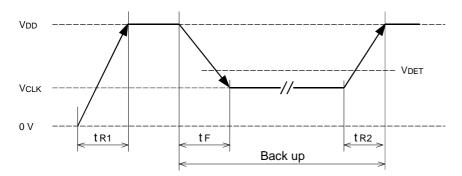

### 7.4. Backup and Recovery

| ltem                               | Symbol | Condition                        | Min. | Тур. | Max. | Unit. |

|------------------------------------|--------|----------------------------------|------|------|------|-------|

| Power supply detection voltage (1) | Vdet   | _                                |      |      | 2.2  | V     |

| Power supply detection voltage (2) | VLOW   | _                                |      |      | 1.6  | V     |

| Power supply<br>drop time          | t F    | _                                | 2    |      |      | μs /V |

| Initial power-up time              | tr1    | -                                |      |      | 10   | ms /V |

| Clock maintenance                  |        | $1.6V \rightarrow VDD \leq 3.6V$ | 5    |      |      | μs /V |

| power-up time                      | t R2   | $1.6V \rightarrow VDD > 3.6V$    | 15   |      |      | μs /V |

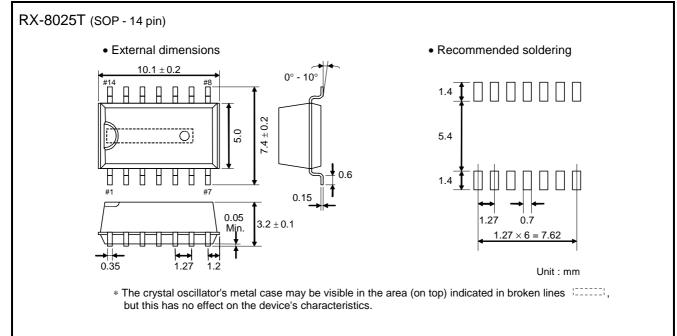

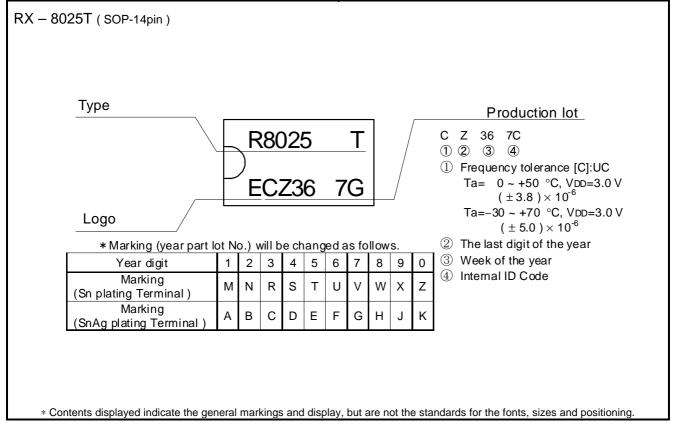

### 8. External Dimensions / Marking Layout

#### 8.1. External dimensions

#### 8.2. Marking layout

### 9. Environmental and mechanical characteristics

(The company evaluation condition We evaluate it by the following examination item and examination condition.)

|     |                              | Val                     | ue *1            |                                                             |  |  |  |

|-----|------------------------------|-------------------------|------------------|-------------------------------------------------------------|--|--|--|

| No. | Item                         | $\Delta$ f / f          | Electrical       | Test Conditions                                             |  |  |  |

|     |                              | $[1 \times 10^{-6}]$ *2 | characteristics  |                                                             |  |  |  |

| 1   | High temperature storage     | *3 ± 50                 |                  | +125 °C × 1 000 h                                           |  |  |  |

| 2   | Low temperature storage      | *3 ±10                  |                  | -55 °C × 1 000 h                                            |  |  |  |

| 3   | High temperature bias        | *3 ±20                  |                  | +85 °C × 5.5 V × 1 000 h                                    |  |  |  |

| 4   | Low temperature bias         | *3 ±10                  |                  | -40 °C × 5.5 V × 1 000 h                                    |  |  |  |

| 5   | Temperature humidity bias    | *3 ±20                  |                  | +85 °C $\times$ 85 %RH $\times$ 5.5 V $\times$ 1 000 h      |  |  |  |

| 6   | Temperature cycle            | *3 ±10                  |                  | -55 °C ⇔ +125 °C                                            |  |  |  |

| 0   | Temperature cycle            | 5 ± 10                  |                  | 30 min at each temp. 100 cycles                             |  |  |  |

|     |                              |                         | *4               | For convention reflow soldering furnace                     |  |  |  |

| 7   | Resistance to soldering heat | ±8                      | 4                | (3 times)                                                   |  |  |  |

|     |                              |                         |                  | Follow JEDEC J-STD-020C                                     |  |  |  |

|     |                              |                         |                  | Free drop from 750 mm height on a hard                      |  |  |  |

| 8   | Drop                         | ±5                      |                  | wooden board for 3 times                                    |  |  |  |

|     |                              |                         |                  | (Board is thickness more than 30 mm)                        |  |  |  |

|     |                              |                         |                  | 10 Hz to 55 Hz amplitude 0.75 mm                            |  |  |  |

| 9   | Vibration                    | ± 5                     |                  | 55 Hz to 500 Hz acceleration 98 m/s <sup>2</sup>            |  |  |  |

| Ŭ   |                              | 20                      |                  | 10 Hz $\rightarrow$ 500 Hz $\rightarrow$ 10 Hz 15min./cycle |  |  |  |

|     |                              |                         |                  | 6 h (2 hours , 3 directions)                                |  |  |  |

| 10  | Flexibility of termination   | No defect for           | wire termination | Put weight of 2.5 N on top of the termination               |  |  |  |

| 10  |                              |                         |                  | Bending following angle :+90 ° to -90 ° to 0                |  |  |  |

| 11  | Solderability                | Termination             | must be 95 %     | Dip termination into solder bath at                         |  |  |  |

|     |                              | covered wit             | n fresh solder   | +235 $\C$ ± 5 $\C$ for 5 s (Using Rosin Flux)               |  |  |  |

| 12  | Solvent resistance           | The marking             | shall be legible | Ref. JIS C 0052 or IEC 60068-2-45                           |  |  |  |

< Notes >

1. \*1 Each test done independently.

2. \*2 Measuring 2 h to 24 h later leaving in room temperature after each test.

3. \*3 Pre conditionings

1. +125 °C  $\times$  24 h to +85 °C  $\times$  85 %  $\times$  168 h  $\rightarrow$  reflow 3 times

2. Initial value shall be after 24 h at room temperature.

4. \*4 Satisfy item [5] Frequency characteristics (exclude Frequency stability and Aging) and item

[6] Electrical characteristics after test

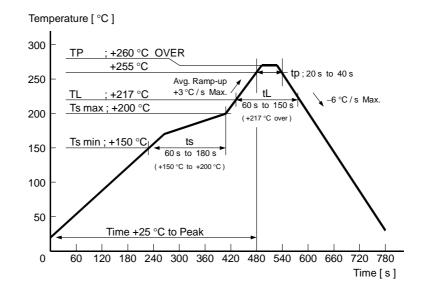

◆ Air-reflow condition (Follow JEDEC J-STD-020C)

#### 10. Application notes

#### 10.1. Notes on handling

This module uses a C-MOS IC to realize low power consumption. Carefully note the following cautions when handling.

(1) Static electricity

While this module has built-in circuitry designed to protect it against electrostatic discharge, the chip could still be damaged by a large discharge of static electricity. Containers used for packing and transport should be constructed of conductive materials. In addition, only soldering irons, measurement circuits, and other such devices which do not leak high voltage should be used with this module, which should also be grounded when such devices are being used.

(2) Noise

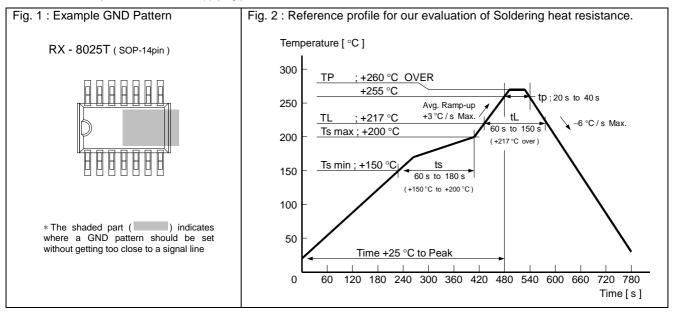

If a signal with excessive external noise is applied to the power supply or input pins, the device may malfunction or "latch up." In order to ensure stable operation, connect a filter capacitor (preferably ceramic) of greater that 0.1F as close as possible to the power supply pins (between VDD and GNDs). Also, avoid placing any device that generates high level of electronic noise near this module. \* Do not connect signal lines to the shaded area in the figure shown in Fig. 1 and, if possible, embed this area in a GND land.

#### (3) Voltage levels of input pins

When the input pins are at the mid-level, this will cause increased current consumption and a reduced noise margin, and can impair the functioning of the device. Therefore, try as much as possible to apply the voltage level close to VDD or GND.

#### (4) Handling of unused pins

Since the input impedance of the input pins is extremely high, operating the device with these pins in the open circuit state can lead to unstable voltage level and malfunctions due to noise. Therefore, pull-up or pull-down resistors should be provided for all unused input pins.

(5) Storage condition

This products is Level 1 for JEDEC L-STD-020C Moisture Sensitivity Level. Storage below 30°C / 85%RH after open packing, and assemble within 6month.

#### 10.2. Notes on packaging

#### (1) Soldering heat resistance.

If the temperature within the package exceeds +260 °C, the characteristics of the crystal oscillator will be degraded and it may be damaged. The reflow conditions within our reflow profile is recommended. Therefore, always check the mounting temperature and time before mounting this device. Also, check again if the mounting conditions are later changed. \* See Fig. 2 profile for our evaluation of Soldering heat resistance for reference.

(2) Mounting equipment

While this module can be used with general-purpose mounting equipment, the internal crystal oscillator may be damaged in some circumstances, depending on the equipment and conditions. Therefore, be sure to check this. In addition, if the mounting conditions are later changed, the same check should be performed again.

#### (3) Ultrasonic cleaning

Depending on the usage conditions, there is a possibility that the crystal oscillator will be damaged by resonance during ultrasonic cleaning. Since the conditions under which ultrasonic cleaning is carried out (the type of cleaner, power level, time, state of the inside of the cleaning vessel, etc.) vary widely, this device is not warranted against damage during ultrasonic cleaning.

- (4) Mounting orientation

- This device can be damaged if it is mounted in the wrong orientation. Always confirm the orientation of the device before mounting. (5) Leakage between pins

- Leakage between pins may occur if the power is turned on while the device has condensation or dirt on it. Make sure the device is dry and clean before supplying power to it.

单击下面可查看定价,库存,交付和生命周期等信息

>>Epson(爱普生)