# 1.8V & 2.5V & 3.3V LVCMOS High-Performance Clock Buffer

#### **FEATURES**

- High-Performance 1:4 LVCMOS Clock Buffer

- Very Low Pin-to-Pin Skew < 50ps

- Very Low Additive Jitter < 50fs

- Very Low Propagation Delay < 3ns</p>

- Synchronous Output Enable

- Supply Voltage: 3.3V or 2.5V or 1.8V

- $f_{max} = 250MHz$  for 3.3V & 2.5V

- $f_{max} = 200MHz$  for 1.8V

- Operating Temperature Range: -40°C to 105°C

- Available in 8-Pin TSSOP or DFN Packages

#### **APPLICATIONS**

- Factory Automation & Control

- Telecommunications Equipment

- Data Center & Enterprise Computing

- Grid Infrastructure

- Motor Drivers

- Medical Imaging

- Consumer Applications

#### **GENERAL DESCRIPTION**

The GM51104 is a modular, high-performance, low-skew, general-purpose clock buffer. High performing characteristics such as low additive jitter, low skew, and wide operation temperature range.

The GM51104 supports a synchronous output enable control (1G) which switches the outputs into a low state when 1G is low.

The GM51104 operates in a 1.8V & 2.5V & 3.3V, and are characterized for operation from -40°C to 105°C.

#### **Device Information**

| PART NO.    | PACKAGE | BODY SIZE     |

|-------------|---------|---------------|

| GM51104TSOG | TSSOP8  | 3.0mm x 4.4mm |

| GM51104DNG  | DFN8    | 2.0mm x 2.0mm |

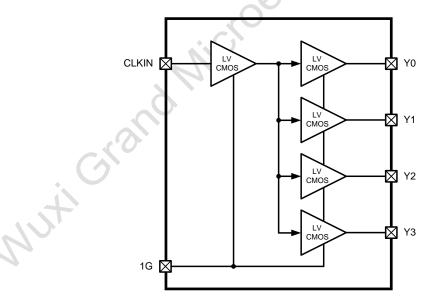

#### **FUNCTION BLOCK DIAGRAM**

Figure 1, Function Block Diagram

## **Revision History**

Note: Page numbers for previous revisions may different from page numbers in the current version.

| VERSION | CHANGE DATE | CHANGE ITEMS                                                                        |

|---------|-------------|-------------------------------------------------------------------------------------|

| V01     | 2024/06     | Initial version completed.                                                          |

| V02     | 2024/06/24  | ESD (Human Body Model) is changed from $\pm 2500 \text{V}$ to $\pm 4000 \text{V}$ . |

|         |             |                                                                                     |

|         |             |                                                                                     |

|         |             |                                                                                     |

|         |             |                                                                                     |

|         |             |                                                                                     |

|         |             | Microelectronics Co., Itid.                                                         |

|         |             | ics Co.                                                                             |

|         |             | chion,                                                                              |

|         |             | : Cloele                                                                            |

|         |             |                                                                                     |

|         | 74 Charl    |                                                                                     |

| N       | 5.7         |                                                                                     |

|         |             |                                                                                     |

|         |             |                                                                                     |

|         |             |                                                                                     |

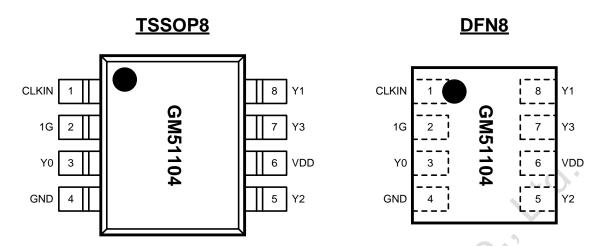

#### **PIN CONFIGURATIONS**

Figure 2, Pin Configurations (Top View)

#### PIN FUNCTION DESCRIPTIONS

|         |            | _      | ***                                                                    |  |  |  |  |  |  |

|---------|------------|--------|------------------------------------------------------------------------|--|--|--|--|--|--|

| PIN NO. | PIN NAME   | TYPE   | DESCRIPTIONS                                                           |  |  |  |  |  |  |

| 1       | CLKIN      | Input  | Single-Ended Clock Input. This pin has an internal pull-down resistor. |  |  |  |  |  |  |

|         |            |        | Output Enable Pin. This pin has an internal pull-down resistor.        |  |  |  |  |  |  |

| 2       | 1G         | Input  | HIGH: Outputs Enabled;                                                 |  |  |  |  |  |  |

|         |            |        | LOW: Outputs Disabled;                                                 |  |  |  |  |  |  |

| 3       | Y0         | Output | LVCMOS Output. Unused outputs can be left floating.                    |  |  |  |  |  |  |

| 4       | GND        | Ground | Power Supply Ground.                                                   |  |  |  |  |  |  |

| 5       | Y2         | Output | LVCMOS Output. Unused outputs can be left floating.                    |  |  |  |  |  |  |

| 6       | VDD        | Power  | Power Supply.                                                          |  |  |  |  |  |  |

| 7       | Y3         | Output | LVCMOS Output. Unused outputs can be left floating.                    |  |  |  |  |  |  |

| 8       | Y1         | Output | LVCMOS Output. Unused outputs can be left floating.                    |  |  |  |  |  |  |

|         | Muti Crand |        |                                                                        |  |  |  |  |  |  |

|         |            |        |                                                                        |  |  |  |  |  |  |

#### **ABSOLUTE MAXIMUM RATINGS**

Permanent device damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum

rating conditions for extended periods may affect device reliability.

| PARAMETER                        | SYMBOL                | RATINGS                         | UNIT |

|----------------------------------|-----------------------|---------------------------------|------|

| Supply Voltage                   | $V_{DD}$              | -0.3 to 3.6                     | V    |

| Input Voltage (CLKIN)            | V <sub>IN</sub>       | -0.3 to (V <sub>DD</sub> + 0.3) | V    |

| Output Enable and Output Voltage | Vo                    | -0.3 to (V <sub>DD</sub> + 0.3) | V    |

| Continuous Output Current        | lo                    | -50 to 50                       | mA   |

| Storage Temperature Range        | T <sub>STG</sub>      | -65 to 150                      | °C   |

| Lead Temperature (solder 4s)     | TL                    | +260                            | °C   |

| Maximum Junction Temperature     | TJ                    | +125                            | °C   |

| ESD (Human Body Model)           | V <sub>ESD_</sub> HBM | ±4000                           | V    |

| ESD (Charged Device Model)       | V <sub>ESD_CDM</sub>  | ±1000                           | V    |

## RECOMMENDED OPERATING CONDITIONS

| PARAMETER                                      | SYMBOL         | MIN   | TYP | MAX   | UNIT  |

|------------------------------------------------|----------------|-------|-----|-------|-------|

| Ambient Temperature                            | T <sub>A</sub> | -40   | 25  | 105   | °C    |

| Supply Voltage (1.8V Supply)                   |                | 1.71  | 1.8 | 1.89  |       |

| Supply Voltage (2.5V Supply)                   | $V_{DD}$       | 2.375 | 2.5 | 2.625 | V     |

| Supply Voltage (3.3V Supply)                   |                | 3.135 | 3.3 | 3.465 |       |

| CLKIN Input Slew Rate                          |                | 1     |     | 4     | V/ns  |

| LVCMOS Clock Input Frequency (2.5&3.3V Supply) | f              | DC    |     | 250   | NALI- |

| LVCMOS Clock Input Frequency (1.8V Supply)     | fclk           | DC    |     | 200   | MHz   |

#### PACKAGE THERMAL RESISTANCE

| PARAMETER                                      | SYMBOL               | RATII  | LINIT |      |

|------------------------------------------------|----------------------|--------|-------|------|

| PARAMETER                                      | SYMBOL               | TSSOP8 | DFN8  | UNIT |

| Thermal resistance from Junction to Ambient    | θја                  | 181.9  | 163   | °C/W |

| Thermal resistance from Junction to Case (top) | θ <sub>JC(top)</sub> | 76.6   | 105.7 | °C/W |

| Thermal resistance from Junction to Board      | θЈВ                  | 111.6  | 84.2  | °C/W |

#### DC ELECTRICAL CHARACTERISTICS

$(V_{DD} = 1.8V \pm 5\%, T_A = -40$ °C to +105°C, Typical Values at  $V_{DD} = 1.8V, T_A = 25$ °C, unless otherwise stated.)

| SYMBOL          | PARAMETER                    | TEST CONDITIONS                                                                      | MIN                      | TYP | MAX                      | UNIT     |

|-----------------|------------------------------|--------------------------------------------------------------------------------------|--------------------------|-----|--------------------------|----------|

| $V_{DD}$        | Operating Voltage            |                                                                                      | 1.71                     | 1.8 | 1.89                     | V        |

| V <sub>IH</sub> | Input High Voltage,<br>CLKIN |                                                                                      | 0.7 x<br>V <sub>DD</sub> |     | $V_{DD}$                 | >        |

| VIL             | Input Low Voltage,<br>CLKIN  |                                                                                      |                          |     | 0.3 x<br>V <sub>DD</sub> | >        |

| V <sub>IH</sub> | Input High Voltage, 1G       |                                                                                      | 1.3                      |     | $V_{DD}$                 | V        |

| VIL             | Input Low Voltage, 1G        |                                                                                      |                          |     | 0.4                      | V        |

| V <sub>OH</sub> | Output High Voltage          | I <sub>OH</sub> = -5mA                                                               | V <sub>DD</sub> – 0.3V   |     |                          | ٧        |

| Vol             | Output Low Voltage           | $I_{OL} = +5mA$                                                                      |                          |     | 0.3                      | <b>V</b> |

| Rout            | Output Impedance             |                                                                                      |                          | 54  |                          | Ω        |

| C <sub>IN</sub> | Input Capacitance,<br>CLKIN  |                                                                                      |                          | 5   |                          | pF       |

| Operating St    | upply Current                |                                                                                      |                          |     |                          |          |

|                 | Static Supply Current        | $1G = V_{DD}$ , CLKIN = $0V$ or $V_{DD}$ .                                           |                          | 13  |                          | μΑ       |

| I <sub>DD</sub> | Active Supply Current        | $1G = V_{DD}$ , All-outputs Active, $f_{CLK} = 100MHz$ , $C_L = 5pF$ , $T_A = 25$ °C | 5                        | 27  |                          | mA       |

| I <sub>PD</sub> | Power-Down Current           | $1G = 0V$ , CLKIN = $0V$ or $V_{DD}$ .                                               |                          | 13  | 50                       | μΑ       |

#### DC ELECTRICAL CHARACTERISTICS

$(V_{DD} = 2.5V \pm 5\%, T_A = -40$ °C to +105°C, Typical Values at  $V_{DD} = 2.5V, T_A = 25$ °C, unless otherwise stated.)

| SYMBOL          | PARAMETER                 | TEST CONDITIONS                                                                      | MIN                    | TYP | MAX                      | UNIT     |

|-----------------|---------------------------|--------------------------------------------------------------------------------------|------------------------|-----|--------------------------|----------|

| $V_{DD}$        | Operating Voltage         |                                                                                      | 2.375                  | 2.5 | 2.625                    | V        |

| ViH             | Input High Voltage, CLKIN | ~(0                                                                                  | $0.7 x$ $V_{DD}$       |     | $V_{DD}$                 | V        |

| VıL             | Input Low Voltage, CLKIN  |                                                                                      |                        |     | 0.3 x<br>V <sub>DD</sub> | ٧        |

| ViH             | Input High Voltage, 1G    |                                                                                      | 1.3                    |     | $V_{DD}$                 | V        |

| $V_{IL}$        | Input Low Voltage, 1G     |                                                                                      |                        |     | 0.4                      | ٧        |

| V <sub>OH</sub> | Output High Voltage       | Iон = -8mA                                                                           | V <sub>DD</sub> – 0.5V |     |                          | V        |

| Vol             | Output Low Voltage        | $I_{OL} = +8mA$                                                                      |                        |     | 0.5                      | <b>V</b> |

| Rout            | Output Impedance          |                                                                                      |                        | 52  |                          | Ω        |

| CIN             | Input Capacitance, CLKIN  |                                                                                      |                        | 5   |                          | рF       |

| Operating St    | upply Current             |                                                                                      |                        |     |                          |          |

|                 | Static Supply Current     | $1G = V_{DD}$ , CLKIN = $0V$ or $V_{DD}$ .                                           |                        | 18  |                          | μΑ       |

| IDD             | Active Supply Current     | $1G = V_{DD}$ , All-outputs Active, $f_{CLK} = 100MHz$ , $C_L = 5pF$ , $T_A = 25$ °C |                        | 27  |                          | mA       |

| I <sub>PD</sub> | Power-Down Current        | $1G = 0V$ , CLKIN = $0V$ or $V_{DD}$ .                                               |                        | 18  |                          | μΑ       |

#### DC ELECTRICAL CHARACTERISTICS

$(V_{DD} = 3.3V \pm 5\%, T_A = -40$ °C to +105°C, Typical Values at  $V_{DD} = 3.3V, T_A = 25$ °C, unless otherwise stated.)

| SYMBOL          | PARAMETER                    | TEST CONDITIONS                                                                      | MIN                      | TYP | MAX                      | UNIT     |

|-----------------|------------------------------|--------------------------------------------------------------------------------------|--------------------------|-----|--------------------------|----------|

| $V_{DD}$        | Operating Voltage            |                                                                                      | 3.135                    | 3.3 | 3.465                    | V        |

| V <sub>IH</sub> | Input High Voltage,<br>CLKIN |                                                                                      | 0.7 x<br>V <sub>DD</sub> |     | $V_{DD}$                 | ٧        |

| VIL             | Input Low Voltage,<br>CLKIN  |                                                                                      |                          |     | 0.3 x<br>V <sub>DD</sub> | V        |

| ViH             | Input High Voltage, 1G       |                                                                                      | 1.6                      |     | $V_{DD}$                 | <b>V</b> |

| $V_{IL}$        | Input Low Voltage, 1G        |                                                                                      |                          |     | 0.4                      | V        |

| $V_{OH}$        | Output High Voltage          | I <sub>OH</sub> = -12mA                                                              | V <sub>DD</sub> – 0.7V   |     |                          | V        |

| Vol             | Output Low Voltage           | I <sub>OL</sub> = +12mA                                                              |                          |     | 0.7                      | <b>V</b> |

| Rout            | Output Impedance             |                                                                                      |                          | 50  |                          | Ω        |

| C <sub>IN</sub> | Input Capacitance,<br>CLKIN  |                                                                                      |                          | 5   |                          | pF       |

| Operating St    | upply Current                |                                                                                      |                          |     |                          |          |

|                 | Static Supply Current        | $1G = V_{DD}$ , CLKIN = $0V$ or $V_{DD}$ .                                           |                          | 24  |                          | μΑ       |

| I <sub>DD</sub> | Active Supply Current        | $1G = V_{DD}$ , All-outputs Active, $f_{CLK} = 100MHz$ , $C_L = 5pF$ , $T_A = 25$ °C | 5                        | 45  |                          | mA       |

| I <sub>PD</sub> | Power-Down Current           | $1G = 0V$ , CLKIN = $0V$ or $V_{DD}$ .                                               |                          | 24  |                          | μΑ       |

# AC ELECTRICAL CHARACTERISTICS(1)

$(V_{DD} = 1.8V \pm 5\%, T_A = -40$ °C to +105°C, Typical Values at  $V_{DD} = 1.8V, T_A = 25$ °C, unless otherwise stated.)

| SYMBOL                          | PARAMETER                                        | TEST CONDITIONS                                      | MIN | TYP | MAX | UNIT   |

|---------------------------------|--------------------------------------------------|------------------------------------------------------|-----|-----|-----|--------|

| f <sub>CLK</sub>                | Input Frequency <sup>(4)</sup>                   |                                                      | 0   |     | 200 | MHz    |

| t <sub>PD</sub>                 | Propagation Delay,<br>CLKIN to Yn <sup>(2)</sup> | C <sub>L</sub> = 5pF                                 |     | 2.5 |     | ns     |

| t <sub>skew</sub>               | Output Skew <sup>(2)</sup>                       | Measured between Outputs Referenced to Y0            |     | 25  | 50  | ps     |

| t <sub>r</sub> / t <sub>f</sub> | Rise and Fall Time                               | 20/80%(VOH - VOL) , C <sub>L</sub> = 5pF             | 0.3 |     | 0.9 | ns     |

| tj                              | RMS Additive Phase<br>Jitter                     | f <sub>CLK</sub> = 156.25MHz,<br>BW = 12KHz to 20MHz |     | 25  |     | fs     |

| O <sub>DC</sub>                 | Output Duty Cycle                                | 50% Input Duty Cycle,<br>f <sub>CLK</sub> = 100MHz   | 45  |     | 55  | %      |

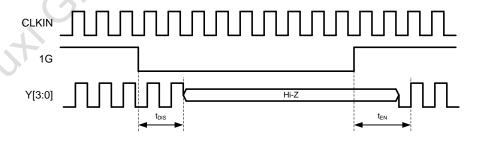

| ten                             | Output Enable Time                               | 1G to Yn, See Figure 3                               |     |     | 6   | cycles |

| tois                            | Output Disable Time                              | 1G to Yn, See Figure 3                               |     |     | 5   | cycles |

# AC ELECTRICAL CHARACTERISTICS(1)

$(V_{DD} = 2.5V \pm 5\%, T_A = -40$ °C to +105°C, Typical Values at  $V_{DD} = 2.5V, T_A = 25$ °C, unless otherwise stated.)

| SYMBOL                          | PARAMETER                                     | TEST CONDITIONS                                      | MIN | TYP | MAX | UNIT   |

|---------------------------------|-----------------------------------------------|------------------------------------------------------|-----|-----|-----|--------|

| fclk                            | Input Frequency <sup>(4)</sup>                |                                                      | 0   |     | 250 | MHz    |

| t <sub>PD</sub>                 | Propagation Delay, CLKIN to Yn <sup>(2)</sup> | C <sub>L</sub> = 5pF                                 |     | 2.5 |     | ns     |

| t <sub>skew</sub>               | Output Skew <sup>(2)</sup>                    | Measured between Outputs<br>Referenced to Y0         |     | 25  | 50  | ps     |

| t <sub>r</sub> / t <sub>f</sub> | Rise and Fall Time                            | 20/80%(VOH - VOL) , C <sub>L</sub> = 5pF             | 0.3 |     | 0.9 | ns     |

| tj                              | RMS Additive Phase Jitter                     | f <sub>CLK</sub> = 156.25MHz,<br>BW = 12KHz to 20MHz |     | 22  |     | fs     |

| O <sub>DC</sub>                 | Output Duty Cycle                             | 50% Input Duty Cycle, fclk = 100MHz                  | 45  |     | 55  | %      |

| t <sub>EN</sub>                 | Output Enable Time                            | 1G to Yn, See Figure 3                               |     |     | 6   | cycles |

| t <sub>DIS</sub>                | Output Disable Time                           | 1G to Yn, See Figure 3                               |     |     | 5   | cycles |

# AC ELECTRICAL CHARACTERISTICS(1)

$(V_{DD} = 3.3V \pm 5\%, T_A = -40$ °C to +105°C, Typical Values at  $V_{DD} = 3.3V, T_A = 25$ °C, unless otherwise stated.)

| SYMBOL                          | PARAMETER                                        | TEST CONDITIONS                                      | MIN | TYP | MAX | UNIT   |

|---------------------------------|--------------------------------------------------|------------------------------------------------------|-----|-----|-----|--------|

| f <sub>CLK</sub>                | Input Frequency <sup>(4)</sup>                   |                                                      | 0   |     | 250 | MHz    |

| <b>t</b> PD                     | Propagation Delay,<br>CLKIN to Yn <sup>(2)</sup> | C <sub>L</sub> = 5pF                                 |     | 2.5 |     | ns     |

| t <sub>skew</sub>               | Output Skew <sup>(2)</sup>                       | Measured between Outputs Referenced to Y0            |     | 25  | 50  | ps     |

| t <sub>r</sub> / t <sub>f</sub> | Rise and Fall Time                               | 20/80%(VOH - VOL) , C <sub>L</sub> = 5pF             | 0.3 |     | 0.9 | ns     |

| tj                              | RMS Additive Phase<br>Jitter                     | f <sub>CLK</sub> = 156.25MHz,<br>BW = 12KHz to 20MHz |     | 18  |     | fs     |

| O <sub>DC</sub>                 | Output Duty Cycle                                | 50% Input Duty Cycle,<br>f <sub>CLK</sub> = 100MHz   | 45  |     | 55  | %      |

| ten                             | Output Enable Time                               | 1G to Yn, See Figure 3                               |     |     | 6   | cycles |

| t <sub>DIS</sub>                | Output Disable Time                              | 1G to Yn, See Figure 3                               |     |     | 5   | cycles |

- AC Parameters for CMOS are dependent upon output capacitive loading.

- 2) 3) 4)

- Parameter is specified by design, not tested in production.

Part-to-part skew is calculated as the difference between the fastest and slowest  $t_{PD}$  across multiple devices.

- Specified by characterization.

Figure 3, Output Timing Diagram

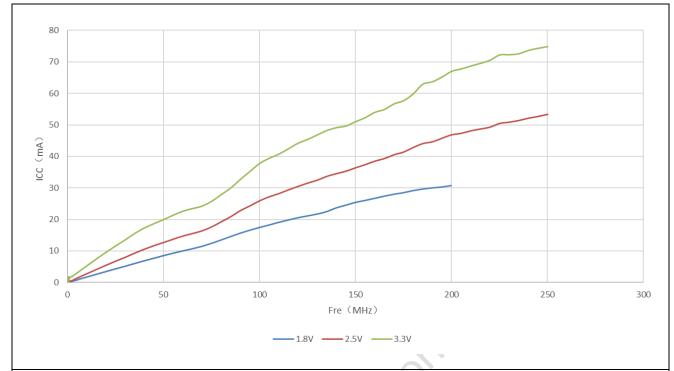

# TYPICAL CHARACTERISTICS

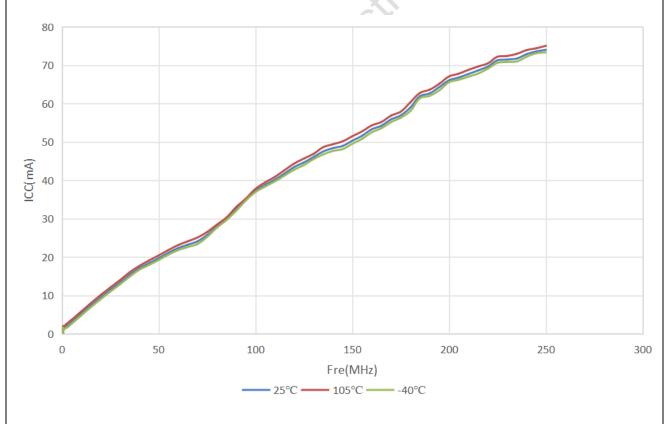

Figure 4, Device Power Consumption vs. Clock Frequency ( $C_L = 5pF$ ) of GM51104 @25 $^{\circ}$ C

Figure 5, Device Power Consumption vs. Clock Frequency (C<sub>L</sub> = 5pF) of GM51104 @VDD=3.3V

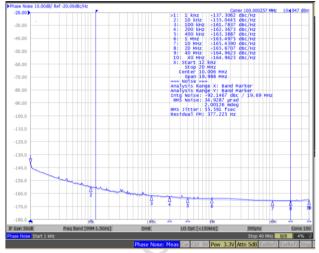

#### **Additive Phase Jitter**

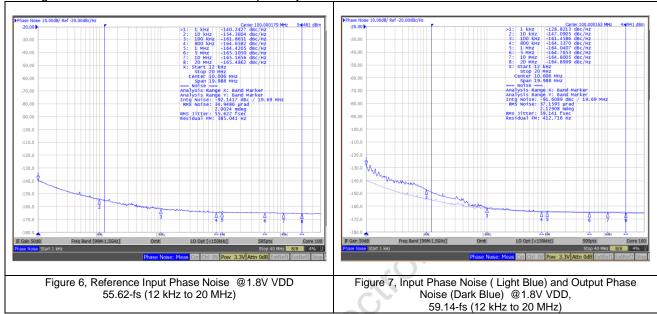

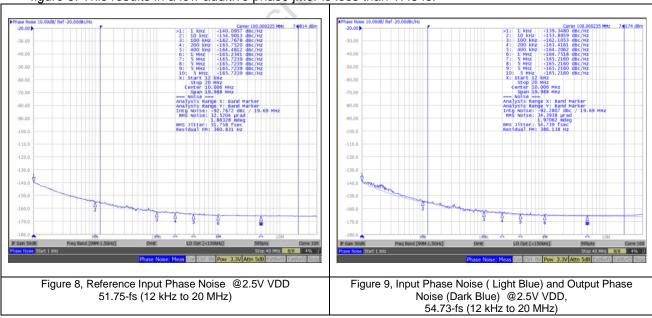

The additive phase jitter for this device was measured using a CRYSTEK CVHD-950X\_100MHz as an input source and Keysight E5052B phase noise analyzer at room temperature.

■ With an integration range of 12kHz to 20MHz (VDD is 1.8V), the reference input has about 55.62 fs of RMS phase jitter shown in figure 6, and the output of GM51104 has about 59.14 fs of RMS jitter shown in figure 7. This results in a low additive phase jitter is less than 20.1 fs.

■ With an integration range of 12kHz to 20MHz (VDD is 2.5V), the reference input has about 51.75 fs of RMS phase jitter shown in figure 8, and the output of GM51104 has about 54.73fs of RMS jitter shown in figure 9. This results in a low additive phase jitter is less than 17.8 fs.

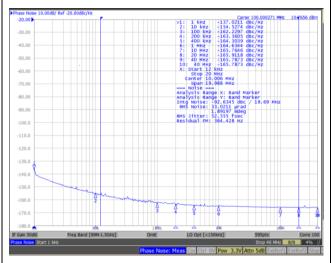

■ With an integration range of 12kHz to 20MHz (VDD is 3.3V), the reference input has about 52.55 fs of RMS phase jitter shown in figure 8, and the output of GM51104 has about 55.59fs of RMS jitter shown in figure 9. This results in a low additive phase jitter is less than 18.13 fs.

Figure 10, Reference Input Phase Noise @3.3V VDD 52.55-fs (12 kHz to 20 MHz)

Figure 11, Figure 11,

Figure 11, Input Phase Noise (Light Blue) and Output Phase Noise (Dark Blue) @3.3V VDD, 55.59-fs (12 kHz to 20 MHz)

#### **FUNCTIONAL DESCRIPTION**

#### Overview

The GM51104 is a low additive jitter LVCMOS buffer solution that can operate up to 250 MHz at  $V_{DD} = 3.3V \& 2.5V$  and 200 MHz at  $V_{DD} = 1.8V$ . The outputs of the GM51104 can be disabled by driving the synchronous output enable pin (1G) low. Unused outputs can be left floating with a minimum copper length to minimize capacitance. In this way, this output will consume minimal output current because it has no load.

#### ■ Output Enable Pin

When the output enable pin 1G is held High, the outputs are enabled. When it is held Low, the outputs are held in a Low state. The 1G pin is synchronized to the input clock to ensure that there are no runt pulses. When 1G is changed from Low to High, the outputs will initially have an impedance of about  $400\Omega$  to ground until the second falling edge of the input clock. Starting with the second falling edge of the input clock, the outputs will buffer the input. If the 1G pin is taken from Low to High when there is no input clock present, the outputs will either go High or Low and stay at that state; they will not oscillate. When the 1G pin is taken from High to Low, the outputs will become Low after the second falling edge of the clock input and then will go to a Disabled (Hi-Z) state starting after the next rising edge.

#### Device Function Modes

Table 1 shows the output logics of the GM51104.

Muti Craind N

| Inpu  | Outputs |    |  |

|-------|---------|----|--|

| CLKIN | 1G      | Yn |  |

| X     | _       | L  |  |

| L     | H       | L  |  |

| Н     | H       | Н  |  |

Table 1, Output Logic Table

#### APPLICATION INFORMATION

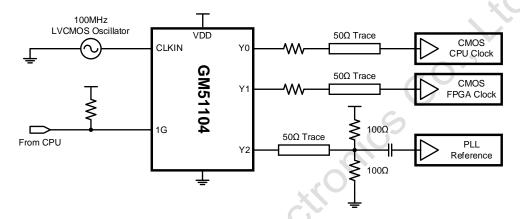

#### ■ Typical Application

The GM51104 shown in Figure 12 is configured to fan out a 100MHz signal from a local LVCMOS oscillator. The CPU is configured to control the output state through 1G. The configuration example is driving three LVCMOS receivers in a backplane application with the following properties:

- The CPU clock can accept a full swing DC-coupled LVCMOS signal. A series resistor is placed near the GM51104 to closely match the characteristic impedance of the trace to minimize reflections.

- The FPGA clock is similarly DC-coupled with an appropriate series resistor placed near the GM51104.

- The PLL in this example can accept a lower amplitude signal, so a Thevenin's equivalent termination is used. The PLL receiver features internal biasing, so AC-coupling can be used when common-mode voltage is mismatched.

Figure 12, Typical Application Diagram

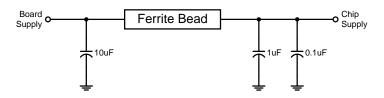

#### Power Supply Recommendations

High-performance clock buffers are sensitive to noise on the power supply, which can dramatically increase the additive jitter of the buffer. Thus, it is essential to reduce noise from the system power supply, especially when the jitter and phase noise is critical to applications. Filter capacitors are used to eliminate the low-frequency noise from the power supply, where the bypass capacitors provide the very low impedance path for high-frequency noise and guards the power supply system against induced fluctuations. These bypass capacitors also provide instantaneous current surges as required by the device and should have low equivalent series resistance (ESR). To properly use the bypass capacitors, they must be placed very close to the power-supply terminals and laid out with short loops to minimize inductance. It is recommended to add as many high-frequency (for example, 0.1µF) bypass capacitors, as there are supply terminals in the package. It is recommended, but does not require, to insert a ferrite bead between the board power supply and the chip power supply that isolates the high-frequency switching noises generated by the clock buffer; these beads prevent the switching noise from leaking into the board supply. It is imperative to choose an appropriate ferrite bead with very low DC resistance to provide adequate isolation between the board supply and the chip supply, as well as to maintain a voltage at the supply terminals that is greater than the minimum voltage required for proper operation.

Figure 13 shows this recommended power supply decoupling method.

Figure 13, Power Supply Decoupling

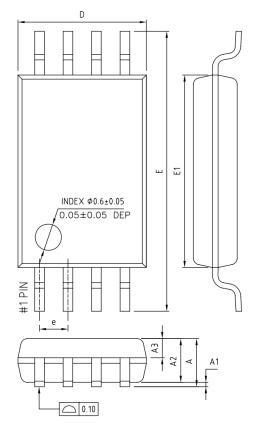

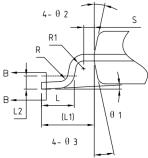

# **PACKAGE OUTLINE (TSSOP8)**

COMMON DIMENSIONS (UNITS OF MEASURE=MILLIMETER)

| SYMBOL  | MIN     | NOM     | MAX         |  |

|---------|---------|---------|-------------|--|

| Α       | _       | -       | 1.20        |  |

| A1      | 0.05    | _       | 0.15        |  |

| A2      | 0.90    | 1.00    | 1.05        |  |

| A3      | 0.34    | 0.44    | 0.54        |  |

| b       | 0.20    | -       | 0.28        |  |

| b1      | 0.20    | 0.22    | 0.24        |  |

| С       | 0.10    | _       | 0.19        |  |

| c1      | 0.10    | 0.13    | 0.15        |  |

| D<br>E  | 2.83    | 2.93    | 3.03        |  |

| Ε       | 6.20    | 6.40    | 6.60        |  |

| E1      | 4.30    | 4.40    | 4.50        |  |

| е       |         | 0.65BSC |             |  |

| L<br>L1 | 0.45    | 0.60    | 0.75        |  |

| L1      |         | 1.00REF |             |  |

| L2      |         | 0.25BSC |             |  |

| R       | 0.09    | _       | -           |  |

| R1      | R1 0.09 |         | _           |  |

| S       | 0.20    | _       | -           |  |

| θ 1     | 0.      | -       | 8*          |  |

| θ 2     | 10°     | 12°     | 14 <b>°</b> |  |

| θ 3     | 10°     | 12°     | 14 <b>°</b> |  |

|         |         |         |             |  |

SECTION B-B

#### NOTES:

ALL DIMENSIONS REFER TO JEDEC STANDARD MO-153 DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

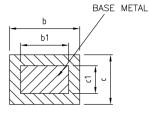

# **PACKAGE OUTLINE (DFN8-2x2)**

SIDE VIEW

|                  | е           | 2 1 |

|------------------|-------------|-----|

|                  | BOTTOM VI   | EW  |

| Wsc - Section A- | ∄<br>Ţ<br>A |     |

| SYMBOL     | MILLIMETER    |         |       |  |  |

|------------|---------------|---------|-------|--|--|

| STMBOL     | MIN           | NOM     | MAX   |  |  |

| A          | 0.70          | 0.75    | 0.80  |  |  |

| A1         | 0             | 0.02    | 0.05  |  |  |

| b          | 0. 18         | 0.25    | 0.30  |  |  |

| <b>b</b> 1 |               | 0.18REF |       |  |  |

| c          | 0.203REF      |         |       |  |  |

| D          | 1.90 2.00 2.1 |         |       |  |  |

| e          | 0. 50BSC      |         |       |  |  |

| Nd         | 1. 50BSC      |         |       |  |  |

| E          | 1. 90         | 2.00    | 2. 10 |  |  |

| L          | 0.45          | 0.50    | 0.55  |  |  |

| h          | 0.10          | 0. 15   | 0. 20 |  |  |

| Wsc        | 0.01          | -       | 0.09  |  |  |

| tsc        | 0.08 -        |         | 0. 18 |  |  |

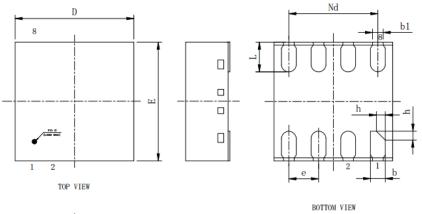

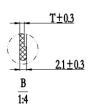

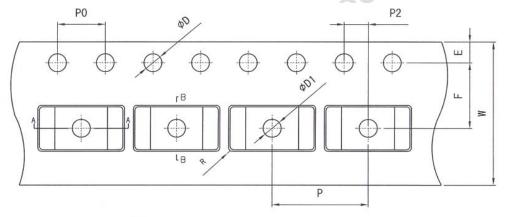

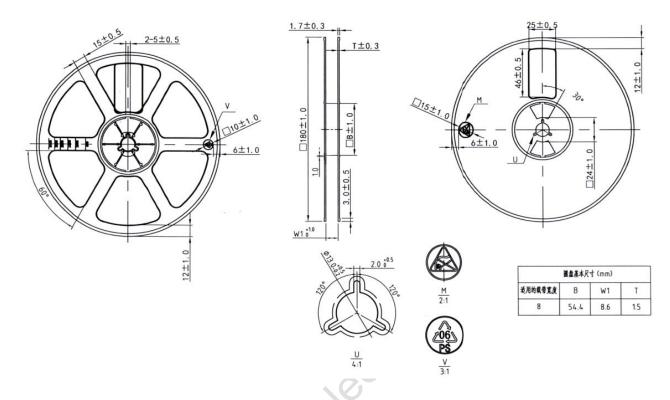

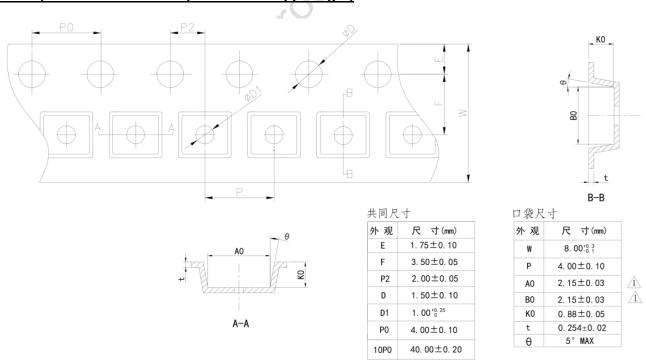

# **TAPE AND REEL INFORMATION OF GM51104TSOG**

#### REEL (13 Inch)

| 型号规格企       | 匹配的     | 基本尺寸 (mm) |     |            |       |     |              |

|-------------|---------|-----------|-----|------------|-------|-----|--------------|

| 望节观俗/公      | 载带宽度    | A         | В   | <b>W</b> 1 | W2Max | T   | D            |

| 13" -12×100 | 12/12.2 |           |     | 12.4       | 18.4  | A   | <u>^</u> \$\ |

| 13" -16×100 | 16      | 330       | 100 | 16.4       | 22.4  | 1.5 | 270          |

| 13" -24×100 | 24      |           |     | 24.4       | 30.4  |     |              |

#### TAPE (Pin 1 orientation in tape locates at upper left)

| 外观   | 尺寸(mm)                |

|------|-----------------------|

| Е    | $1.75\pm0.1$          |

| F    | $5.5\pm0.05$          |

| P2   | $2.0\pm0.05$          |

| D    | 1. 5+0,1              |

| D1   | 1. 5 <sup>+0. 1</sup> |

| P0   | $4.0\pm0.1$           |

| R    | 0. 5TYP               |

| 10P0 | $40.0\pm0.20$         |

口袋尺寸  $12.0\pm0.1$ 8.0±0.1  $6.9\pm0.1$ A0  $3.4\pm0.1$  $1.2\pm0.1$ ВО 1  $0.3 \pm 0.05$  $1.6\pm 0.1$ K1 A1 A2 AA  $3.8 \pm 0.1$ 4. 4±0. 1 3° TYP Δ

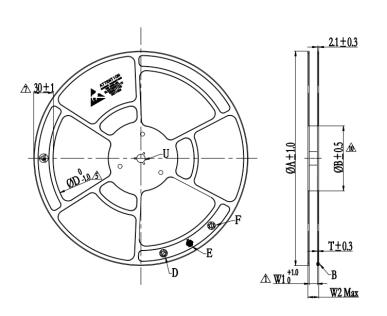

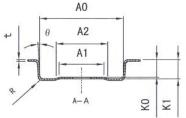

## TAPE AND REEL INFORMATION OF GM51104DNG

#### REEL (7 Inch)

#### TAPE (Pin 1 orientation in tape locates at upper right)

# 产品订购信息

| 244位旦            |                                                                          | 工作组会共用           | <b>北水产</b> 白 | (日 <i>朱</i> ) (年) (日 | 环况产与            | 有块子汁                 |

|------------------|--------------------------------------------------------------------------|------------------|--------------|----------------------|-----------------|----------------------|

| 器件编号             | 产品丝印                                                                     | 工作温度范围           | 封装信息         | 湿敏等级                 | 环保信息            | 包装方法                 |

| GM51104TSOG      | 51104<br>XXXXX <sup>(1)</sup><br>YYWW <sup>(2)</sup> Z <sup>(3)</sup>    | -40°C 至 +105°C   | TSSOP8       | MSL-3                | RoHS &<br>Green | 卷带和卷盘<br>(每卷 5000 只) |

| GM51104DNG       | 51104D<br>XXXXXX <sup>(1)</sup><br>YYWW <sup>(2)</sup> ZZ <sup>(3)</sup> | -40°C 至 +105°C   | DFN8-2x2     | MSL-3                | RoHS &<br>Green | 卷带和卷盘<br>(每卷 3000 只) |

| 注: (1) XXXXX 和 X | XXXXXX 表示批次号                                                             | ·。 (2) YY 表示年号,W | /W 表示周号。     | (3) Z 和 ZZ 表:        | 示生产信息。          |                      |

|                  |                                                                          | Micro            | ectic        |                      |                 |                      |

# 单击下面可查看定价,库存,交付和生命周期等信息

>>GrandMicro(有容微)