#### DIFFERENTIAL TRANSCEIVER WITH TRANSIENT VOLTAGE SUPPRESSION

#### description

The HX75LBC184 and HX65LBC184 are differential data line transceivers in the trade-standard footprint of the HX75176 with built-in protection against high-energy noise transients. This feature provides a substantial increase in reliability for better immunity to noise transients coupled to the data cable over most existing devices. Use of these circuits provides a reliable low-cost direct-coupled (with no isolation transformer) data line interface without requiring any external components.

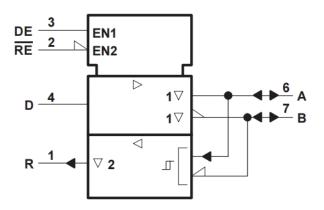

The HX75LBC184 and HX65LBC184 can withstand overvoltage transients of 400-W peak (typical). The conventional combination wave called out in IEC 61000-4-5 simulates the overvoltage transient and models a unidirectional surge caused by overvoltages from switching and secondary lightning transients.

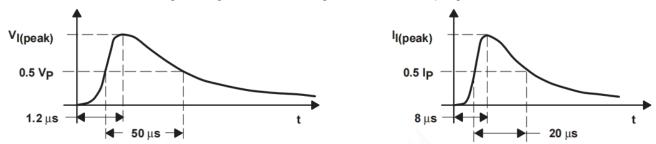

A biexponential function defined by separate rise and fall times for voltage and current simulates the combination wave. The standard 1.2  $\mu$ s/50  $\mu$ s combination waveform is shown in Figure 1 and in the test description in Figure 15.

The device also includes additional desirable features for party-line data buses in electrically noisy environment applications including industrial process control. The differential-driver design incorporates slew-rate-controlled outputs sufficient to transmit data up to 250 kbps. Slew-rate control allows longer unterminated cable runs and longer stub lengths from the main backbone than possible with uncontrolled and faster voltage transitions. A unique receiver design provides a fail-safe output of a high level when the inputs are left floating (open circuit). The HX75LBC184 and HX65LBC184 receiver also includes a high input resistance equivalent to one-fourth unit load allowing connection of up to 128 similar devices on the bus.

The HX75LBC184 is characterized for operation from 0°C to 70°C. The HX65LBC184 is characterized from -40°C to 85°C.

#### Features

- Integrated Transient Voltage Suppression

- ESD Protection for Bus Terminals Exceeds:

- ±30 kV IEC 61000-4-2, Contact Discharge

- ±15 kV IEC 61000-4-2, Air-Gap Discharge

- ±15 kV EIA/JEDEC Human Body Model

- Circuit Damage Protection of 400-W Peak (Typical) Per IEC 61000-4-5

- Controlled Driver Output-Voltage Slew Rates Allow Longer Cable Stub Lengths

- 250-kbps in Electrically Noisy Environments

- Open-Circuit Fail-Safe Receiver Design

- 1/4 Unit Load Allows for 128 Devices Connected on Bus

- Thermal Shutdown Protection

- Power-Up/-Down Glitch Protection

- Each Transceiver Meets or Exceeds the Requirements of TIA/EIA-485 (RS-485)

- and ISO/IEC 8482:1993(E) Standards

- Low Disabled Supply Current 300 µA Max

- Pin Compatible With HX75176

- Applications:

- Industrial Networks

- Utility Meters

- Motor Control

# **ORDERING INFORMATION**

| DEVICE        | Package Type | MARKING | Packing | Packing Qty  |

|---------------|--------------|---------|---------|--------------|

| HX65LBC184PG  | DIP8         | 6LB184  | TUBE    | 2000pcs/box  |

| HX65LBC184DRG | SOP8         | 6LB184  | REEL    | 2500pcs/reel |

| HX75LBC184PG  | DIP8         | 7LB184  | TUBE    | 2000pcs/box  |

| HX75LBC184DRG | SOP8         | 7LB184  | REEL    | 2500pcs/reel |

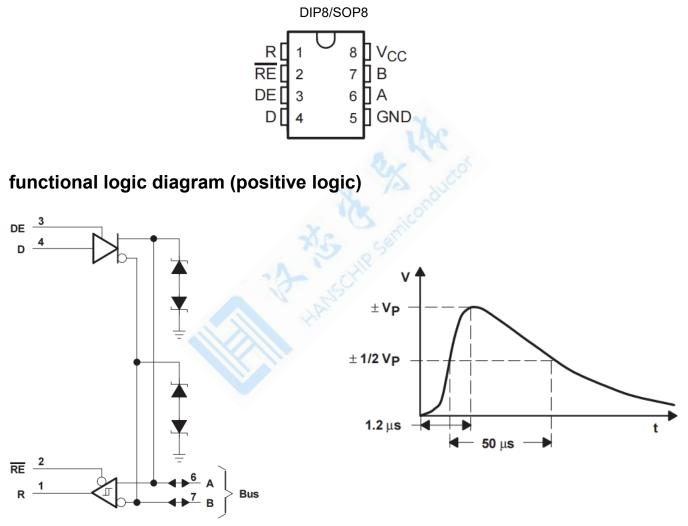

## **PIN ASSIGNMENT**

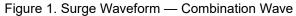

## schematic of inputs and outputs

## **DRIVER FUNCTION TABLE**

| INPUT | ENABLE | OUTPUTS |   |  |  |  |

|-------|--------|---------|---|--|--|--|

| D     | DE     | A       | В |  |  |  |

| Н     | H X L  | H S     | L |  |  |  |

| L     | H      | RL.     | Н |  |  |  |

| X     |        | Z       | Z |  |  |  |

H = high level, L = low level, ? = indeterminate,

X = irrelevant, Z = high impedance (off)

# **RECEIVER FUNCTION TABLE**

| DIFFERENTIAL INPUTS     | ENABLE | OUTPUT |

|-------------------------|--------|--------|

| A – B                   | RE     | R      |

| V <sub>ID</sub> ≥ 0.2 V | L      | Н      |

| $-0.2 V < V_D < 0.2 V$  | L      | ?      |

| VID < -0.2 V            | L      | L      |

| X                       | Н      | Z      |

| Open                    | L      | Н      |

H = high level, L = low level, ? = indeterminate,

X = irrelevant, Z = high impedance (off)

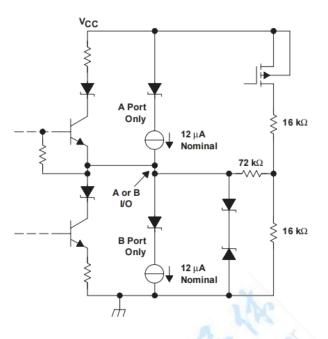

# logic symbol†

† This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Condition                                          | Min       | Мах       |

|----------------------------------------------------|-----------|-----------|

| Supply voltage, VCC (see NOTE 1)                   | -0.5V     | 7V        |

| Continuous voltage range at ant bus terminal       | -15V      | 15V       |

| Data input/output voltage                          | -0.3V     | 7V        |

| Receiver outputn current,IQ                        | -20mA     | +20mA     |

| Electrostatic discharge:                           | 100       | -         |

| Contact discharge (IEC1000-4-2)A,B,GND(see Note 2) | -         | 30KV      |

| Air discharge (IEC61000-4-2)A,B,GND(see Note 2)    | all'in    | 15KV      |

| Human body model (see Note 3)A,B,GND(see Note 2)   |           | 15KV      |

| All pins                                           | -         | 3KV       |

| All terminals (Class 3A)(see Note 2)               | -         | 8KV       |

| All terminals(Class 3B)(see Note 2)                | -         | 1200V     |

| Continuous total power dissipation(see Note 4)     | Internall | y Limited |

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. NOTES: 1. All voltage values, except differential input/output bus voltage, are with respect to network ground terminal.

2. GND and bus terminal ESD protection is beyond readily available test equipment capabilities for IEC 61000-4-2, EIA/JEDEC test method A114-A and MIL-STD-883C method 3015. Ratings listed are limits of test equipment; device performance exceeds these limits.

3. Tested in accordance with JEDEC Standard 22, Test Method A114-A.

4. The driver shuts down at a junction temperature of approximately 160°C. To operate below this temperature, see the Dissipation Rating Table.

## **DISSIPATION RATING TABLE**

| PACKAGE | TA ≤ 25℃ POWER<br>RATING | DERATING FACTOR<br>ABOVE TA = 25℃ | TA = 70°C POWER<br>RATING | TA = 85°C POWER<br>RATING |

|---------|--------------------------|-----------------------------------|---------------------------|---------------------------|

| N       | 725 mW                   | <b>5.8 mW/°</b> ℃                 | 464 mW                    | 377 mW                    |

| М       | 1150 mW                  | <b>9.2 mW/</b> ℃                  | 736 mW                    | 598 mW                    |

### recommended operating conditions

|                                    |                                             | MIN‡ | TYP | MAX  | UNIT |

|------------------------------------|---------------------------------------------|------|-----|------|------|

| 5                                  | Supply voltage, VCC                         | 4.75 | 5   | 5.25 | V    |

| Voltage at any bus termin          | nal (separately or common mode), VI or VIC  | -7   |     | 12   | V    |

| High-level input voltage, VIH      | High-level input voltage, VIH D, DE, and RE |      |     |      | V    |

| Low-level input voltage, VIL       | D, DE, and RE                               |      | 0.8 |      | V    |

| Differ                             | Differential input voltage,  VID            |      |     |      | V    |

| High lovel output ourrent lou      | Driver                                      | -60  |     |      | mA   |

| High-level output current, IOH     | Receiver                                    |      | -8  |      | mA   |

|                                    | Driver                                      |      | 60  |      |      |

| Low-level output current, IOL      | Low-level output current, IOL Receiver      |      | 4   |      | mA   |

|                                    | HX75LBC184                                  |      |     | 70   | °C   |

| Operating free-air temperature, TA | HX65LBC184                                  | -40  |     | 85   | °C   |

‡ The algebraic convention, in which the less-positive (more-negative) limit is designated minimum, is used in this data sheet.

## **DRIVER SECTION**

### electrical characteristics over recommended operating conditions (unless otherwise noted)

|                          | PARAMETER                                                                         | ALTERNATE<br>SYMBOLS              | TEST CONDITIONS                | MIN TYPT       | мах | UNIT |

|--------------------------|-----------------------------------------------------------------------------------|-----------------------------------|--------------------------------|----------------|-----|------|

|                          |                                                                                   |                                   | DE = RE = 5 V, No Load         | 12             | 25  | mA   |

| ICC                      | Supply current                                                                    | NA                                | DE = 0 V,<br>No Load RE = 5 V, | 175            | 300 | μΑ   |

| ЧΗ                       | High-level input current (D, DE, RE)                                              | NA                                | VI = 2.4 V                     | 50             |     | μΑ   |

| Ι <sub>Ι</sub> Γ         | Low-level input current (D, DE, RE)                                               | NA                                | VI = 0.4 V                     | -50            |     | μΑ   |

|                          |                                                                                   | -1-                               | Vo = -7 V                      | -250 -120      |     |      |

| los                      | Short-circuit output current<br>(see Note 5)                                      | NA                                | NO = ACC                       | 250            |     | mA   |

|                          | (See Note 3)                                                                      | NA.                               | Vo = 12 V                      | 250            |     |      |

| IOZ                      | High-impedance output current                                                     | NA                                |                                | See Receiver I |     | mA   |

| Vo                       | Output voltage                                                                    | Voa, Vob                          | IO = 0                         | 0              | VCC | V    |

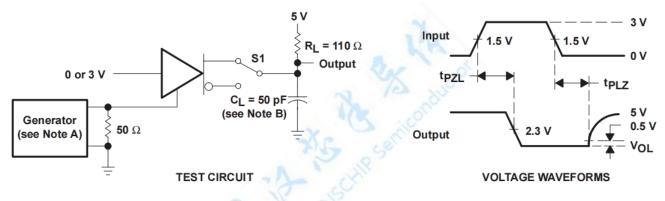

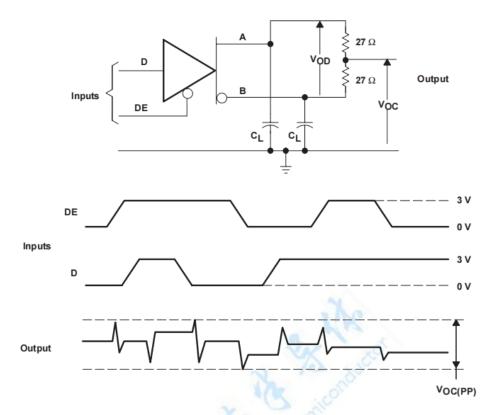

| V <sub>OC(PP)</sub>      | Peak-to-peak change in common-<br>mode output voltage during state<br>transitions | NA                                | See Figures 5 and 6            | 0.8            |     | V    |

| Voc                      | Common-mode output voltage                                                        | V <sub>os</sub>                   | See Figure 4                   | 1              | 3   | V    |

| ∆V <sub>OC</sub><br>(SS) | Magnitude of change, common-<br>mode steady-state output voltage                  | V <sub>os</sub> — V <sub>os</sub> | See Figure 5                   | 0.1            |     | V    |

| Vod                      | Magnitude of differential output                                                  | Vo                                | I <sup>O</sup> = 0             | 1.5<br>6       |     | V    |

|                          | voltage ∣VA — \⁄B∣                                                                |                                   | RL = 54 , See Figure 4         | 1.5            |     | V    |

| Vod                      | Change in differential voltage mag-<br>nitude between logic states                | $  V_t  -  V_t  $                 | RL = 54                        | 0.1            |     | V    |

† All typical values are measured with TA = 25  $^\circ\!\!\mathbb{C}$  and VCC = 5 V.

NOTE 5: This parameter is measured with only one output being driven at a time.

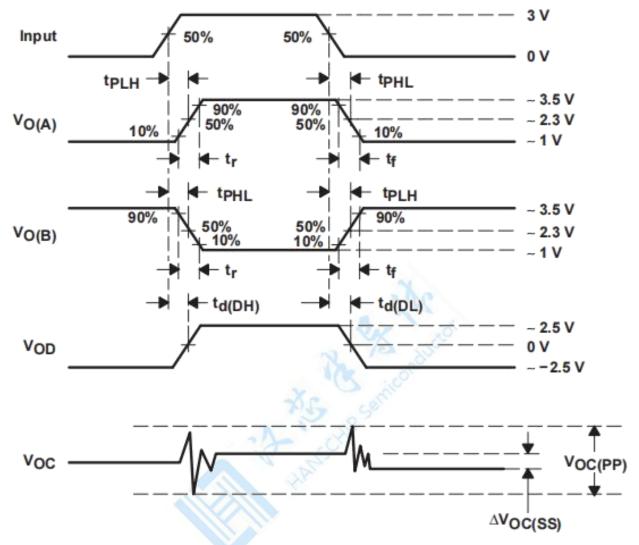

## switching characteristics over recommended operating conditions

### (unless otherwise noted)

|                    | PARAMETER                                                | TEST CO          | NDITIONS                | MIN  | TYP | MAX | UNIT |

|--------------------|----------------------------------------------------------|------------------|-------------------------|------|-----|-----|------|

| <sup>t</sup> d(DH) | Differential output delay time, low-to-high-level output |                  |                         |      | 1.3 |     | μs   |

| <sup>t</sup> d(DL) | Differential-output delay time, high-to-low-level output |                  |                         |      | 1.3 |     | μs   |

| <sup>t</sup> PLH   | Propagation delay time, low-to-high-level output         | $P_1 = 54$       |                         |      | 0.5 | 1.3 | μs   |

| <sup>t</sup> PHL   | Propagation delay time, high-to-low-level output         | Γ <u></u> - 34Λ, | C <sub>L</sub> = 50 pF, |      | 0.5 | 1.3 | μs   |

| t <sub>sk(p)</sub> | Pulse skew ( td(DH) — đ(DL) )                            | See Figure 5     |                         |      | 75  | 150 | ns   |

| tr                 | Rise time, single ended                                  |                  |                         | 0.25 |     | 1.2 | μs   |

| tf                 | Fall time, single ended                                  |                  |                         | 0.25 |     | 1.2 | μs   |

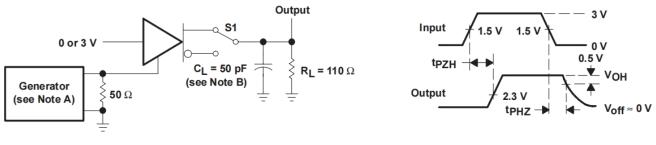

| <sup>t</sup> PZH   | Output enable time to high level                         | RL = 110         | See Figure 2            |      | 3.5 |     | μs   |

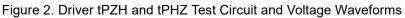

| <sup>t</sup> PZL   | Output enable time to low level                          | RL = 110         | See Figure 3            |      | 3.5 |     | μs   |

| <sup>t</sup> PHZ   | Output disable time from high level                      | RL = 110         | See Figure 2            |      | 2   |     | μs   |

| <sup>t</sup> PLZ   | Output disable time from low level                       | RL = 110         | See Figure 3            |      | 2   |     | μs   |

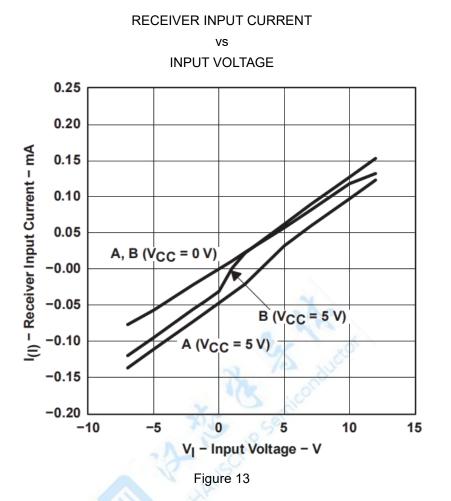

## **RECEIVER SECTION**

#### electrical characteristics over recommended operating conditions (unless otherwise noted)

|                  | PARAMETER                              | TEST C              | ONDITIONS                     | ΜΙΝ ΤΥΡ <sup>†</sup> ΜΑΧ | UNIT |    |

|------------------|----------------------------------------|---------------------|-------------------------------|--------------------------|------|----|

| ICC              | Supply surrent (total package)         | DE = RE = 0 V,      | No Load                       | 3.9                      | mA   |    |

|                  | Supply current (total package)         | RE = 5 V,No Load    | DE = 0 V,                     | 300                      | μA   |    |

|                  |                                        | 0.00                | VI = 12 V                     | 250                      |      |    |

|                  | Input current                          | Other input = 0 V   | VI = 12 V, VCC = 0            | 250                      |      |    |

| "                | I input current                        | iput current        |                               | VI = -7 V                | -200 | μΑ |

|                  |                                        | · //· //·           | $V_{I} = -7 V$ , $V_{CC} = 0$ | -200                     |      |    |

| loz              | High-impedance-state output current    | Vo = 0.4 V to 2.4 \ | /                             | 100                      | μΑ   |    |

| V <sub>hys</sub> | Input hysteresis voltage               | a bi                |                               | 70                       | mV   |    |

| VIT+             | Positive-going input threshold voltage | Y                   |                               | 200                      | mV   |    |

| VIT-             | Negative-going input threshold voltage |                     |                               | -200                     | mV   |    |

| Vон              | High-level output voltage              | IOH = - 8 mA        | Figure 7                      | 2.8                      | V    |    |

| VOL              | Low-level output voltage               | IOL = 4 mA          | Figure 7                      | 0.4                      | V    |    |

† All typical values are at VCC = 5 V, TA =  $25^{\circ}$ C.

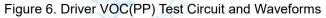

#### switching characteristics over recommended operating conditions (unless otherwise noted)

|                    | PARAMETER                                        | TEST CONDITIONS          | MIN | TYP | MAX | UNIT |

|--------------------|--------------------------------------------------|--------------------------|-----|-----|-----|------|

| <sup>t</sup> PLH   | Propagation delay time, low-to-high-level output | CL = 50 pF, See Figure 7 |     | 150 |     | ns   |

| <sup>t</sup> PHL   | Propagation delay time, high-to-low-level output | CL = 50 pr, See Figure 7 |     | 150 |     | ns   |

| <sup>t</sup> sk(p) | Pulse skew ( t <sub>pHL</sub> — þLH )            |                          |     | 50  |     | ns   |

| tr                 | Rise time, single ended                          | See Figure 7             |     | 20  |     | ns   |

| tf                 | Fall time, single ended                          |                          |     | 20  |     | ns   |

| <sup>t</sup> PZH   | Output enable time to high level                 |                          |     | 100 |     | ns   |

| <sup>t</sup> PZL   | Output enable time to low level                  | Soo Eiguro 9             |     | 100 |     | ns   |

| <sup>t</sup> PHZ   | Output disable time from high level              | See Figure 8             |     | 100 |     | ns   |

| <sup>t</sup> PLZ   | Output disable time from low level               |                          |     | 100 |     | ns   |

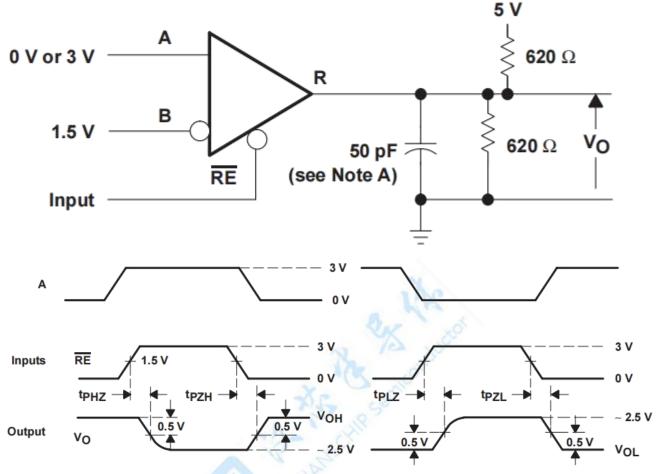

**TEST CIRCUIT**

VOLTAGE WAVEFORMS

NOTES:

A. The input pulse is supplied by a generator having the following characteristics: PRR = 1.25 kHz, 50% duty cycle, tr  $\leq$  10 ns, tf  $\leq$  10 ns, ZO = 50  $\Omega$ .

B. CL includes probe and jig capacitance.

NOTES:

A. The input pulse is supplied by a generator having the following characteristics: PRR = 1.25 kHz, 50% duty cycle, tr  $\leq$  10 ns, tf  $\leq$  10 ns, ZO = 50  $\Omega$ .

B. CL includes probe and jig capacitance.

Figure 3. Driver tPZL and tPLZ Test Circuit and Voltage Waveforms

NOTES:

A. Resistance values are in ohms and are 1% tolerance.

B. CL includes probe and jig capacitance.

#### Figure 4. Driver Test Circuit, Voltage, and Current Definitions

Figure 5. Driver Timing, Voltage and Current Waveforms

#### NOTES:

A. Resistance values are in ohms and are 1% tolerance.

B. CL includes probe and jig capacitance (± 10%).

NOTE A: This value includes probe and jig capacitance ( $\pm$  10%).

Figure 7. Receiver tPLH and tPHL Test Circuit and Voltage Waveforms

NOTE A: This value includes probe and jig capacitance (± 10%).

Figure 8. Receiver tPZL, tPLZ, tPZH, and tPHZ Test Circuit and Voltage Waveforms

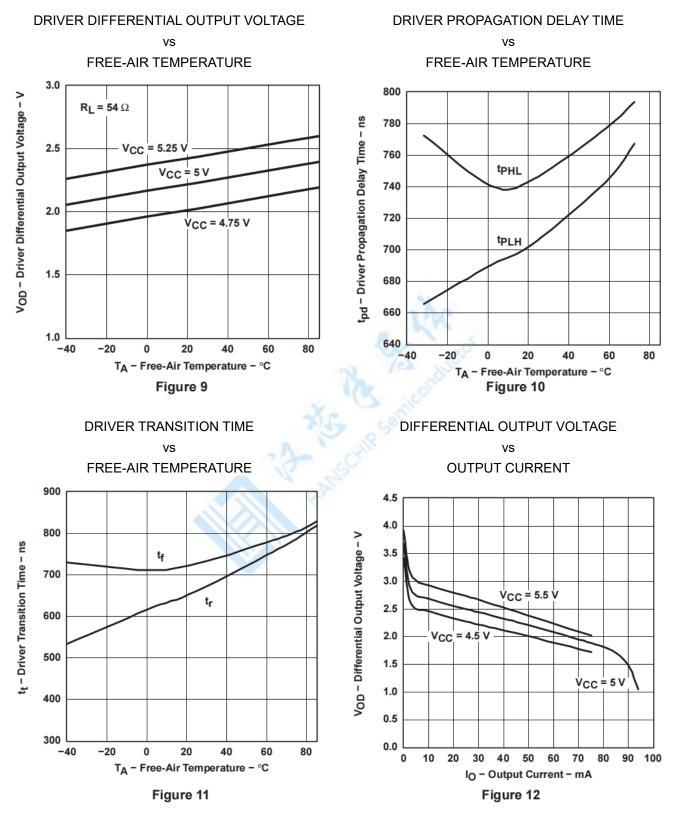

# **TYPICAL CHARACTERISTICS**

## **TYPICAL CHARACTERISTICS**

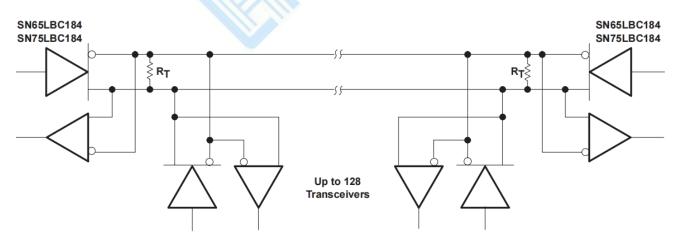

**APPLICATION INFORMATION**

NOTE A: The line should be terminated at both ends in its characteristic impedance (RT = ZO). Stub lengths off the main line should be kept as short as possible.

Figure 14. Typical Application Circuit

## **APPLICATION INFORMATION**

#### 'LBC184 test description

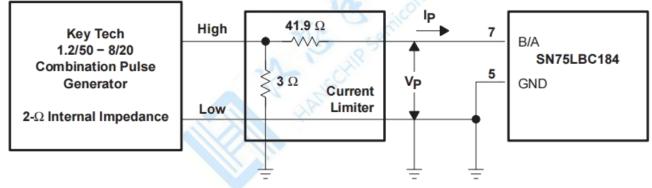

The 'LBC184 is tested against the IEC 61000–4–5 recommended transient identified as the combination wave. The combination wave provides a 1.2-/50- $\mu$ s open-circuit voltage waveform and a 8-/20- $\mu$ s short-circuit current waveform shown in Figure 15. The testing is performed with a combination/hybrid pulse generator with an effective output impedance of 2  $\Omega$ . The setup for the overvoltage stress is shown in Figure 16 with all testing performed with power applied to the 'LBC184 circuit.

#### NOTE

High voltage transient testing is done on a sampling basis.

Figure 15. Short-Circuit Current Waveforms

The 'LBC184 is tested and evaluated for both maximum (single pulse) as well as life test (multiple pulse) capabilities. The 'LBC184 is evaluated against transients of both positive and negative polarity and all testing is performed with the worst-case transient polarity. Transient pulses are applied to the bus pins (A & B) across ground as shown in Figure 16.

Figure 16. Overvoltage-Stress Test Circuit

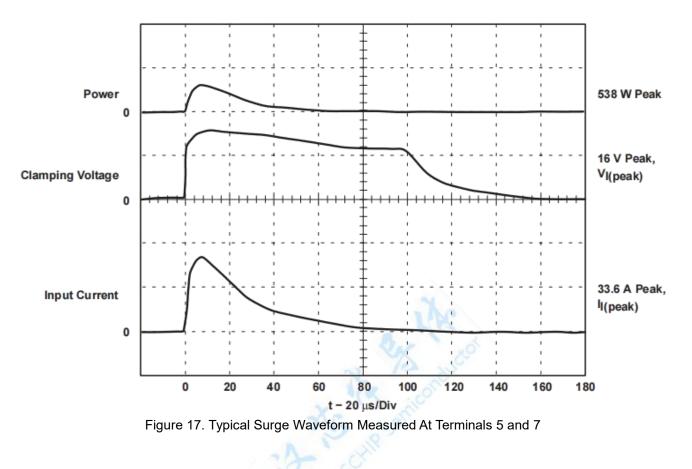

An example waveform as seen by the 'LBC184 is shown in Figure 17. The bottom trace is current, the middle trace shows the clamping voltage of the device and the top trace is power as calculated from the voltage and current waveforms. This example shows a peak clamping voltage of 16 V, peak current of 33.6 A yielding an absorbed peak power of 538 W.

#### NOTE

A circuit reset may be required to ensure normal data communications following a transient noise pulse of greater than 250 W peak.

### **APPLICATION INFORMATION**

# **Physical Dimensions**

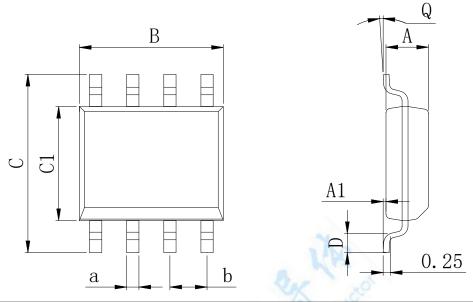

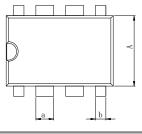

#### SOP8 (150mil)

| Dimensions In M | Dimensions In Millimeters(SOP8) |      |      |      |      |      |    |      |          |  |  |  |

|-----------------|---------------------------------|------|------|------|------|------|----|------|----------|--|--|--|

| Symbol:         | А                               | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |  |  |

| Min:            | 1.35                            | 0.05 | 4.90 | 5.80 | 3.80 | 0.40 | 0° | 0.35 | 1.27 BSC |  |  |  |

| Max:            | 1.55                            | 0.20 | 5.10 | 6.20 | 4.00 | 0.80 | 8° | 0.45 | 1.27 630 |  |  |  |

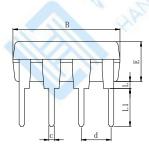

DIP8

#### Dimensions In Millimeters(DIP8L)

0

| Symbol: | А    | В    | D    | D1   | E    | L    | L1   | а    | b    | С    | d        |

|---------|------|------|------|------|------|------|------|------|------|------|----------|

| Min:    | 6.10 | 9.00 | 8.40 | 7.42 | 3.10 | 0.50 | 3.00 | 1.50 | 0.85 | 0.40 | 2.54 BSC |

| Max:    | 6.68 | 9.50 | 9.00 | 7.82 | 3.55 | 0.70 | 3.60 | 1.55 | 0.90 | 0.50 | 2.34 030 |

深圳市汉芯半导体有限公司 http://www.hanschip.com

2022 September

#### **IMPORTANT STATEMENT:**

Shenzhen Hanschip semiconductor co., ltd. reserves the right to change the products and services provided without notice. Customers should obtain the latest relevant information before ordering, and verify the timeliness and accuracy of this information.

Customers are responsible for complying with safety standards and taking safety measures when using our products for system design and machine manufacturing to avoid potential risks that may result in personal injury or property damage.

Our products are not licensed for applications in life support, military, aerospace, etc., so we do not bear the consequences of the application of these products in these fields.

Our documentation is only permitted to be copied without any tampering with the content, so we do not accept any responsibility or liability for the altered documents. 单击下面可查看定价,库存,交付和生命周期等信息

>>HGC(深圳汉芯)