# 2-Kbit I<sup>2</sup>C-compatible Serial EEPROM

### Features

- Supply Voltage Range: 1.7V to 5.5V

- 2-wire Serial Interface I<sup>2</sup>C Compatible

400 kHz and High Speed 1MHz Transfer Rate Compatibility

- Byte and Page (up to 16 Bytes) Write Mode

Partial Page Write Allowed

- Self-timed Write Cycle (3ms Maximum)

- Additional 16-byte Write Lockable Page and 128-bit Unique ID

- Hardware and Software Write Protection on the Whole Memory Array

- Schmitt Trigger, Filtered Inputs for Noise Suppression

- High Reliability

- Endurance: 2,000,000 Write Cycles

- Data Retention: 200 Years

- ESD Protection (Human Body Model): 5000V

- Low Operating Current

- Write Current: 0.5mA (Maximum)

- Read Current: 0.5mA (Maximum)

- Standby Current: 1µA (Maximum)

- Operating Temperature Range: -40°C to +105°C

- Green Packaging Options (RoHS Compliant, Pb/Halogen-free)

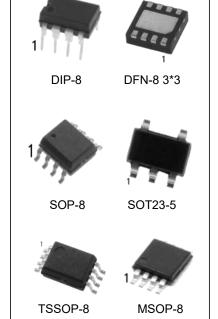

DIP-8/SOP-8/MSOP-8/TSSOP-8/DFN-8/SOT23-5

| DEVICE        | Package Type | MARKING | Packing | Packing Qty  |

|---------------|--------------|---------|---------|--------------|

| AT24C02CN     | DIP-8        | 24C02C  | TUBE    | 2000pcs/box  |

| AT24C02CM/TR  | SOP-8        | 24C02C  | REEL    | 2500pcs/reel |

| AT24C02CMM/TR | MSOP-8       | C02C    | REEL    | 3000pcs/reel |

| AT24C02CDQ/TR | DFN-8        | 24C02C  | REEL    | 2500pcs/reel |

| AT24C02CM5/TR | SOT23-5      | 2CMU    | REEL    | 3000pcs/reel |

| AT24C02CMT/TR | TSSOP-8      | 24C02C  | REEL    | 2500pcs/reel |

### **Ordering Information**

## Description

The AT24C02C is a 2-Kbit I<sup>2</sup> C-compatible serial EEPROM device. The device is designed to operate in a supply voltage range of 1.7V to 5.5V, with a maximum of 1MHz transfer rate, over an operating temperature range of -40°C to +105°C. The device incorporates a Write Protection pin used for hardware Write Protection on the whole memory array. The device also offers a Software Write Protection feature for users to write protect the whole memory array.

The memory array is organized as 16 pages of 16 bytes each, totaling 256\*8 bits. The device offers an additional 16-byte Identification Page for users to store sensitive application parameters. This page can be permanently locked in Read-only mode after the data is written into the Identification Page. The device also

offers a separate memory block (in Read-only mode) containing a factory programmed 128-bit Unique ID and can be accessed to by sending a specific Read command.

The AT24C02C is delivered in lead-free green packages: DIP-8,SOP-8, MSOP-8, DFN-8 and SOT23-5.

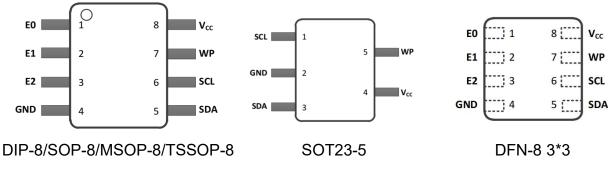

## **Pin Configuration**

## **Pin Descriptions**

| Symbol         | Туре             | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E0<br>E1<br>E2 | Input            | <b>Device Address Inputs:</b> The E0, E1, and E2 pins are device address inputs for compatibility with other 2-wire serial EEPROM devices. These pins can be directly connected to VCC or GND in any combination, allowing up to eight devices on a single bus system. If these pins are left floating, the E0, E1, and E2 pins will be internally pulled down to GND.                                                                                                                                                        |

| SDA            | Input/<br>Output | Serial Data: The SDA pin is an open-drain bidirectional input/output pin used to serially transfer data to and from the device.                                                                                                                                                                                                                                                                                                                                                                                               |

| SCL            | Input            | <b>Serial Clock:</b> The SCL pin is used to provide a clock to the device and is used to control the flow of data to and from the device. Command and input data present on the SDA pin is always latched in on the rising edge of SCL, while output data on the SDA pin is always clocked out on the falling edge of SCL.                                                                                                                                                                                                    |

| vcc            | Power            | <b>Device Power Supply:</b> The VCC pin is used to supply the source voltage to the device. Operations at invalid VCC voltages may produce spurious results and should not be attempted.                                                                                                                                                                                                                                                                                                                                      |

| GND            | Power            | Ground: The ground reference for the power supply. GND should be connected to the system ground.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| WP             | Input            | <b>Write Protection:</b> The WP pin is used to write protect the entire contents of the memory. When the WP pin is connected to Power Supply, the entire memory array becomes Write-protected, that is, the device becomes Read-only. When the WP pin is connected to GND, Write operations are enabled. If the pin is left floating, the WP pin will be internally pulled down to GND. When the WP pin is driven high, the device address byte and the word address bytes are acknowledged, data bytes are not acknowledged. |

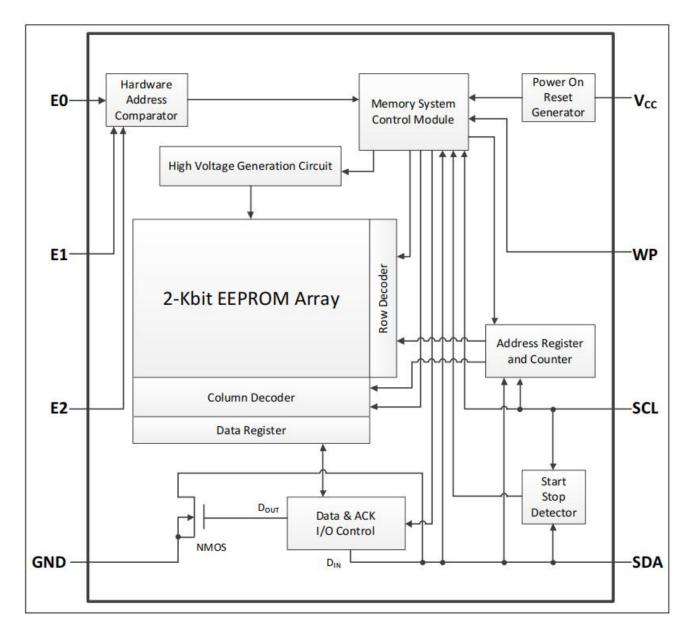

## **Functional Block Diagram**

## **Device Communication**

The AT24C02C operates as a Slave and utilizes a 2-wire serial interface to communicate with the Master. The Master initiates and controls all Read and Write operations to the slave devices on the serial bus, and both the Master and the slave devices can transmit and receive data on the bus.

The serial interface is comprised of just two signal lines: the Serial Clock (SCL) and the Serial Data (SDA). Data is always latched into the AT24C02C on the rising edge of SCL and is always output from the device on the falling edge of SCL. Both the SCL pin and SDA pin incorporate integrated spike suppression filters and Schmitt Triggers to minimize the effects of input spikes and bus noise.

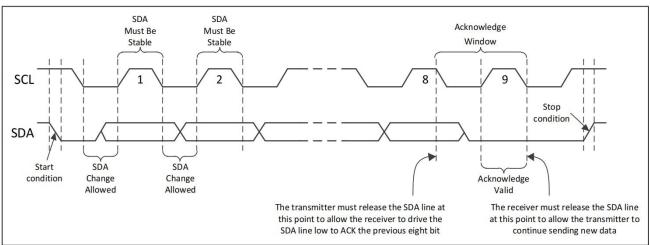

All command and data information is transferred with the Most Significant Bit (MSB) first. During the bus communication, one data bit is transmitted every clock cycle, and after eight bits of data has been transferred, the receiving device must respond with an acknowledge or a no-acknowledge response bit during a ninth clock cycle generated by the Master. Therefore, nine clock cycles are required for every one byte of data transferred. There is no unused clock cycle during any Read or Write operation, so there must not be any interruptions or breaks during the data stream.

During data transfers, data on the SDA pin must only change while SCL is low, and the data must remain stable while SCL is high. If data on the SDA pin changes while SCL is high, then either a Start or a Stop condition will occur. The number of data bytes transferred between a Start and a Stop condition is not limited and is determined by the Master.

## Start Condition

A Start condition occurs when there is a high-to-low transition on the SDA pin while the SCL pin is stable in Logic 1 state. The Start condition must precede any command as the Master uses a Start condition to initiate any data transfer sequence (see **Figure 1**). The AT24C02C will continuously monitor the SDA and SCL pins for a Start condition, and the device will not respond unless one is given.

#### Figure 1 Start, Stop, and ACK

### **Stop Condition**

A Stop condition occurs when there is a low-to-high transition on the SDA pin while the SCL pin is stable in Logic 1 state (see **Figure 1**). A stop condition terminates communication between the device and the Master. A Stop condition at the end of a Write command triggers the EEPROM internal write cycle. Otherwise, the device subsequently returns to Standby mode after receiving a Stop condition.

### Acknowledge (ACK)

After each byte of data is received, the AT24C02C should acknowledge to the Master that it has received the data byte successfully. This is accomplished by the Master first releasing the SDA line and providing the ACK/NACK clock cycle (a ninth clock cycle for every byte). During the ACK/NACK clock cycle, the device must output Logic 0 as ACK for the entire clock cycle so that the SDA line must be stable in Logic 0 state during the entire high period of the clock cycle (see **Figure 1**).

### **Standby Mode**

The AT24C02C features a low-power Standby mode which is enabled:

- (1) Upon power-up;

- (2) After the receipt of a Stop condition in Read operation;

- (3) The completion of any internal operations.

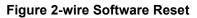

### Software Reset

After an interruption in protocol, power loss, or system reset, any 2-wire part can be reset by following these steps: (1) Create a Start condition; (2) Clock nine cycles; (3) Create another Start condition followed by a Stop condition (see **Figure 2**).

#### **Device Reset and Initialization**

The AT24C02C incorporates a Power-On Reset (POR) circuit to prevent inadvertent operations during power-up. On a cold power-up, the device does not respond to any instructions until the supply voltage reaches the internal power-on reset threshold voltage (VPOR). The supply voltage must rise continuously between VPOR and minimum VCC without any ring back to ensure a proper power-up. Once the supply voltage passes VPOR, the device is reset and enters Standby mode. However, no protocol should be issued to the device until a valid and stable supply voltage is applied. The supply voltage must remain stable and valid until the end of the protocol transmission, and for a Write instruction, until the end of the internal write cycle.

This POR behavior is bi-directional. It protects the AT24C02C against brown-out failure caused by a temporary loss of power. In a similar way, as soon as the supply voltage drops below the internal brown-out reset threshold voltage (VBOR), the device is reset and stops responding to any instructions.

### **Data Security**

The AT24C02C incorporates a hardware data protection feature that allows the user to write protect the whole memory array (and Identification Page) when the WP pin is connected directly to VCC.

The AT24C02C also offers a Software Write Protection (SWP) feature that allows the user to write protect the whole memory array (and Identification Page) when the internal non-volatile SWP bit is set to Logic 1.

## **Device Addressing**

The AT24C02C requires a 7-bit device address and a Read/Write select bit following a Start condition from the Master to initiate communication with the serial EEPROM. The device address byte is comprised of a 4-bit device type identifier followed by three device address bits (E2, E1, E0) and a  $R/\overline{W}$  select bit, and is clocked by the Master on the SDA pin with the most significant bit (MSB, bit 7) first.

The device will respond to two unique device type identifiers. The device type identifier of '1010' is necessary to select the device memory for normal Read or Write operation. The device type identifier of '1011' is used (1) to select the Identification Page for Read or Write/Lock operation; (2) to select the Software Write Protection bit for Read or Write operation; (3) for Read Unique ID (see **Table 1**).

The software device address bits (E2, E1 and E0) must match their corresponding hard-wired device address inputs (E2, E1 and E0), allowing up to eight devices on the bus at the same time. The eighth bit of the address byte is the R/ $\overline{W}$  operation selection bit. A Read operation is selected if this bit is Logic 1, and a Write operation is selected if this bit is Logic 0. Upon a compare of the device address byte, the AT24C02C outputs an ACK or a NACK during the ninth clock cycle if the compare is true or not true, respectively. The device will return to the low-power Standby mode after a NACK.

| Function                                         | Dev   | ісе Тур | e Iden | tifier | Device Address |       |       | Read/Write |

|--------------------------------------------------|-------|---------|--------|--------|----------------|-------|-------|------------|

| Function                                         | bit 7 | bit 6   | bit 5  | bit 4  | bit 3          | bit 2 | bit 1 | bit 0      |

| When accessing the 2-Kbit memory array           | 1     | 0       | 1      | 0      | E2             | E1    | E0    | RŴ         |

| When accessing the Identification Page           | 1     | 0       | 1      | 1      | E2             | E1    | E0    | R/Ŵ        |

| When accessing the Lock Identification Page bit  | 1     | 0       | 1      | 1      | E2             | E1    | E0    | 0          |

| When accessing the Software Write Protection bit | 1     | 0       | 1      | 1      | E2             | E1    | E0    | R/Ŵ        |

| When accessing the Unique ID                     | 1     | 0       | 1      | 1      | E2             | E1    | E0    | 1          |

| Table 1 | AT24C02C Devi | ce Address     | Bvte |

|---------|---------------|----------------|------|

|         | /             | 00 / la al 000 |      |

Once the AT24C02C has acknowledged the device address byte, the device waits for the Master to send the word address byte for a certain Read or Write instruction according to **Table 2**. The device should respond to the word address byte with an ACK.

| Everytter                      |                   | Word Address Byte |                  |       |       |       |       |       |  |  |

|--------------------------------|-------------------|-------------------|------------------|-------|-------|-------|-------|-------|--|--|

| Function                       | bit 7             | bit 6             | bit 5            | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |  |  |

| Random Read                    | A7 <sup>[1]</sup> | A6                | A5               | A4    | A3    | A2    | A1    | A0    |  |  |

| Byte/Page Write                | A7                | A6                | A5               | A4    | A3    | A2    | A1    | A0    |  |  |

| Read/Write Identification Page | 0                 | 0                 | X <sup>[2]</sup> | Х     | A3    | A2    | A1    | A0    |  |  |

| Lock Identification Page       | 0                 | 1                 | Х                | Х     | Х     | Х     | Х     | х     |  |  |

| Read Lock Status               | 0                 | 0                 | Х                | Х     | Х     | Х     | Х     | х     |  |  |

| Read/Write SWP Bit             | 1                 | 1                 | Х                | Х     | Х     | Х     | Х     | х     |  |  |

| Read Unique ID                 | 1                 | 0                 | Х                | Х     | A3    | A2    | A1    | A0    |  |  |

#### Table 2 AT24C02C Word Address Bits

Notes: <sup>[1]</sup> A = Significant address bit.

<sup>[2]</sup> X = Bit is Don't Care

## **Read and Write Operations**

### Write Operations

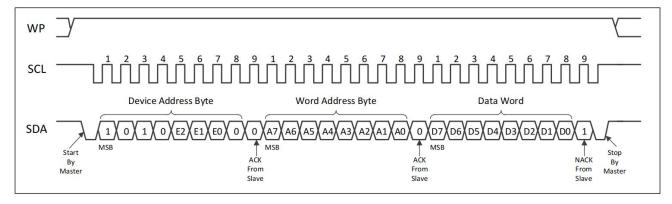

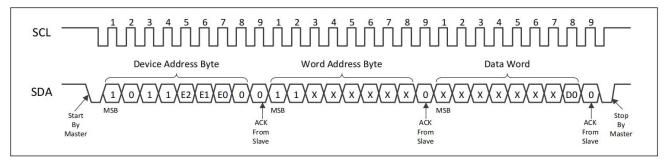

### **Byte Write**

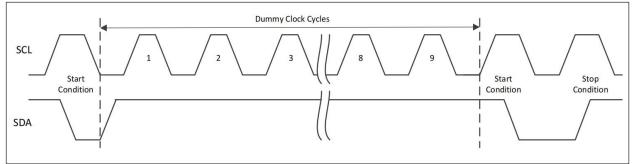

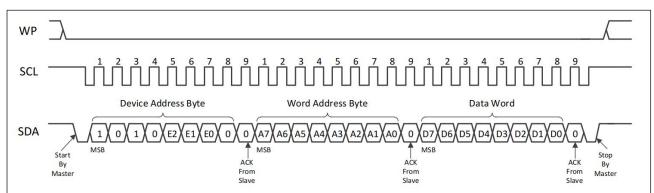

For a Byte Write operation, the Master sends a Start condition followed by the device type identifier of '1010', the device address bits and the  $R/\overline{W}$  select bit set to Logic 0. The AT24C02C responds with an ACK during the ninth clock cycle and waits for the Master to send one word address byte. Then the device responds to the word address byte with an ACK. After receiving ACK from the AT24C02C , the Master transmits one data byte. If the addressed location has been Write-protected, by the WP pin connected to VCC or the SWP bit set to Logic 1, the device responds with a NACK, and the location is not modified. If the addressed location is not Write-protected, by the WP pin set to GND and the SWP bit set to Logic 0, the device will respond with an ACK (see **Figure 3** and **Figure 4**). The Master ends the Byte Write sequence with a Stop condition during the 10th clock cycle to initiate the internally self-timed write cycle. A Stop condition issued during any other clock cycle during the Write operation will not trigger the internal write cycle.

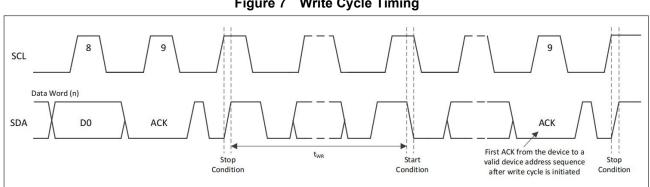

Once the write cycle begins, the preloaded data word will be programmed in the amount of time not to exceed the tWR specification (see **Figure 7**). During the time, the Master should wait a fixed time by the tWR specification, or for time sensitive applications, an ACK polling routine can be implemented. All inputs are ignored by the device during the write cycle and the device will not respond until the write cycle is completed. The serial EEPROM will increment its internal address counter each time a byte is written.

#### Figure 3 Byte Write Operation with Write Protection Pin Set to Low (and SWP bit = 0)

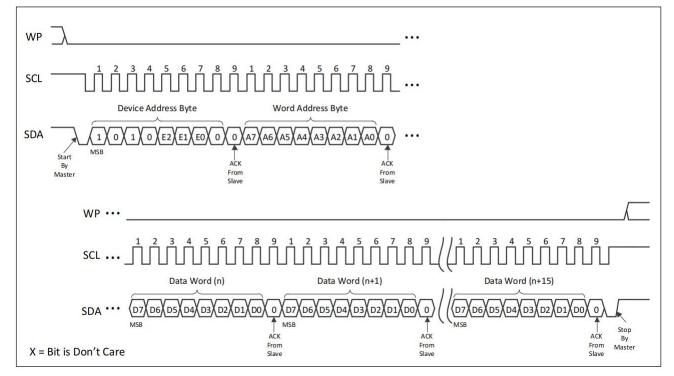

#### Page Write

The 2-Kbit serial EEPROM is capable of writing up to 16 data bytes at a time by executing the Page Write sequence. A partial or full Page Write operation is initiated the same as a Byte Write operation except that the Master does not send a Stop condition after the first data word is clocked in. Instead, after the device has acknowledged to the first data word, the Master can transmit up to fifteen more data words. The device responds with an ACK after each data word is received if the WP pin is set to GND and the SWP bit set to Logic 0, while the device is not acknowledged to each data word and the addressed locations are not modified if the WP pin is connected to VCC or the SWP bit set to Logic 1 (see **Figure 5** and **Figure 6**). After the device acknowledges to the last data word, the Master should terminate the Page Write sequence with a Stop condition to start the internal write cycle. A Stop condition issued at any other clock cycle will not initiate the internally self-timed write cycle and the Write sequence will have to be repeated again. Once the write cycle begins, the data words should be programmed in the amount of time not exceeding the tWR specification (see **Figure 7**). During this time, the Master should wait a fixed time by the specified tWR parameter, or for time sensitive applications, an ACK polling routine can be implemented.

The lower four bits of the word address are internally incremented following the receipt of each data word. The higher word address bits are not incremented, retaining the memory page row location. When the internally generated word address reaches the page boundary, then the following data word is placed at the beginning of the same page. If more than sixteen data words are transmitted to the device, the data word address will roll over and the previous data will be overwritten. The address roll-over during a Write sequence is from the last byte of the current page to the first byte of the same page.

Figure 6 Page Write Operation with Write Protection Pin Set to High (or SWP bit = 1)

#### Write Cycle Timing

The length of the self-timed write cycle, or tWR, is defined as the amount of time from a valid Stop condition that begins the internal write sequence to the Start condition of the first device address byte sent to the AT24C02C that it subsequently responds to with an ACK (see Figure 7).

Write Cycle Timing Figure 7

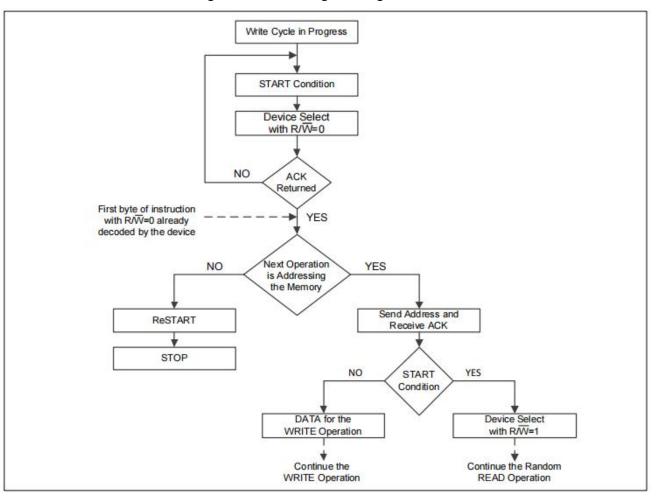

#### Acknowledge (ACK) Polling

An ACK polling routine can be implemented to optimize time sensitive applications that would not prefer to wait the fixed maximum write cycle time but would prefer to know immediately when the serial EEPROM write cycle has completed to start a subsequent operation. Once the internally self-timed write cycle has started, the device inputs are disabled and ACK polling can be initiated. An ACK polling routine involves sending a valid Start condition followed by the device address byte. While the write cycle is in progress, the device will not respond with an ACK, indicating the device is busy writing data. Once completed, the device returns an ACK and the next device operation can be started (see **Figure 8**).

#### Figure 8 Acknowledge Polling Flow Chart

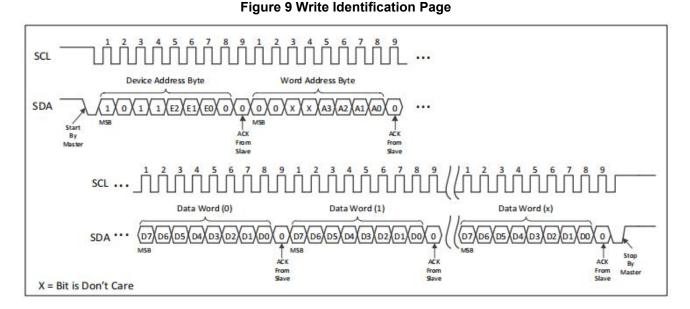

### Write Identification Page

The device offers a 16-byte Identification Page (ID Page) in addition to the 2-Kbit memory array for storage of specific application data. This Identification Page can be written and permanently locked in Read-only mode after the data is written into this Page. The Identification Page is written by issuing the Write Identification Page instruction (see **Figure 9**), which is similar to Page Write, except that:

- The device type identifier is defined as '1011';

- The word address bits A7:A6 must be '00', bits A5:A4 are Don't Care;

- The word address bits A3:A0 define the byte locations inside the ID Page (see Table 2).

If the Identification Page has been locked, the data bytes transferred during the Write Identification Page instruction will not be acknowledged.

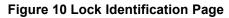

#### Lock Identification Page

The Lock Identification Page (Lock ID) instruction permanently locks the Identification Page in Read-only mode. The Lock ID instruction is similar to Byte Write, except the following specific conditions:

- The device type identifier is defined as '1011';

- The word address bits A7:A6 must be '01' and other word address bits are Don't Care;

- The data byte must be equal to the binary value xxxx\_xx1x, where x is Don't Care (see **Figure 10**).

Once a valid Lock ID instruction has been executed, if another Lock ID instruction is issued, the device will respond with a NACK to the data byte.

http://www.hgsemi.com.cn

#### Software Write Protection (SWP)

In order to prevent unwanted Write sequence, the AT24C02C offers an internal non-volatile SWP bit, which makes it possible to protect the content in the whole memory array (and Identification Page). Updating the SWP bit to a new value is a reversible action by performing the Write SWP Bit instruction. This instruction is similar to Byte Write, except that:

- The device type identifier is defined as '1011';

- The word address bits A7:A6 must be '11' and other word address bits are Don't Care;

- The higher seven bits of the data word byte are Don't Care and bit 0 (D0) configures the SWP bit (see Figure 11). The SWP bit can be updated from Logic 0 to 1 and from Logic 1 to 0. Write operations are disabled (Read-only) when the SWP bit is set to Logic 1, while Write operations are enabled when the SWP bit is set to Logic 0.

Writing more than one byte will discard the write cycle and the value of SWP bit will not be changed.

Note that the device also incorporates a Write Protection pin used for hardware Write Protection. Either connecting the WP pin directly to VCC or setting the SWP bit to Logic 1 will write protect the whole memory array (and Identification Page). Writing the SWP bit is performed independently of the state of the WP pin connection. Upon a certain instruction send by the Master, the device will automatically load the last configuration of the SWP bit.

#### Figure 11 Write SWP Bit

## **Read Operations**

All Read operations are initiated by the Master transmitting a Start condition, a device type identifier of '1010' or '1011', three software device address bits (E2, E1, E0) that match corresponding hard-wired address pins (E2, E1, E0), and the  $R/\overline{W}$  select bit with Logic 1 state. In the following clock cycle, the AT24C02C should respond with an ACK. The subsequent protocol depends on the type of Read operation desired. There are three Read operations for memory array: Current Address Read, Random Address Read, and Sequential Read with the device type identifier of '1010'; four Read operations for Identification Page, SWP bit and Unique ID: Read Identification Page, Read the Lock Status, Read SWP Bit and Read Unique ID with the device type identifier of '1011'. Read operations are performed independently of the state of the WP pin connection and the value of SWP bit.

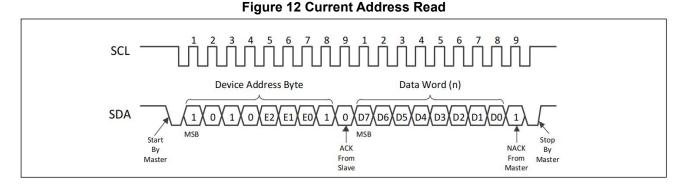

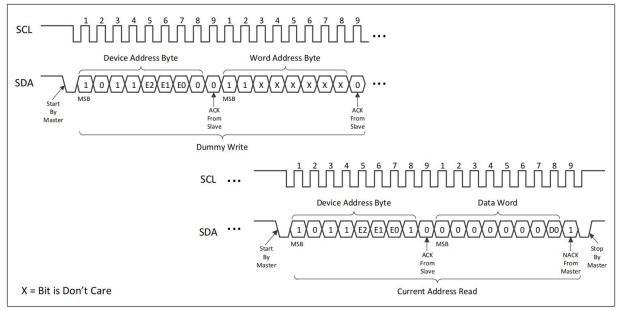

### **Current Address Read**

For a Current Address Read operation, the Master sends a Start condition followed by transmitting the device address byte with the  $R/\overline{W}$  bit set to Logic 1 (see **Figure 12**). The AT24C02C should respond with an ACK and then serially transmits the data word addressed by the internal address counter. This address maintained by the internal address counter is the last address accessed during the last Read or Write operation. The counter is then incremented by one and the address will stay valid between operations as long as power to the device is supplied. The address roll-over during a Read operation is from the last byte of the last page to the first byte of the first page. To end the command, the Master responds with a NACK followed by a Stop condition.

Note that the internal address counter value is defined by instructions accessing the 2-Kbit memory or the Identification Page or the Unique ID. For example, when accessing the ID Page, the counter value is loaded with the byte location in the ID Page. Therefore the next Current Address Read in the memory uses this new address counter value. When accessing the memory, it is recommended to always use Random Read instruction instead of Current Address Read instruction.

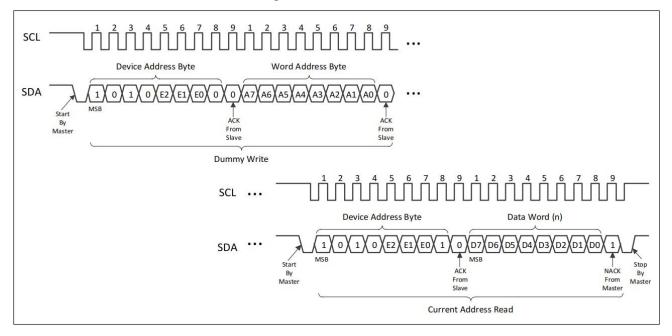

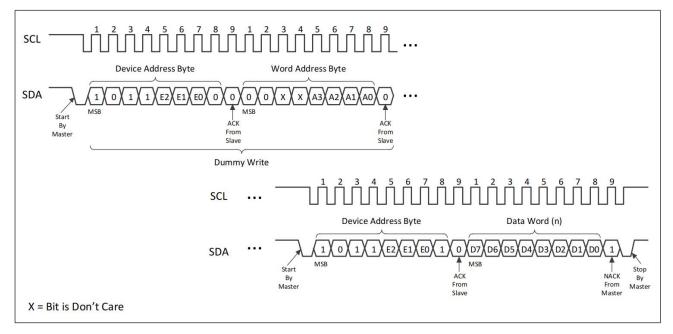

#### Random Read

A Random Read operation allows the Master to access any memory location in a random manner and requires a dummy write sequence to preload the starting data word address. To perform a Random Read, the device address byte and the word address bytes are transmitted to the AT24C02C as part of the dummy write sequence (see **Figure 13** bytes are clocked in and acknowledged by the AT24C02C, the Master must generate another Start condition. The Master initiates a Current Address Read by sending another device address byte with the R/W bit set to Logic 1. The AT24C02C responds with an ACK to the device address byte and serially clocks out the first data word and increments its internal address counter. The device will continue to transmit sequential data words as long as the Master continues to acknowledge each data word.

To end the sequence, the Master responds with a NACK followed by a Stop condition.

Figure 13 Random Read

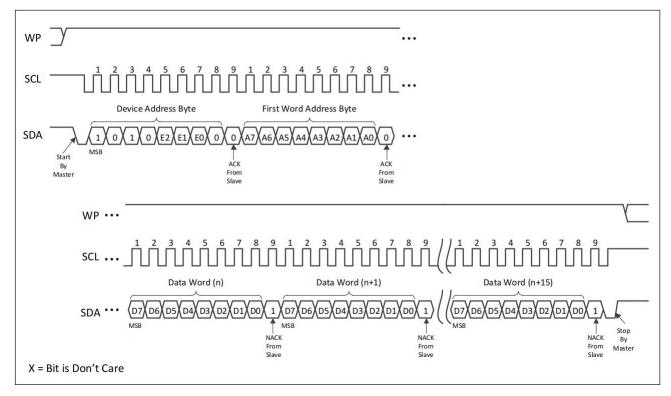

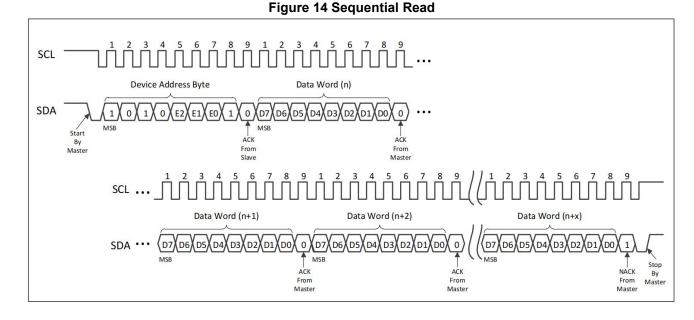

### **Sequential Read**

A Sequential Read operation is initiated in the same way as either a Current Address Read or a Random Read, except that after the AT24C02C transmitting the first data word, the Master responds with an ACK instead of a NACK. As long as the AT24C02C receives an ACK, it will continue to increment the data word address and serially clock out the sequential data words (see **Figure 14**). When the internal address counter is at the last byte of the last page, the word address will roll over to the beginning of the memory array and the Sequential Read operation will continue. The Sequential Read operation is terminated by the Master responding with a NACK followed by a Stop condition.

### **Read Identification Page**

The Identification Page can be read by issuing a Read Identification Page instruction. This instruction uses the same protocol and format as Random Read, except that:

- The device type identifier is defined as '1011';

- The word address bits A7:A6 must be '00', bits A5:A4 are Don't Care;

- The word address bits A3:A0 define the byte locations inside the ID Page (see **Table 2**).

When the end of Identification Page is reached, the word address will roll over to the beginning of the Identification Page. The Read Identification Page operation is terminated by the Master responding with a NACK followed by a Stop condition (see **Figure 15**).

#### Figure 15 Read Identification Page

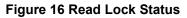

#### **Read Lock Status**

The locked/unlocked status of the Identification Page can be checked by transmitting a specific truncated command, Write Identification Page instruction and one data byte to the device. The device responds with an ACK to the data byte if the Identification Page is unlocked, or responds with a NACK if the Identification Page has been locked. Right after this, it is recommended to transmit a Start condition to the device followed by a Stop condition (see **Figure 16**), so that the truncated Write command will not be executed because the Start condition resets the device internal logic, and the device is then set back into Standby mode by the Stop condition.

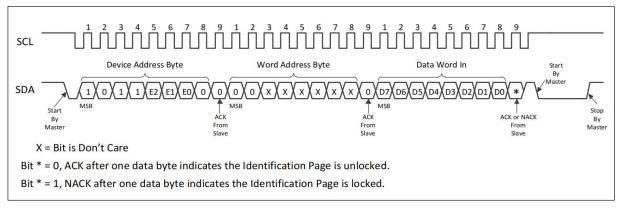

## **Read SWP Bit**

Reading the Software Write Protection bit is performed with a Read SWP Bit instruction, which is similar to Random Read except that:

- The device type identifier is defined as '1011';

- The word address bits A7:A6 must be '11' and other word address bits are Don't Care;

- The higher seven bits of the data word byte are read as '0000000' and the bit 0 (D0) is the value of SWP bit (see **Figure 17**).

Reading more than one byte will loop on reading the SWP bit value.

#### Figure 17 Read SWP Bit

http://www.hgsemi.com.cn

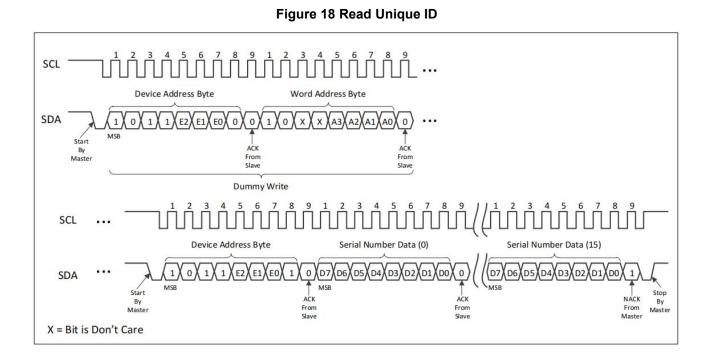

### Read Unique ID

The AT24C02C offers a separate memory block containing a factory programmed 128-bit Unique ID (UID), or Serial Number. Reading the Serial Number is similar to Sequential Read, except that:

- The device type identifier is defined as '1011';

- The word address bits A7:A6 must be '10', bits A5:A4 are Don't Care;

- The word address bits A3:A0 define the byte locations inside the Unique ID (see Table 2).

In order to guarantee a unique number, the entire 128-bit value must be read from the starting address of the Serial Number block. Reading from a location other than the first address of the block will not result in a unique Serial Number. To read the first byte of the Serial Number, the word address bits A3:A0 need to be '0000'. Writing or altering the 128-bit Unique ID is not allowed. When the end of the 128-bit UID block is reached (16 bytes of data), the word address will roll over to the beginning of the 128-bit UID block. The Read Unique ID operation is terminated when the Master responds with a NACK to the data byte followed by a Stop condition (see **Figure 18**).

## **Electrical Specifications**

### **Absolute Maximum Ratings**

| Symbol           | Parameter                              | Value        | Unit |

|------------------|----------------------------------------|--------------|------|

|                  | Ambient temperature with power applied | -55 to +130  | °C   |

| T <sub>STG</sub> | Storage temperature                    | -65 to +150  | °C   |

| Vcc              | Supply voltage                         | -0.5 to +6.0 | V    |

| V <sub>IN</sub>  | Voltage on input Pins                  | -0.5 to +6.0 | V    |

| V <sub>ESD</sub> | Electrostatic pulse (human body model) | 5000         | V    |

**Note:** Stresses beyond those listed under 'Absolute Maximum Ratings' may cause permanent damage to the device. Functional operation of the device at these ratings or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **DC Characteristics**

Operating range:  $T_A = -40^{\circ}$ C to  $+105^{\circ}$ C,  $V_{CC} = 1.7$ V to 5.5V (unless otherwise noted).

| Symbol           | Parameter                           | Test Condition                              | Min                 | Мах                  | Unit |

|------------------|-------------------------------------|---------------------------------------------|---------------------|----------------------|------|

| Vcc              | Supply Voltage                      |                                             | 1.7                 | 5.5                  | V    |

|                  |                                     | V <sub>CC</sub> = 1.7V, Read at 1MHz        | -                   | 0.1                  | mA   |

| I <sub>CC1</sub> | Supply Current (Read)               | V <sub>CC</sub> = 5.5V, Read at 400 kHz     | -                   | 0.4                  | mA   |

|                  |                                     | V <sub>cc</sub> = 5.5V, Read at 1MHz        | -                   | 0.5                  | mA   |

|                  |                                     | $V_{CC}$ = 1.7V, Write at 400 kHz           | -                   | 0.2                  | mA   |

| Icc2             | Supply Current (Write)              | $V_{CC}$ = 5.5V, Write at 400 kHz           | -                   | 0.5                  | mA   |

|                  |                                     | $V_{CC}$ = 1.7V, $V_{IN}$ = $V_{CC}$ or GND | -                   | 0.5                  | μA   |

| I <sub>SB</sub>  | Standby Current                     | $V_{CC}$ = 5.5V, $V_{IN}$ = $V_{CC}$ or GND | -                   | 1.0                  | μA   |

| ILI              | Input Leakage Current               | $V_{IN} = V_{CC}$ or GND                    | -                   | 1.0                  | μA   |

| ILO              | Output Leakage Current              | V <sub>OUT</sub> = V <sub>CC</sub> or GND   | -                   | 1.0                  | μA   |

| VIL              | Input Low-Level Voltage (SDA, SCL)  |                                             | -0.5                | 0.3*Vcc              | V    |

| VIH              | Input High-Level Voltage (SDA, SCL) |                                             | 0.7*V <sub>cc</sub> | V <sub>cc</sub> +0.5 | V    |

| V <sub>OL1</sub> | Low-Level Output Voltage            | V <sub>CC</sub> > 2V, I <sub>OL</sub> = 3mA | -                   | 0.4                  | V    |

| V <sub>OL2</sub> | Low-Level Output Voltage            | V <sub>CC</sub> ≤2V, I <sub>OL</sub> = 2mA  | -                   | 0.2                  | V    |

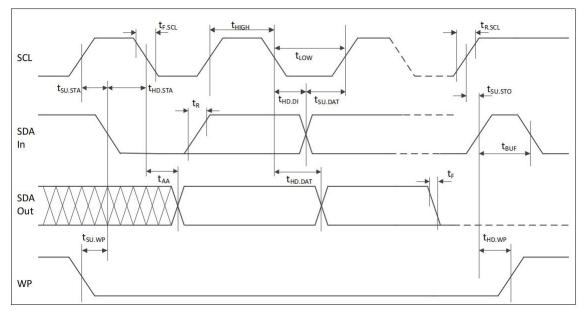

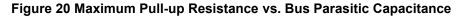

## AC Characteristics

Operating range:  $T_A = -40^{\circ}$ C to +105°C,  $V_{CC} = 1.7$ V to 5.5V,  $C_L = 100$ pF (unless otherwise noted). Measurement conditions: Input rise and fall time  $\leq 50$ ns Input pulse voltages:  $0.2^{*}V_{CC}$  to  $0.8^{*}V_{CC}$  Input and output timing reference voltages:  $0.3^{*}V_{CC}$  to  $0.7^{*}V_{CC}$

| Symbol              | Parameter                                 | Fast M<br>V <sub>cc</sub> = 1.7 |     |     | beed Mode<br>7V to 5.5V | Unit |

|---------------------|-------------------------------------------|---------------------------------|-----|-----|-------------------------|------|

|                     |                                           | Min                             | Max | Min | Max                     |      |

| fscL                | Clock Frequency, SCL                      | -                               | 400 | -   | 1000                    | kHz  |

| t <sub>LOW</sub>    | Clock Pulse Width Low                     | 1300                            | -   | 600 | -                       | ns   |

| t <sub>ніGH</sub>   | Clock Pulse Width High                    | 600                             | -   | 260 | -                       | ns   |

| t <sub>R</sub> [1]  | SDA Rise Time                             | -                               | 300 | -   | 300                     | ns   |

| t <sub>F</sub> [1]  | SDA(Out) Fall Time                        | -                               | 300 | -   | 100                     | ns   |

| t <sub>HD.STA</sub> | Start Hold Time                           | 600                             | -   | 250 | -                       | ns   |

| t <sub>su.sta</sub> | Start Setup Time                          | 600                             | -   | 250 | -                       | ns   |

| t <sub>su.sto</sub> | Stop Setup Time                           | 600                             | -   | 250 | -                       | ns   |

| t <sub>BUF</sub>    | Bus Free Time between Stop and Next Start | 1300                            | -   | 500 | -                       | ns   |

| t <sub>HD.DI</sub>  | Data In Hold Time                         | 0.0                             | -   | 0.0 | -                       | ns   |

| t <sub>su.dat</sub> | Data In Setup Time                        | 100                             | -   | 50  | -                       | ns   |

| t <sub>HD.DAT</sub> | Data Out Hold Time                        | 50                              | -   | 50  | -                       | ns   |

| t <sub>AA</sub>     | SCL Low to Data Out Valid                 | 100                             | 900 | 50  | 500                     | ns   |

| t <sub>SU.WP</sub>  | WP Pin Setup Time                         | 1200                            | -   | 600 | -                       | ns   |

| t <sub>HD.WP</sub>  | WP Pin Hold Time                          | 1200                            | -   | 600 | -                       | ns   |

| t <sub>wR</sub>     | Write Cycle Time                          | -                               | 3   | -   | 3                       | ms   |

| tı                  | Noise Suppression Time                    | -                               | 50  | -   | 50                      | ns   |

Notes: <sup>[1]</sup> This parameter is ensured by characterization only.

Figure 19 Bus Timing

## **Pin Capacitance**

Operating range for pin capacitance:  $T_A = +25^{\circ}C$ , fC = 1MHz,  $V_{CC} = 1.7V$  to 5.5V.

| Symbol          | Parameter[1]                   | Max | Unit | Test Condition        |

|-----------------|--------------------------------|-----|------|-----------------------|

| CI/O            | Input/output Capacitance (SDA) | 8   | pF   | V <sub>1/0</sub> = 0V |

| C <sub>IN</sub> | Input Capacitance (other Pins) | 6   | pF   | V <sub>IN</sub> = 0V  |

Note: <sup>[1]</sup> These parameters are ensured by characterization only.

### **Reliability Characteristics**

| Symbol | Parameter             | Min               | Unit  | Test Condition                    |

|--------|-----------------------|-------------------|-------|-----------------------------------|

| NW     | Write Cycle Endurance | 2x10 <sup>6</sup> | cycle | T <sub>A</sub> = +25°C, Page Mode |

| Dr     | Data Retention        | 200               | year  | T <sub>A</sub> = +25°C            |

## **Initial Delivery State**

The AT24C02C serial EEPROM is delivered as follows:

- All bits in the memory array are set to '1' (each byte contains FFh).

- All bits in the Identification Page are set to '1' (each byte contains FFh).

- The Software Write Protection bit is set to '0'.

Q

0.25

A

Ω

## **Physical Dimensions**

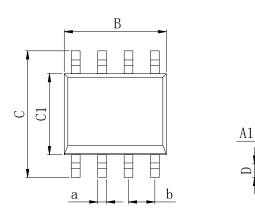

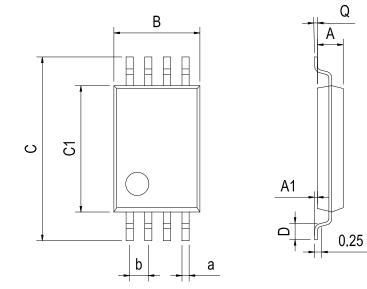

## SOP8

| Dimensions In Millimeters(SOP8) |      |      |      |      |      |      |    |      |          |  |

|---------------------------------|------|------|------|------|------|------|----|------|----------|--|

| Symbol:                         | A    | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |

| Min:                            | 1.35 | 0.05 | 4.90 | 5.80 | 3.80 | 0.40 | 0° | 0.35 | 1.27 BSC |  |

| Max:                            | 1.55 | 0.20 | 5.10 | 6.20 | 4.00 | 0.80 | 8° | 0.45 | 1.27 030 |  |

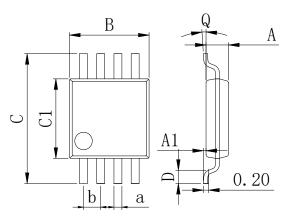

## MSOP8

| Dimensions In Millimeters(MSOP8) |      |      |      |      |      |      |    |      |          |  |  |

|----------------------------------|------|------|------|------|------|------|----|------|----------|--|--|

| Symbol:                          | А    | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |  |

| Min:                             | 0.80 | 0.05 | 2.90 | 4.75 | 2.90 | 0.35 | 0° | 0.25 | 0.65 BSC |  |  |

| Max:                             | 0.90 | 0.20 | 3.10 | 5.05 | 3.10 | 0.75 | 8° | 0.35 | 0.00 650 |  |  |

## **Physical Dimensions**

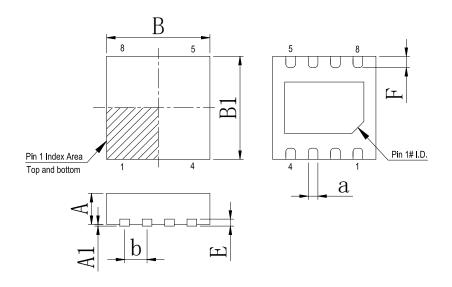

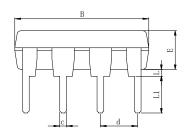

## DFN-8 3\*3

| Dimensions In Millimeters(DFN-8 3*3) |      |      |      |      |      |      |      |          |  |  |

|--------------------------------------|------|------|------|------|------|------|------|----------|--|--|

| Symbol:                              | A    | A1   | В    | B1   | Е    | F    | а    | b        |  |  |

| Min:                                 | 0.85 | 0.00 | 2.90 | 2.90 | 0.20 | 0.30 | 0.20 |          |  |  |

| Max:                                 | 0.95 | 0.05 | 3.10 | 3.10 | 0.25 | 0.50 | 0.34 | 0.65 BSC |  |  |

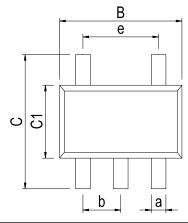

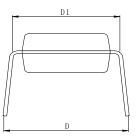

SOT23-5

| Dimensions In Millimeters(SOT23-5) |      |      |      |      |      |      |    |      |            |          |

|------------------------------------|------|------|------|------|------|------|----|------|------------|----------|

| Symbol:                            | A    | A1   | В    | С    | C1   | D    | Q  | а    | b          | е        |

| Min:                               | 1.05 | 0.00 | 2.82 | 2.65 | 1.50 | 0.30 | 0° | 0.30 | - 0.95 BSC | 1.90 BSC |

| Max:                               | 1.15 | 0.15 | 3.02 | 2.95 | 1.70 | 0.60 | 8° | 0.40 |            |          |

## **Physical Dimensions**

TSSOP-8 (4.4\*3.0)

| Dimensions In Millimeters(TSSOP-8) |      |      |      |      |      |      |    |      |          |  |

|------------------------------------|------|------|------|------|------|------|----|------|----------|--|

| Symbol:                            | A    | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |

| Min:                               | 0.85 | 0.05 | 2.90 | 6.20 | 4.30 | 0.40 | 0° | 0.20 | 0.65 BSC |  |

| Max:                               | 0.95 | 0.20 | 3.10 | 6.60 | 4.50 | 0.80 | 8° | 0.25 | 0.00 630 |  |

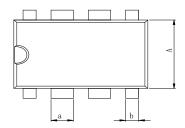

DIP-8

| Dimensions In Millimeters(DIP8) |      |      |      |      |      |      |      |      |      |      |          |

|---------------------------------|------|------|------|------|------|------|------|------|------|------|----------|

| Symbol:                         | A    | В    | D    | D1   | E    | L    | L1   | а    | b    | С    | d        |

| Min:                            | 6.10 | 9.00 | 8.40 | 7.42 | 3.10 | 0.50 | 3.00 | 1.50 | 0.85 | 0.40 | 2.54.000 |

| Max:                            | 6.68 | 9.50 | 9.00 | 7.82 | 3.55 | 0.70 | 3.60 | 1.55 | 0.90 | 0.50 | 2.54 BSC |

http://www.hgsemi.com.cn

## **Revision History**

| DATE     | REVISION            | PAGE |

|----------|---------------------|------|

| 2014-6-4 | New                 | 1-27 |

| 2023-7-3 | Added DIP-8 package | 1    |

#### **IMPORTANT STATEMENT:**

Huaguan Semiconductor reserves the right to change its products and services without notice. Before ordering, the customer shall obtain the latest relevant information and verify whether the information is up to date and complete. Huaguan Semiconductor does not assume any responsibility or obligation for the altered documents.

Customers are responsible for complying with safety standards and taking safety measures when using Huaguan Semiconductor products for system design and machine manufacturing. You will bear all the following responsibilities: Select the appropriate Huaguan Semiconductor products for your application; Design, validate and test your application; Ensure that your application meets the appropriate standards and any other safety, security or other requirements. To avoid the occurrence of potential risks that may lead to personal injury or property loss.

Huaguan Semiconductor products have not been approved for applications in life support, military, aerospace and other fields, and Huaguan Semiconductor will not bear the consequences caused by the application of products in these fields. All problems, responsibilities and losses arising from the user's use beyond the applicable area of the product shall be borne by the user and have nothing to do with Huaguan Semiconductor, and the user shall not claim any compensation liability against Huaguan Semiconductor by the terms of this Agreement.

The technical and reliability data (including data sheets), design resources (including reference designs), application or other design suggestions, network tools, safety information and other resources provided for the performance of semiconductor products produced by Huaguan Semiconductor are not guaranteed to be free from defects and no warranty, express or implied, is made. The use of testing and other quality control technologies is limited to the quality assurance scope of Huaguan Semiconductor. Not all parameters of each device need to be tested.

The documentation of Huaguan Semiconductor authorizes you to use these resources only for developing the application of the product described in this document. You have no right to use any other Huaguan Semiconductor intellectual property rights or any third party intellectual property rights. It is strictly forbidden to make other copies or displays of these resources. You should fully compensate Huaguan Semiconductor and its agents for any claims, damages, costs, losses and debts caused by the use of these resources. Huaguan Semiconductor accepts no liability for any loss or damage caused by infringement.

单击下面可查看定价,库存,交付和生命周期等信息

>>HGSEMI(华冠)