# DS34C87 CMOS Quad TRI-STATE® Differential Line Driver

#### **General Description**

The DS34C87 is a quad differential line driver designed for digital data transmission over balanced lines. The DS34C87 meets all the requirements of EIA standard RS-422 while retaining the low power characteristics of CMOS. This enables the construction of serial and terminal interfaces while maintaining minimal power consumption.

The DS34C87 accepts TTL or CMOS input levels and translates these to RS-422 output levels. This part uses special output circuitry that enables the individual drivers to power down without loading down the bus. The DS34C87 also includes special power up and down circuitry which will TRI-STATE the outputs during power up or down, preventing spurious glitches on its outputs. This device has separate enable circuitry for each pair of the four drivers. The DS34C87 is pin compatible to the DS3487.

All inputs are protected against damage due to electrostatic discharge by diodes to  $V_{\rm CC}$  and ground.

#### **Features**

- TTL input compatible

- Typical propagation delays: 8 ns

- Typical output skew: 0.5 ns

- Outputs won't load line when V<sub>CC</sub> = 0V

- Meets the requirements of EIA standard RS-422

- Operation from single 5V supply

- TRI-STATE outputs for connection to system buses

- Low quiescent current

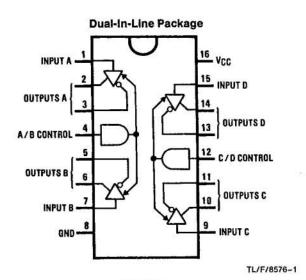

### **Connection and Logic Diagrams**

Top View

Order Number DS34C87J,

DS34C87N or DS34C87M

See NS Package Number

J16A, M16A or N16A

TL/F/8576-2

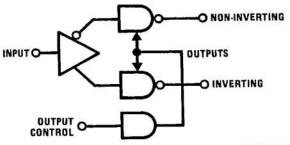

#### **Truth Table**

| Input | Control<br>Input | Non-Inverting<br>Output | Inverting<br>Output |  |  |

|-------|------------------|-------------------------|---------------------|--|--|

| Н     | Н                | Н                       | L                   |  |  |

| L     | н                | L                       | н                   |  |  |

| X     | L                | Z                       | z                   |  |  |

L = Low logic state

X = Irrelevant

H = High logic state

Z = TRI-STATE (high impedance)

For complete specifications see the Interface Databook.

### Absolute Maximum Ratings (Notes 1 & 2)

If Military/Aerospace specified devices are required, contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage (V <sub>CC</sub> )                        | -0.5 to 7.0V                  |

|----------------------------------------------------------|-------------------------------|

| DC Voltage (V <sub>IN</sub> )                            | -1.5 to V <sub>CC</sub> +1.5V |

| DC Output Voltage (VOUT)                                 | -0.5 to 7V                    |

| Clamp Diode Current (I <sub>IK</sub> , I <sub>OK</sub> ) | ± 20 mA                       |

| DC Output Current, per pin (IOUT)                        | ± 150 mA                      |

| DC VCC or GND Current (ICC)                              | ±150 mA                       |

| Storage Temperature Range (TSTG)                         | -65°C to +150°C               |

| Power Dissipation (Note 3) (PD)                          | 500 mW                        |

| Lead Temperature (TL) (Soldering 4 sec                   | ) 260°C                       |

### **Operating Conditions**

|                                                             | Min  | Max  | Units |

|-------------------------------------------------------------|------|------|-------|

| Supply Voltage (VCC)                                        | 4.50 | 5.50 | V     |

| DC Input or Output Voltage (VIN, VOUT)                      | 0    | Vcc  | ٧     |

| Operating Temperature Range (T <sub>A</sub> )               | -40  | +85  | ٩C    |

| Input Rise or Fall Times (t <sub>r</sub> , t <sub>f</sub> ) |      | 500  | ns    |

### DC Electrical Characteristics $V_{CC} = 5V \pm 10\%$ (unless otherwise specified) (Note 4)

| Symbol                           | Parameter                            |                                                                                                                 | Conditions                        | Min                  | Тур        | Max         | Units    |

|----------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------|------------|-------------|----------|

| V <sub>IH</sub>                  | High Level Input<br>Voltage          |                                                                                                                 |                                   | 2.0                  |            |             | ٧        |

| V <sub>IL</sub>                  | Low Level Input<br>Voltage           |                                                                                                                 |                                   |                      |            | 0.8         | ٧        |

| V <sub>OH</sub>                  | High Level Output<br>Voltage         | $V_{IN} = V_{IH} \text{ or } V_{IL},$ $I_{OUT} = -20 \text{ mA}$                                                |                                   | 2.5                  |            |             | ٧        |

| V <sub>OL</sub>                  | Low Level Output<br>Voltage          | V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> ,<br>I <sub>OUT</sub> = 48 mA                              |                                   |                      |            | 0.5         | V        |

| V <sub>T</sub>                   | Differential Output<br>Voltage       | R <sub>L</sub> = 100 Ω<br>(Note 5)                                                                              |                                   | 2.0                  |            |             | ٧        |

| V <sub>T</sub>  - ∇ <sub>T</sub> | Difference In<br>Differential Output | R <sub>L</sub> = 100 Ω<br>(Note 5)                                                                              |                                   |                      |            | 0.4         | ٧        |

| Vos                              | Common Mode<br>Output Voltage        | $R_L = 100 \Omega$ (Note 5)                                                                                     |                                   |                      |            | 3.0         | ٧        |

| Vos-⊽os                          | Difference In<br>Common Mode Output  | R <sub>L</sub> = 100 Ω<br>(Note 5)                                                                              |                                   |                      |            | 0.4         | ٧        |

| lin                              | Input Current                        | V <sub>IN</sub> = V <sub>CC</sub> , GND, V <sub>IH</sub> , or V <sub>IL</sub>                                   |                                   | U (C. 1988 1997 1997 |            | ±1.0        | μΑ       |

| loc                              | Quiescent Supply<br>Current          | I <sub>OUT</sub> = 0 μA,<br>V <sub>IN</sub> = V <sub>CC</sub> or GND<br>V <sub>IN</sub> = 2.4V or 0.5V (Note 6) |                                   |                      | 200<br>0.8 |             | μA<br>mA |

| loz                              | TRI-STATE Output<br>Leakage Current  | V <sub>OUT</sub> = V <sub>CC</sub> or GND<br>Control = V <sub>IL</sub>                                          |                                   |                      | ±0.5       | ±5.0        | μΑ       |

| Isc                              | Output Short<br>Circuit Current      | V <sub>IN</sub> = V <sub>CC</sub> or GND<br>(Note 7)                                                            |                                   | -30                  |            | -150        | mA       |

| OFF                              | Output Leakage Current<br>Power Off  | V <sub>CC</sub> = 0V                                                                                            | $V_{OUT} = 6V$ $V_{OUT} = -0.25V$ |                      |            | 100<br>-100 | μA<br>μΑ |

Note 1: Absolute Maximum Ratings are those values beyond which damage to the device may occur.

Note 2: Unless otherwise specified, all voltages are referenced to ground. All currents into device pins are positive; all currents out of device pins are negative.

Note 3: Power Dissipation temperature derating-plastic "N" package: -12 mW/°C from 65°C to 85°C.

ceramic "J" package: -12 mW/°C from 100°C to 125°C.

Note 4: Unless otherwise specified, min/max limits apply across the -40°C to 85°C temperature range. All typicals are given for V<sub>CC</sub> = 5V and T<sub>A</sub> = 25°C.

Note 5: See EIA Specification RS-422 for exact test conditions.

Note 6: Measured per input. All other inputs at VCC or GND.

Note 7: Only one output at a time should be shorted.

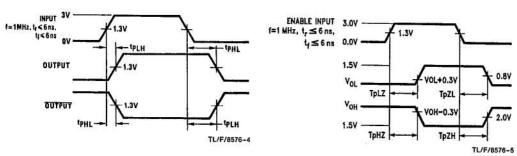

# Switching Characteristics $V_{CC} = 5V \pm 10\%$ , $t_r = t_f = 6$ ns (Figures 1, 2, 3, and 4) (Note 4)

| Symbol                              | Parameter                                  | Conditions | Min | Тур | Max | Units |

|-------------------------------------|--------------------------------------------|------------|-----|-----|-----|-------|

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation Delay input to Output          | S1 Open    |     | 8   |     | ns    |

| Skew                                | (Note 8)                                   | S1 Open    |     | 0.5 |     | ns    |

| t <sub>TLH</sub> , t <sub>THL</sub> | Differential Output Rise<br>And Fall Times | S1 Open    |     | 8   |     | ns    |

| t <sub>PZH</sub>                    | Output Enable Time                         | S1 Closed  |     | 13  |     | ns    |

| tpzL                                | Output Enable Time                         | S1 Closed  |     | 15  |     | ns    |

| t <sub>PHZ</sub>                    | Output Disable Time (Note 9)               | S1 Closed  |     | 9   |     | ns    |

| t <sub>PLZ</sub>                    | Output Disable Time (Note 9)               | S1 Closed  |     | 10  |     | ns    |

| C <sub>PD</sub>                     | Power Dissipation<br>Capacitance (Note 10) |            |     | 100 |     | pF    |

| CIN                                 | Input Capacitance                          |            |     | 10  |     | pF    |

Note 8: Skew is defined as the difference in propagation delays between complementary outputs at the 50% point.

Note 9: Output disable time is the delay from ENABLE or ENABLE being switched to the output transistors turning off. The actual disable times are less than indicated due to the delay added by the RC time constant of the load.

Note 10: CpD determines the no load dynamic power consumption, PD = CpD V2CC f + ICC VCC, and the no load dynamic current consumption, IS = CpD VCC f + ICC.

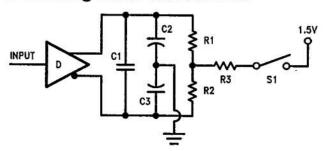

### **AC Test Circuit and Switching Time Waveforms**

Note: C1 = C2 = C3 = 40 pF, R1 = R2 =  $50\Omega$ , R3 =  $500\Omega$ FIGURE 1. AC Test Circuit

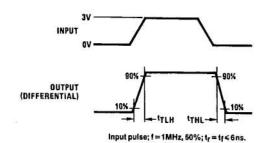

### AC Test Circuit and Switching Time Waveforms (Continued)

FIGURE 2. Propagation Delays

FIGURE 3. Enable and Disable Times

FIGURE 4. Differential Rise and Fall Times

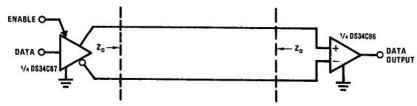

### **Typical Applications**

### Two-Wire Balanced System, RS-422

## Important statement:

Huaguan Semiconductor Co,Ltd. reserves the right to change the products and services provided without notice. Customers should obtain the latest relevant information before ordering, and verify the timeliness and accuracy of this information.

Customers are responsible for complying with safety standards and taking safety measures when using our products for system design and machine manufacturing to avoid potential risks that may result in personal injury or property damage.

Our products are not licensed for applications in life support, military, aerospace, etc., so we do not bear the consequences of the application of these products in these fields.

Our documentation is only permitted to be copied without any tampering with the content, so we do not accept any responsibility or liability for the altered documents.

### 单击下面可查看定价,库存,交付和生命周期等信息

>>HGSEMI (华冠)