# **Quadruple 2-Input NAND Gates with Open-Drain Outputs**

#### **Features**

- Wide Operating Voltage Range: 2 V to 6 V

- Outputs Can Drive Up To 10 LSTTL Loads

- Low Power Consumption, 20-µA Maximum ICC

- Typical tpd = 8 ns at 5 V

- ±4-mA Output Drive at 5 V

- Low Input Current of 1 μA

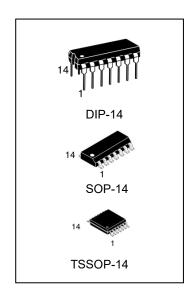

## **Ordering Information**

| DEVICE      | Package Type | MARKING | Packing | Packing Qty  |

|-------------|--------------|---------|---------|--------------|

| 74HC03N     | DIP-14       | 74HC03  | TUBE    | 1000pcs/Box  |

| 74HC03M/TR  | SOP-14       | 74HC03  | REEL    | 2500pcs/Reel |

| 74HC03MT/TR | TSSOP-14     | HC03    | REEL    | 2500pcs/Reel |

### **Description**

This device contains four independent 2-input NAND Gates with open-drain outputs. Each gate performs the Boolean function Y = A ● B in positive logic

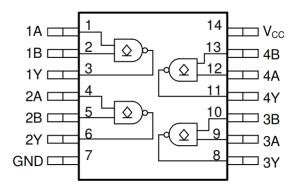

### **Functional pinout**

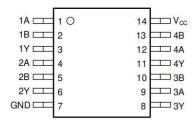

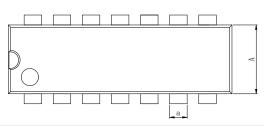

# **Pin Configuration**

DIP-14/SOP-14/TSSOP-14

#### **Pin Functions**

|      | PIN           | I/O    | DESCRIPTION         |

|------|---------------|--------|---------------------|

| NAME | DIP/SOP/TSSOP | 1/0    | DESCRIPTION         |

| 1A   | 1             | Input  | Channel 1, Input A  |

| 1B   | 2             | Input  | Channel 1, Input B  |

| 1Y   | 3             | Output | Channel 1, Output Y |

| 2A   | 4             | Input  | Channel 2, Input A  |

| 2B   | 5             | Input  | Channel 2, Input B  |

| 2Y   | 6             | Output | Channel 2, Output Y |

| GND  | 7             | _      | Ground              |

| 3Y   | 8             | Output | Channel 3, Output Y |

| 3A   | 9             | Input  | Channel 3, Input A  |

| 3B   | 10            | Input  | Channel 3, Input B  |

| 4Y   | 11            | Output | Channel 4, Output Y |

| 4A   | 12            | Input  | Channel 4, Input A  |

| 4B   | 13            | Input  | Channel 4, Input B  |

| VCC  | 14            | _      | Positive Supply     |

## **Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|      |                                          |                    | MIN | MAX | UNIT |

|------|------------------------------------------|--------------------|-----|-----|------|

| VCC  | Supply voltage                           | -0.5               | 7   | V   |      |

| IIK  | Input clamp current(2)                   | VI < 0 or VI > VCC | -   | ±20 | mA   |

| IOK  | Output clamp current(2)                  | VO < 0 or VO > VCC | -   | ±20 | mA   |

| Ю    | Continuous output current                | -                  | ±25 | mA  |      |

|      | Continuous current through VCC or GND    |                    | -   | ±50 | mA   |

| TJ   | Junction temperature(3)                  |                    | -   | 150 | °C   |

| Tstg | Storage temperature                      | -65                | 150 | °C  |      |

| TL   | Lead Temperature (Soldering, 10 seconds) | -                  | 245 | °C  |      |

Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These

are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond

those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for

extended periods may affect device reliability.

- 2. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

- 3. Guaranteed by design.

### **Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|       |                                     |             | MIN             | NOM | MAX  | UNIT |  |

|-------|-------------------------------------|-------------|-----------------|-----|------|------|--|

| VCC   | Supply voltage                      |             | 2               | 5   | 6    | V    |  |

|       |                                     | VCC = 2 V   | 1.5             |     |      |      |  |

| VIH   | High-level input voltage            | VCC = 4.5 V | 3.15            |     |      | V    |  |

|       |                                     | VCC = 6 V   | 4.2             |     |      |      |  |

|       |                                     | VCC = 2 V   |                 |     | 0.5  |      |  |

| VIL   | Low-level input voltage             | VCC = 4.5 V |                 |     | 1.35 | V    |  |

|       |                                     | VCC = 6 V   |                 |     | 1.8  |      |  |

| VI    | Input voltage                       |             | 0               |     | VCC  | ٧    |  |

| VO    | Output voltage                      |             | 0               |     | VCC  | V    |  |

|       |                                     | VCC = 2 V   |                 |     | 1000 |      |  |

| Δt/Δν | Input transition rise and fall rate | VCC = 4.5 V |                 |     | 500  | ns   |  |

|       |                                     | VCC = 6 V   |                 |     | 400  |      |  |

| TA    | Operating free-air temperature      | 74HC03      | <del>-4</del> 0 |     | 85   | °C   |  |

### **Thermal Information**

|             |                                    |         | 74HC03  |         |      |

|-------------|------------------------------------|---------|---------|---------|------|

|             | THERMAL METRIC(1)                  | (SOP)   | (DIP)   | (TSSOP) | UNIT |

|             |                                    | 14 PINS | 14 PINS | 14 PINS |      |

| RθJA        | Junction-to-ambient                |         | 66.0    | 151.7   | °C/W |

| NOJA        | thermal resistance                 | 133.6   | 00.0    | 151.7   | C/VV |

| D0 10(to a) | Junction-to-case (top)             | 89      | F0.7    | 79.4    | °C/M |

| ReJC(top)   | RθJC(top) thermal resistance       |         | 53.7    | 79.4    | °C/W |

| DO ID       | Junction-to-board                  | 80 F    | 45.7    | 04.7    | °C/W |

| RθJB        | thermal resistance                 | 89.5    | 45.7    | 94.7    | C/VV |

|             | Junction-to-top                    | 45.5    | 22.2    | 05.0    | °C/M |

| ΨЈТ         | characterization parameter         | 45.5    | 33.3    | 25.2    | °C/W |

| IIIID       | Junction-to-board characterization |         | 45.5    | 94.1    | °C/W |

| ΨЈВ         | parameter                          | 89.1    | 45.5    | 94.1    | C/VV |

| DO IC(bct)  | Junction-to-case (bottom) thermal  | NI/A    | NI/A    | NI/A    | °C/M |

| RθJC(bot)   | resistance                         | N/A     | N/A     | N/A     | °C/W |

### **Electrical Characteristics**

over operating free-air temperature range (unless otherwise noted)  $^{(1)}(2)$

|     |                       |                    |              |            | Op   | erating | free-air | tempe         | rature ( | TA)  |      |

|-----|-----------------------|--------------------|--------------|------------|------|---------|----------|---------------|----------|------|------|

| PA  | RAMETER               | TEST CON           | NDITIONS     | vcc        | 25°C |         |          | -40°C to 85°C |          |      | UNIT |

|     |                       |                    |              |            | MIN  | TYP     | MAX      | MIN           | TYP      | MAX  |      |

| ЮН  | Output voltage        | VI = VIH<br>or VIL | VO = VCC     | 6 V        |      | 0.01    | 0.5      |               |          | 5    | μA   |

|     |                       |                    |              | 2 V        |      | 0.002   | 0.1      |               |          | 0.1  |      |

|     |                       | VI = VIH<br>or VIL | IOL = 20 μA  | 4.5 V      |      | 0.001   | 0.1      |               |          | 0.1  | V    |

| VOL |                       |                    |              | 6 V        |      | 0.001   | 0.1      |               |          | 0.1  |      |

|     | output voltage        | OI VIL             | IOL = 4 mA   | 4.5 V      |      | 0.17    | 0.26     |               |          | 0.33 |      |

|     |                       |                    | IOL = 5.2 mA | 6 V        |      | 0.15    | 0.26     |               |          | 0.33 |      |

| II  | Input leakage current | VI = VC            | CC or 0      | 6 V        |      |         | ±0.1     |               |          | ±1   | μA   |

| ICC | Supply current        | VI = VCC or 0      | IO = 0       | 6 V        |      |         | 2        |               |          | 20   | μA   |

| Ci  | Input capacitance     |                    |              | 2 V to 6 V |      | 3       | 10       |               |          | 10   | pF   |

<sup>(1)</sup> VCCI is the VCC associated with the input port.

(2) VCCO is the VCC associated with the output port.

## **Switching Characteristics**

over operating free-air temperature range (unless otherwise noted)

|      |                                     |        |    |       | Ор   | erating | free-aiı | tempe | erature | (TA) |      |

|------|-------------------------------------|--------|----|-------|------|---------|----------|-------|---------|------|------|

|      | PARAMETER                           |        | то | o vcc | 25°C |         |          | -4    | 0°C to  | 85°C | UNIT |

|      |                                     |        |    |       | MIN  | TYP     | MAX      | MIN   | TYP     | MAX  |      |

|      |                                     |        |    | 2 V   |      | 60      | 105      |       |         | 131  |      |

| tplh | tplh Propagation delay, low-to-high | A or B | Y  | 4.5 V |      | 13      | 25       |       |         | 31   | ns   |

|      |                                     |        |    | 6 V   |      | 10      | 23       |       |         | 27   |      |

|      |                                     |        | Y  | 2 V   |      | 50      | 100      |       |         | 125  |      |

| tphl | Propagation delay<br>high-to-low    | A or B |    | 4.5 V |      | 10      | 20       |       |         | 25   | ns   |

|      | nign-to-low                         |        |    | 6 V   |      | 8       | 17       |       |         | 21   |      |

|      |                                     |        |    | 2 V   |      | 38      | 75       |       |         | 95   |      |

| tt   | tt Transition-time                  |        | Y  | 4.5 V |      | 8       | 15       |       |         | 19   | ns   |

|      |                                     |        |    | 6 V   |      | 6       | 13       |       |         | 16   |      |

## **Operating Characteristics**

over operating free-air temperature range; typical values measured at TA = 25°C (unless otherwise noted)

|     | PARAMETER            | TEST CONDITIONS | vcc        | MIN | TYP | MAX | UNIT |

|-----|----------------------|-----------------|------------|-----|-----|-----|------|

| Cpd | Power dissipation    | No load         | 2 V to 6 V |     | 20  |     | pF   |

| Сри | capacitance per gate | INO IOAU        | 2 0 10 0 0 |     | 20  |     | PΓ   |

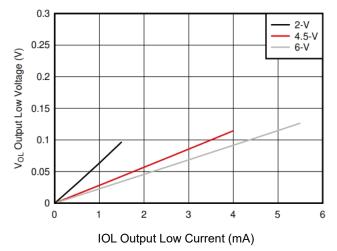

## **Typical Characteristics**(TA = 25°C)

Figure 5-1. Typical output voltage in the low state (VOL)

#### **Parameter Measurement Information**

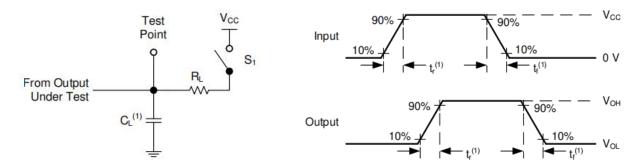

Phase relationships between waveforms were chosen arbitrarily. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  1 MHz, ZO = 50  $\Omega$ , tt < 6 ns.

The outputs are measured one at a time, with one input transition per measurement

A. CL= 50 pF and includes probe and jig capacitance

Figure 6-1. Load Circuit

A. tt is the greater of tr and tf.

Figure 6-2. Voltage Wave forms Transition Times

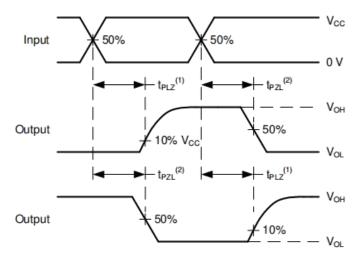

A. The maximum between tPLH and tPHL is used for tpd.

Figure 6-3. Voltage Wave forms Propagation Delays

### **Detailed Description**

#### Overview

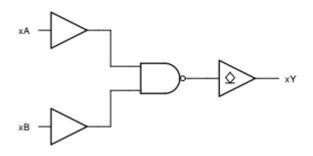

This device contains four independent 2-input NAND gates with open-drain outputs. Each gate performs the Boolean function  $Y = A \bullet B$  in positive logic.

### **Functional Block Diagram**

### **Feature Description**

#### **CMOS Open-Drain Outputs**

The open-drain output allows the device to sink current to GND but not to source current from VCC. When the output is not actively pulling the line low, it will go into a high impedance state. This allows the device to be used for a wide variety of applications, including up-translation and down-translation, as the output voltage can be determined by an external pull-up resistor.

The current drive capability of this device creates fast edges into light loads, so routing and load conditions should be considered to prevent ringing. Additionally, the outputs of this device are capable of driving larger currents than the device can sustain without being damaged. It is important for the power output of the device to be limited to avoid thermal runaway and damage due to over-current. The electrical and thermal limits defined the in the Absolute Maximum Ratingsmust be followed at all times.

The 74HC03 can drive a load with a total capacitance less than or equal to the maximum load listed in the Switching Characteristics connected to a high-impedance CMOS input while still meeting all of the datasheet specifications. Larger capacitive loads can be applied, however it is not recommended to exceed the provided load value. If larger capacitive loads are required, it is recommended to add a series resistor between the output and the capacitor to limit output current to the values given in the Absolute Maximum Ratings.

#### **Standard CMOS Inputs**

Standard CMOS inputs are high impedance and are typically modeled as a resistor from the input to ground in parallel with the input capacitance given in the Electrical Characteristics. The worst case resistance is calculated with the maximum input voltage, given in the Absolute Maximum Ratings, and the maximum input leakage current, given in the Electrical Characteristics, using ohm's law  $(R = V \div I)$ .

Signals applied to the inputs need to have fast edge rates, as defined by the input transition time in the Recommended Operating Conditions to avoid excessive current consumption and oscillations. If a slow or noisy input signal is required, a device with a Sch mitt-trigger input should be used to condition the input signal prior to the standard CMOS input.

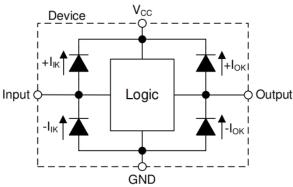

### **Clamp Diode Structure**

The inputs and outputs to this device have both positive and negative clamping diodes as depicted in Figure 7-1.

#### **CAUTION**

Voltages beyond the values specified in the Absolute Maximum Ratings table can cause damage to the device. The recommended input and output voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

Figure 7-1. Electrical Placement of Clamping Diodes for Each Input and Output

#### **Device Functional Modes**

Table 7-1. Function Table

| INF | PUTS | ОИТРИТ |

|-----|------|--------|

| A   | В    | Y      |

| Н   | Н    | L      |

| L   | X    | Z      |

| X   | L    | Z      |

# **Physical Dimensions**

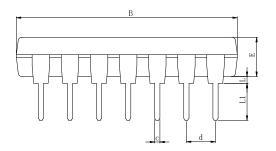

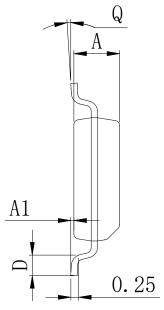

## DIP-14

| Dimensions In Millimeters(DIP-14) |      |       |      |      |      |      |      |      |      |          |  |

|-----------------------------------|------|-------|------|------|------|------|------|------|------|----------|--|

| Symbol:                           | Α    | В     | D    | D1   | Е    | L    | L1   | а    | С    | d        |  |

| Min:                              | 6.10 | 18.94 | 8.10 | 7.42 | 3.10 | 0.50 | 3.00 | 1.50 | 0.40 | 2.54 BSC |  |

| Max:                              | 6.68 | 19.56 | 10.9 | 7.82 | 3.55 | 0.70 | 3.60 | 1.55 | 0.50 | 2.54 BSC |  |

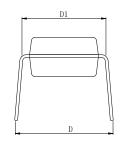

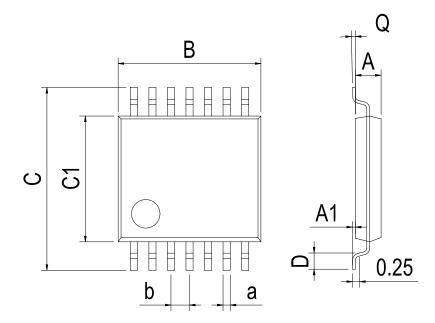

SOP-14

| Dimensions In Millimeters(SOP-14) |      |      |      |      |      |      |    |      |          |  |  |

|-----------------------------------|------|------|------|------|------|------|----|------|----------|--|--|

| Symbol:                           | Α    | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |  |

| Min:                              | 1.35 | 0.05 | 8.55 | 5.80 | 3.80 | 0.40 | 0° | 0.35 | 4.07.000 |  |  |

| Max:                              | 1.55 | 0.20 | 8.75 | 6.20 | 4.00 | 0.80 | 8° | 0.45 | 1.27 BSC |  |  |

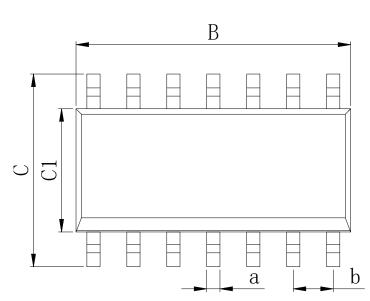

# **Physical Dimensions**

### TSSOP-14

| Dimensions In M | Dimensions In Millimeters(TSSOP-14) |      |      |      |      |      |    |      |          |  |  |  |

|-----------------|-------------------------------------|------|------|------|------|------|----|------|----------|--|--|--|

| Symbol:         | A                                   | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |  |  |

| Min:            | 0.85                                | 0.05 | 4.90 | 6.20 | 4.30 | 0.40 | 0° | 0.20 | 0.65 BSC |  |  |  |

| Max:            | 0.95                                | 0.20 | 5.10 | 6.60 | 4.50 | 0.80 | 8° | 0.25 | 0.00 BSC |  |  |  |

# **Revision History**

| DATE      | REVISION                                                                   | PAGE  |

|-----------|----------------------------------------------------------------------------|-------|

| 2020-3-8  | New                                                                        | 1-12  |

| 2023-8-31 | Update encapsulation type、Update Lead Temperature、Updated DIP-14 dimension | 1、3、9 |

#### **IMPORTANT STATEMENT:**

Huaguan Semiconductor reserves the right to change its products and services without notice. Before ordering, the customer shall obtain the latest relevant information and verify whether the information is up to date and complete. Huaguan Semiconductor does not assume any responsibility or obligation for the altered documents.

Customers are responsible for complying with safety standards and taking safety measures when using Huaguan Semiconductor products for system design and machine manufacturing. You will bear all the following responsibilities: Select the appropriate Huaguan Semiconductor products for your application; Design, validate and test your application; Ensure that your application meets the appropriate standards and any other safety, security or other requirements. To avoid the occurrence of potential risks that may lead to personal injury or property loss.

Huaguan Semiconductor products have not been approved for applications in life support, military, aerospace and other fields, and Huaguan Semiconductor will not bear the consequences caused by the application of products in these fields. All problems, responsibilities and losses arising from the user's use beyond the applicable area of the product shall be borne by the user and have nothing to do with Huaguan Semiconductor, and the user shall not claim any compensation liability against Huaguan Semiconductor by the terms of this Agreement.

The technical and reliability data (including data sheets), design resources (including reference designs), application or other design suggestions, network tools, safety information and other resources provided for the performance of semiconductor products produced by Huaguan Semiconductor are not guaranteed to be free from defects and no warranty, express or implied, is made. The use of testing and other quality control technologies is limited to the quality assurance scope of Huaguan Semiconductor. Not all parameters of each device need to be tested.

The documentation of Huaguan Semiconductor authorizes you to use these resources only for developing the application of the product described in this document. You have no right to use any other Huaguan Semiconductor intellectual property rights or any third party intellectual property rights. It is strictly forbidden to make other copies or displays of these resources. You should fully compensate Huaguan Semiconductor and its agents for any claims, damages, costs, losses and debts caused by the use of these resources. Huaguan Semiconductor accepts no liability for any loss or damage caused by infringement.

## 单击下面可查看定价,库存,交付和生命周期等信息

>>HGSEMI (华冠)