## **DTMF Generators**

#### **Features**

Operating voltage: 2.0V~5.5V

Serial mode for the HG9200A

Serial/parallel mode for the HG9200B

Low standby current

Low total harmonic distortion

3.58MHz crystal or ceramic resonator

HG9200A: 8-pin DIP/SOP package

HG9200B: 14-pin SOP package

### **Ordering Information**

| DEVICE      | Package Type | MARKING | Packing | Packing Qty  |

|-------------|--------------|---------|---------|--------------|

| HG9200AN    | DIP-8        | HG9200A | TUBE    | 2000pcs/box  |

| HG9200AM/TR | SOP-8        | HG9200A | REEL    | 2500pcs/reel |

| HG9200BM/TR | SOP-14       | HG9200B | REEL    | 2500pcs/reel |

## **General Description**

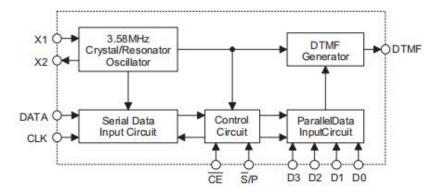

The HG9200A/B tone generators are designed for MCU interfaces. They can be instructed by a MCU to gener ate 16 dual tones and 8 single tones from the DTMF pin. The HG9200A provides a serial mode whereas the HG9200B contains a selectable serial/parallel mode interface for various applications such as security systems, home automation, remote control through telephone lines, communication systems, etc.

### **Block Diagram**

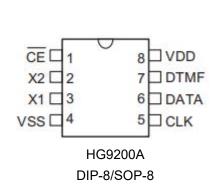

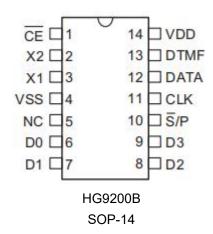

## **Pin Assignment**

## **Pin Description**

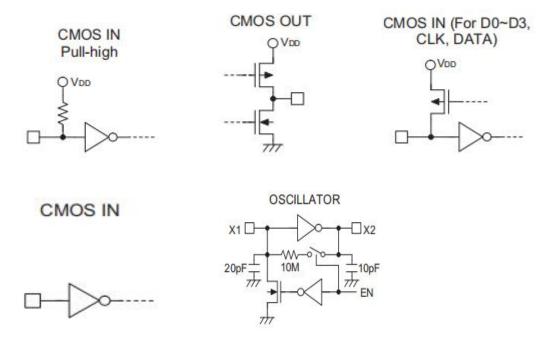

| Pin Name | I/O | Internal<br>Connection              | Description                                                                                                                                                                                                                               |

|----------|-----|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CE       | ı   | CMOS IN<br>Pull-high                | Chip enable, active low                                                                                                                                                                                                                   |

| X2       | 0   |                                     | The system oscillator consists of an inverter, a bias resistor, and the required load                                                                                                                                                     |

| X1       | ı   | Oscillator                          | capacitor on chip.  The oscillator function can be implemented by Connect a standard 3.579545MHz crystal to the X1 and X2 terminals.                                                                                                      |

| VSS      |     |                                     | Negative power suppl, ground                                                                                                                                                                                                              |

| NC       |     |                                     | No connection                                                                                                                                                                                                                             |

| D0~D3    | ı   | CMOS IN<br>Pull-high or<br>Floating | Data inputs for the parallel mode When the IC is operating in the serial mode, the data input terminals (D0~D3) are included with a pull-high resistor. When the IC is operating in the parallel mode, these pins become floating.        |

| S/P      | I   | CMOS IN                             | Operation mode selection input  S/P="H": Parallel mode  S/P="L": Serial mode                                                                                                                                                              |

| CLK      | I   | CMOS IN<br>Pull-high or<br>Floating | Data synchronous clock input for the serial mode When the IC is operating in the parallel mode, the input terminal (CLK) is included with a pull-high resistor. When the IC is operating in the serial mode, this pin be- comes floating. |

# HG9200A/HG9200B

| Pin Name | I/O | Internal<br>Connection              | Description                                                                                                                                                                                                                        |

|----------|-----|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATA     | I   | CMOS IN<br>Pull-high or<br>Floating | Data input terminal for the serial mode  When the IC is operating in the parallel mode, the input terminal (DATA) is included with a pull-high resistor. When the IC is operating in the serial mode, this pin be- comes floating. |

| DTMF     | 0   | CMOS OUT                            | Output terminal of the DTMF signal                                                                                                                                                                                                 |

| VDD      |     |                                     | Positive power supply, 2.0V~5.5V for normal operation                                                                                                                                                                              |

### Approximate internal connection circuits

## **Absolute Maximum Ratings**

| Condition                                | Min     | Max     | UNITS |

|------------------------------------------|---------|---------|-------|

| Supply Voltage                           | -0.3    | 6       | V     |

| Input Voltage                            | VSS-0.3 | VDD+0.3 | V     |

| Storage Temperature                      | -50     | 125     | °C    |

| Operating Temperature                    | -20     | 75      | °C    |

| Lead Temperature (Soldering, 10 seconds) | -       | 245     | °C    |

Note: These are stress ratings only. Stresses exceeding the range specified under Absolute Maximum Ratings may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

#### **Electrical Characteristics**

| 0                | D                              |      | Test Conditions                                       | N4:                 | T      |                    | 11!4 |

|------------------|--------------------------------|------|-------------------------------------------------------|---------------------|--------|--------------------|------|

| Symbol           | Parameter                      | VDD  | Conditions                                            | Min.                | Тур.   | Max.               | Unit |

| V <sub>DD</sub>  | Operating Voltage              | -    | -                                                     | 2                   | -      | 5.5                | V    |

|                  |                                |      | S/P=V <sub>DD</sub> ,D0∼D3=V <sub>SS</sub> ,          | -                   | 240    | 2500               |      |

| I <sub>DD</sub>  | Operating Current              | 5.0V | CE=V <sub>SS</sub> , No load                          | -                   | 950    | 3000               | μA   |

| V <sub>IL</sub>  | "Low"Input Voltage             | -    | -                                                     | VSS                 | -      | 0.2V <sub>DD</sub> | V    |

| V <sub>IH</sub>  | "High" Input Voltage           | -    | -                                                     | 0.8V <sub>DD</sub>  | -      | $V_{DD}$           | V    |

|                  | Standby Current                | 2.5V |                                                       | -                   | -      | 1                  |      |

| I <sub>STB</sub> | Standby Current                | 5.0V | $\overline{S}/P=V_{DD},\overline{CE}=V_{DD},$ no load | -                   | -      | 2                  | μA   |

| Б                | Dull high Desistance           | 2.5V | VOL=0V                                                | 120                 | 180    | 270                | 1.0  |

| $R_P$            | Pull-high Resistance           | 5.0V | VOL=UV                                                | 45                  | 68     | 100                | kΩ   |

| +                | DTMF Output Delay Time         |      |                                                       |                     | tUP+6  | tUP+8              | mo   |

| t <sub>DE</sub>  | (Parallel Mode)                | 5V   | -                                                     | -                   | IUFTO  | IUFTO              | ms   |

| $V_{TDC}$        | DTMF Output DC Level           | 2V~  | DTMF Output                                           | 0.45V <sub>DD</sub> | _      | 0.75Vnn            | V    |

| V IDC            | D Tivii Output DO Level        | 5.5V | DTMI Output                                           | 0.4300              |        | U.73V              | V    |

| I <sub>TOL</sub> | DTMF Sink Current              | 2.5V | $V_{\text{DTMF}}$ =0.5 $V$                            | 0.1                 |        |                    | mA   |

| $V_{\text{TAC}}$ | DTMF Output AC Level           | 2.5V | Row group, RL= $5k\Omega$                             | 0.12                | 0.15   | 0.18               | Vrms |

| A <sub>CR</sub>  | Column Pre-emphasis            | 2.5V | Row group=0dB                                         | 1                   | 2      | 3                  | dB   |

| $R_L$            | DTMF Output Load               | 2.5V | tHD ≤-23dB                                            | 5                   | -      | -                  | kΩ   |

| t <sub>HD</sub>  | Tone Signal Distortion         | 2.5V | RL=5kΩ                                                | -                   | 30     | 23                 | dB   |

| f <sub>CLK</sub> | Clock Input Rate (Serial Mode) | -    | -                                                     | -                   | 100    | 500                | kHz  |

|                  | Oscillator Starting Time       |      | The time from $\overline{\sf CE}$ falling             |                     |        |                    |      |

| t <sub>UP</sub>  | (When $\overline{CE}$ is low)  | 5.0V | edge to normal oscillator                             | -                   | -      | 10                 | ms   |

|                  | (WITEH CE IS IOW)              |      | operation                                             |                     |        |                    |      |

| fosc             | System Frequency               | -    | Crystal=3.5795MHz                                     | 3.5759              | 3.5795 | 3.5831             | MHz  |

## **Functional Description**

The HG9200A/B are DTMF generators for MCU interfaces. They are controlled by a MCU in the serial mode or the parallel mode (for the HG9200B only).

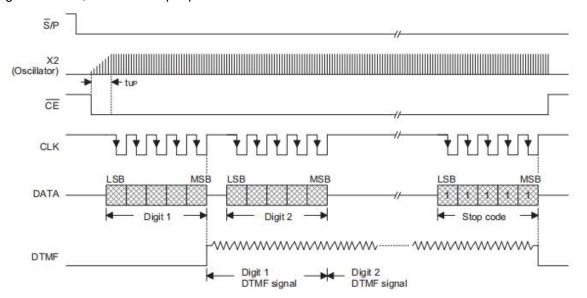

## Serial mode (HG9200A/B)

The HG9200A/B employ a data input, a 5-bit code, and a synchronous clock to transmit a DTMF signal. Every digit of a phone number to be transmitted is selected by a series of inputs which consist of 5-bit data. Of the 5 bits, the D0(LSB) is the first received bit. The HG9200A/B will latch data on the falling edge of the clock (CLK pin). The relationship between the digital codes and the tone output frequency is shown in Table 1. As for the control timing diagram, refer to Figure 1.

When the system is operating in the serial mode a pull-high resistor is attached to D0~D3 (for parallel mode) on the input terminal.

Table 1: Digits vs. input data vs. tone output frequency (serial mode)

| Digit    | D4 | D3 | D2 | D1 | D0 | Tone Output<br>Frequency (Hz) |

|----------|----|----|----|----|----|-------------------------------|

| 1        | 0  | 0  | 0  | 0  | 1  | 697+1209                      |

| 2        | 0  | 0  | 0  | 1  | 0  | 697+1336                      |

| 3        | 0  | 0  | 0  | 1  | 1  | 697+1477                      |

| 4        | 0  | 0  | 1  | 0  | 0  | 770+1209                      |

| 5        | 0  | 0  | 1  | 0  | 1  | 770+1336                      |

| 6        | 0  | 0  | 1  | 1  | 0  | 770+1477                      |

| 7        | 0  | 0  | 1  | 1  | 1  | 852+1209                      |

| 8        | 0  | 1  | 0  | 0  | 0  | 852+1336                      |

| 9        | 0  | 1  | 0  | 0  | 1  | 852+1477                      |

| 0        | 0  | 1  | 0  | 1  | 0  | 941+1336                      |

| *        | 0  | 1  | 0  | 1  | 1  | 941+1209                      |

| #        | 0  | 1  | 1  | 0  | 0  | 941+1477                      |

| А        | 0  | 1  | 1  | 0  | 1  | 697+1633                      |

| В        | 0  | 1  | 1  | 1  | 0  | 770+1633                      |

| С        | 0  | 1  | 1  | 1  | 1  | 852+1633                      |

| D        | 0  | 0  | 0  | 0  | 0  | 941+1633                      |

| -        | 1  | 0  | 0  | 0  | 0  | 697                           |

| -        | 1  | 0  | 0  | 0  | 1  | 770                           |

| -        | 1  | 0  | 0  | 1  | 0  | 852                           |

| -        | 1  | 0  | 0  | 1  | 1  | 941                           |

| -        | 1  | 0  | 1  | 0  | 0  | 1209                          |

| -        | 1  | 0  | 1  | 0  | 1  | 1336                          |

| -        | 1  | 0  | 1  | 1  | 0  | 1477                          |

| -        | 1  | 0  | 1  | 1  | 1  | 1633                          |

| DTMF OFF | 1  | 1  | 1  | 1  | 1  | -                             |

Note: The codes not listed in Table 1 are not used D4 is MSB

For the HG9200B, the  $\overline{S}/P$  pin has to be connected low for serial mode operation.

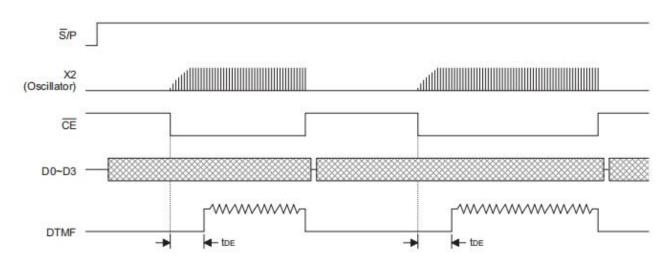

#### Parallel mode (HG9200B)

The HG9200B provides four data inputs D0 $\sim$ D3 to generate their corresponding DTMF signals. The  $\overline{S}$ /P has to be connected high to select the parallel operation mode. Then the input data codes should be determined. Finally, the  $\overline{CE}$  is connected low to transmit the DTMF signal from the DTMF pin.

The TDE time (about 6ms) will be delayed from the  $\overline{\text{CE}}$  falling edge to the DTMF signal output.

The relationship between the digital codes and the tone output frequency is illustrated in Table 2. As for the control timing diagram, see Figure 2. When the system is operating in the parallel mode, D0~D3 are all in the floating state. Thus, these data input pins should not float.

Figure 1

Table 2: Digits vs. input data vs. tone output frequency (parallel mode)

| Digit | D3 | D2 | D1 | D0 | Tone Output<br>Frequency (Hz) |

|-------|----|----|----|----|-------------------------------|

| 1     | 0  | 0  | 0  | 1  | 697+1209                      |

| 2     | 0  | 0  | 1  | 0  | 697+1336                      |

| 3     | 0  | 0  | 1  | 1  | 697+1477                      |

| 4     | 0  | 1  | 0  | 0  | 770+1209                      |

| 5     | 0  | 1  | 0  | 1  | 770+1336                      |

| 6     | 0  | 1  | 1  | 0  | 770+1477                      |

| 7     | 0  | 1  | 1  | 1  | 852+1209                      |

| 8     | 1  | 0  | 0  | 0  | 852+1336                      |

| 9     | 1  | 0  | 0  | 1  | 852+1477                      |

| 0     | 1  | 0  | 1  | 0  | 941+1336                      |

| *     | 1  | 0  | 1  | 1  | 941+1209                      |

| #     | 1  | 1  | 0  | 0  | 941+1477                      |

| А     | 1  | 1  | 0  | 1  | 697+1633                      |

| В     | 1  | 1  | 1  | 0  | 770+1633                      |

| С     | 1  | 1  | 1  | 1  | 852+1633                      |

| D     | 0  | 0  | 0  | 0  | 941+1633                      |

Note:The data (D0~D3)should be ready before the  $\overline{\text{CE}}$  becomes low.

Figure 2

## **Tone frequency**

| Output Fre | quency (Hz) | - %Error |  |  |

|------------|-------------|----------|--|--|

| Specified  | Actual      | %EITOI   |  |  |

| 697        | 699         | +0.29%   |  |  |

| 770        | 766         | -0.52%   |  |  |

| 852        | 847         | -0.59%   |  |  |

| 941        | 948         | +0.74%   |  |  |

| 1209       | 1215        | +0.50%   |  |  |

| 1336       | 1332        | -0.30%   |  |  |

| 1477       | 1472        | -0.34%   |  |  |

<sup>%</sup> Error does not contain the crystal frequency drift

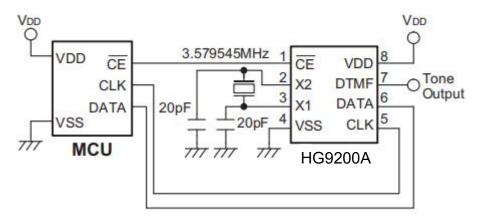

## **Application Circuits**

#### Serial mode

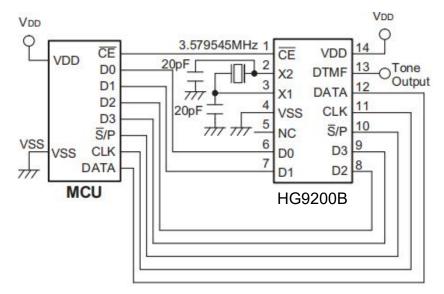

#### Serial/parallel mode

# **Physical Dimensions**

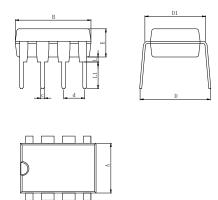

### DIP-8

| Dimensions In Millimeters(DIP-8) |      |      |      |      |      |      |      |      |      |      |          |

|----------------------------------|------|------|------|------|------|------|------|------|------|------|----------|

| Symbol:                          | Α    | В    | D    | D1   | Е    | L    | L1   | а    | b    | С    | d        |

| Min:                             | 6.10 | 9.00 | 8.10 | 7.42 | 3.10 | 0.50 | 3.00 | 1.50 | 0.85 | 0.40 | 2.54.000 |

| Max:                             | 6.68 | 9.50 | 10.9 | 7.82 | 3.55 | 0.70 | 3.60 | 1.55 | 0.90 | 0.50 | 2.54 BSC |

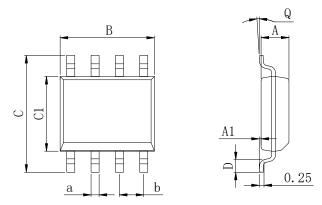

$SOP\text{--}8_{\ (150mil)}$

| Dimensions In Millimeters(SOP-8) |      |      |      |      |      |      |    |      |          |  |

|----------------------------------|------|------|------|------|------|------|----|------|----------|--|

| Symbol:                          | Α    | A1   | В    | С    | C1   | D    | Ø  | а    | b        |  |

| Min:                             | 1.35 | 0.05 | 4.90 | 5.80 | 3.80 | 0.40 | 0° | 0.35 | 1.27 BSC |  |

| Max:                             | 1.55 | 0.20 | 5.10 | 6.20 | 4.00 | 0.80 | 8° | 0.45 | 1.27 BSC |  |

# **Physical Dimensions**

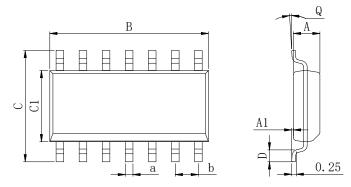

### SOP-14

| Dimensions In M | Dimensions In Millimeters(SOP-14) |      |      |      |      |      |    |      |          |  |  |  |

|-----------------|-----------------------------------|------|------|------|------|------|----|------|----------|--|--|--|

| Symbol:         | Α                                 | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |  |  |

| Min:            | 1.35                              | 0.05 | 8.55 | 5.80 | 3.80 | 0.40 | 0° | 0.35 | 1.27 BSC |  |  |  |

| Max:            | 1.55                              | 0.20 | 8.75 | 6.20 | 4.00 | 0.80 | 8° | 0.45 | 1.27 650 |  |  |  |

## **Revision History**

| DATE      | REVISION                                                                  | PAGE  |

|-----------|---------------------------------------------------------------------------|-------|

| 2014-6-9  | New                                                                       | 1-12  |

| 2023-8-30 | Update encapsulation type、Update Lead Temperature、Updated DIP-8 dimension | 1、3、9 |

## HG9200A/HG9200B

#### **IMPORTANT STATEMENT:**

Huaguan Semiconductor reserves the right to change its products and services without notice. Before ordering, the customer shall obtain the latest relevant information and verify whether the information is up to date and complete. Huaguan Semiconductor does not assume any responsibility or obligation for the altered documents.

Customers are responsible for complying with safety standards and taking safety measures when using Huaguan Semiconductor products for system design and machine manufacturing. You will bear all the following responsibilities: Select the appropriate Huaguan Semiconductor products for your application; Design, validate and test your application; Ensure that your application meets the appropriate standards and any other safety, security or other requirements. To avoid the occurrence of potential risks that may lead to personal injury or property loss.

Huaguan Semiconductor products have not been approved for applications in life support, military, aerospace and other fields, and Huaguan Semiconductor will not bear the consequences caused by the application of products in these fields. All problems, responsibilities and losses arising from the user's use beyond the applicable area of the product shall be borne by the user and have nothing to do with Huaguan Semiconductor, and the user shall not claim any compensation liability against Huaguan Semiconductor by the terms of this Agreement.

The technical and reliability data (including data sheets), design resources (including reference designs), application or other design suggestions, network tools, safety information and other resources provided for the performance of semiconductor products produced by Huaguan Semiconductor are not guaranteed to be free from defects and no warranty, express or implied, is made. The use of testing and other quality control technologies is limited to the quality assurance scope of Huaguan Semiconductor. Not all parameters of each device need to be tested.

The documentation of Huaguan Semiconductor authorizes you to use these resources only for developing the application of the product described in this document. You have no right to use any other Huaguan Semiconductor intellectual property rights or any third party intellectual property rights. It is strictly forbidden to make other copies or displays of these resources. You should fully compensate Huaguan Semiconductor and its agents for any claims, damages, costs, losses and debts caused by the use of these resources. Huaguan Semiconductor accepts no liability for any loss or damage caused by infringement.

## 单击下面可查看定价,库存,交付和生命周期等信息

>>HGSEMI (华冠)