### **DualPrecisionMonostable**

### **General Description**

The CD4538B is a dual, precision monostable multivibrator with independent trigger and reset controls. The device is retriggerable and resettable, and the control inputs are inter- nally latched. Two trigger inputs are provided to allow either rising or falling edge triggering. The reset inputs are active low and prevent triggering while active. Precise control of output pulse-width has been achieved using linear CMOS techniques. The pulse duration and accuracy are deter-mined by external components Rx and Cx. The device does not allow the timing capacitor to discharge through the tim- ing pin on power-down condition. For this reason, no exter-nal protection resistor is required in series with the timing pin. Input protection from static discharge is provided on all pins.

#### **Features**

- Wide supply voltage range:5.0V to 15V

- High noise immunity:0.45 V<sub>CC</sub> (typ.)

- Low power TTL compatibility:Fan out of 2 driving 74L or 1 driving 74LS

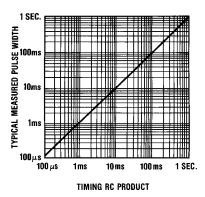

- New formula: PWout = RC (PW in seconds, R in Ohms, C in Farads)

- ±1.0% pulse-width variation from part to part (typ.)

- Wide pulse-width rang:1 µS to ∞

- Separate latched reset inputs

- Symmetrical output sink and source capability

- Low standby current:5 nA (typ.)@ 5 VDC

- Pin compatible to CD4528B

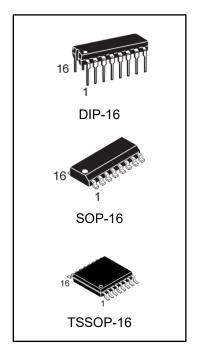

## **Ordering Information**

| DEVICE       | Package Type | MARKING | Packing | Packing Qty  |

|--------------|--------------|---------|---------|--------------|

| CD4538BE     | DIP-16       | CD4538B | TUBE    | 1000pcs/box  |

| CD4538BM/TR  | SOP-16       | CD4538B | REEL    | 2500pcs/reel |

| CD4538BMT/TR | TSSOP-16     | CD4538B | REEL    | 2500pcs/reel |

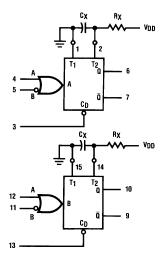

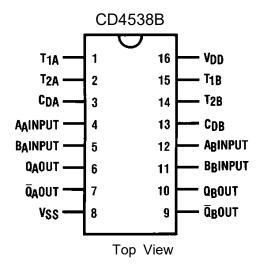

## **Block and Connection Diagrams**

RX and CX are External Components  $V_{\text{DD}} - \text{Pin 16}$

## V<sub>SS</sub>-Pin 8

## **Dual-In-Line Package**

### **Truth Table**

|       | Inputs   | Out | puts |   |

|-------|----------|-----|------|---|

| Clear | Α        | В   | Q    | Q |

| L     | Х        | Х   | L    | Н |

| X     | Н        | X   | L    | Н |

| X     | X        | L   | L    | Н |

| Н     | L        | ↓   | М    | W |

| Н     | <b>↑</b> | Н   | M    | W |

|       |          |     |      |   |

H= High Level L

L= Low Level

↑= Transition from Low to High

↓= Transition from High to Low

M= One High Level Pulse

W= One Low Level Pulse

X= Irrelevant

### **Maximum Ratings**

| Symbol          | Parameter                 | Min                       | Max | Unit |            |  |  |

|-----------------|---------------------------|---------------------------|-----|------|------------|--|--|

| VDD             | DC Supply Voltage         | DC Supply Voltage         |     |      |            |  |  |

| V <sub>IN</sub> | Input Voltage             | Input Voltage             |     |      |            |  |  |

| Ts              | Storage Temperature Range | Storage Temperature Range |     |      |            |  |  |

| P <sub>D</sub>  | Power Dissipation         | Dual-In-Line              | 70  | 00   | mW         |  |  |

| FD              | Fower Dissipation         | Small Outline             | 500 |      | mW         |  |  |

| TL              | Lead Temperature          | Soldering, 10 seconds     | 26  | 30   | $^{\circ}$ |  |  |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed, they are not meant to imply that the devices should be operated at these limits. The tables of "Recommended Operating Conditions" and "Electrical Characteristics" provide conditions for acutal device operation.

Note 2: VSS e 0V unless otherwise specified.

## **Recommended Operating Conditions**

| Symbol          | Parameter                   | Min | Max | Unit            |

|-----------------|-----------------------------|-----|-----|-----------------|

| VDD             | DC Supply Voltage           | 5   | 15  | $V_{DC}$        |

| V <sub>IN</sub> | Input Voltage               | 0   | -   | V <sub>DC</sub> |

| T <sub>A</sub>  | Operating Temperature Range | -40 | +85 | °C              |

### **DC Electrical Characteristics**

| Cumb al | Downwater                                | Conditions                                                                                 | -40                   | )°C                  | +25°C                 |                         |                      | +85°C                 |                      |       |

|---------|------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------|----------------------|-----------------------|-------------------------|----------------------|-----------------------|----------------------|-------|

| Symbol  | Parameter                                | Conditions                                                                                 | Min                   | Max                  | Min                   | Тур                     | Max                  | Min                   | Max                  | Units |

| IDD     | Quiescent<br>Device Current              | VDD=5V<br>VDD=10V<br>VDD=15V<br>VIL=VSS<br>VDD=15V<br>All Outputs Open                     |                       | 20<br>40<br>80       |                       | 0.005<br>0.010<br>0.015 | 20<br>40<br>80       |                       | 150<br>300<br>600    | μА    |

| VOL     | Low Level<br>Output Voltage              | VDD=5V<br>VDD=10V<br>VDD=15V  VIH=VDD,ViL=Vss                                              |                       | 0.05<br>0.05<br>0.05 |                       | 0<br>0<br>0             | 0.05<br>0.05<br>0.05 |                       | 0.05<br>0.05<br>0.05 | V     |

| VOH     | High Level<br>Output Voltage             | VDD=5V<br>VDD=10V<br>VDD=15V VIH=VDD,ViL=Vss                                               | 4.95<br>9.95<br>14.95 |                      | 4.95<br>9.95<br>14.95 | 5<br>10<br>15           |                      | 4.95<br>9.95<br>14.95 |                      | V     |

| VIL     | Low Level<br>Input Voltage               | IIoI<1 μA<br>VDD=5V,VO=0.5V of 4.5V<br>VDD=10V,VO=1.0V of 9.0V<br>VDD=15V,VO=1.5V of 13.5V |                       | 1.5<br>3.0<br>4.0    |                       | 2.25<br>4.50<br>6.75    | 1.5<br>3.0<br>4.0    |                       | 1.5<br>3.0<br>4.0    | V     |

| VIH     | High Level<br>Input Voltage              | IIol<1 µA<br>VDD=5V,VO=0.5V of 4.5V<br>VDD=10V,VO=1.0V of 9.0V<br>VDD=15V,VO=1.5V of 13.5V | 3.5<br>7.0<br>11.0    |                      | 3.5<br>7.0<br>11.0    | 2.75<br>5.50<br>8.25    |                      | 3.5<br>7.0<br>11.0    |                      | V     |

| IOL     | Low Level Output Current (Note 3)        | VDD=5V,VO 0.4V<br>VDD=10V,VO=0.5V<br>VDD=15V,VO=1.5V VIH=VDD<br>VIL=VSS                    | 0.52<br>1.3<br>3.6    |                      | 0.44<br>1.1<br>3.0    | 0.88<br>2.25<br>8.8     |                      | 0.36<br>0.9<br>2.4    |                      | mA    |

| ЮН      | High Level<br>Output Current<br>(Note 3) | VDD=5V,VO=4.6<br>VDD=10V,VO=9.5V<br>VDD=15V,VO=13.5V                                       | -0.52<br>-1.3<br>-3.6 |                      | -0.44<br>-1.1<br>-3.0 | -0.88<br>-2.25<br>-8.8  |                      | -0.36<br>-0.9<br>-2.4 |                      | mA    |

| IIN     | Input Current,<br>Pin2 or 14             | VDD=15V, VIN=0V or 15V                                                                     |                       | ±0.02                |                       | ±10 <sup>-5</sup>       | ±0.05                |                       | ±0.5                 | μΑ    |

| IIN     | Input Current<br>Other Inputs            | VDD=15V, VIN=0V or 15V                                                                     |                       | ±0.3                 |                       | ±10 <sup>-5</sup>       | ±0.3                 |                       | ±1.0                 | μА    |

Note 3: IOH and IOL are tested one output at a time.

#### **AC Electrical Characteristics**

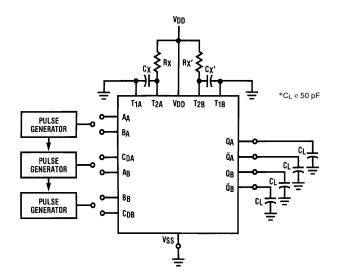

\* TA = 25°C, C<sub>L</sub>=50 pF, and tr= tf= 20 ns unless otherwise specified

| Symbol                                                                      | Parameter                                                                                 | Condition                                                                                                               | าร                                                      | Min                  | Тур                   | Max                     | Units    |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------|-----------------------|-------------------------|----------|

| tTLH,<br>tTHL                                                               | Output Transition Time                                                                    | $V_{DD}$ =5V<br>$V_{DD}$ =10V<br>$V_{DD}$ =15V                                                                          |                                                         |                      | 100<br>50<br>40       | 200<br>100<br>80        | ns       |

| tPLH,<br>tPHL                                                               | Propagation Delay Time                                                                    | Trigger Operation—<br>A orB toQ orQ<br>$V_{DD}=5V$<br>$V_{DD}=10V$<br>$V_{DD}=15V$<br>Reset Operation—<br>$C_D$ toQ orQ |                                                         |                      | 300<br>150<br>100     | 600<br>300<br>220       | ns       |

|                                                                             |                                                                                           | $V_{DD}=5V$ $V_{DD}=10V$ $V_{DD}=15V$                                                                                   |                                                         |                      | 250<br>125<br>95      | 500<br>250<br>190       | ns       |

| tWL,<br>tWH                                                                 | Minimum Input Pulse Width A, B, or C <sub>D</sub>                                         | $V_{DD}$ =5V<br>$V_{DD}$ =10V<br>$V_{DD}$ =15V                                                                          |                                                         |                      | 35<br>30<br>25        | 70<br>60<br>50          | ns       |

| tRR                                                                         | Minimum Retrigger Time                                                                    | $V_{DD}=5V$ $V_{DD}=10V$ $V_{DD}=15V$                                                                                   |                                                         |                      | 0                     | 0<br>0<br>0             | ns       |

| CIN                                                                         | Input Capacitance                                                                         | Pin 2 or 14<br>Other Inputs                                                                                             |                                                         |                      | 10<br>5               | 7.5                     | pF       |

|                                                                             |                                                                                           | Rχ=100 kΩ                                                                                                               | $V_{DD}$ =5V<br>$V_{DD}$ =10V<br>$V_{DD}$ =15V          | 208<br>211<br>216    | 226<br>230<br>235     | 244<br>248<br>254       | μS       |

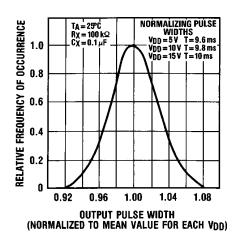

| PWOUT                                                                       | Output Pulse Width (Q or Q)<br>( <b>Note</b> : For Typical<br>Distribution, see Figure 9) | Rχ=100 kΩ<br>Cχ=0.1μF                                                                                                   | $V_{DD}$ =5 $V$<br>$V_{DD}$ =10 $V$<br>$V_{DD}$ =15 $V$ | 8.83<br>9.02<br>9.20 | 9.60<br>9.80<br>10.00 | 10.37<br>10.59<br>10.80 | ms       |

|                                                                             |                                                                                           | Rχ=100kΩ<br>Cχ=10.0 μF                                                                                                  | $V_{DD}$ =5V<br>$V_{DD}$ =10V<br>$V_{DD}$ =15V          | 0.87<br>0.89<br>0.91 | 0.95<br>0.97<br>0.99  | 1.03<br>1.05<br>1.07    | S        |

| Pulse Width Match between Circuits in the Same Package Cχ=0.1 μF, Rχ=100 kΩ |                                                                                           | Rχ=100 kΩ<br>Cχ=0.1 μF                                                                                                  | $V_{DD}$ =5 $V$<br>$V_{DD}$ =10 $V$<br>$V_{DD}$ =15 $V$ |                      | ±1<br>±1<br>±1        |                         | %        |

| Operatir                                                                    | ng Conditions                                                                             |                                                                                                                         |                                                         |                      | I                     |                         |          |

| RX<br>CX                                                                    | External Timing Resistance<br>External Timing Capacitance                                 |                                                                                                                         |                                                         | 5.0<br>0             |                       | **<br>No Limit          | kΩ<br>pF |

Note 4:AC parameters are guaranteed by DC correlated testing.

Note 5:The maximum usable resistance  $R_X$  is a function of the leakage of the Capacitor  $C_X$ , leakage of the CD4538B, and leakage due to board layout, surface resistance, etc.

## **Logic Diagram**

## **Theory of Operation**

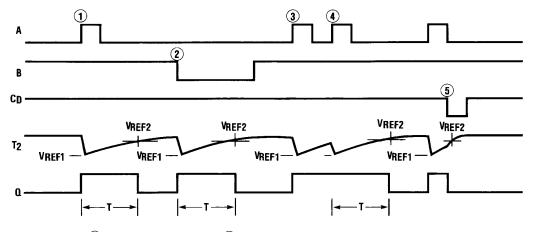

- POSITIVE EDGE TRIGGER NEGATIVE EDGE TRIGGER

- POSITIVE EDGE RE-TRIGGER (PULSE LENGTHENING) RESET (PULSE SHORTENING)

- POSITIVE EDGE TRIGGER

FIGURE 2

#### **Trigger Operation**

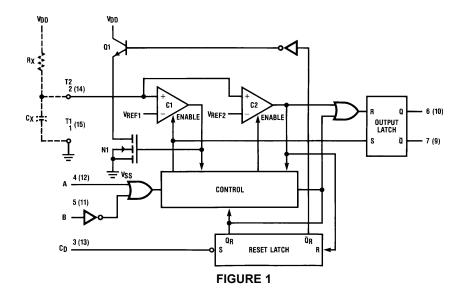

The block diagram of the CD4538B is shown in Figure 1, with circuit operation following.

As shown in Figures 1 and 2, before an input trigger occurs, the monostable is in the quiescent state with the Q output low, and the timing capacitor  $C_X$  completely charged to  $V_{DD}$ . When the trigger input A goes from  $V_{SS}$  to  $V_{DD}$  (while inputs B and  $C_D$  are held to  $V_{DD}$ ) a valid trigger is recog- nized, which turns on comparator C1 and N-Channel tran- sistor N1. At the same time the output latch is set. With transistor N1 on, the capacitor  $C_X$  rapidly discharges toward  $V_{SS}$  until  $V_{REF1}$  is reached. At this point the output of com- parator C1 changes state and transistor N1 turns off. Com- parator C1 then turns off while at the same time comparator C2 turns on. With transistor N1 off, the capacitor  $C_X$  begins to charge through the timing resistor, RX, toward  $V_{DD}$ . When the voltage across  $C_X$  equals  $V_{REF2}$ , comparator C2 changes state causing the output latch to reset (Q goes low) while at the same time disabling comparator C2. This ends the timing cycle with the monostable in the quiescent state, waiting for the next trigger.

A valid trigger is also recognized when trigger input B goes from  $V_{DD}$  to  $V_{SS}$  (while input A is at VSS and input CD is at  $V_{DD}$ )<sup>2</sup>.

It should be noted that in the quiescent state  $C_X$  is fully charged to  $V_{DD}$ , causing the current through resistor  $R_X$  to be zero. Both comparators are "off" with the total device current due only to reverse junction leakages. An added feature of the CD4538B is that the output latch is set via the input trigger without regard to the capacitor voltage. Thus, propagation delay from trigger to Q is independent of the value of  $C_X$ ,  $R_X$ , or the duty cycle of the input waveform.

## **Retrigger Operation**

The CD4538B is retriggered if a valid trigger occurs <sup>®</sup> fol lowed by another valid triggerm <sup>®</sup> before the Q output has returned to the quiescent (zero) state. Any retrigger, after the timing node voltage at pin 2 or 14 has begun to rise from VREF1, but has not yet reached VREF2, will cause an in crease in output pulse width T. When a valid retrigger is initiatedm<sup>®</sup>, the voltage at T2 will again drop to VREF1 before progressing along the RC charging curve toward VDD. The Q output will remain high until time T, after the last valid retrigger.

### **Reset Operation**

The CD4538B may be reset during the generation of the output pulse. In the reset mode of operation, an input pulse on CD sets the reset latch and causes the capacitor to be fast charged to VDD by turning on transistor Q1  $^{\odot}$ . When the voltage on the capacitor reaches VREF2, the reset latch will clear and then be ready to accept another pulse. If the CD input is held low, any trigger inputs that occur will be inhibited and the Q and  $\overline{Q}$  outputs of the output latch will not change. Since the Q output is reset when an input low level is detected on the CD input, the output pulse T can be made significantly shorter than the minimum pulse width specification

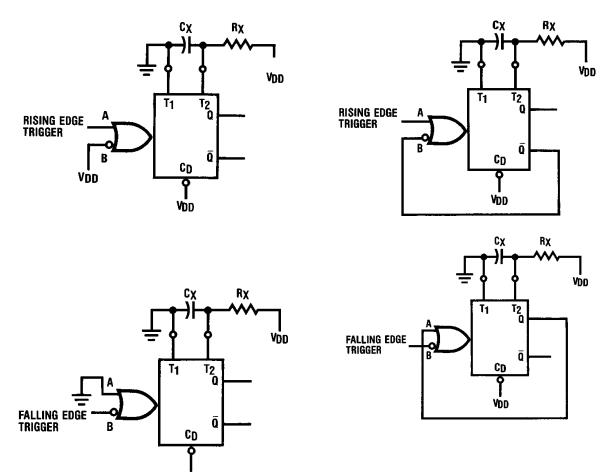

## **Typical Applications**

FIGURE 3. Retriggerable Monostables Circuitry

FIGURE 4. Non-Retriggerable Monostables Circuitry

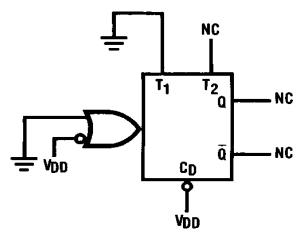

FIGURE 5. Connection of Unused Sections

## **Typical Applications**

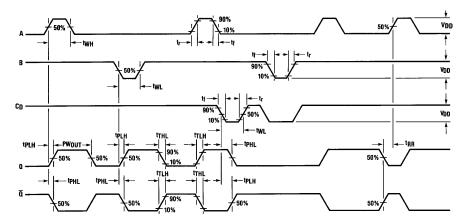

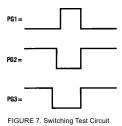

FIGURE 6. Switching Test Waveforms

Input Connections

| Characteristics                                                            | CD              | Α               | В               |

|----------------------------------------------------------------------------|-----------------|-----------------|-----------------|

| tPLH, tPHL, tTLH, tTHL<br>PWOUT, tWH, tWL                                  | V <sub>DD</sub> | PG1             | V <sub>DD</sub> |

| tPLH, tPHL, tTLH, tTHL<br>PWOUT, tWH, tWL                                  | V <sub>DD</sub> | V <sub>SS</sub> | PG2             |

| <sup>t</sup> PLH(R), <sup>t</sup> PHL(R), <sup>t</sup> WH, <sup>t</sup> WL | PG3             | PG1             | PG2             |

\*Includes capacitance of probes, wiring, and fixture parasitic Note: Switching test waveforms for PG1, PG2, PG3 are shown in Figure 6.

20 ns — — — — — — — — — — — — VDD — — — 0 V

Duty Cycle e 50%

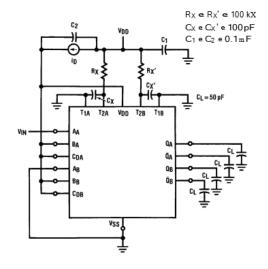

FIGURE8.Power Dissipation Test

Circuit and Waveforms

### **Typical Applications**

FIGURE 9. Typical Normalized Distribution of Units for Output Pulse Width

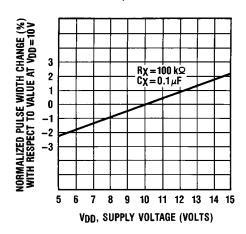

FIGURE 10. Typical Pulse Width Variation as a Function of Supply Voltage  $V_{DD}$

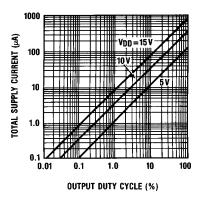

FIGURE 11. Typical Total Supply Current VersusFIGURE Output Duty Cycle,  $R_X = 100 \text{ k}\Omega$ ,  $C_L = 50 \text{ pF}$ ,  $C_X = 100 \text{ pF}$ , One Monostable Switching Only

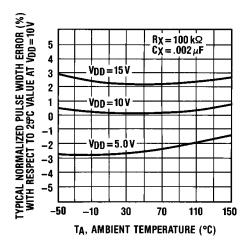

FIGURE 12. Typical Pulse Width Error Versus Temperature

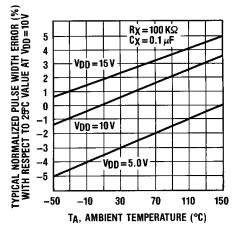

FIGURE 13. Typical Pulse Width Error Versus Temperature

FIGURE 14. Typical Pulse Width Versus Timing RC Product

# **Physical Dimensions**

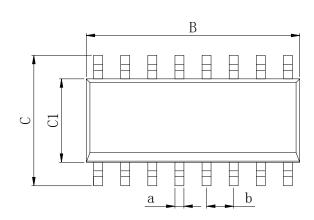

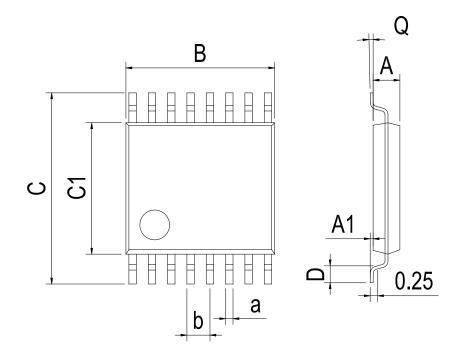

### SOP16

| Dimensions In Millimeters(SOP16) |      |      |      |      |      |      |    |      |          |  |  |

|----------------------------------|------|------|------|------|------|------|----|------|----------|--|--|

| Symbol:                          | Α    | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |  |

| Min:                             | 1.35 | 0.05 | 9.80 | 5.80 | 3.80 | 0.40 | 0° | 0.35 | 1.27 BSC |  |  |

| Max:                             | 1.55 | 0.20 | 10.0 | 6.20 | 4.00 | 0.80 | 8° | 0.45 | 1.27 BSC |  |  |

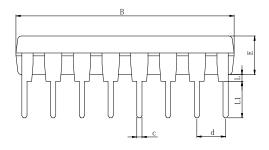

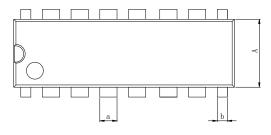

#### DIP16

| Dimensions In Millimeters(DIP16) |      |       |      |      |      |      |      |      |      |      |          |

|----------------------------------|------|-------|------|------|------|------|------|------|------|------|----------|

| Symbol:                          | Α    | В     | D    | D1   | E    | L    | L1   | а    | b    | С    | d        |

| Min:                             | 6.10 | 18.94 | 8.40 | 7.42 | 3.10 | 0.50 | 3.00 | 1.50 | 0.85 | 0.40 | 2.54 BSC |

| Max:                             | 6.68 | 19.56 | 9.00 | 7.82 | 3.55 | 0.70 | 3.60 | 1.55 | 0.90 | 0.50 | 2.04 BSC |

# **Physical Dimensions**

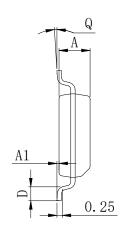

### TSSOP16

| Dimensions In Millimeters(TSSOP16) |      |      |      |      |      |      |    |      |          |  |  |

|------------------------------------|------|------|------|------|------|------|----|------|----------|--|--|

| Symbol:                            | Α    | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |  |

| Min:                               | 0.85 | 0.05 | 4.90 | 6.20 | 4.30 | 0.40 | 0° | 0.20 | 0.65 BSC |  |  |

| Max:                               | 0.95 | 0.20 | 5.10 | 6.60 | 4.50 | 0.80 | 8° | 0.25 | 0.05 BSC |  |  |

#### **IMPORTANT STATEMENT:**

Huaguan Semiconductor reserves the right to change its products and services without notice. Before ordering, the customer shall obtain the latest relevant information and verify whether the information is up to date and complete. Huaguan Semiconductor does not assume any responsibility or obligation for the altered documents.

Customers are responsible for complying with safety standards and taking safety measures when using Huaguan Semiconductor products for system design and machine manufacturing. You will bear all the following responsibilities: Select the appropriate Huaguan Semiconductor products for your application; Design, validate and test your application; Ensure that your application meets the appropriate standards and any other safety, security or other requirements. To avoid the occurrence of potential risks that may lead to personal injury or property loss.

Huaguan Semiconductor products have not been approved for applications in life support, military, aerospace and other fields, and Huaguan Semiconductor will not bear the consequences caused by the application of products in these fields. All problems, responsibilities and losses arising from the user's use beyond the applicable area of the product shall be borne by the user and have nothing to do with Huaguan Semiconductor, and the user shall not claim any compensation liability against Huaguan Semiconductor by the terms of this Agreement.

The technical and reliability data (including data sheets), design resources (including reference designs), application or other design suggestions, network tools, safety information and other resources provided for the performance of semiconductor products produced by Huaguan Semiconductor are not guaranteed to be free from defects and no warranty, express or implied, is made. The use of testing and other quality control technologies is limited to the quality assurance scope of Huaguan Semiconductor. Not all parameters of each device need to be tested.

The documentation of Huaguan Semiconductor authorizes you to use these resources only for developing the application of the product described in this document. You have no right to use any other Huaguan Semiconductor intellectual property rights or any third party intellectual property rights. It is strictly forbidden to make other copies or displays of these resources. You should fully compensate Huaguan Semiconductor and its agents for any claims, damages, costs, losses and debts caused by the use of these resources. Huaguan Semiconductor accepts no liability for any loss or damage caused by infringement.

## 单击下面可查看定价,库存,交付和生命周期等信息

>>HGSEMI (华冠)