#### **Functional Safety PMIC**

#### **Features**

- High efficient power management integrated circuit (PMIC)

- Serial step up and step down pre regulator for wide input voltage range from 3.0 to 40 V with full performance and low over all power loss

- Low drop post regulator 5.0 V/200 mA for communication supply (QCO)

- Low drop post regulator 5.0 V/600 mA (TLF35584QxVS1) or 3.3 V/600 mA (TLF35584QxVS2) for  $\mu$ C supply (QUC)

- Voltage reference 5.0 V ±1% for ADC supply, 150 mA current capability (QVR)

- Two trackers for sensor supply following voltage reference 150 mA current capability each (QT1 and QT2)

- Standby regulator 5.0 V/10 mA (TLF35584QxVS1) or 3.3 V/10 mA (TLF35584QxVS2) (QST)

- Provides enable, sync out signal and voltage monitoring for an optional external post regulator for core supply

- Independent voltage monitoring block and error pin monitoring

- Configurable window and functional watchdog

- Safe State Control with two safe state signals with programmable delay

- · 16-bit SPI, interrupt and reset function

- PRO-SIL<sup>™</sup> Features:

- ISO 26262 compliant supporting up to ASIL-D

- Safety Documentation (Safety Manual & Safety Analysis Summary Report)

- Green Product (RoHS compliant)

# O Infineon

## **Potential applications**

- Electric Power Steering

- Battery Management

- Inverter

- Transmission

- Engine Management

- Domain Control

#### **Product validation**

Qualified for Automotive Applications.

Product validation according to AEC-Q100/101.

# **Functional Safety PMIC**

#### **Description**

## **Description**

The OPTIREG<sup>™</sup> PMIC TLF35584 is a high efficient Functional Safety PMIC (Power Management Integrated Circuit).

| Туре                          | Package    |

|-------------------------------|------------|

| TLF35584QVVS1 (5.0 V Variant) | PG-VQFN-48 |

| TLF35584QVVS2 (3.3 V Variant) | PG-VQFN-48 |

| TLF35584QKVS1 (5.0 V Variant) | PG-LQFP-64 |

| TLF35584QKVS2 (3.3 V Variant) | PG-LQFP-64 |

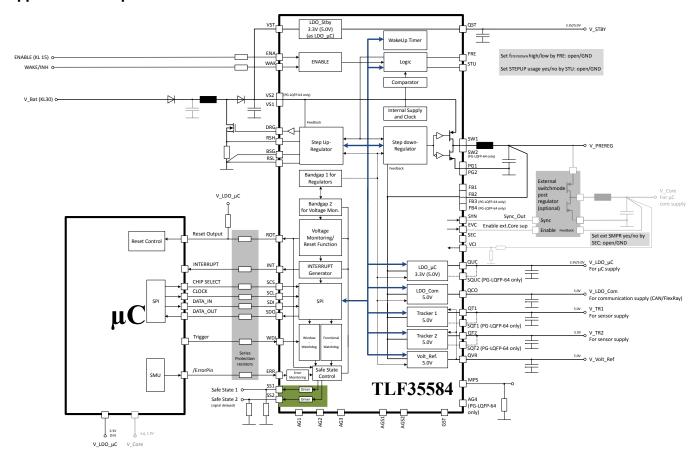

#### **Application Example**

The following information is given as an example for the implementation of the device only and shall Note: not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

- Please contact us for additional supportive documentation.

- For further information you may contact <a href="http://www.infineon.com/OPTIREG-PMIC">http://www.infineon.com/OPTIREG-PMIC</a>

This figure is a very simplyfied example on an application circuit. The function must be verified in the Note: real application.

# **Functional Safety PMIC**

#### 1 Absolute maximum ratings

#### **Absolute maximum ratings** 1

#### Absolute maximum ratings<sup>2)</sup> Table 1

$T_i = -40$ °C to 150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                 | Symbol             | Values |      |      | Unit | Note or condition |

|-------------------------------------------|--------------------|--------|------|------|------|-------------------|

|                                           |                    | Min.   | Тур. | Max. |      |                   |

| Voltages                                  |                    |        |      |      |      | 1                 |

| Boost driver ground                       | $V_{BSG}$          | -0.3   | _    | 0.3  | V    | _                 |

| Input standby LDO                         | V <sub>VST</sub>   | -0.3   | _    | 40   | V    | 3)4)              |

| Input voltage pin 1 (pre regulator)       | V <sub>VS1</sub>   | -0.3   | _    | 40   | V    | _                 |

| Input voltage pin 2 (pre regulator)       | V <sub>VS2</sub>   | -0.3   | _    | 40   | V    | PG-LQFP-64 only   |

| External step up power stage, gate        | $V_{DRG}$          | -0.3   | _    | 40   | V    | _                 |

| External power stage, sense resistor high | V <sub>RSH</sub>   | -0.3   | -    | 40   | V    | -                 |

| External power stage, sense resistor low  | V <sub>RSL</sub>   | -0.3   | -    | 6.0  | V    | -                 |

| Enable input                              | V <sub>ENA</sub>   | -0.3   | _    | 40   | V    | _                 |

| Enable input                              | I <sub>ENA</sub>   | -5     | _    | _    | mA   | 5)                |

| Wake input                                | V <sub>WAK</sub>   | -0.3   | _    | 40   | V    | _                 |

| Wake input                                | I <sub>WAK</sub>   | -5     | _    | _    | mA   | _                 |

| Reset output                              | V <sub>ROT</sub>   | -0.3   | _    | 6.0  | V    | _                 |

| SPI chip select input                     | V <sub>SCS</sub>   | -0.3   | _    | 6.0  | V    | _                 |

| SPI clock input                           | V <sub>SCL</sub>   | -0.3   | _    | 6.0  | V    | _                 |

| SPI data in (MOSI) input                  | $V_{\mathrm{SDI}}$ | -0.3   | _    | 6.0  | V    | _                 |

| SPI data out (MISO output)                | V <sub>SDO</sub>   | -0.3   | _    | 6.0  | V    | _                 |

| Interrupt output                          | V <sub>INT</sub>   | -0.3   | _    | 6.0  | V    | _                 |

| Window watchdog trigger input             | $V_{\mathrm{WDI}}$ | -0.3   | _    | 6.0  | V    | _                 |

| Error pin input                           | V <sub>ERR</sub>   | -0.3   | _    | 6.0  | V    | _                 |

| Safe state 1 output                       | V <sub>SS1</sub>   | -0.3   | _    | 6.0  | V    | _                 |

| Safe state 2 output                       | V <sub>SS2</sub>   | -0.3   | _    | 6.0  | V    | _                 |

| Output voltage reference LDO              | $V_{\rm QVR}$      | -0.3   | _    | 6.0  | V    | _                 |

| Output tracker 2                          | $V_{\rm QT2}$      | -1.0   | _    | 40   | V    | _                 |

<sup>2</sup> Not subject to production test, specified by design.

<sup>3</sup> Maximum rating is 60 V, if rise time from 0 to 60 V is longer than 10 ms

<sup>4</sup> Maximum rating is 49 V, for an overall time of 10 s (in the range of 40 V to 49 V) during the lifetime of the product independent from the rise time.

<sup>5</sup> Consider external series resistor for negative voltages < -0.3 V to ensure maximum rating of current

### **Functional Safety PMIC**

#### 1 Absolute maximum ratings

#### Absolute maximum ratings<sup>2)</sup> (continued) Table 1

$T_i = -40$ °C to 150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                               | Symbol             | Values |      |      | Unit | Note or condition |

|-----------------------------------------|--------------------|--------|------|------|------|-------------------|

|                                         |                    | Min.   | Тур. | Max. |      |                   |

| Sense Pin for tracker 2                 | $V_{SQT2}$         | -0.3   | _    | 40   | V    | PG-LQFP-64 only   |

| Output tracker 1                        | $V_{\mathrm{QT1}}$ | -1.0   | _    | 40   | V    | _                 |

| Sense Pin for tracker 1                 | $V_{SQT1}$         | -0.3   | _    | 40   | V    | PG-LQFP-64 only   |

| Output communication LDO                | $V_{\rm QCO}$      | -0.3   | _    | 6.0  | V    | _                 |

| Output microcontroller LDO              | $V_{QUC}$          | -0.3   | _    | 6.0  | V    | _                 |

| Sense Pin for microcontroller LDO       | V <sub>SQUC</sub>  | -0.3   | _    | 6.0  | V    | PG-LQFP-64 only   |

| External core voltage monitor input     | V <sub>VCI</sub>   | -0.3   | -    | 6.0  | V    | -                 |

| HW config: ext. core voltage<br>monitor | V <sub>SEC</sub>   | -0.3   | _    | 6.0  | V    | -                 |

| Synchronization output                  | $V_{SYN}$          | -0.3   | _    | 6.0  | V    | _                 |

| Enable output for ext. core supply      | V <sub>EVC</sub>   | -0.3   | _    | 6.0  | V    | _                 |

| Step down feedback input 4              | $V_{FB4}$          | -0.3   | -    | 7.0  | V    | PG-LQFP-64 only   |

| Step down feedback input 3              | $V_{FB3}$          | -0.3   | -    | 7.0  | V    | PG-LQFP-64 only   |

| Step down feedback input 2              | $V_{FB2}$          | -0.3   | _    | 7.0  | V    | _                 |

| Step down feedback input 1              | V <sub>FB1</sub>   | -0.3   | -    | 7.0  | V    | _                 |

| Step down power ground 2                | $V_{PG2}$          | -0.3   | -    | 0.3  | V    | _                 |

| Step down power ground 1                | $V_{PG1}$          | -0.3   | _    | 0.3  | V    | _                 |

| Step down switching node 2              | V <sub>SW2</sub>   | -0.3   | _    | 40   | V    | PG-LQFP-64 only   |

| Step down switching node 1              | $V_{\rm SW1}$      | -0.3   | -    | 40   | V    | _                 |

| HW config: step up pre regulator        | V <sub>STU</sub>   | -0.3   | _    | 6.0  | V    | _                 |

| HW config: step down frequency          | $V_{FRE}$          | -0.3   | _    | 6.0  | V    | _                 |

| Output standby LDO                      | $V_{\rm QST}$      | -0.3   | -    | 6.0  | V    | _                 |

| Input MPS                               | $V_{MPS}$          | -0.3   | _    | 6.0  | V    | _                 |

| Temperatures                            |                    |        |      |      |      |                   |

| Junction temperature                    | T <sub>j</sub>     | -40    | -    | 150  | °C   | -                 |

| Storage temperature                     | $T_{\rm stg}$      | -55    | -    | 150  | °C   | -                 |

| ESD susceptibility                      |                    |        |      |      |      |                   |

| ESD susceptibility to GND               | V <sub>ESD</sub>   | -2     | _    | 2    | kV   | HBM <sup>6)</sup> |

<sup>2</sup> Not subject to production test, specified by design.

<sup>6</sup> ESD susceptibility, HBM according to JEDEC HBM Human Body Model ANSI/ESDA/JEDEC JS001 (1.5  $k\Omega$ , 100 pF)

#### **Functional Safety PMIC**

Rev 1.0 2019-03-25

#### 1 Absolute maximum ratings

#### Absolute maximum ratings<sup>2)</sup> (continued) Table 1

$T_i = -40$ °C to 150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                               | Symbol                  | Values |      |      | Unit | Note or condition |

|-----------------------------------------|-------------------------|--------|------|------|------|-------------------|

|                                         |                         | Min.   | Тур. | Max. |      |                   |

| ESD susceptibility to GND               | V <sub>ESD</sub>        | -500   | _    | 500  | V    | CDM <sup>7)</sup> |

| ESD susceptibility (corner pins) to GND | V <sub>ESD,Corner</sub> | -750   | _    | 750  | V    | CDM               |

Downloaded From Oneyac.com

<sup>2</sup> Not subject to production test, specified by design.

<sup>7</sup> ESD susceptibility, Charged Device Model "CDM" ESDA STM5.3.1 or ANSI/ESD S.5.3.1

## **OPTIREG<sup>™</sup> PMIC TLF35584 Functional Safety PMIC**

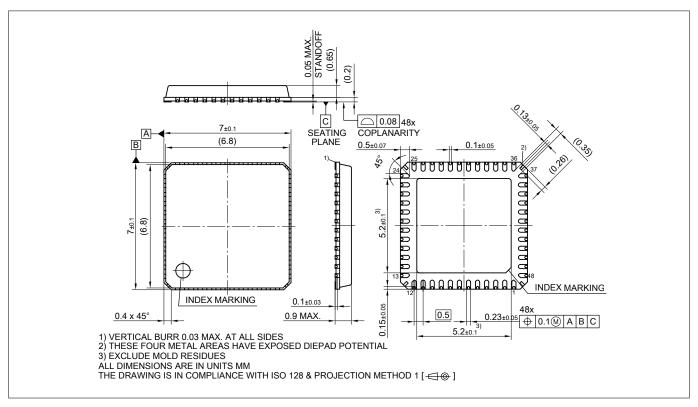

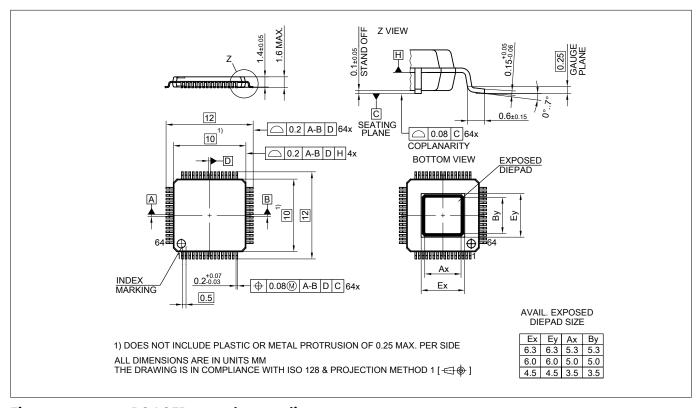

#### 2 Package information 8)

Dimensions in mm

#### Package information 8) 2

Figure 1 PG-VQFN-48 package outline

Figure 2 PG-LQFP-64 package outline

Downloaded From Oneyac.com

<sup>8</sup> Dimensions in mm

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2019-03-25 Published by Infineon Technologies AG 81726 Munich, Germany

© 2019 Infineon Technologies AG All Rights Reserved.

Do you have a question about any aspect of this document?

${\bf Email: erratum@infineon.com}$

Document reference IFX-jmv1546509847065

#### IMPORTANT NOTICE

The information contained in this application note is given as a hint for the implementation of the product only and shall in no event be regarded as a description or warranty of a certain functionality, condition or quality of the product. Before implementation of the product, the recipient of this application note must verify any function and other technical information given herein in the real application. Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind (including without limitation warranties of non-infringement of intellectual property rights of any third party) with respect to any and all information given in this application note.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury

# 单击下面可查看定价,库存,交付和生命周期等信息

# >>Infineon(英飞凌)