Interworking Element for 8 E1/T1 Lines

PXB 4219E, PXB 4220E, PXB 4221E, Version 3.4

Wired Communications

Never stop thinking.

# Revision History: 2003-01-20 DS3 Previous Version: Preliminary Data Sheet, DS2, 2002-05-06 Page Subjects (major changes since last revision)

ABM<sup>®</sup>, ACE<sup>®</sup>, AOP<sup>®</sup>, ARCOFI<sup>®</sup>, ASM<sup>®</sup>, ASP<sup>®</sup>, DigiTape<sup>®</sup>, DuSLIC<sup>®</sup>, EPIC<sup>®</sup>, ELIC<sup>®</sup>, FALC<sup>®</sup>, GEMINAX<sup>®</sup>, IDEC<sup>®</sup>, INCA<sup>®</sup>, IOM<sup>®</sup>, IPAT<sup>®</sup>-2, ISAC<sup>®</sup>, ITAC<sup>®</sup>, IWE<sup>®</sup>, IWORX<sup>®</sup>, MUSAC<sup>®</sup>, MuSLIC<sup>®</sup>, OCTAT<sup>®</sup>, OptiPort<sup>®</sup>, POTSWIRE<sup>®</sup>, QUAT<sup>®</sup>, QuadFALC<sup>®</sup>, SCOUT<sup>®</sup>, SICAT<sup>®</sup>, SICOFI<sup>®</sup>, SIDEC<sup>®</sup>, SLICOFI<sup>®</sup>, SMINT<sup>®</sup>, SOCRATES<sup>®</sup>, VINETIC<sup>®</sup>, 10BaseV<sup>®</sup>, 10BaseVX<sup>®</sup> are registered trademarks of Infineon Technologies AG. 10BaseS<sup>™</sup>, EasyPort<sup>™</sup>, VDSLite<sup>™</sup> are trademarks of Infineon Technologies AG. Microsoft<sup>®</sup> is a registered trademark of Microsoft Corporation. Linux<sup>®</sup> is a registered trademark of Linux Torvalds.

The information in this document is subject to change without notice.

#### Edition 2003-01-20

Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany

© Infineon Technologies AG 2003.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| Table of                                                                                                   | Contents                                                                                                                                                                                                                                                                              | Page                                                           |

|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 1<br>1.1<br>1.2<br>1.3<br>1.3.1<br>1.3.2<br>1.4<br>1.5                                                     | Overview Features Logic Symbol Typical Applications Line Card Echo Canceller Differences Between PXB4220 And PXB4219 Differences Between PXB4220 And PXB4221                                                                                                                          | 15<br>17<br>18<br>19<br>19                                     |

| 2<br>2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6<br>2.2.7<br>2.2.8<br>2.2.9<br>2.2.10 | Pin Descriptions Pin Diagram Pin Definitions and Functions Generic Framer Interface UTOPIA Interface IMA Interface Clock Recovery Interface Microprocessor Interface External RAM Interface Test Interface Miscellaneous Power Supply Not Connected Pins                              | 22<br>23<br>23<br>25<br>27<br>27<br>28<br>28<br>30<br>31<br>32 |

| 3<br>3.1<br>3.1.1<br>3.1.2<br>3.1.2.1<br>3.1.2.2<br>3.2<br>3.3                                             | Functional Description Operating Modes ATM Mode AAL Mode Unstructured CES Mode Structured CES Mode Functional Block Diagram Functional Block Description                                                                                                                              | 35<br>35<br>35<br>36<br>37                                     |

| 4.1<br>4.1.1<br>4.1.1.1<br>4.1.1.2<br>4.1.1.3<br>4.1.1.4<br>4.1.1.5<br>4.1.2<br>4.2.1<br>4.2.1             | Operational Description  ATM Transmit Functions Operation ATM Transmit Buffer Filling Level Cell Discarding Cell rate de-coupling: Idle/Unassigned Cell Insertion Cell Payload Scrambling HEC Generation Setup of ATM Transmit Ports ATM Receive Functions Operation Cell Delineation | 42 42 43 43 44 44 45 46                                        |

| Table of | Contents                                             | Page |

|----------|------------------------------------------------------|------|

| 4.2.1.2  | HEC Check: Header Error Detection and Correction     | 48   |

| 4.2.1.3  | Cell Payload Descrambling                            | 49   |

| 4.2.1.4  | Idle, Physical Layer or Unassigned Cell Deletion     | 49   |

| 4.2.2    | Setup of ATM Receive Ports                           | 51   |

| 4.3      | AAL Segmentation Functions                           | 52   |

| 4.3.1    | Operation                                            | 52   |

| 4.3.1.1  | Segmentation Port Decorrelation                      |      |

| 4.3.1.2  | Segmentation                                         | 53   |

| 4.3.1.3  | Transport of the Framer Port Number                  | 53   |

| 4.3.1.4  | Transport of CAS Information                         | 54   |

| 4.3.1.5  | CAS Conditioning and Freezing Upstream               | 54   |

| 4.3.1.6  | Segmentation Buffer                                  | 55   |

| 4.3.1.7  | Padding Partially Filled Cells                       | 55   |

| 4.3.2    | Setup of AAL Segmentation Channels                   | 56   |

| 4.4      | AAL Reassembly Functions                             | 58   |

| 4.4.1    | Operation                                            | 58   |

| 4.4.1.1  | Port and Channel Identification                      | 58   |

| 4.4.1.2  | Sequence Number Protection field check               | 58   |

| 4.4.1.3  | Sequence Number field check                          | 59   |

| 4.4.1.4  | RTS Extraction and Verification                      | 59   |

| 4.4.1.5  | Pointer Field Detection and Verification             | 59   |

| 4.4.1.6  | CAS Conditioning and Freezing Downstream             | 60   |

| 4.4.1.7  | Insertion of Dummy Cells at Cell Loss                | 60   |

| 4.4.1.8  | Reassembly Buffer                                    | 60   |

| 4.4.1.9  | Handling of Reassembly Buffer Overflow               | 61   |

| 4.4.1.10 | Handling of Reassembly Buffer Underflow              | 61   |

| 4.4.1.11 | Synchronization of SDT Structure with Port Structure | 62   |

| 4.4.2    | Setup                                                | 62   |

| 4.4.2.1  | Setup of Reassembly Channels                         | 62   |

| 4.4.2.2  | Physical Reassembly Buffer Size                      | 63   |

| 4.4.2.3  | Initialization of the Reassembly Buffer              |      |

| 4.4.2.4  | Re-Initialization of the Reassembly Buffer           | 69   |

| 4.5      | Internal Clock Recovery Circuit (ICRC)               | 70   |

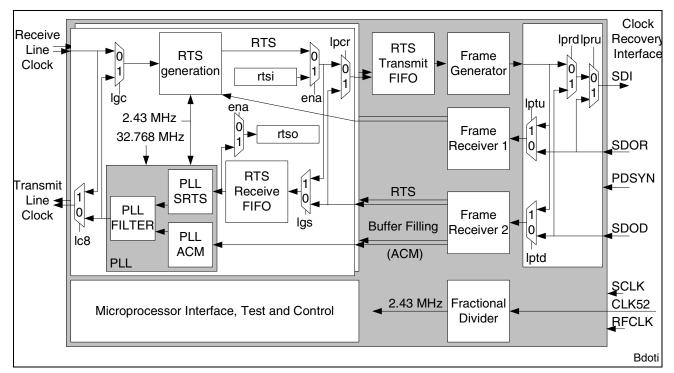

| 4.5.1    | Data Flow                                            | 71   |

| 4.5.2    | Frame Generator                                      |      |

| 4.5.3    | Frame Receiver                                       | 72   |

| 4.5.4    | RTS Receive FIFO                                     |      |

| 4.5.5    | RTS Transmit FIFO                                    |      |

| 4.5.6    | ICRC Loopback Modes                                  |      |

| 4.5.7    | RTS Injection                                        |      |

| 4.5.8    | Fractional Divider                                   |      |

| 4.5.9    | Clocks                                               | 74   |

| Table of | Contents                                 | Page  |

|----------|------------------------------------------|-------|

| 4.5.10   | Power Management                         | 74    |

| 4.5.11   | PLL Block                                | 74    |

| 4.5.11.1 | PLL-SRTS:                                | 74    |

| 4.5.11.2 | PLL-FILTER                               | 75    |

| 4.5.11.3 | PLL-ACM                                  | 75    |

| 4.5.11.4 | SRTS with ACM:                           | 78    |

| 4.6      | Internal Queues                          | 79    |

| 4.6.1    | Event Queue                              | 79    |

| 4.6.2    | Output Queue                             | 79    |

| 4.6.3    | Interrupt Queue                          | 79    |

| 4.7      | OAM Processing                           | 80    |

| 4.8      | Loopback Modes                           | 81    |

| 4.8.1    | Upstream Loop                            | 81    |

| 4.8.2    | Downstream Loop                          | 81    |

| 4.8.3    | Serial Loop                              | 82    |

| 4.9      | Cell Insertion                           | 83    |

| 4.10     | Cell Extraction                          | 84    |

| 4.11     | Mapping of Channels to Timeslots         | 85    |

| 4.11.1   | ATM Mode                                 | 85    |

| 4.11.2   | AAL Mode                                 | 86    |

| 4.11.2.1 | Unstructured CES                         | 86    |

| 4.11.2.2 | Structured CES                           | 87    |

| 4.11.2.3 | Structured CES with CAS                  | 88    |

| 5        | Interface Description                    | 91    |

| 5.1      | Generic Framer Interface                 |       |

| 5.1.1    | FALC Mode (FAM)                          | 91    |

| 5.1.1.1  | T1 FALC Mode                             |       |

| 5.1.1.2  | E1 FALC Mode                             | 95    |

| 5.1.2    | Generic Interface Mode (GIM)             | 95    |

| 5.1.2.1  | T1 Mode                                  | 95    |

| 5.1.2.2  | E1 Mode                                  | 98    |

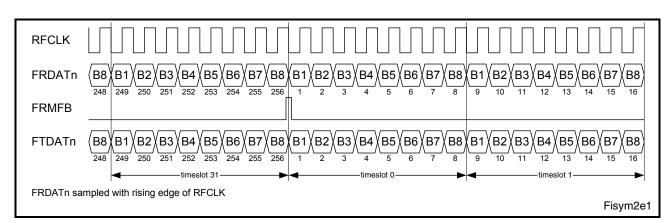

| 5.1.3    | Synchronous Modes (SYM)                  | . 100 |

| 5.1.3.1  | Synchronous Mode at 2.048 MHz (SYM2)     | . 100 |

| 5.1.3.2  | Synchronous Mode at 8.192 MHz (SYM8)     | . 102 |

| 5.1.4    | Echo Canceller Mode (EC)                 | . 103 |

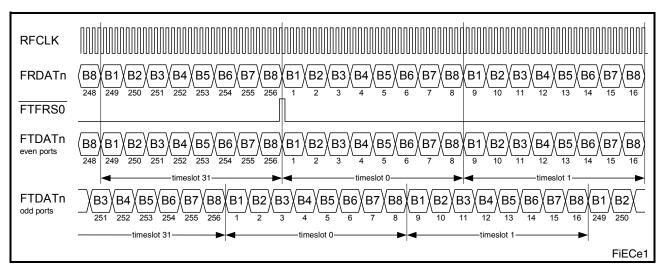

| 5.2      | UTOPIA Interface                         | . 105 |

| 5.2.1    | Port Addresses                           | . 105 |

| 5.2.2    | Back Pressure/ATM Cell Discarding        | . 106 |

| 5.2.2.1  | General Backpressure Mechanism           | . 106 |

| 5.2.2.2  | Port Specific Backpressure Mechanism     | . 107 |

| 5.2.3    | Sideband Signals of the UTOPIA Interface | . 107 |

| 5.3      | IMA Interface                            | . 109 |

| Table of                                                                          | Contents                                                                                                                                                                                                                                                                                                                          | Page                                               |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 5.4<br>5.5<br>5.5.1<br>5.5.2<br>5.6<br>5.7<br>5.8                                 | Clock Recovery Interface Microprocessor Interface Interrupt Handling Microprocessor Interface Mode External RAM Interface Boundary Scan Interface Master Clock                                                                                                                                                                    | . 112<br>. 112<br>. 113<br>. 115                   |

| 6<br>6.1<br>6.1.1<br>6.1.1.1<br>6.1.1.2<br>6.1.1.3<br>6.1.1.4<br>6.1.1.5<br>6.1.2 | Memory Structure Internal Configuration RAM's RAM1: Receive Port Configuration RAM1: ATM Receive Reference Slot RAM1: ATM Receive Continuation Slot RAM1: AAL Receive Reference Slot RAM1: AAL Receive Continuation Slot RAM1: AAL Receive Continuation Slot RAM1: ATM or AAL Receive Idle Slot RAM2: Transmit Port Configuration | . 120<br>. 121<br>. 121<br>. 122<br>. 123<br>. 126 |

| 6.1.2.1<br>6.1.2.2<br>6.1.2.3<br>6.1.2.4<br>6.1.2.5                               | RAM2: ATM Transmit Reference Slot RAM2: ATM Transmit Continuation Slot RAM2: AAL Transmit Reference Slot RAM2: AAL Transmit Continuation Slot RAM2: ATM or AAL Transmit Idle Slot                                                                                                                                                 | . 127<br>. 128<br>. 129<br>. 132<br>. 133          |

| 6.1.3<br>6.1.3.1<br>6.1.4<br>6.1.4.1<br>6.2                                       | RAM3: Transmit Port Configuration Extended                                                                                                                                                                                                                                                                                        | . 134<br>. 135<br>. 136<br>. 137                   |

| 6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6                                | Statistics Counters Statistics Counter thresholds Interrupt Queue Timers Cell Insertion Buffer Cell Extraction Buffer                                                                                                                                                                                                             | . 140<br>. 141<br>. 142<br>. 143                   |

| 6.2.7<br>6.2.7.1<br>6.2.7.2<br>6.2.8                                              | Segmentation/ATM Receive Buffers                                                                                                                                                                                                                                                                                                  | . 146<br>. 146<br>. 146                            |

| <b>7</b><br>7.1<br>7.2<br>7.3<br>7.4                                              | Register Description  Port Configuration Registers (pcfN)  ASIC Configuration Register (acfg)  OAM Control Register (oamc)  OAM-Counter Enable Register for ATM Ports (catm)                                                                                                                                                      | . 151<br>. 154<br>. 156                            |

| Table o | of Contents                                                       | Page |

|---------|-------------------------------------------------------------------|------|

| 7.5     | OAM-Counter Enable Register for AAL Ports (caal)                  | 158  |

| 7.6     | Byte-Pattern Register bp3 and bp2 (bp32)                          |      |

| 7.7     | Byte-Pattern Register bp1 and bp0 (bp10)                          |      |

| 7.8     | ATM Control Register (atmc)                                       |      |

| 7.9     | RX Idle/Unassigned Cell Control Register (rxid)                   |      |

| 7.10    | TX Idle/Unassigned Cell Control Register (txid)                   |      |

| 7.11    | Loopback Control Register (lpbc)                                  |      |

| 7.12    | Cell Fill Register for Partially Filled Cells (cfil)              |      |

| 7.13    | Interrupt Mask Register 1 (imr1)                                  |      |

| 7.14    | Timer Enable Register (time)                                      |      |

| 7.15    | Cell Delineation FSM Status Register (cdfs)                       | 168  |

| 7.16    | Version Register (vers)                                           | 169  |

| 7.17    | Clock Monitor Register (ckmo)                                     | 170  |

| 7.18    | Interrupt Status Register 1 (isr1)                                | 171  |

| 7.19    | Extended Interrupt Status 1 Register (eis1)                       | 173  |

| 7.20    | Extended Interrupt Status 2 Register (eis2)                       | 174  |

| 7.21    | Extended Interrupt Status 3 Register (eis3)                       | 175  |

| 7.22    | Extended Interrupt Status 4 Register (eis4)                       |      |

| 7.23    | Interrupt Status Register 2 (isr2)                                |      |

| 7.24    | Operation Mode Register (opmo)                                    |      |

| 7.25    | FT Clock Select Register (ftcs)                                   |      |

| 7.26    | Cell Filter VCI Pattern 1 Register (cfvp1)                        |      |

| 7.27    | Cell Filter VCI Mask 1 Register (cfvm1)                           |      |

| 7.28    | Cell Filter VCI Pattern 2 Register (cfvp2)                        |      |

| 7.29    | Cell Filter VCI Mask 2 Register (cfvm2)                           |      |

| 7.30    | Cell Filter Payload Type Register (cfpt)                          |      |

| 7.31    | Command Register (cmd)                                            |      |

| 7.32    | Cell Filter Read Pointer Register (cfrp)                          |      |

| 7.33    | Threshold Register (thrshld)                                      |      |

| 7.34    | UTOPIA Configuration Register (utconf)                            |      |

| 7.35    | CAS 1 Register (cas1)                                             |      |

| 7.36    | CAS 2 Register (cas2)                                             |      |

| 7.37    | CAS 3 Register (cas3)                                             |      |

| 7.38    | Threshold Register for Ports 0 and 1 (thrsp01)                    |      |

| 7.39    | Threshold Register for Ports 2 and 3 (thrsp23)                    |      |

| 7.40    | Threshold Register for Ports 4 and 5 (thrsp45)                    |      |

| 7.41    | Threshold Register for Ports 6 and 7 (thrsp67)                    |      |

| 7.42    | Extended Interrupt Status 0 Register (eis0)                       |      |

| 7.43    | LCD Timer Register (Icdtimer)                                     |      |

| 7.44    | Interrupt Source Register (irs)                                   |      |

| 7.45    | Interrupt Mask (irm)                                              |      |

| 7.46    | Internal Clock Recovery Circuit Configuration Register (icrcconf) | 202  |

| Table of                                                                                                                                                     | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.47<br>7.48<br>7.49<br>7.50<br>7.51<br>7.52<br>7.53<br>7.54<br>7.55<br>7.56<br>7.57<br>7.58<br>7.59<br>7.60<br>7.61<br>7.62<br>7.63<br>7.64<br>7.65<br>7.66 | Configuration Register Downstream of Port N (condN) Interrupt Source of Port N (irsN) Interrupt Mask of Port N (irmN) Test Input of Port N (tsinN) Configuration Register Upstream Direction of Port N (conuN) Average Buffer Filling of Port N (avbN) ACM Shift Factor of Port N (asfN) Time of Initial Free Run of Port N (tiniN) Threshold Out of Lock Detection of Port N (tresh) ICRC Parity Errors at Clock Recovery Interface (per) ICRC Synchronization Errors at Clock Recovery Interface (scri) ICRC Clock Recovery Interface FIFO Overflow (crifo) ICRC Version Register (icrcv) SRTS Receive FIFO Underflow of Port N (sruN) SRTS Receive FIFO Overflow of Port N (sroN) SRTS Generator Reset of Port N (srrN) SRTS Invalid Value Processed of Port N (sriN) ACM Data Too Late of Port N (atlN) Out Of Lock Register of Port N (statN) | . 206<br>. 207<br>. 208<br>. 209<br>. 210<br>. 211<br>. 212<br>. 213<br>. 214<br>. 215<br>. 216<br>. 217<br>. 218<br>. 219<br>. 220<br>. 221<br>. 223 |

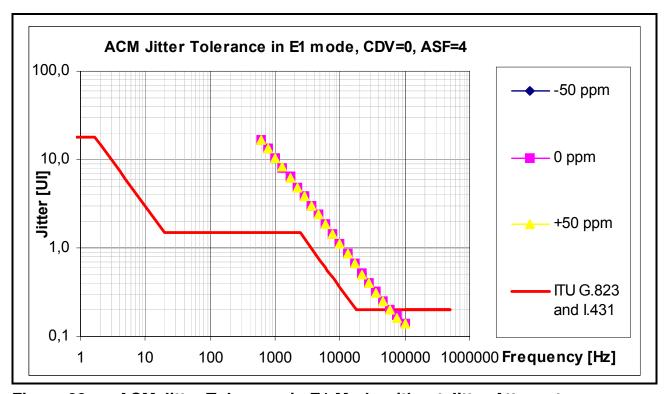

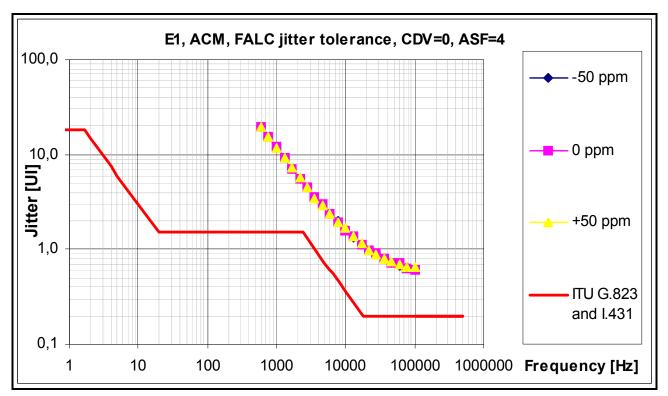

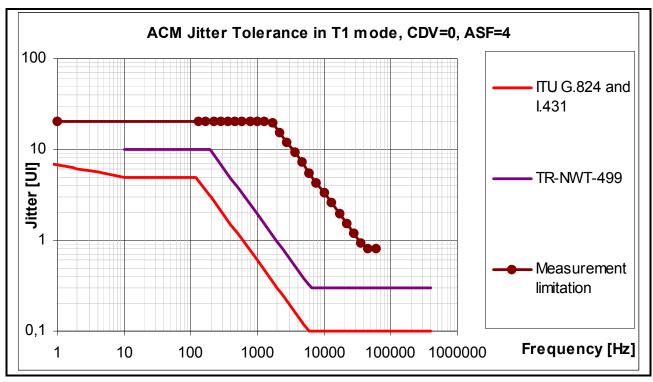

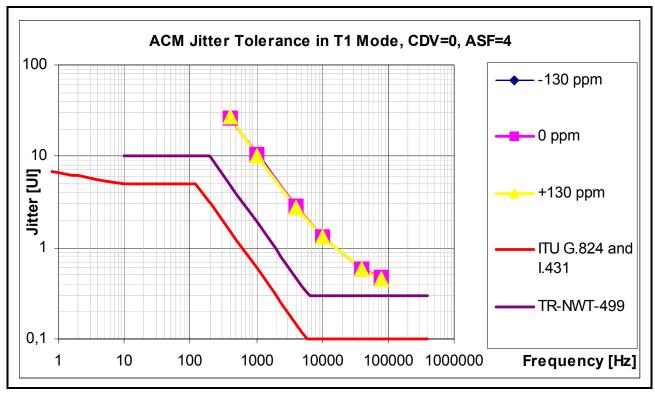

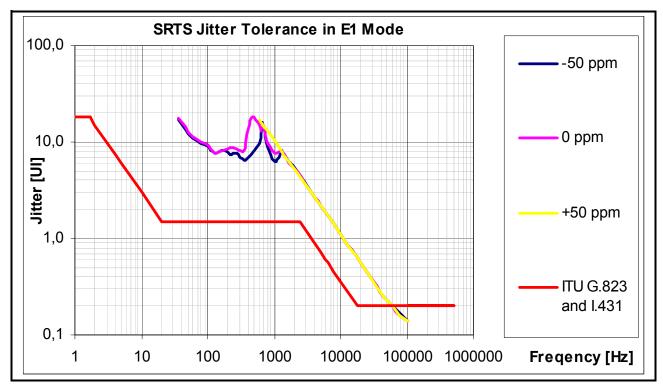

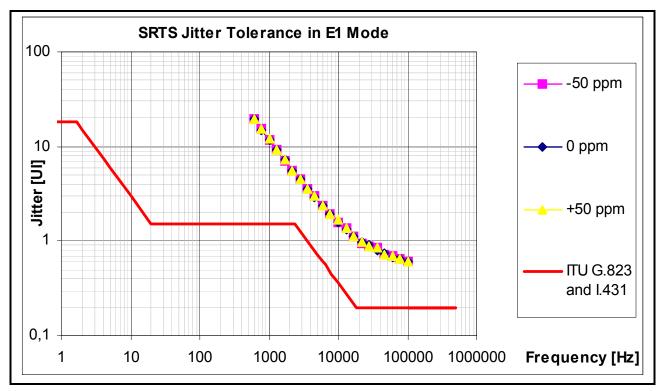

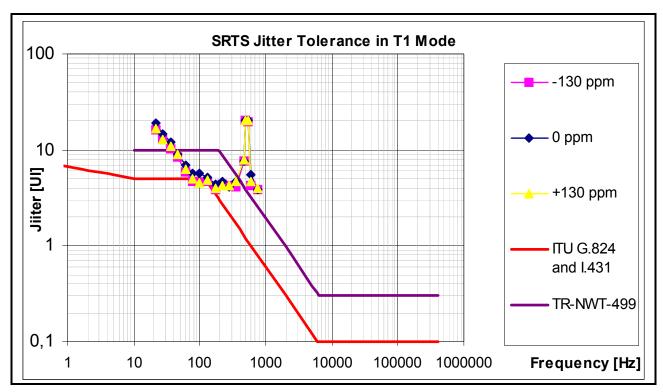

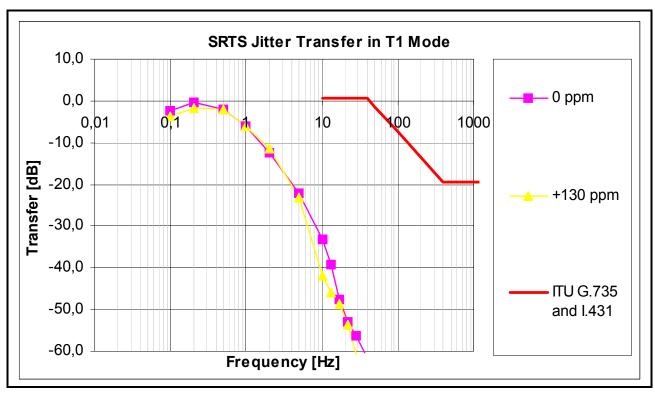

| 7.67  8 8.1 8.2 8.3 8.3.1 8.3.2 8.3.3 8.3.4 8.3.5 8.3.6 8.3.7 8.3.8                                                                                          | Application Hints Clock Concept Translating AAL Statistics Counters into the ATMF CES Version 2 MIB Jitter Characteristics of the Internal Clock Recovery Circuit ACM Jitter Tolerance in E1 Mode ACM Jitter Tolerance in E1 Mode SRTS Jitter Tolerance in E1 Mode SRTS Jitter Tolerance in T1 Mode ACM Jitter Transfer in E1 Mode ACM Jitter Transfer in E1 Mode SRTS Jitter Transfer in E1 Mode                                                                                                                                                                                                                                                                                                                                                  | . 226<br>. 228<br>. 230<br>. 231<br>. 233<br>. 234<br>. 236<br>. 237                                                                                  |

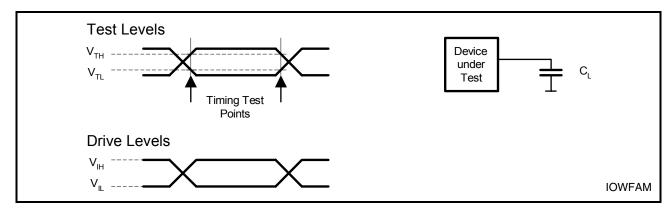

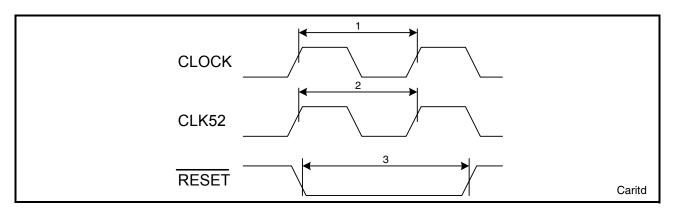

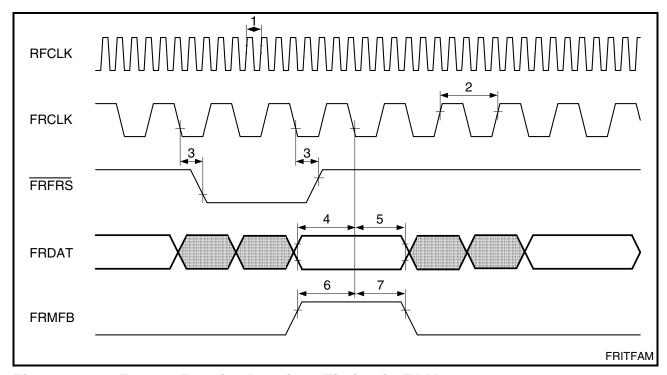

| 9<br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.6.1                                                                                                         | Electrical Characteristics Absolute Maximum Ratings Operating Range Thermal Package Characteristics DC Characteristics Capacitances AC Characteristics Clock and Reset Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 242<br>. 242<br>. 243<br>. 244<br>. 245<br>. 246                                                                                                    |

| Table of Contents                                                   |                                                                                                                                                          | Page                                                                            |  |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|

| 9.6.2<br>9.6.2.1<br>9.6.2.2<br>9.6.2.3<br>9.6.2.4<br>9.6.3<br>9.6.4 | Framer Interface Framer Interface in FAM Framer Interface in GIM Framer Interface in SYM Mode Framer Interface in EC Mode UTOPIA Interface IMA Interface | . 248<br>. 248<br>. 251<br>. 254<br>. 256<br>. 256                              |  |

| 9.6.5<br>9.6.6<br>9.6.6.1<br>9.6.6.2<br>9.6.7<br>9.6.8              | Clock Recovery Interface  Microprocessor Interface  Intel Mode  Motorola Mode  RAM Interface  Boundary-Scan Test Interface                               | <ul><li>. 262</li><li>. 262</li><li>. 264</li><li>. 265</li></ul>               |  |

| 10<br>10.1<br>10.2<br>10.3                                          | Testmode  Device Identification Register  Instruction Register  Boundary-Scan Register                                                                   | <ul><li>. 268</li><li>. 268</li></ul>                                           |  |

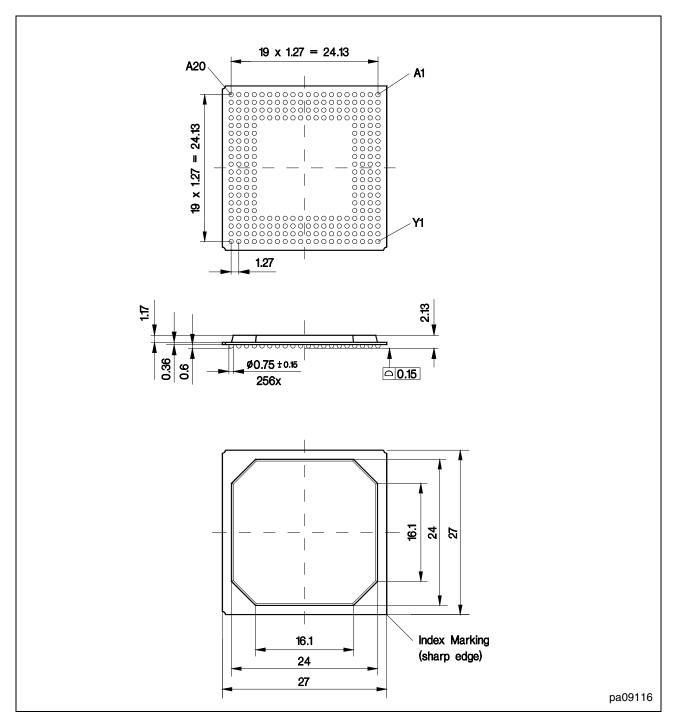

| 11                                                                  | Package Outlines                                                                                                                                         | . 273                                                                           |  |

| 12<br>12.1<br>12.2<br>12.3<br>12.4<br>12.4.1<br>12.4.2              | Appendix ATM Adaptation Layer 1 Synchronous Residual Time Stamp SRTS Adaptive Clock Method ACM Channel Associated Signalling E1 DS1                      | <ul><li>. 274</li><li>. 278</li><li>. 280</li><li>. 281</li><li>. 281</li></ul> |  |

| 13                                                                  | Contacts for SRTS Patent Fee                                                                                                                             | . 284                                                                           |  |

| 14                                                                  | Glossary                                                                                                                                                 | . 285                                                                           |  |

| 15                                                                  | Bibliography                                                                                                                                             | . 288                                                                           |  |

| List of Figu | ures                                                                  | Page  |

|--------------|-----------------------------------------------------------------------|-------|

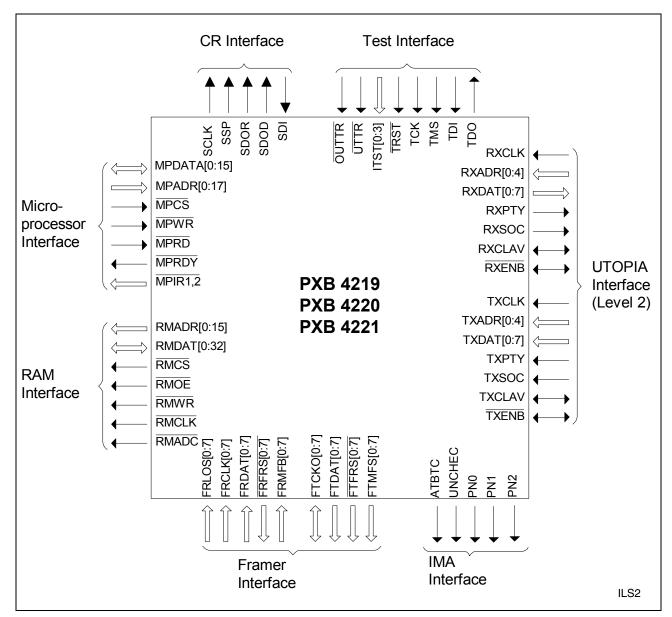

| Figure 1     | Logic Symbol                                                          | 17    |

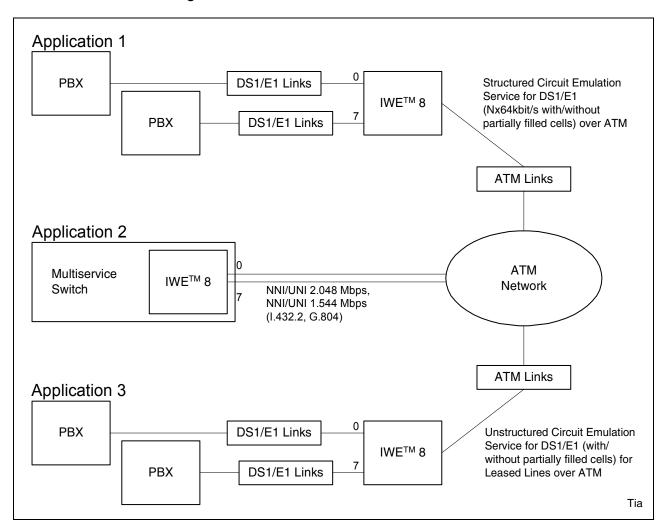

| Figure 2     | Typical IWE8 Applications                                             |       |

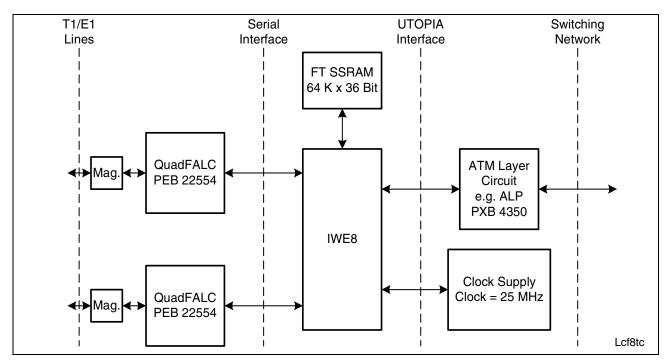

| Figure 3     | Line Card for 8 T1/E1 Channels                                        |       |

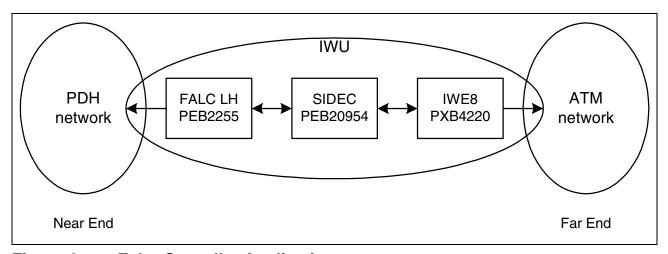

| Figure 4     | Echo Canceller Application                                            |       |

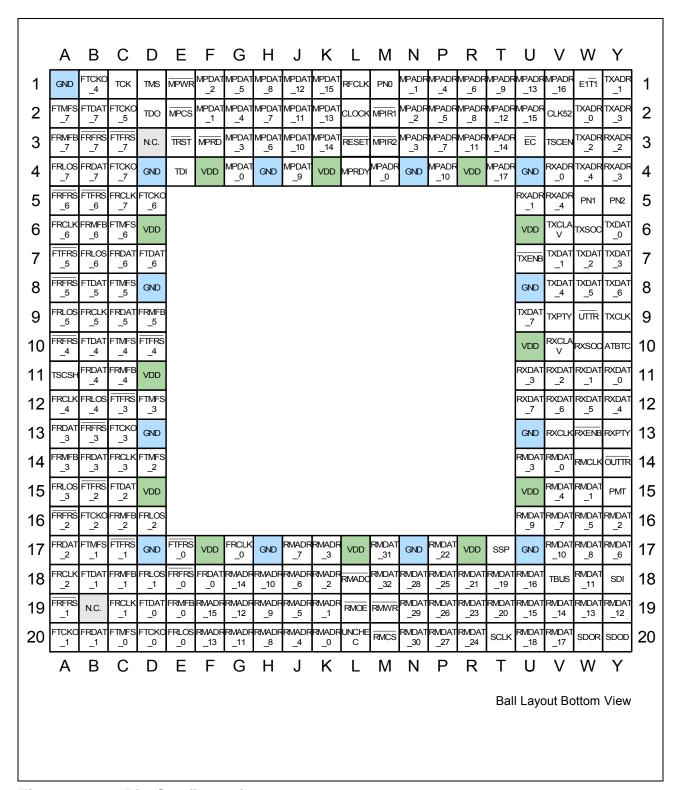

| Figure 5     | Pin Configuration                                                     | 22    |

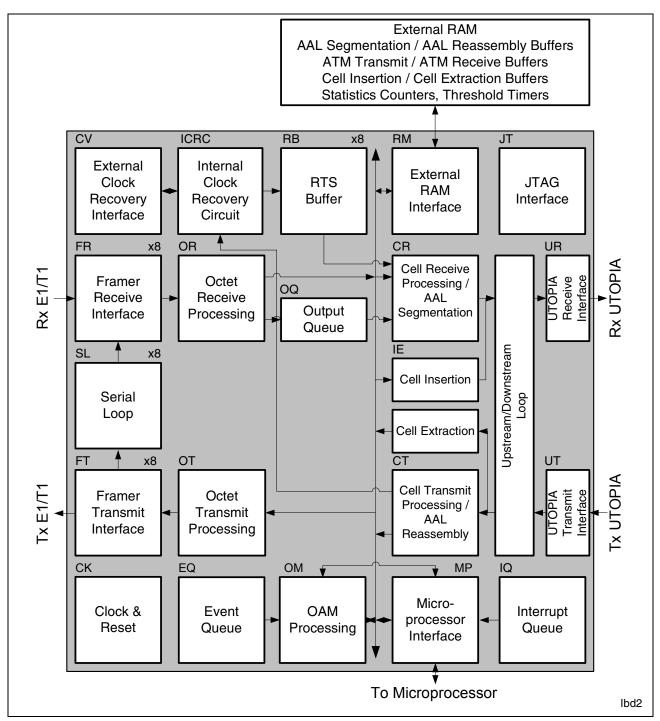

| Figure 6     | Block Diagram                                                         |       |

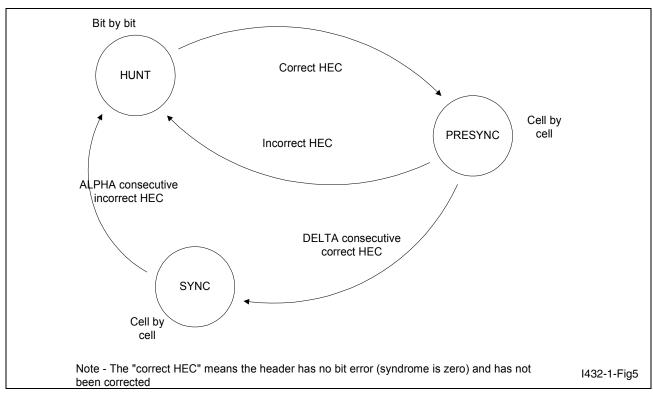

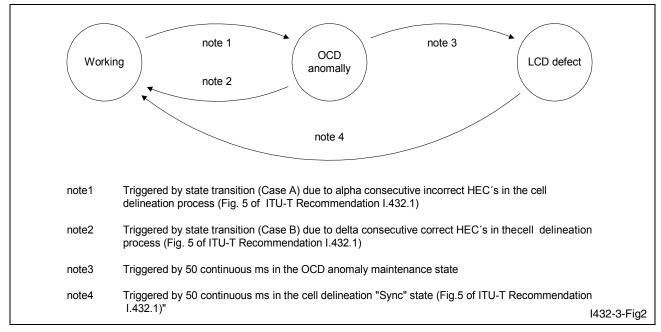

| Figure 7     | Cell delineation state diagram (Figure 5/I.432.1)                     | 47    |

| Figure 8     | Maintenance state transitions for cell delineation (Figure 2/ I.432.3 | ) 47  |

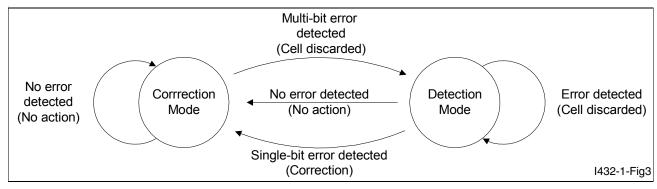

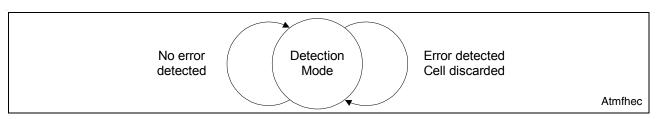

| Figure 9     | HEC: Receiver mode of Operation (Figure 3/ITU I.432.1)                | 48    |

| Figure 10    | HEC Detection According to ATM Forum                                  | 49    |

| Figure 11    | Pre-assigned cell header values at the UNI (Table 1/I.361)            | 50    |

| Figure 12    | Pre-defined header field values [11]                                  |       |

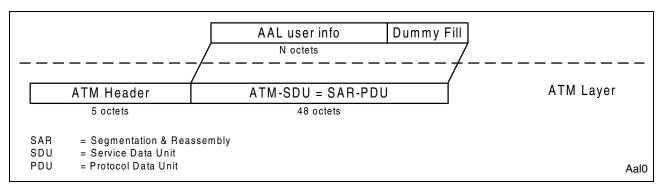

| Figure 13    | SAR-PDU of AAL Type 0                                                 | 53    |

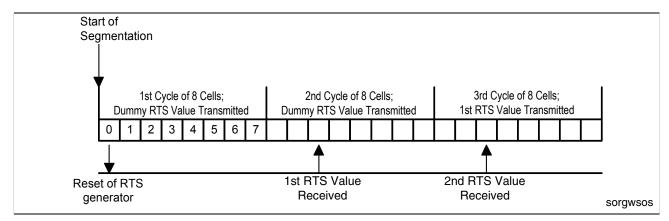

| Figure 14    | Synchronization of SRTS Generation with the Start of Segmentation     |       |

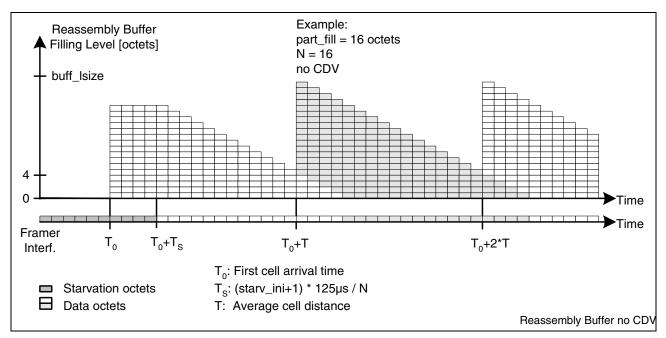

| Figure 15    | Reassembly Buffer Initialization: No CDV                              | 64    |

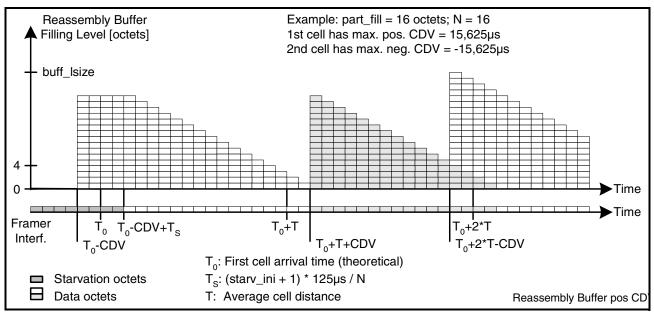

| Figure 16    | Reassembly Buffer Initialization: positive CDV at Start Up            | 65    |

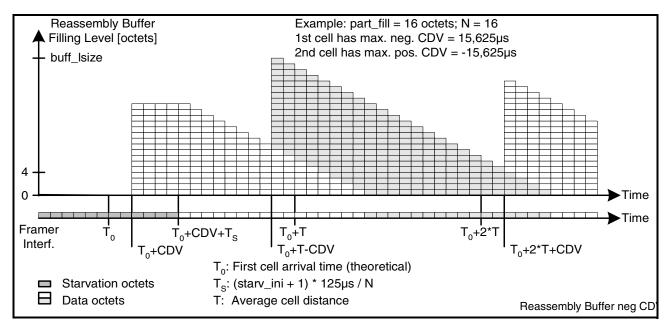

| Figure 17    | Reassembly Buffer Initialization: Negative CDV at Start Up            | 66    |

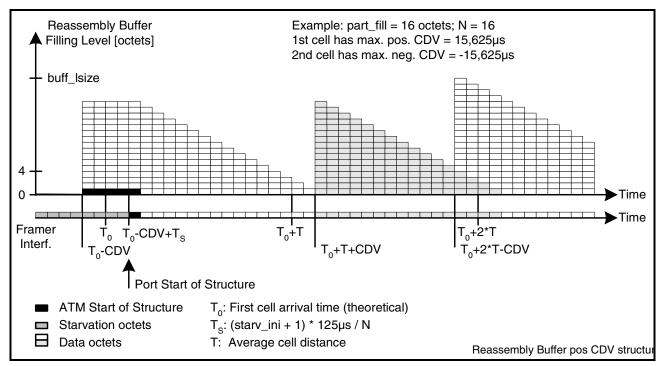

| Figure 18    | Reassembly Buffer Initialization for SDT: positive CDV at Start Up.   | 67    |

| Figure 19    | Block Diagram of the ICRC                                             | 71    |

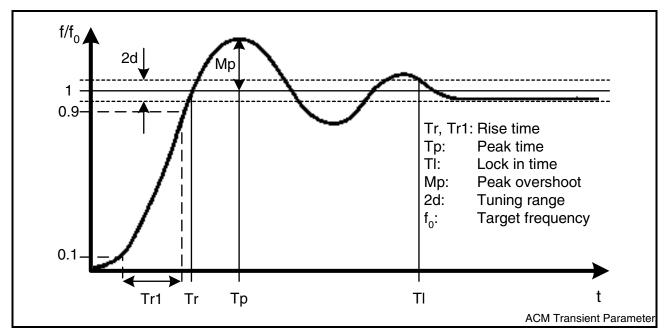

| Figure 20    | Transient Parameters                                                  |       |

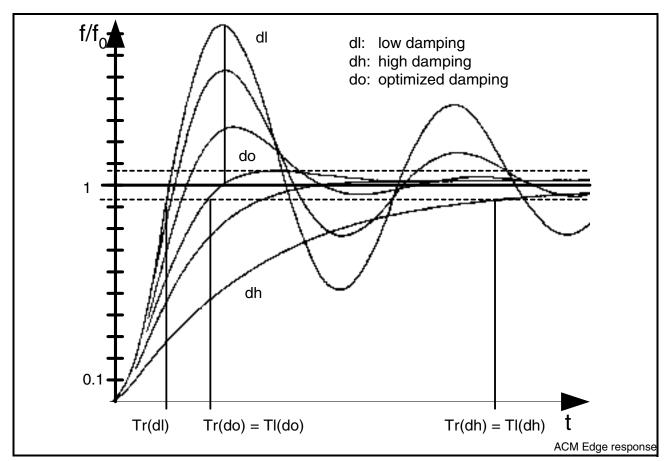

| Figure 21    | Influence of Damping on Lock in Time                                  |       |

| Figure 22    | Connection of IWE8 to QuadFALC                                        |       |

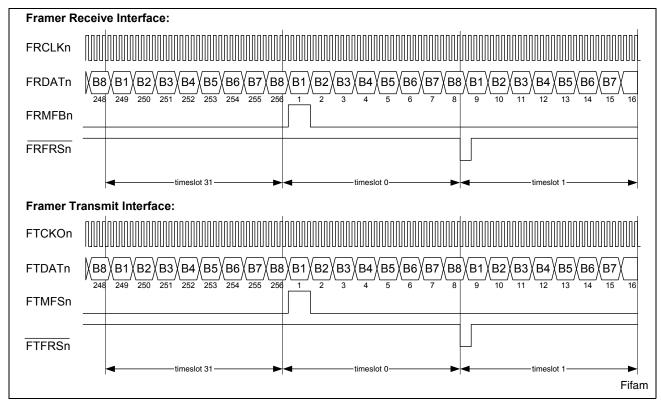

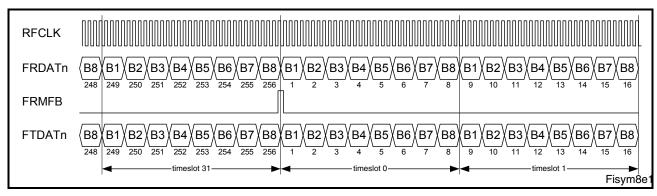

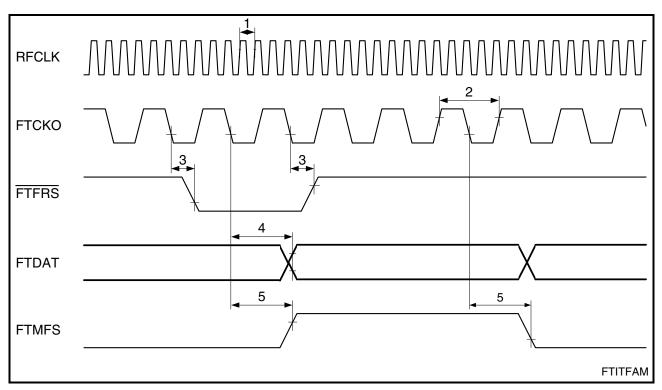

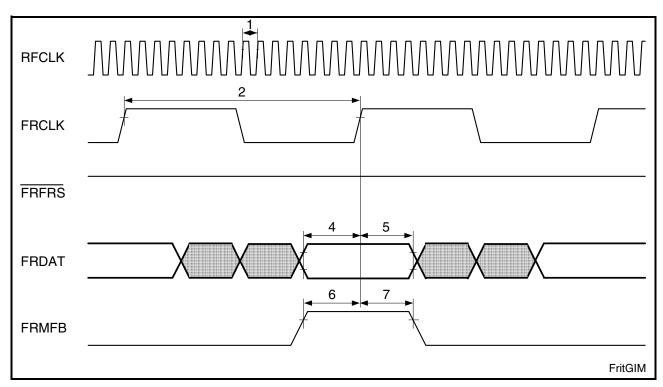

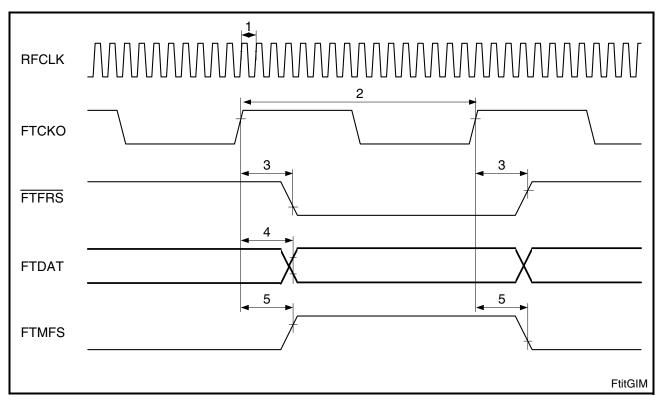

| Figure 23    | Framer Interface in FAM                                               |       |

| Figure 24    | Framer Interface in GIM T1                                            |       |

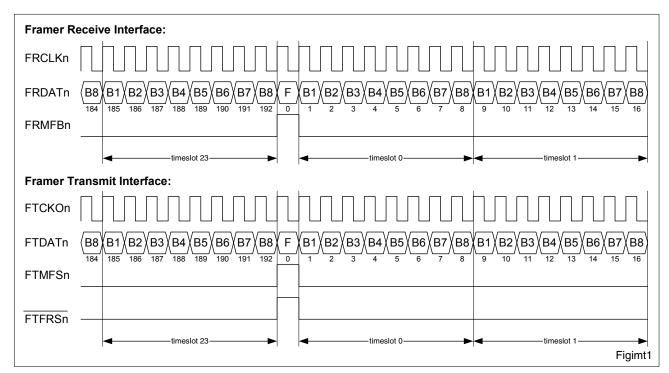

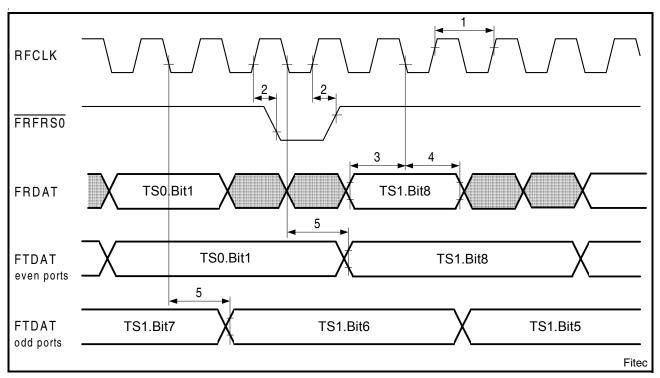

| Figure 25    | Framer Interface in GIM E1                                            |       |

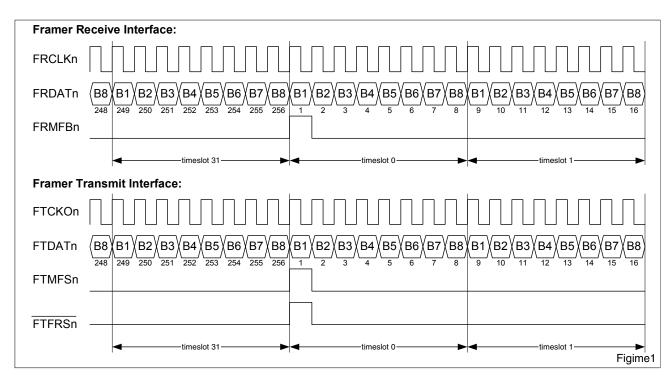

| Figure 26    | Framer Interface in SYM2 E1                                           |       |

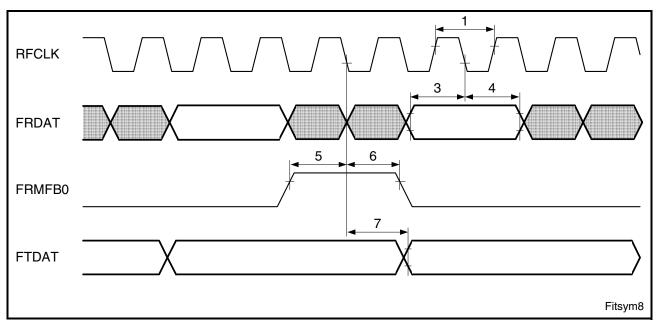

| Figure 27    | Framer Interface in SYM8 E1                                           |       |

| Figure 28    | Framer Interface in EC Mode                                           |       |

| Figure 29    | UTOPIA Receive and Transmit Interfaces in Slave Mode                  |       |

| Figure 30    | Utopia Sideband Signals                                               |       |

| Figure 31    | IMA Interface Protocol                                                |       |

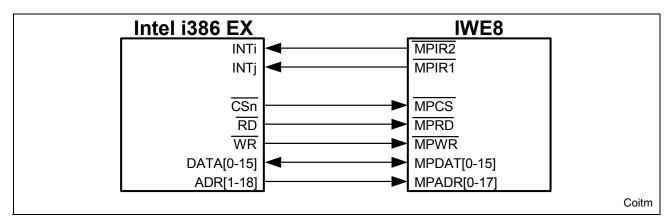

| Figure 32    | Connection of IWE8 to an Intel Type Microprocessor                    |       |

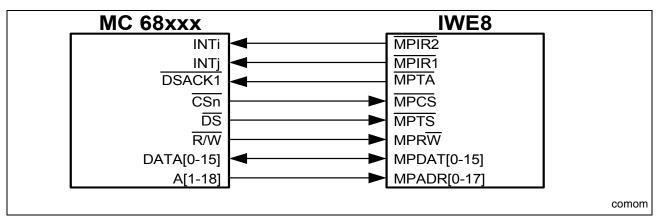

| Figure 33    | Connection of IWE8 to an Motorola Type Microprocessor                 |       |

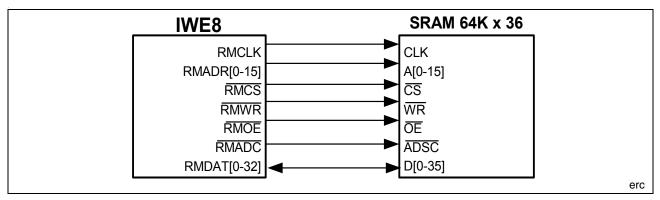

| Figure 34    | External RAM Connection                                               |       |

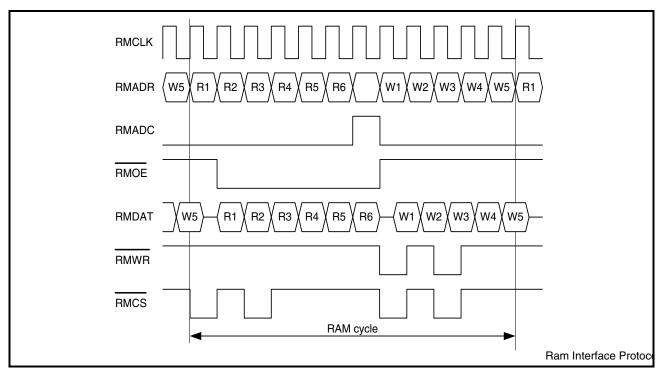

| Figure 35    | RAM Interface Protocol                                                |       |

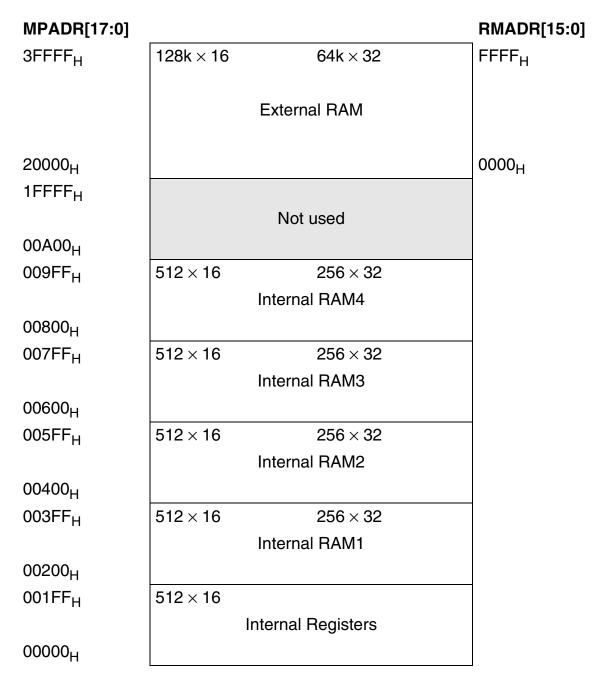

| Figure 36    | Memory Model                                                          |       |

| Figure 37    | Structure of the IWE8 external RAM                                    |       |

| Figure 38    | Clock Concept                                                         |       |

| Figure 39    | ACM litter Tolerance in E1 Mode without Jitter Attenuator             |       |

| Figure 40    | ACM litter Tolerance in E1 Mode with Jitter Attenuator                |       |

| Figure 41    | ACM litter Tolerance in T1 Mode without Jitter Attenuator             |       |

| Figure 42    | ACM Jitter Tolerance in T1 Mode with Jitter Attenuator                | . 232 |

| List of Figu | ires F                                                               | age |

|--------------|----------------------------------------------------------------------|-----|

| Figure 43    | SRTS Jitter Tolerance in E1 Mode without Jitter Attenuator           | 233 |

| Figure 44    | SRTS Jitter Tolerance in E1 Mode with Jitter Attenuator              | 234 |

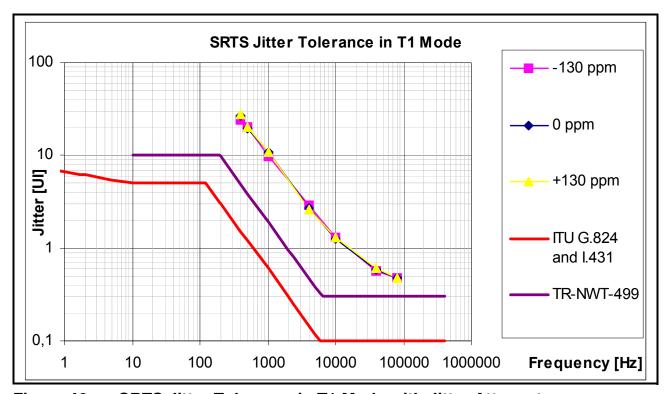

| Figure 45    | SRTS Jitter Tolerance in T1 Mode without Jitter Attenuator           | 235 |

| Figure 46    | SRTS Jitter Tolerance in T1 Mode with Jitter Attenuator              | 235 |

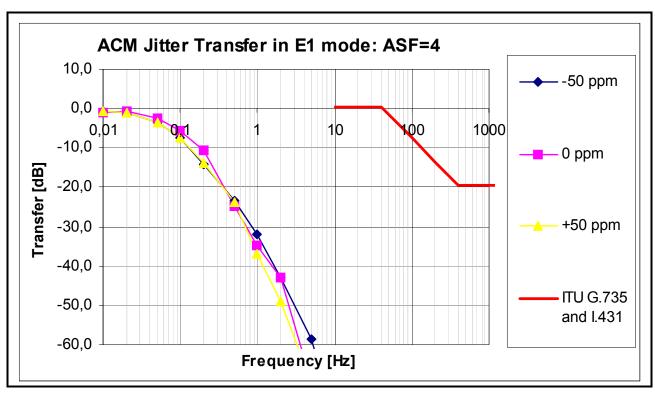

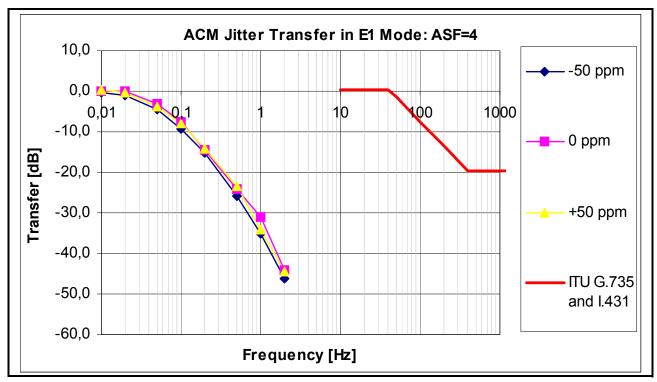

| Figure 47    | ACM Jitter Transfer in E1 Mode without Jitter Attenuator             | 236 |

| Figure 48    | ACM Jitter Transfer in E1 Mode with Jitter Attenuator                | 237 |

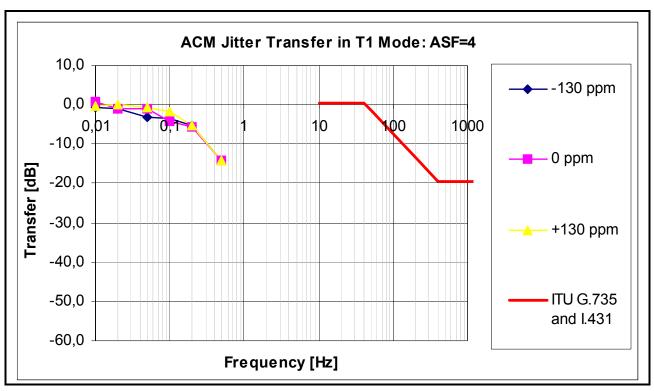

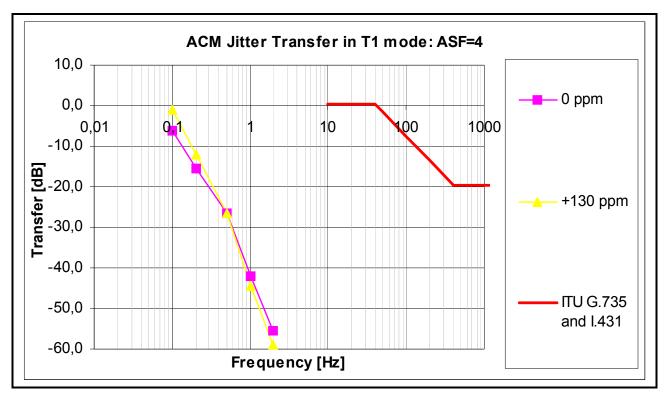

| Figure 49    | ACM Jitter Transfer in T1 Mode without Jitter Attenuator             |     |

| Figure 50    | ACM Jitter Transfer in T1 Mode with Jitter Attenuator                | 238 |

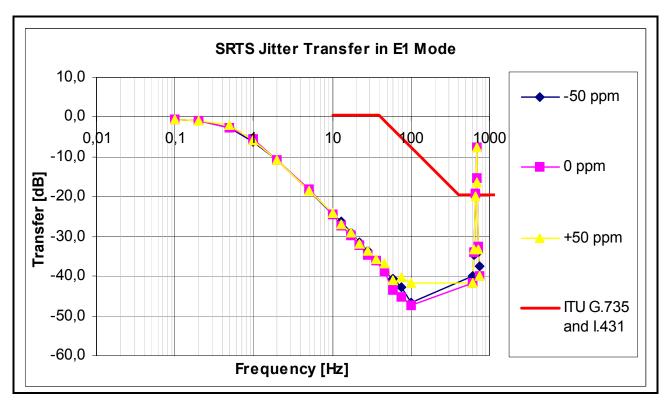

| Figure 51    | SRTS Jitter Transfer in E1 Mode without Jitter Attenuator            | 239 |

| Figure 52    | SRTS Jitter Transfer in E1 Mode with Jitter Attenuator               | 240 |

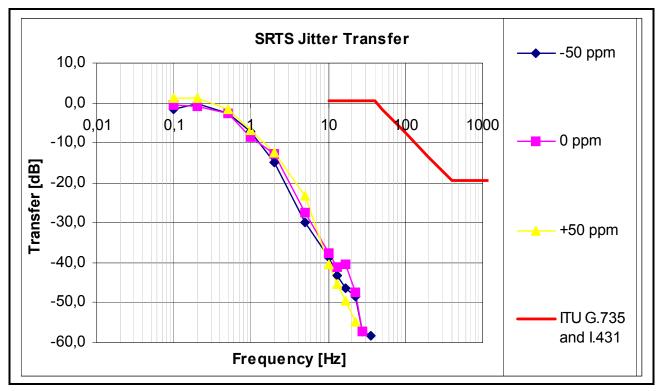

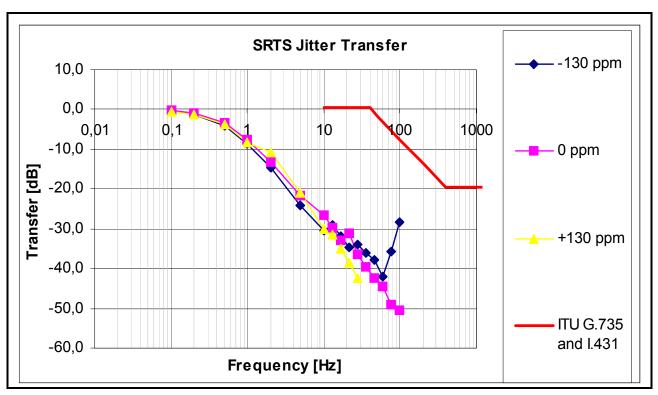

| Figure 53    | SRTS Jitter Transfer in T1 Mode without Jitter Attenuator            |     |

| Figure 54    | SRTS Jitter Transfer in T1 Mode with Jitter Attenuator               |     |

| Figure 55    | Input/Output Waveforms for AC Measurements                           |     |

| Figure 56    | Clock and Reset Interface Timing Diagram                             |     |

| Figure 57    | Framer Receive Interface Timing in FAM                               | 248 |

| Figure 58    | Framer Transmit Interface Timing in FAM                              |     |

| Figure 59    | Framer Receive Interface Timing in GIM                               |     |

| Figure 60    | Framer Transmit Interface Timing in GIM                              |     |

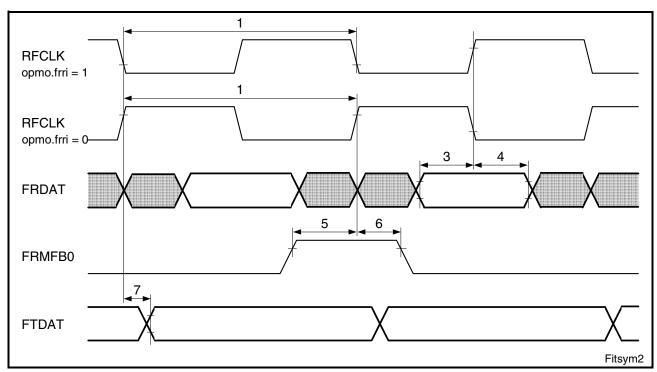

| Figure 61    | Framer Interface Timing for SYM 2.048 MHz                            |     |

| Figure 62    | Framer Interface Timing in SYM 8.192 MHz                             |     |

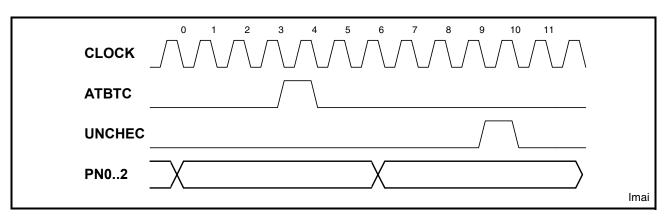

| Figure 63    | Framer Interface Timing in EC Mode                                   |     |

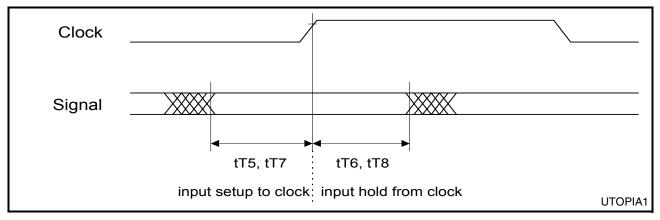

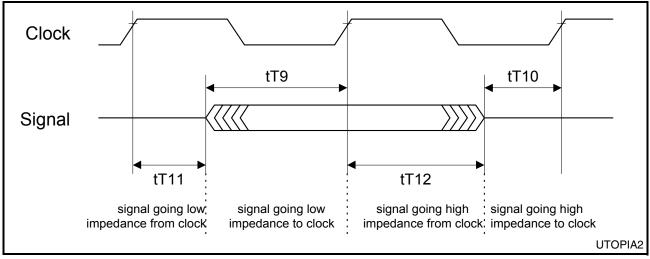

| Figure 64    | Setup and hold time definition (single- and multi PHY)               |     |

| Figure 65    | Tri-state timing (multi-PHY, multiple devices only)                  |     |

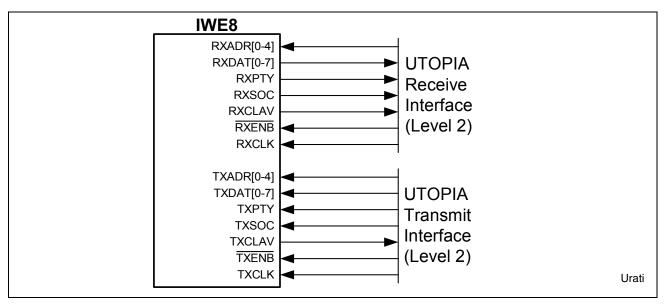

| Figure 66    | Timing of the IMA Interface                                          |     |

| Figure 67    | Clock Recovery Interface Timing Diagram                              |     |

| Figure 68    | Intel Mode Write Cycle Timing Diagram                                |     |

| Figure 69    | Intel Mode Read Cycle Timing Diagram                                 |     |

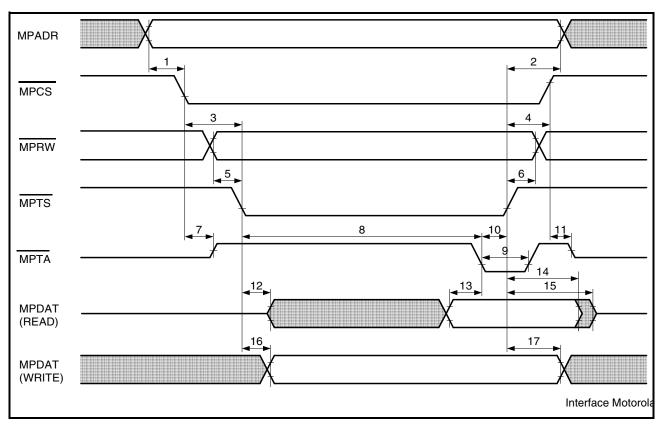

| Figure 70    | Motorola Mode Timing Diagram                                         |     |

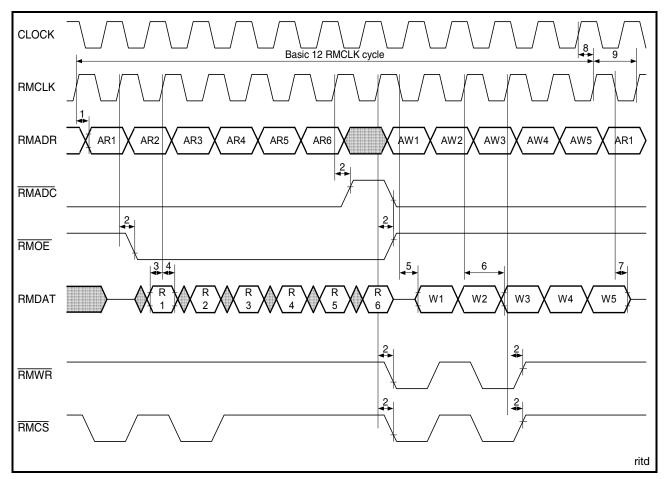

| Figure 71    | RAM Interface Timing Diagram                                         |     |

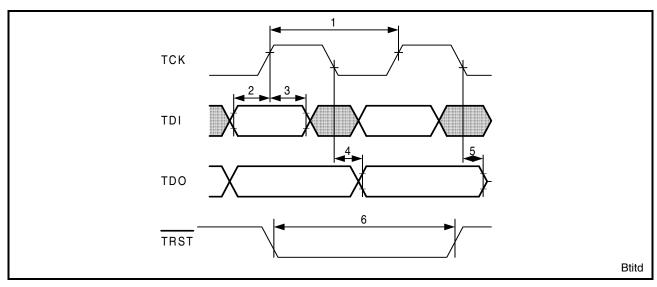

| Figure 72    | Boundary-Scan Test Interface Timing Diagram                          |     |

| Figure 73    | Package Outline: P-BGA-256 (Plastic Metric Quad Flat Package)        |     |

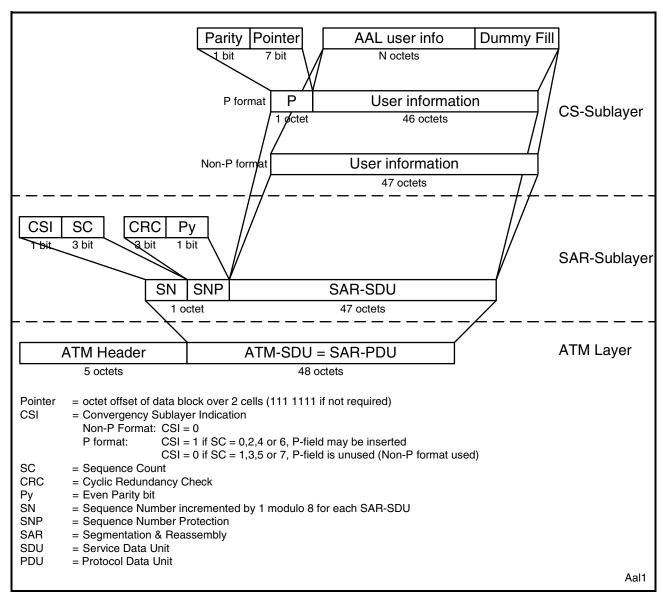

| Figure 74    | Structure of the AAL1 SAR-PDU                                        | 274 |

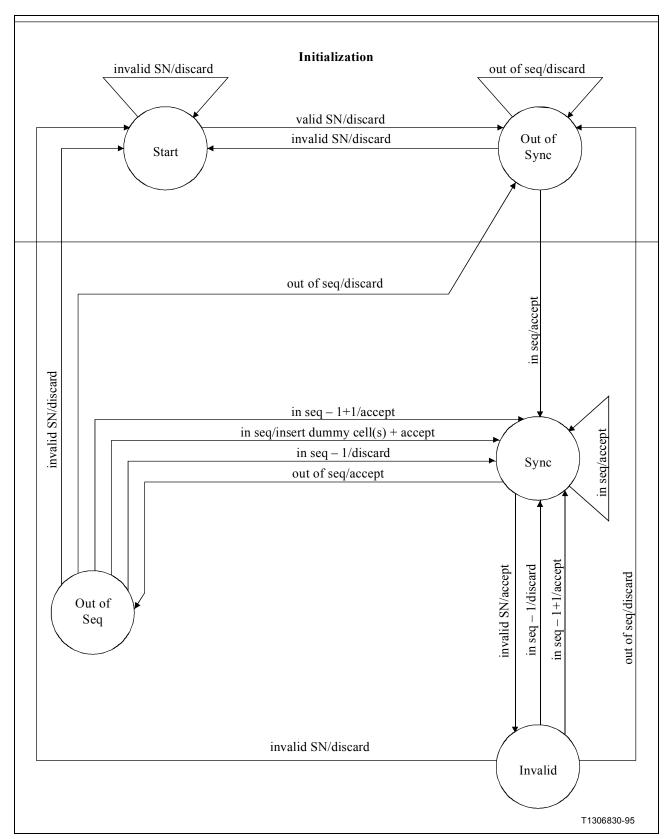

| Figure 75    | Informative and Example Algorithm State Machine (Fig. III.2/I.363.1) |     |

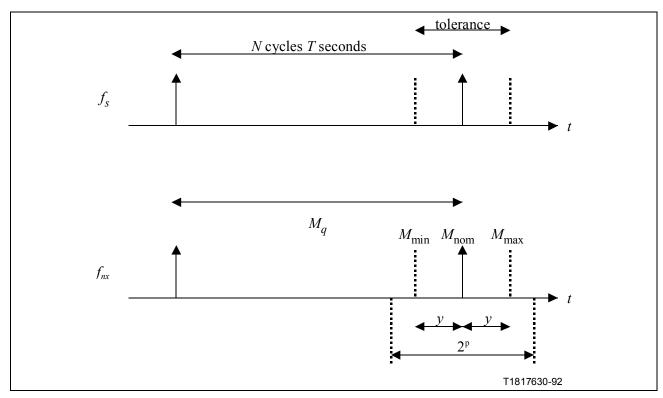

| Figure 76    | The Concept of SRTS (Fig. 5/I.363.1)                                 |     |

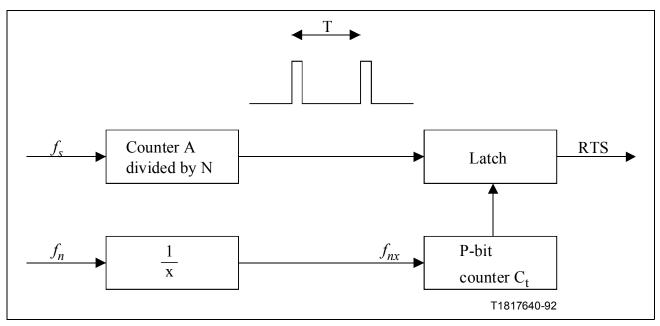

| Figure 77    | Generation of Residual Time Stamp (RTS) (Fig.6/ I.363.1)             |     |

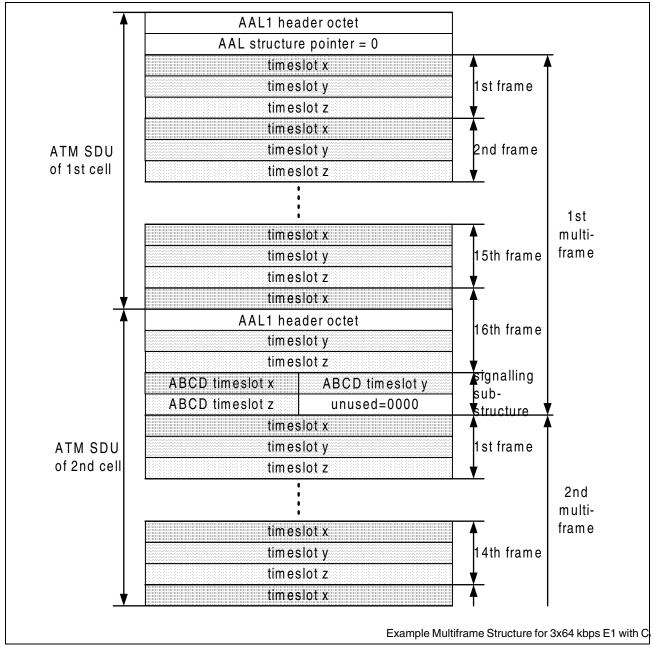

| Figure 78    | Example Multiframe Structure for 3x64 kbit/s E1 with CAS             |     |

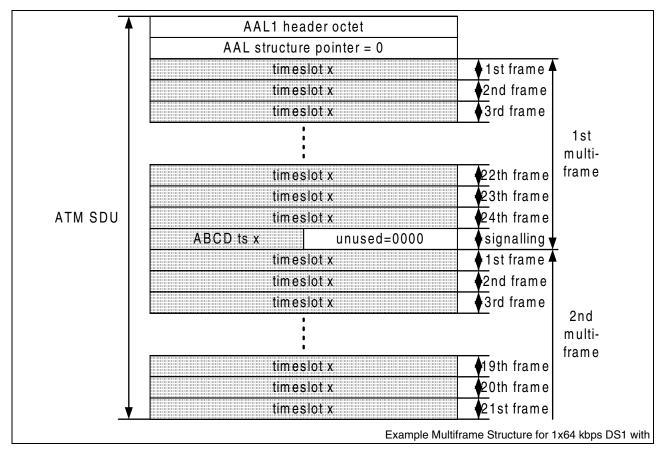

| Figure 70    | Example Multiframe Structure for 1y64 khit/s DS1 with CAS            | 283 |

| List of Tab | oles                                                             | Page    |

|-------------|------------------------------------------------------------------|---------|

| Table 1     | Generic Framer Interface (73 pins)                               | 23      |

| Table 2     | UTOPIA Interface (36 pins)                                       |         |

| Table 3     | IMA Interface                                                    | 27      |

| Table 4     | Clock Recovery Interface                                         |         |

| Table 5     | Microprocessor Interface                                         | 28      |

| Table 6     | External RAM Interface                                           | 30      |

| Table 7     | Test Interface                                                   | 31      |

| Table 8     | Miscellaneous                                                    | 32      |

| Table 9     | Power Supply                                                     | 33      |

| Table 10    | Not Connected Pins                                               | 33      |

| Table 11    | Functions of IWE8 Blocks                                         | 38      |

| Table 12    | ATM Cell Discarding                                              | 43      |

| Table 13    | Activation sequence for ATM transmit ports                       | 45      |

| Table 14    | Activation sequence for ATM receive ports                        | 51      |

| Table 15    | Definition of the CAS Signalling Conditioning Nibbles            | 54      |

| Table 16    | Relationship betw. Cell Filling & Segmentation Buffer Subblock S | ize. 55 |

| Table 17    | Cell Filling level values                                        |         |

| Table 18    | Activation sequence for AAL segmentation channels                |         |

| Table 19    | Activation sequence for AAL reassembly channels                  | 63      |

| Table 20    | Relationship betw. Cell Filling and Reassembly Buffer Subblock S | Size 63 |

| Table 21    | Coding of Slot Type in internal configuration RAMs               | 85      |

| Table 22    | RAM slot positions for ITU-T G.804 compliant ATM mapping         | 85      |

| Table 23    | AAL Idle slot positions for structured CES in AAL mode           | 87      |

| Table 24    | AAL Idle slot positions for structured CES with CAS in AAL mode  | 89      |

| Table 25    | Time slot Mapping in T1 Translation Mode 0                       | 94      |

| Table 26    | F-Channel Format in T1 Mode                                      |         |

| Table 27    | Clock Recovery Interface frame format                            | 110     |

| Table 28    | Configuration of the Microprocessor Interface Mode               |         |

| Table 29    | Master Clock Frequency Depending on Mode                         |         |

| Table 30    | Statistics Counters for ATM Ports                                |         |

| Table 31    | Statistics Counters for AAL Ports                                | 138     |

| Table 32    | Internal Registers                                               |         |

| Table 33    | Absolute Maximum Ratings                                         |         |

| Table 34    | Clock and Reset Interface AC Timing Characteristics              |         |

| Table 35    | Framer Receive Interface Timing in FAM                           | 249     |

| Table 36    | Framer Transmit Interface Timing in FAM                          |         |

| Table 37    | Framer Receive Interface Timing in GIM                           | 251     |

| Table 38    | Framer Transmit Interface Timing in GIM                          |         |

| Table 39    | Framer Interface AC Timing Characteristics in SYM2 Mode          | 254     |

| Table 40    | Framer Interface Timing in SYM8                                  |         |

| Table 41    | Framer Interface Timing in EC Mode                               |         |

| Table 42    | Transmit Timing (8-Bit Data Bus. 33 MHz. Single PHY)             | 258     |

| List of Table | es                                                     | Page |

|---------------|--------------------------------------------------------|------|

| Table 43      | Receive Timing (8-Bit Data Bus, 33 MHz, Single PHY)    | 258  |

| Table 44      | Transmit Timing (8-Bit Data Bus, 33 MHz, Multi-PHY)    | 259  |

| Table 45      | Receive Timing (8-Bit Data Bus, 33 MHz, Multi-PHY)     | 259  |

| Table 46      | IMA Interface AC Timing Characteristics                | 261  |

| Table 47      | Clock Recovery Interface AC Timing Characteristics     | 261  |

| Table 48      | Intel Mode Write Cycle AC Characteristics              | 262  |

| Table 49      | Intel Mode Read Cycle AC Timing Characteristics        | 263  |

| Table 50      | Motorola Mode AC Timing Characteristics                | 264  |

| Table 51      | RAM Interface AC Timing Characteristics                | 266  |

| Table 52      | Boundary-Scan Test Interface AC Timing Characteristics | 267  |

| Table 53      | Boundary Scan Register                                 |      |

| Table 54      | Bit allocation of E1 time slot 16 for CAS              | 281  |

| Table 55      | Allocation of CAS Bits to 24 Frame Multiframe          | 283  |

**Overview**

#### 1 Overview

The Interworking Element for

8 E1/T1 Lines PXB 4219E, PXB 4220E, PXB 4221E (IWE8) is a member of Infineon's ATM chip set. Together with framing and line interface components (e.g. Infineon's QuadFALC PEB 22554) the IWE8 serves as gateway between Asynchronous Transfer Mode (ATM) networks and timeslot based PDH networks.

Each of the 8 E1 or T1 input and output ports can be configured independently to operate in one of two basic modes:

#### **ATM Mode**

ATM mode ports operate as an ATM User Network Interface (UNI) at 2.048 Mbit/s (E1) or 1.544 Mbit/s (T1).

The device supports mapping of ATM cells in T1/E1 frames according to ITU-T G.804, "ATM Cell Mapping into Plesiochronous Digital Hierarchy (PDH)" [26] and ATM Forum, "ATM on Fractional E1/T1" [9].

It implements all Transmission Convergence (TC) sublayer functions of the Physical Layer (PHY) defined in ITU-T I.432, "B-ISDN User-network Interface - Physical layer Specification" [32]

#### **AAL Mode**

AAL mode ports operate as an ATM Circuit Emulation Service Interworking Function (CES-IWF) between Constant Bit Rate (CBR) equipment and an ATM network as described by the ATM Forum, "Circuit Emulation Services Version 2.0" [10]. (only PXB 4220/4221)

The CBR circuits are converted into ATM constant bit-rate virtual channels using the ATM Adaptation Layer type 1 (AAL1) as defined in I.363.1, "B-ISDN ATM Adaptation Layer Specification, Types 1 and 2" [31] or without any ATM Adaptation Layer overhead, which will be referred as AAL type 0 throughout the rest of this document.

The IWE8 provides the segmentation and reassembly function.

Both the "Unstructured DS1/E1 Service" and the "Structured DS1/E1 N x 64 kbit/s Basic Service" as described in the "Circuit Emulation Services Version 2.0" by the ATM Forum in [10] are supported. For simplicity reasons the shorthand notation "Unstructured CES" will be used to identify the "Unstructured DS1/E1 Service" while the "Structured DS1/E1 N x 64 kbit/s Service" will be referred to as "Structured CES" throughout the rest of this document.

## Interworking Element for 8 E1/T1 Lines IWE8

**PXB 4219E, PXB** 4220E, PXB 4221E

P-BGA-256-2

#### Version 3.4

#### 1.1 **Features**

- Full duplex ATM Packetizer/Depacketizer for 8 E1/T1 highways

- Configurable to T1 or E1 mode via external pin

- 8 T1/E1 ports configurable independently to ATM or AAL Mode

- ATM Mode (PXB 4219/4220/4221):

- ATM cell mapping into PDH according to ITU-T G.804 [26]

- B-ISDN User-Network interface Physical Layer according to ITU-T I.432 [32]

- B-ISDN User-Network interface Physical Layer operation at 1544 KBit/s and 2048 KBit/s according to ITU-T I.432.3 [34]

- AAL Mode (PXB 4220/4221):

- AAL1 according to ITU-T I.363.1 [31] or transparent without any adaptation layer overhead (AAL0)

- T1/E1 unstructured service according to ATM Forum af-vtoa-0078.000 [10] section

- - Robust/Fast according to ITU-T I.363.1 [30]

- According to ETSI (prl-ETS 300353 annex D) [17]

- Fast: Saves 6 ms during reassembly for 1 x 64 kbit/s connection

- AAL0 option: 48 Bytes user payload per ATM Cell, without AAL overhead

- Reassembly buffer can compensate up to +/- 4 ms Cell Delay Variation (CDV)

- Statistics counters per channel for lost/misinserted/errored cells etc.

| <ul> <li>Structured T1/E1 N x 64 kbit/s service according to [10] section 2 with M cl</li> </ul> | hannels |

|--------------------------------------------------------------------------------------------------|---------|

| of N x 64 kbit/s (M,N = 1to 24 for T1) (M,N = 1to 32 for E1)                                     |         |

| <ul> <li>Channel Associated Signalling (CAS) support according to [10]</li> </ul>                |         |

| <ul> <li>Echo Canceller Mode</li> </ul>                                                          |         |

| <ul> <li>Partially filled cells with programmable filling thresholds</li> </ul>                  |         |

| <ul> <li>Selectable Sequence Count Algorithm:</li> </ul>                                         |         |

|                                                                                                  |         |

| Туре                            | Package   |

|---------------------------------|-----------|

| PXB 4219E, PXB 4220E, PXB 4221E | P-BGA-256 |

Overview

- Internal clock recovery circuit using Synchronous Residual Time Stamp (SRTS, for fully filled cells only) or Adaptive Clock Method (ACM) for unstructured CES ports.

For SRTS a patent fee needs to be paid. Optionally, it's possible to order the PXB 4221 device, which comes without SRTS clock recovery.

- Trunk freezing and conditioning according to Bellcore TR-NWT-000170 [14]

- IMA interface:

- Programmable threshold between read and write pointer of Mapping Buffer

- Output Signal for buffer threshold crossing

- Output Signal for discarded cell

- Output pins for port number indication

- 8 generic framer interfaces with integrated transmit clock selector supporting

- Synchronous Mode (SYM) for E1

- Generic Interface Mode (GIM)

- FALC Mode (FAM): Glue-less interface for Infineon's Framer and Line Interface Components (FALC)

- Echo Canceller Mode (EC): ATM cells are duplicated internally and transmitted via two framer ports

- UTOPIA industry standard interface:

- Level 2 in slave mode; 8 data, 5 address lines

- Level 1 in master/slave mode

- UTOPIA clock up to 38.88 MHz

- 16-bit generic microprocessor interface for control and configuration of the chip runs either in Intel 386EX or Motorola compatible mode

- External synchronous Flow-Through SSRAM 1 x 64k x 33 bit or 1 x 64k x 32 bit required

- · Build-in data path loops for test

- Cell insertion/extraction via microprocessor interface

- 3.3 Volt power supply with 5 Volt tolerant inputs

- Typical power dissipation 1 Watt

- P-BGA-256 package

- Temperature range from -40° to +85°C

# 1.2 Logic Symbol

Figure 1 Logic Symbol

## 1.3 Typical Applications

Figure 2 illustrates three typical application areas which utilize the IWE8 chip in Line Interface Cards (LICs) or Network Interface Controllers (NICs).

Application 1 utilizes the IWE8 as an internetworking device for communication between a narrowband Time-Slot based network and an ATM network.

Application 2 utilizes the IWE8 chip to enable the use of an existing T1/E1 access line for connection to an ATM network.

In application 3, the IWE8 chip enables terminals using a Leased Line or Time-Slot based service to convert from T1/E1 network connection to ATM network connection without noticeable changes to the subscriber.

Figure 2 Typical IWE8 Applications

The PXB 4220 IWE8 chip is designed to handle up to eight T1/E1 ports. It transfers data between the Pulse Code Modulation (PCM)-highway and an UTOPIA ATM Interface.

#### 1.3.1 Line Card

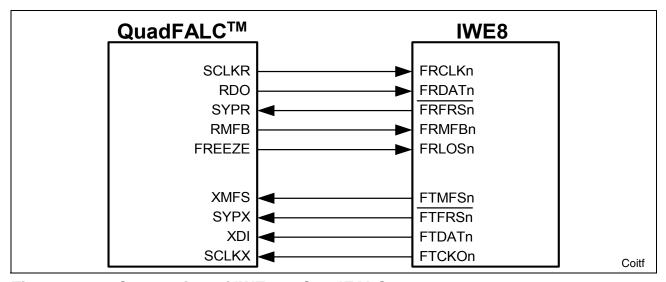

**Figure 3** shows an example Line Interface Card (LIC) utilizing the IWE8 in a switch environment. Two Infineon Quad Framer and Line Interface Component (QuadFALC, PEB 22554) chips are connected at the PCM ports. An ATM Layer circuit is connected at the UTOPIA Interface port and could be implemented using Infineon PXB 4350 ATM Layer Processor (ALP) chip.

Figure 3 Line Card for 8 T1/E1 Channels

External synchronous SRAM is always required for proper IWE8 operation. The IWE8 requires only one main operating clock of 12 times the data rate of one port. An emergency clock of 32.768 MHz is optional. The Framer and Utopia interface clocks can be completely asynchronous with respect to the main clock. A microprocessor controls and operates the IWE8 via a generic 16-bit interface.

#### 1.3.2 Echo Canceller

In communication links reflections resulting in an electrical echo are due to hybrid splits or imperfect terminations in subscriber loops. Acoustical echoes may occur due to poor isolation of microphone and speaker of some telephone systems. These electrical and acoustical echoes disturb the quality of the transmission. To ensure high quality, pure data transmission the ITU-T suggests in the recommendation G.131 [22] the use of echo cancellers. Echo cancellation is extremely desirable for data links with total round trip transmission times of more than 50 ms.

Figure 4 Echo Canceller Application

The echo cancelling function itself is performed in STM. In the application above the IWE8 is used to translate voice ATM channels into STM channels and vice versa. Infineon's Smart Integrated Digital Echo Canceller (SIDEC, PEB 20954) is used for cancellation of the echo that is generated by reflection on the near end side and heard by the far end speaker. The SIDEC can cancel end echo paths (SDH or PDH network on near end side) up to 128 ms. For details see [21]

**Overview**

#### 1.4 Differences Between PXB4220 And PXB4219

The IWE8 type PXB 4219 does only support the ATM mode used for ITU-T G.804 compliant ATM cell mapping into the plesiochronous digital hierarchy (PDH) at line rates of 1544 kbit/s and 2048 kbit/s. The AAL mode is not available.

#### 1.5 Differences Between PXB4220 And PXB4221

The IWE8 type PXB 4220 uses an internal clock recovery mechanism (SRTS) which is patented by Bellcore. SRTS is supported for fully filled cells only.

#### Related Patents are:

- Bellcore patent No. 5,260,978

(Synchronous Residual Time Stamp for Timing Recovery in a broadband network)

- Bellcore patent No. 4,839,306

(Method and apparatus for multiplexing circuit and packet traffic)

Infineon Technologies is not allowed to collect SRTS license fees on the IWE8 on behalf of Bellcore. Contacts for license issues are given in **Chapter 13**.

Every IWE8 customer must get in contact with Bellcore legal department by himself to clarify whether his application needs to license the SRTS functionality.

For customers who do not want to use the built-in SRTS mechanism, Infineon provides a special version of the IWE8. The name of this device is PXB 4221 and covers the same functionality (pin and register compatible) like the PXB 4220. SRTS is physically and permanently disabled, so that no patent fees have to be paid.

**Pin Descriptions**

# 2 Pin Descriptions

## 2.1 Pin Diagram

Figure 5 Pin Configuration

**Pin Descriptions**

#### 2.2 Pin Definitions and Functions

#### **Output Pull Up and Pull Down Type Definitions**

**PUX** Pull Up of strength x (x = A, B) is implemented. The

corresponding current is specified in Chapter 9.4

**PDx** Pull Down of strength x (x = A) is implemented. The

corresponding current is specified in Chapter 9.4

**Tri** Tri-stated when inactive

#### 2.2.1 Generic Framer Interface

Table 1 Generic Framer Interface (73 pins)

| Pin No.                                      | Symbol     | Input (I)<br>Output (O) | Function                                                                                                                         |

|----------------------------------------------|------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| C5, A6, B9,<br>A12, C14,<br>A18, C19,<br>G17 | FRCLK[7:0] | I                       | Framer Receive Clock Receive clock for the framer interface                                                                      |

| B4, C7, C9,<br>B11, B14,<br>A17, B20,<br>F18 | FRDAT[7:0] | I<br>PDA                | Framer Receive Data Receive data input of the framer interface                                                                   |

| A3, B6, D9,<br>C11, A14,<br>C16, C18,<br>E19 | FRMFB[7:0] | I<br>PUA                | Framer Receive Multiframe Begin Indication that a new multi-/superframe is available on the receive side of the framer interface |

| B3, A5, A8,<br>A10, B13,<br>A16, A19,<br>E18 | FRFRS[7:0] | O<br>PUA                | Framer Receive Frame Synchronization Pulse Indication that a new frame is available on the receive side of the framer interface  |

| A4,B7, A9,<br>B12, A15,<br>D16, D18,<br>E20  | FRLOS[7:0] | I<br>PDA                | Framer Receive Loss of Signalling Indication that CAS bits are invalid, IWE8 will start CAS freezing                             |

# **Pin Descriptions**

Table 1 Generic Framer Interface (73 pins) (cont'd)

| Pin No.                                      | Symbol     | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                             |

|----------------------------------------------|------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C4, D5, C2,<br>B1, C13,<br>B16, A20,<br>D20  | FTCKO[7:0] | O/I<br>PDA              | Framer Transmit Clock Transmit clock for the framer interface.  Recovered clock output from the ICRC Framer receive clock output from pin FRCLKN  Output of the clock derived from RFCLK Input for an external clock recovery device |

| B2, D7, B8,<br>B10, A13,<br>C15, B18,<br>D19 | FTDAT[7:0] | O<br>PUA                | Framer Transmit Data Transmit data output of the framer interface                                                                                                                                                                    |

| A2, C6, C8,<br>C10, D12,<br>D14, B17,<br>C20 | FTMFS[7:0] | O<br>PUA                | Framer Transmit Multiframe Synchronization Indication that a new multi-/superframe is available on the transmit side of the framer interface                                                                                         |

| C3, B5, A7,<br>D10, C12,<br>B15, C17,<br>E17 | FTFRS[7:0] | O<br>PUA                | Framer Transmit Frame Synchronization Pulse Indication that a new frame is available on the transmit side of the framer interface                                                                                                    |

| L1                                           | RFCLK      | I                       | Reference Clock SYM and EC mode: Central framer interface clock for all framer ports FAM and GIM: Optional SRTS/ACM reference or emergency clock for the framer receive interface in case of clock failure                           |

**Pin Descriptions**

# 2.2.2 UTOPIA Interface

Table 2 UTOPIA Interface (36 pins)

| Pin No.                                         | Symbol     | Input (I)<br>Output (O)      | Function                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------|------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U12, V12,<br>W12, Y12,<br>U11, V11,<br>W11, Y11 | RXDAT[7:0] | O<br>PUA                     | UTOPIA Receive Data Bus Byte-wide data driven from PHY to ATM layer. RxData[7] is the MSB.                                                                                                                                                                                                                    |

| Y13                                             | RXPTY      | O<br>PUA                     | UTOPIA Receive Odd Parity Bit Odd parity for RXDAT[0:7] driven by the PHY layer.                                                                                                                                                                                                                              |

| W10                                             | RXSOC      | O<br>PDA                     | UTOPIA Receive Start-of-Cell Active high signal asserted by the PHY layer when RXDAT[0:7] contains the first valid byte of a cell.                                                                                                                                                                            |

| V10                                             | RXCLAV     | Slave: O<br>Master: I<br>PDA | UTOPIA Receive Cell Available Slave: RXCLAV is an active high signal asserted by the PHY layer to indicate that it has data available for transfer to the ATM layer.  Master: RXCLAV is an active high signal asserted by the ATM layer to indicate that it has data available for transfer to the PHY layer. |

| V13                                             | RXCLK      | I                            | UTOPIA Receive Clock Transfer/synchronization clock from the ATM layer to the PHY layer for synchronizing transfers on RXDAT[0:7].                                                                                                                                                                            |

| W13                                             | RXENB      | Slave: I<br>Master: O<br>PUA | UTOPIA Receive Enable Slave: Active low signal asserted by the ATM layer to indicate that RXDAT[0:7] and RXSOC will be sampled at the end of the next cycle. Master: Active low signal asserted by the PHY layer to indicate that RXDAT[0:7] and RXSOC will be sampled at the end of the next cycle.          |

# **Pin Descriptions**

Table 2 UTOPIA Interface (36 pins) (cont'd)

| Pin No.                                 | Symbol     | Input (I)<br>Output (O)      | Function                                                                                                                                                                                                                           |

|-----------------------------------------|------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V5, Y4, Y3,<br>U5, V4                   | RXADR[4:0] | I<br>PUA                     | UTOPIA Receive Address Bus Five bit wide true data driven from the ATM to MPHY layer to select the appropriate MPHY device. RXADR[4] is the MSB.                                                                                   |

| U9, Y8,<br>W8, V8,<br>Y7, W7,<br>V7, Y6 | TXDAT[7:0] | I<br>PUA                     | UTOPIA Transmit Data Bus Byte-wide true data driven from ATM to PHY layer. TXDAT[7] is the MSB.                                                                                                                                    |

| V9                                      | TXPTY      | I<br>PUA                     | UTOPIA Transmit Odd Parity Bit TXPTY is the odd parity bit over TXDAT[0:7] driven by the ATM layer.                                                                                                                                |

| W6                                      | TXSOC      | I<br>PDA                     | UTOPIA Transmit Start-of-Cell Active high signal asserted by the ATM layer when TXDAT[0:7] contains the first valid byte of the cell.                                                                                              |

| V6                                      | TXCLAV     | Slave: O<br>Master: I<br>PDA | UTOPIA Transmit Cell Available Slave: TXCLAV is an active high signal asserted by the PHY layer to indicate it can accept data.  Master: TXCLAV is an active high signal asserted by the ATM layer to indicate it can accept data. |

| Y9                                      | TXCLK      | I                            | UTOPIA Transmit Clock Data transfer/synchronization clock provided by the ATM layer to the PHY layer for synchronizing transfers on TXDAT[0:7].                                                                                    |

# **Pin Descriptions**

Table 2 UTOPIA Interface (36 pins) (cont'd)

| Pin No.                  | Symbol     | Input (I)<br>Output (O)      | Function                                                                                                                                                                                                                                      |

|--------------------------|------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U7                       | TXENB      | Slave: I<br>Master: O<br>PUA | UTOPIA Transmit Enable Slave: Active low signal asserted by the ATM layer during cycles when TXDAT[0:7] contains valid cell data. Master: Active low signal asserted by the PHY layer during cycles when TXDAT[0:7] contains valid cell data. |

| W4, Y2,<br>W3, Y1,<br>W2 | TXADR[4:0] | I<br>PUA                     | UTOPIA Transmit Address Bus Five bit wide true data driven from the ATM to MPHY layer to poll and select the appropriate MPHY device. TXADR4 is the MSB.                                                                                      |

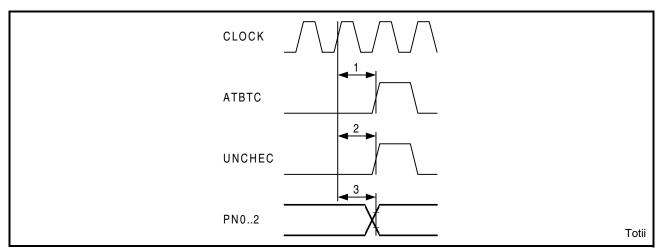

#### 2.2.3 IMA Interface

Table 3 IMA Interface

| Pin No.       | Symbol  | Input (I)<br>Output (O) | Function                                                                                                                                                                  |

|---------------|---------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Y10           | ATBTC   | O<br>Tri                | ATM Transmit Buffer Threshold Crossing Indicates if the difference between the write and read pointer of the mapping buffer became smaller than a SW selectable threshold |

| L20           | UNCHEC  | O<br>Tri                | Uncorrectable HEC Error Indicates if a cell has been discarded due to an uncorrectable HEC error                                                                          |

| Y5, W5,<br>M1 | PN[2:0] | O<br>Tri                | Port Number Indicates the port number where the cell causing ATBT or UNCHEC being asserted came from                                                                      |

**Pin Descriptions**

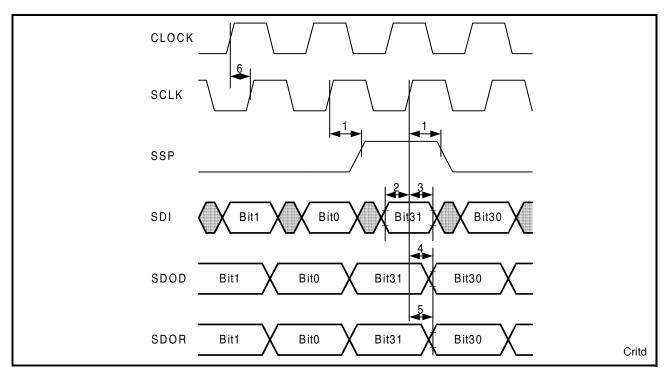

# 2.2.4 Clock Recovery Interface

Table 4 Clock Recovery Interface

| . 45.0  | Olook 1100 | orony mitoriaco         |                                                                                                            |

|---------|------------|-------------------------|------------------------------------------------------------------------------------------------------------|

| Pin No. | Symbol     | Input (I)<br>Output (O) | Function                                                                                                   |

| Y18     | SDI        | I                       | Serial Data Input Clock recovery frame input.                                                              |

| Y20     | SDOD       | O<br>Tri                | Serial Data Output Data Clock recovery frame output                                                        |

| W20     | SDOR       | O<br>Tri                | Serial Data Output Reset Clock recovery reset frame output                                                 |

| T17     | SSP        | O<br>Tri                | Serial Synchronization Pulse Frame synchronization pulse output                                            |

| T20     | SCLK       | O<br>Tri                | Serial Clock Clock output of the clock recovery interface. Runs at the same frequency than the CLOCK input |

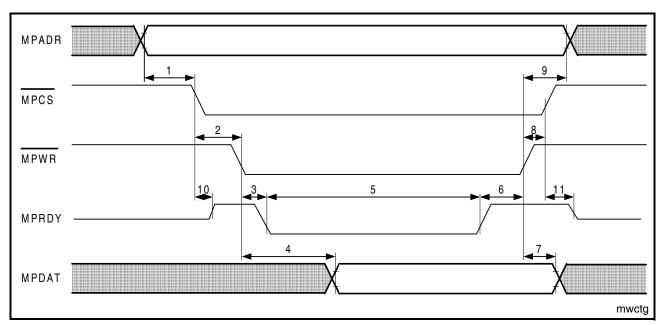

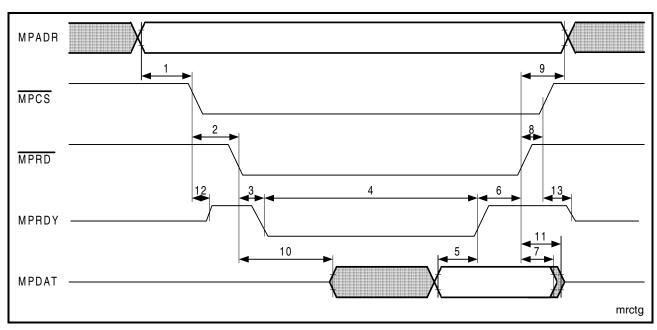

# 2.2.5 Microprocessor Interface

Table 5 Microprocessor Interface

| Pin No.                                                                               | Symbol      | Input (I)<br>Output (O) | Function                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------|-------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| K1, K3, K2,<br>J1, J2, J3,<br>J4, H1, H2,<br>H3, G1,<br>G2, G3, F1,<br>F2, G4         | MPDAT[15:0] | I/O<br>PUA              | Microprocessor Data Bus This bidirectional three-state bus provides the general-purpose data path between the IWE8 and an external master. The bus uses little endian word order. MPDAT15 is the MSB. |

| T4, V1, U2,<br>T3, U1, T2,<br>R3, P4, T1,<br>R2, P3, R1,<br>P2, P1, N3,<br>N2, N1, M4 | MPADR[17:0] |                         | Microprocessor Address Bus Provides the address of the current bus cycle. Addresses are 16-bit aligned. MPADR17 is the MSB of the bus                                                                 |

| E2                                                                                    | MPCS        | I                       | Microprocessor Chip Select This signal is driven by the bus master to indicate a read or write access.                                                                                                |

# **Pin Descriptions**

Table 5

Microprocessor Interface (cont'd)

| Pin No. | Symbol        | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|---------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E1      | MPWR/<br>MPRW | I                       | Microprocessor Write Enable (Intel Bus Mode) This signal is driven by the bus master to indicate a write data transfer Read/Write Enable (Motorola Bus Mode) This three-state signal is driven by the bus master to indicate the direction of the bus's data transfer                                                                                                                     |

| F3      | MPRD/<br>MPTS | I                       | Microprocessor Read Enable (Intel Bus Mode) This signal is driven by the bus master to indicate a read data transfer Microprocessor Transfer Start (Motorola Bus Mode) This signal is asserted by the bus master to indicate the start of a bus cycle that transfers data to or from the device                                                                                           |

| L4      | MPRDY<br>MPTA | O<br>Tri                | Microprocessor Ready (Intel Bus Mode) This three-state output indicates that the device has accepted date from the master (write) or has driven the data bus with valid data (read) Microprocessor Transfer Acknowledge (Motorola Bus Mode) This three-state output indicates that the device has accepted date from the master (write) or has driven the data bus with valid data (read) |

| M2      | MPIR1         | O<br>PUB                | Microprocessor Interrupt Request 1 Main interrupt pin indicating a special event in the IWE8.                                                                                                                                                                                                                                                                                             |

| M3      | MPIR2         | O<br>PUB                | Microprocessor Interrupt Request 2 This signal is generated by timer set 2 to indicate that a counter expired                                                                                                                                                                                                                                                                             |

**Pin Descriptions**

# 2.2.6 External RAM Interface

Table 6 External RAM Interface

| Table 0                                                                                                                                                        | Table 0 External nam interface |                         |                                                                                                                                                             |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin No.                                                                                                                                                        | Symbol                         | Input (I)<br>Output (O) | Function                                                                                                                                                    |  |

| F19, G18,<br>F20, G19,<br>G20, H18,<br>H19, H20,<br>J17, J18,<br>J19, J20,<br>K17, K18,<br>K19, K20                                                            | RMADR[15:0]                    | O<br>Tri                | RAM Address Bus This bus provides the address of the current bus cycle. RMADR15 is the MSB.                                                                 |  |

| M18, M17, N20, N19, N18, P20, P19, P18, R20, R19, P17, R18, T19, T18, U20, V20, U18, U19, V19, W19, W19, W17, U16, W17, V16, V17, W16, V15, U14, Y16, W15, V14 | RMDAT[32:0]                    | I/O<br>PUB              | RAM Data Bus This bidirectional three-state bus provides the data path between the IWE8 and the external memory. RMDAT32 is parity bit, RMDAT31 is the MSB. |  |

| M20                                                                                                                                                            | RMCS                           | O<br>Tri                | RAM Chip Select This signal enables read or write accesses to the external memory                                                                           |  |

| L19                                                                                                                                                            | RMOE                           | O<br>Tri                | RAM Output Enable This signal enables the outputs of the external memory                                                                                    |  |

| M19                                                                                                                                                            | RMWR                           | O<br>Tri                | RAM Write Enable This output is asserted when a write access to the external memory                                                                         |  |

# **Pin Descriptions**

Table 6 External RAM Interface (cont'd)

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                  |

|---------|--------|-------------------------|-------------------------------------------------------------------------------------------|

| L18     | RMADC  | O<br>Tri                | RAM Address Control This output is asserted to indicate a valid address on RMADR[15:0]    |

| W14     | RMCLK  | O<br>Tri                | RAM Clock Clock output for the external RAM. It runs at the same frequency as CLOCK input |

## 2.2.7 Test Interface

#### Table 7 Test Interface

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                               |

|---------|--------|-------------------------|----------------------------------------------------------------------------------------|

| D2      | TDO    | O<br>Tri                | Boundary Scan Test Data Output                                                         |

| E4      | TDI    | I<br>PUA                | Boundary Scan Test Data Input                                                          |

| C1      | TCK    | I<br>PUA                | Boundary Scan Test Clock                                                               |

| D1      | TMS    | I<br>PUA                | Boundary Scan Test Mode Select 0 = normal operation 1 = Enable boundary scan test mode |

| E3      | TRST   | I<br>PDA                | Boundary Scan Test Reset                                                               |

| V3      | TSCEN  | I<br>PDA                | Internal Test Pins                                                                     |

| A11     | TSCSH  |                         | TSCEN and TSCSH must be low for proper operation                                       |

| Y15     | PMT    | PDA                     | Internal Test Pins                                                                     |

| V18     | TBUS   |                         | 00 = Intel mode<br>01 = prohibited<br>10 = prohibited<br>11 = Motorola Mode            |

# **Pin Descriptions**

| Table 7 | Test Interface (cont'd) |                         |                                                                                                                  |  |

|---------|-------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------|--|

| Pin No. | Symbol                  | Input (I)<br>Output (O) | Function                                                                                                         |  |

| W9      | UTTR                    | I<br>PUA                | Utopia TRI-STATE 0 = tristate all Utopia outputs 1 = normal operation                                            |  |