16/32-Bit

**Architecture**

XC2336B

16/32-Bit Single-Chip Microcontroller with 32-Bit Performance XC2000 Family / Value Line

Data Sheet V1.5 2014-06

Edition 2014-06

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2014 Infineon Technologies AG

All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (<a href="https://www.infineon.com">www.infineon.com</a>).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

16/32-Bit

**Architecture**

XC2336B

16/32-Bit Single-Chip Microcontroller with 32-Bit Performance XC2000 Family / Value Line

Data Sheet V1.5 2014-06

#### XC2336B Data Sheet

Revision History: V1.5 2014-06

Previous Versions:

V1.4, 2013-02

V1.3, 2011-07

V1.2, 2010-04

V1.1, 2009-07

#### V1.0, 2009-03 Preliminary

|      | ,                                                                     |

|------|-----------------------------------------------------------------------|

| Page | Subjects (major changes since last revision)                          |

| 9    | Added XC2336B-40FxLR to Basic Device Types                            |

| 10   | Moved XC2336B-24FxL, XC2336B-40FxL from Basic to Special Device Types |

| 103  | Added package type PG-LQFP-64-24                                      |

#### **Trademarks**

C166<sup>™</sup>, TriCore<sup>™</sup> and DAVE<sup>™</sup> are trademarks of Infineon Technologies AG.

#### We Listen to Your Comments

Is there any information in this document that you feel is wrong, unclear or missing? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

#### **Table of Contents**

## **Table of Contents**

| 1     | Summary of Features 7                             |

|-------|---------------------------------------------------|

| 1.1   | Basic Device Types                                |

| 1.2   | Special Device Types                              |

| 1.3   | Definition of Feature Variants                    |

| 2     | General Device Information                        |

| 2.1   | Pin Configuration and Definition                  |

| 2.2   | Identification Registers                          |

| 3     | Functional Description                            |

| 3.1   | Memory Subsystem and Organization                 |

| 3.2   | Central Processing Unit (CPU)                     |

| 3.3   | Memory Protection Unit (MPU) 34                   |

| 3.4   | Memory Checker Module (MCHK)                      |

| 3.5   | Interrupt System                                  |

| 3.6   | On-Chip Debug Support (OCDS)                      |

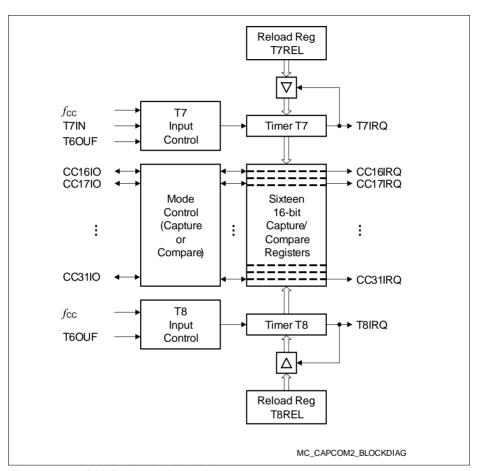

| 3.7   | Capture/Compare Unit (CC2)                        |

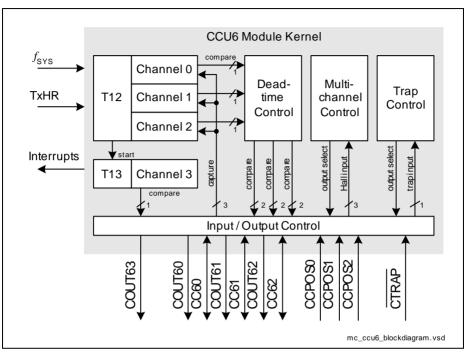

| 3.8   | Capture/Compare Units CCU6x                       |

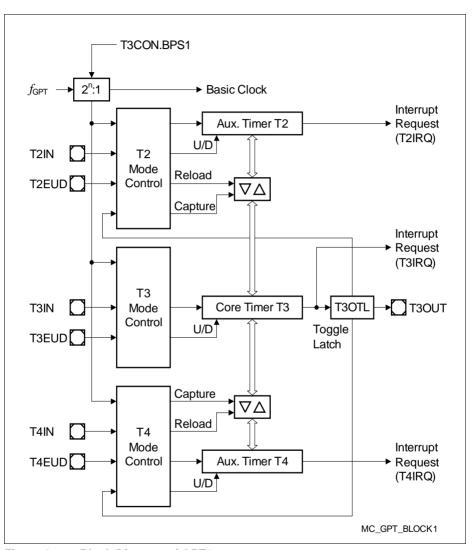

| 3.9   | General Purpose Timer (GPT12E) Unit               |

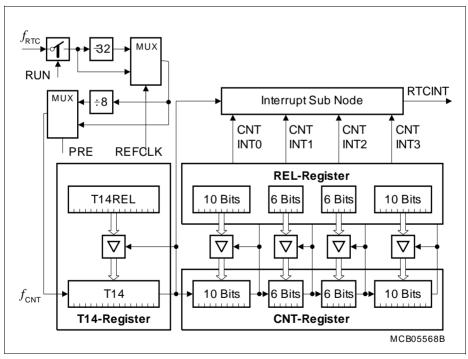

| 3.10  | Real Time Clock                                   |

| 3.11  | A/D Converters                                    |

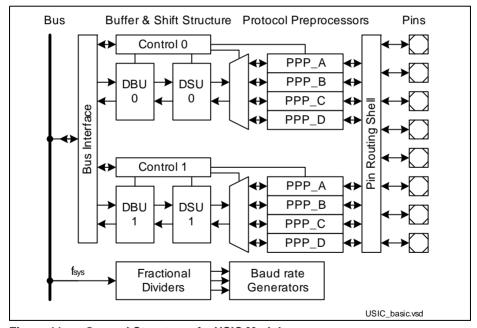

| 3.12  | Universal Serial Interface Channel Modules (USIC) |

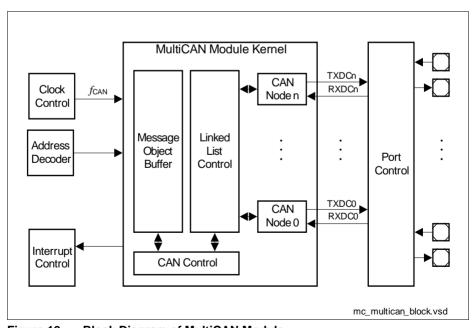

| 3.13  | MultiCAN Module                                   |

| 3.14  | System Timer                                      |

| 3.15  | Watchdog Timer 52                                 |

| 3.16  | Clock Generation                                  |

| 3.17  | Parallel Ports                                    |

| 3.18  | Instruction Set Summary                           |

| 4     | Electrical Parameters 58                          |

| 4.1   | General Parameters 58                             |

| 4.1.1 | Operating Conditions                              |

| 4.2   | Voltage Range definitions 61                      |

| 4.2.1 | Parameter Interpretation 61                       |

| 4.3   | DC Parameters 62                                  |

| 4.3.1 | DC Parameters for Upper Voltage Area 64           |

| 4.3.2 | DC Parameters for Lower Voltage Area              |

| 4.3.3 | Power Consumption 68                              |

| 4.4   | Analog/Digital Converter Parameters               |

| 4.5   | System Parameters                                 |

| 4.6   | Flash Memory Parameters 79                        |

| 4.7   | AC Parameters 81                                  |

# XC2336B XC2000 Family / Value Line

#### **Table of Contents**

| 4.7.1   | Testing Waveforms 81                              |   |

|---------|---------------------------------------------------|---|

| 4.7.2   | Definition of Internal Timing                     | 2 |

| 4.7.2.1 | Phase Locked Loop (PLL)                           | 3 |

| 4.7.2.2 | Wakeup Clock 86                                   | ò |

| 4.7.2.3 | Selecting and Changing the Operating Frequency 86 | j |

| 4.7.3   | External Clock Input Parameters                   | 7 |

| 4.7.4   | Pad Properties                                    | ) |

| 4.7.5   | Synchronous Serial Interface Timing               | 3 |

| 4.7.6   | Debug Interface Timing                            | 7 |

| 5       | Package and Reliability                           | 3 |

| 5.1     | Packaging                                         | 3 |

| 5.2     | Thermal Considerations                            | 5 |

| 5.3     | Quality Declarations                              | ò |

16/32-Bit Single-Chip Microcontroller with 32-Bit Performance XC2336B (XC2000 Family)

## 1 Summary of Features

For a quick overview and easy reference, the features of the XC2336B are summarized here.

- High-performance CPU with five-stage pipeline and MPU

- 12.5 ns instruction cycle @ 80 MHz CPU clock (single-cycle execution)

- One-cycle 32-bit addition and subtraction with 40-bit result

- One-cycle multiplication (16 × 16 bit)

- Background division (32 / 16 bit) in 21 cycles

- One-cycle multiply-and-accumulate (MAC) instructions

- Enhanced Boolean bit manipulation facilities

- Zero-cycle jump execution

- Additional instructions to support HLL and operating systems

- Register-based design with multiple variable register banks

- Fast context switching support with two additional local register banks

- 16 Mbytes total linear address space for code and data

- 1,024 Bytes on-chip special function register area (C166 Family compatible)

- Integrated Memory Protection Unit (MPU)

- Interrupt system with 16 priority levels providing 96 interrupt nodes

- Selectable external inputs for interrupt generation and wake-up

- Fastest sample-rate 12.5 ns

- Eight-channel interrupt-driven single-cycle data transfer with Peripheral Event Controller (PEC), 24-bit pointers cover total address space

- Clock generation from internal or external clock sources, using on-chip PLL or prescaler

- Hardware CRC-Checker with Programmable Polynomial to Supervise On-Chip Memory Areas

- · On-chip memory modules

- 8 Kbytes on-chip stand-by RAM (SBRAM)

- 2 Kbytes on-chip dual-port RAM (DPRAM)

- Up to 16 Kbytes on-chip data SRAM (DSRAM)

- Up to 16 Kbytes on-chip program/data SRAM (PSRAM)

- Up to 320 Kbytes on-chip program memory (Flash memory)

- Memory content protection through Error Correction Code (ECC)

- On-Chip Peripheral Modules

- Two synchronizable A/D Converters with up to 9 channels, 10-bit resolution, conversion time below 1 μs, optional data preprocessing (data reduction, range check), broken wire detection

- 16-channel general purpose capture/compare unit (CC2)

- Two capture/compare units for flexible PWM signal generation (CCU6x)

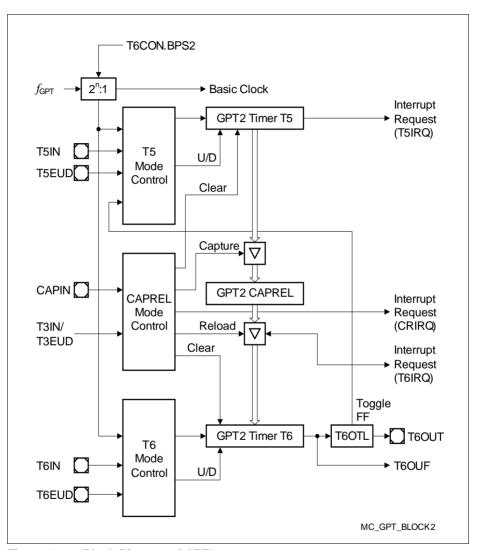

- Multi-functional general purpose timer unit with 5 timers

- 4 serial interface channels to be used as UART, LIN, high-speed synchronous channel (SPI/QSPI), IIC bus interface (10-bit addressing, 400 kbit/s), IIS interface

- On-chip MultiCAN interface (Rev. 2.0B active) with 64 message objects (Full CAN/Basic CAN) on up to 2 CAN nodes and gateway functionality

- On-chip system timer and on-chip real time clock

- Single power supply from 3.0 V to 5.5 V

- Power reduction and wake-up modes

- Programmable watchdog timer and oscillator watchdog

- Up to 40 general purpose I/O lines

- On-chip bootstrap loaders

- Supported by a full range of development tools including C compilers, macroassembler packages, emulators, evaluation boards, HLL debuggers, simulators, logic analyzer disassemblers, programming boards

- On-chip debug support via Device Access Port (DAP) or JTAG interface

- 64-pin Green LQFP package, 0.5 mm (19.7 mil) pitch

## **Ordering Information**

The ordering code for an Infineon microcontroller provides an exact reference to a specific product. This ordering code identifies:

- the derivative itself, i.e. its function set, the temperature range, and the supply voltage

- the temperature range:

- SAF-...: -40°C to 85°C

- SAH-...: -40°C to 110°C

- SAK-...: -40°C to 125°C

- the package and the type of delivery.

For ordering codes for the XC2336B please contact your sales representative or local distributor.

This document describes several derivatives of the XC2336B group:

Basic Device Types are readily available and

**Special Device Types** are only available on request.

As this document refers to all of these derivatives, some descriptions may not apply to a specific product, in particular to the special device types.

For simplicity the term XC2336B is used for all derivatives throughout this document.

## 1.1 Basic Device Types

Basic device types are available and can be ordered through Infineon's direct and/or distribution channels.

Table 1 Synopsis of XC2336B Basic Device Types

| Derivative <sup>1)</sup> | Flash<br>Memory <sup>2)</sup> |                        | Capt./Comp.<br>Modules <sup>4)</sup> | ADC <sup>5)</sup><br>Chan. | Interfaces <sup>5)</sup>      |

|--------------------------|-------------------------------|------------------------|--------------------------------------|----------------------------|-------------------------------|

| XC2336B-40FxLR           | 320 Kbytes                    | 16 Kbytes<br>16 Kbytes |                                      | 7 + 2                      | 2 CAN Node,<br>4 Serial Chan. |

<sup>1)</sup> x is a placeholder for available speed grade in MHz.

<sup>2)</sup> Specific information about the on-chip Flash memory in Table 3.

<sup>3)</sup> All derivatives additionally provide 8 Kbytes SBRAM and 2 Kbytes DPRAM.

<sup>4)</sup> Due to bonding limitations in the XC2336B devices only a subset of the CCU61 features can be used. The module has the T12 and T13 timer inputs and no outputs connected. Therefore only CCU61 timers can be triggered from external. This can typically be used for periodic triggering of ADCs.

Specific information about the available channels in Table 5.

Analog input channels are listed for each Analog/Digital Converter module separately (ADC0 + ADC1).

## 1.2 Special Device Types

Special device types are only available for high-volume applications on request.

Table 2 Synopsis of XC2336B Special Device Types

| Derivative <sup>1)</sup> | Flash<br>Memory <sup>2)</sup> | PSRAM<br>DSRAM <sup>3)</sup> | Capt./Comp.<br>Modules <sup>4)</sup> | ADC <sup>5)</sup> Chan. | Interfaces <sup>5)</sup>      |

|--------------------------|-------------------------------|------------------------------|--------------------------------------|-------------------------|-------------------------------|

| XC2336B-24FxL            | 192 Kbytes                    | 8 Kbytes<br>16 Kbytes        | CC2<br>CCU60/1                       | 7 + 2                   | 2 CAN Node,<br>4 Serial Chan. |

| XC2336B-40FxL            | 320 Kbytes                    | 16 Kbytes<br>16 Kbytes       | CC2<br>CCU60/1                       | 7 + 2                   | 2 CAN Node,<br>4 Serial Chan. |

<sup>1)</sup> x is a placeholder for available speed grade in MHz.

Specific information about the available channels in Table 5.

Analog input channels are listed for each Analog/Digital Converter module separately (ADC0 + ADC1).

<sup>2)</sup> Specific information about the on-chip Flash memory in Table 3.

<sup>3)</sup> All derivatives additionally provide 8 Kbytes SBRAM and 2 Kbytes DPRAM.

<sup>4)</sup> Due to bonding limitations in the XC2336B devices only a subset of the CCU61 features can be used. The module has the T12 and T13 timer inputs and no outputs connected. Therefore only CCU61 timers can be triggered from external. This can typically be used for periodic triggering of ADCs.

#### 1.3 Definition of Feature Variants

The XC2336B types are offered with several Flash memory sizes. **Table 3** and **Table 4** describe the location of the available Flash memory.

Table 3 Continuous Flash Memory Ranges

| Total Flash Size | 1st Range <sup>1)</sup>                      | 2nd Range                                    | 3rd Range                                    |

|------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|

| 320 Kbytes       | C0'0000 <sub>H</sub><br>C0'EFFF <sub>H</sub> | C1'0000 <sub>H</sub><br>C4'FFFF <sub>H</sub> | n.a.                                         |

|                  |                                              | C1'0000 <sub>H</sub><br>C1'FFFF <sub>H</sub> | C4'0000 <sub>H</sub><br>C4'FFFF <sub>H</sub> |

<sup>1)</sup> The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

Table 4 Flash Memory Module Allocation (in Kbytes)

| Total Flash Size | Flash 0 <sup>1)</sup> | Flash 1 |

|------------------|-----------------------|---------|

| 320              | 256                   | 64      |

| 192              | 128                   | 64      |

<sup>1)</sup> The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

The XC2336B types are offered with different interface options. **Table 5** lists the available channels for each option.

Table 5 Interface Channel Association

| Total Number      | Available Channels / Message Objects |

|-------------------|--------------------------------------|

| 7 ADC0 channels   | CH0, CH2, Ch4, CH8, CH10, CH13, CH15 |

| 2 ADC1 channels   | CH0, CH4                             |

| 2 CAN nodes       | CAN0, CAN1<br>64 message objects     |

| 4 serial channels | U0C0, U0C1, U1C0, U1C1               |

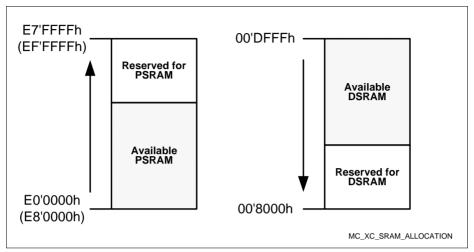

The XC2336B types are offered with several SRAM memory sizes. Figure 1 shows the allocation rules for PSRAM and DSRAM. Note that the rules differ:

- PSRAM allocation starts from the lower address

- DSRAM allocation starts from the higher address

For example 8 Kbytes of PSRAM will be allocated at E0'0000h-E0'1FFFh and 8 Kbytes of DSRAM will be at 00'C000h-00'DFFFh.

Figure 1 SRAM Allocation

#### 2 General Device Information

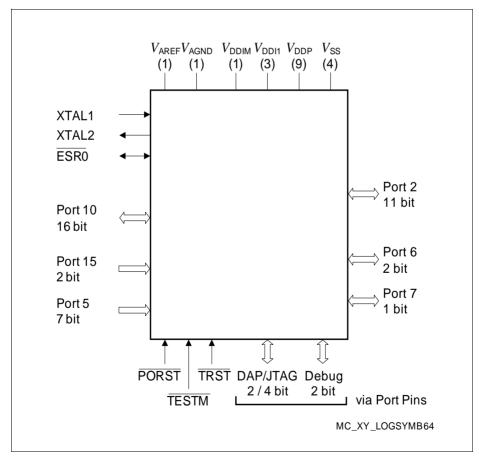

The XC2336B series (16/32-Bit Single-Chip Microcontroller with 32-Bit Performance) is a part of the Infineon XC2000 Family of full-feature single-chip CMOS microcontrollers. These devices extend the functionality and performance of the C166 Family in terms of instructions (MAC unit), peripherals, and speed. They combine high CPU performance (up to 80 million instructions per second) with extended peripheral functionality and enhanced IO capabilities. Optimized peripherals can be adapted flexibly to meet the application requirements. These derivatives utilize clock generation via PLL and internal or external clock sources. On-chip memory modules include program Flash, program RAM, and data RAM.

Figure 2 XC2336B Logic Symbol

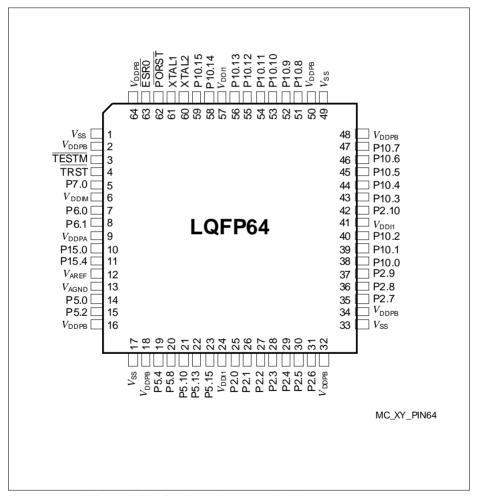

## 2.1 Pin Configuration and Definition

The pins of the XC2336B are described in detail in **Table 6**, which includes all alternate functions. For further explanations please refer to the footnotes at the end of the table. The following figure summarizes all pins, showing their locations on the four sides of the package.

Figure 3 XC2336B Pin Configuration (top view)

#### **Key to Pin Definitions**

- Ctrl.: The output signal for a port pin is selected by bit field PC in the associated register Px\_IOCRy. Output O0 is selected by setting the respective bit field PC to 1x00<sub>B</sub>, output O1 is selected by 1x01<sub>B</sub>, etc.

Output signal OH is controlled by hardware.

- **Type**: Indicates the pad type and its power supply domain (A, B, M, 1).

- St: Standard pad

- Sp: Special pad e.g. XTALx

- DP: Double pad can be used as standard or high speed pad

- In: Input only pad

- PS: Power supply pad

Table 6 Pin Definitions and Functions

| Pin | Symbol | Ctrl.      | Туре | Function                                                                                                                                                                                                                                                                                                                               |

|-----|--------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | TESTM  | I          | In/B | $\begin{tabular}{ll} \textbf{Testmode Enable} \\ \textbf{Enables factory test modes, must be held HIGH for} \\ \textbf{normal operation (connect to $V_{\rm DDPB}$)}. \\ \textbf{An internal pull-up device will hold this pin high} \\ \textbf{when nothing is driving it.} \\ \end{tabular}$                                         |

| 4   | TRST   | 1          | In/B | Test-System Reset Input For normal system operation, pin TRST should be held low. A high level at this pin at the rising edge of PORST activates the XC2336B's debug system. In this case, pin TRST must be driven low once to reset the debug system. An internal pull-down device will hold this pin low when nothing is driving it. |

| 5   | P7.0   | O0 / I     | St/B | Bit 0 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                                                          |

|     | T3OUT  | 01         | St/B | GPT12E Timer T3 Toggle Latch Output                                                                                                                                                                                                                                                                                                    |

|     | T6OUT  | O2         | St/B | GPT12E Timer T6 Toggle Latch Output                                                                                                                                                                                                                                                                                                    |

|     | TDO_A  | OH /<br>IH | St/B | JTAG Test Data Output / DAP1 Input/Output If DAP pos. 0 or 2 is selected during start-up, an internal pull-down device will hold this pin low when nothing is driving it.                                                                                                                                                              |

|     | ESR2_1 | I          | St/B | ESR2 Trigger Input 1                                                                                                                                                                                                                                                                                                                   |

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.  | Туре | Function                                       |

|-----|------------------|--------|------|------------------------------------------------|

| 7   | P6.0             | O0 / I | DA/A | Bit 0 of Port 6, General Purpose Input/Output  |

|     | EMUX0            | O1     | DA/A | External Analog MUX Control Output 0 (ADC0)    |

|     | BRKOUT           | О3     | DA/A | OCDS Break Signal Output                       |

|     | ADCx_REQG<br>TyG | I      | DA/A | External Request Gate Input for ADC0/1         |

|     | U1C1_DX0E        | I      | DA/A | USIC1 Channel 1 Shift Data Input               |

| 8   | P6.1             | O0 / I | DA/A | Bit 1 of Port 6, General Purpose Input/Output  |

|     | EMUX1            | O1     | DA/A | External Analog MUX Control Output 1 (ADC0)    |

|     | T3OUT            | O2     | DA/A | GPT12E Timer T3 Toggle Latch Output            |

|     | U1C1_DOUT        | О3     | DA/A | USIC1 Channel 1 Shift Data Output              |

|     | ADCx_REQT<br>RyE | I      | DA/A | External Request Trigger Input for ADC0/1      |

|     | ESR1_6           | I      | DA/A | ESR1 Trigger Input 6                           |

| 10  | P15.0            | I      | In/A | Bit 0 of Port 15, General Purpose Input        |

|     | ADC1_CH0         | I      | In/A | Analog Input Channel 0 for ADC1                |

| 11  | P15.4            | I      | In/A | Bit 4 of Port 15, General Purpose Input        |

|     | ADC1_CH4         | I      | In/A | Analog Input Channel 4 for ADC1                |

|     | T6INA            | I      | In/A | GPT12E Timer T6 Count/Gate Input               |

| 12  | $V_{AREF}$       | -      | PS/A | Reference Voltage for A/D Converters ADC0/1    |

| 13  | $V_{AGND}$       | -      | PS/A | Reference Ground for A/D Converters ADC0/1     |

| 14  | P5.0             | I      | In/A | Bit 0 of Port 5, General Purpose Input         |

|     | ADC0_CH0         | I      | In/A | Analog Input Channel 0 for ADC0                |

| 15  | P5.2             | I      | In/A | Bit 2 of Port 5, General Purpose Input         |

|     | ADC0_CH2         | I      | In/A | Analog Input Channel 2 for ADC0                |

|     | TDI_A            | I      | In/A | JTAG Test Data Input                           |

| 19  | P5.4             | I      | In/A | Bit 4 of Port 5, General Purpose Input         |

|     | ADC0_CH4         | I      | In/A | Analog Input Channel 4 for ADC0                |

|     | T3EUDA           | I      | In/A | GPT12E Timer T3 External Up/Down Control Input |

|     | TMS_A            | I      | In/A | JTAG Test Mode Selection Input                 |

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.  | Туре | Function                                       |

|-----|------------------|--------|------|------------------------------------------------|

| 20  | P5.8             | I      | In/A | Bit 8 of Port 5, General Purpose Input         |

|     | ADC0_CH8         | I      | In/A | Analog Input Channel 8 for ADC0                |

|     | ADC1_CH8         | I      | In/A | Analog Input Channel 8 for ADC1                |

|     | CCU6x_T12H<br>RC | I      | In/A | External Run Control Input for T12 of CCU60/1  |

|     | CCU6x_T13H<br>RC | I      | In/A | External Run Control Input for T13 of CCU60/1  |

| 21  | P5.10            | I      | In/A | Bit 10 of Port 5, General Purpose Input        |

|     | ADC0_CH10        | I      | In/A | Analog Input Channel 10 for ADC0               |

|     | ADC1_CH10        | I      | In/A | Analog Input Channel 10 for ADC1               |

|     | BRKIN_A          | I      | In/A | OCDS Break Signal Input                        |

|     | CCU61_T13<br>HRA | I      | In/A | External Run Control Input for T13 of CCU61    |

| 22  | P5.13            | I      | In/A | Bit 13 of Port 5, General Purpose Input        |

|     | ADC0_CH13        | I      | In/A | Analog Input Channel 13 for ADC0               |

| 23  | P5.15            | I      | In/A | Bit 15 of Port 5, General Purpose Input        |

|     | ADC0_CH15        | I      | In/A | Analog Input Channel 15 for ADC0               |

| 25  | P2.0             | O0 / I | St/B | Bit 0 of Port 2, General Purpose Input/Output  |

|     | RxDC0C           | I      | St/B | CAN Node 0 Receive Data Input                  |

|     | T5INB            | I      | St/B | GPT12E Timer T5 Count/Gate Input               |

| 26  | P2.1             | O0 / I | St/B | Bit 1 of Port 2, General Purpose Input/Output  |

|     | TxDC0            | O1     | St/B | CAN Node 0 Transmit Data Output                |

|     | T5EUDB           | I      | St/B | GPT12E Timer T5 External Up/Down Control Input |

|     | ESR1_5           | I      | St/B | ESR1 Trigger Input 5                           |

| 27  | P2.2             | O0 / I | St/B | Bit 2 of Port 2, General Purpose Input/Output  |

|     | TxDC1            | O1     | St/B | CAN Node 1 Transmit Data Output                |

|     | ESR2_5           | I      | St/B | ESR2 Trigger Input 5                           |

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.  | Туре | Function                                      |

|-----|------------------|--------|------|-----------------------------------------------|

| 28  | P2.3             | O0 / I | St/B | Bit 3 of Port 2, General Purpose Input/Output |

|     | U0C0_DOUT        | O1     | St/B | USIC0 Channel 0 Shift Data Output             |

|     | CC2_CC16         | O3 / I | St/B | CAPCOM2 CC16IO Capture Inp./ Compare Out.     |

|     | ESR2_0           | I      | St/B | ESR2 Trigger Input 0                          |

|     | U0C0_DX0E        | I      | St/B | USIC0 Channel 0 Shift Data Input              |

|     | U0C1_DX0D        | I      | St/B | USIC0 Channel 1 Shift Data Input              |

|     | RxDC0A           | I      | St/B | CAN Node 0 Receive Data Input                 |

| 29  | P2.4             | O0 / I | St/B | Bit 4 of Port 2, General Purpose Input/Output |

|     | U0C1_DOUT        | O1     | St/B | USIC0 Channel 1 Shift Data Output             |

|     | TxDC0            | O2     | St/B | CAN Node 0 Transmit Data Output               |

|     | CC2_CC17         | O3 / I | St/B | CAPCOM2 CC17IO Capture Inp./ Compare Out.     |

|     | ESR1_0           | I      | St/B | ESR1 Trigger Input 0                          |

|     | U0C0_DX0F        | I      | St/B | USIC0 Channel 0 Shift Data Input              |

|     | RxDC1A           | I      | St/B | CAN Node 1 Receive Data Input                 |

| 30  | P2.5             | O0 / I | St/B | Bit 5 of Port 2, General Purpose Input/Output |

|     | U0C0_SCLK<br>OUT | 01     | St/B | USIC0 Channel 0 Shift Clock Output            |

|     | TxDC0            | O2     | St/B | CAN Node 0 Transmit Data Output               |

|     | CC2_CC18         | O3 / I | St/B | CAPCOM2 CC18IO Capture Inp./ Compare Out.     |

|     | U0C0_DX1D        | I      | St/B | USIC0 Channel 0 Shift Clock Input             |

|     | ESR1_10          | I      | St/B | ESR1 Trigger Input 10                         |

| 31  | P2.6             | O0 / I | St/B | Bit 6 of Port 2, General Purpose Input/Output |

|     | U0C0_SELO<br>0   | O1     | St/B | USIC0 Channel 0 Select/Control 0 Output       |

|     | U0C1_SELO<br>1   | O2     | St/B | USIC0 Channel 1 Select/Control 1 Output       |

|     | CC2_CC19         | O3 / I | St/B | CAPCOM2 CC19IO Capture Inp./ Compare Out.     |

|     | U0C0_DX2D        | I      | St/B | USIC0 Channel 0 Shift Control Input           |

|     | RxDC0D           | I      | St/B | CAN Node 0 Receive Data Input                 |

|     | ESR2_6           | I      | St/B | ESR2 Trigger Input 6                          |

Table 6 Pin Definitions and Functions (cont'd)

|     | ic o i ili bellilitions and |        |      | anotione (cont a)                                                                                                                                                                                                                                                             |  |

|-----|-----------------------------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin | Symbol                      | Ctrl.  | Type | Function                                                                                                                                                                                                                                                                      |  |

| 35  | P2.7                        | O0 / I | St/B | Bit 7 of Port 2, General Purpose Input/Output                                                                                                                                                                                                                                 |  |

|     | U0C1_SELO<br>0              | O1     | St/B | USIC0 Channel 1 Select/Control 0 Output                                                                                                                                                                                                                                       |  |

|     | U0C0_SELO<br>1              | O2     | St/B | USIC0 Channel 0 Select/Control 1 Output                                                                                                                                                                                                                                       |  |

|     | CC2_CC20                    | O3 / I | St/B | CAPCOM2 CC20IO Capture Inp./ Compare Out.                                                                                                                                                                                                                                     |  |

|     | U0C1_DX2C                   | I      | St/B | USIC0 Channel 1 Shift Control Input                                                                                                                                                                                                                                           |  |

|     | RxDC1C                      | I      | St/B | CAN Node 1 Receive Data Input                                                                                                                                                                                                                                                 |  |

|     | ESR2_7                      | I      | St/B | ESR2 Trigger Input 7                                                                                                                                                                                                                                                          |  |

| 36  | P2.8                        | O0 / I | DP/B | Bit 8 of Port 2, General Purpose Input/Output                                                                                                                                                                                                                                 |  |

|     | U0C1_SCLK<br>OUT            | O1     | DP/B | USIC0 Channel 1 Shift Clock Output                                                                                                                                                                                                                                            |  |

|     | EXTCLK                      | O2     | DP/B | Programmable Clock Signal Output                                                                                                                                                                                                                                              |  |

|     | CC2_CC21                    | O3 / I | DP/B | CAPCOM2 CC21IO Capture Inp./ Compare Out.                                                                                                                                                                                                                                     |  |

|     | U0C1_DX1D                   | I      | DP/B | USIC0 Channel 1 Shift Clock Input                                                                                                                                                                                                                                             |  |

| 37  | P2.9                        | O0 / I | St/B | Bit 9 of Port 2, General Purpose Input/Output                                                                                                                                                                                                                                 |  |

|     | U0C1_DOUT                   | 01     | St/B | USIC0 Channel 1 Shift Data Output                                                                                                                                                                                                                                             |  |

|     | TxDC1                       | O2     | St/B | CAN Node 1 Transmit Data Output                                                                                                                                                                                                                                               |  |

|     | CC2_CC22                    | O3 / I | St/B | CAPCOM2 CC22IO Capture Inp./ Compare Out.                                                                                                                                                                                                                                     |  |

|     | CLKIN1                      | I      | St/B | Clock Signal Input 1                                                                                                                                                                                                                                                          |  |

|     | TCK_A                       | IH     | St/B | DAPO/JTAG Clock Input  If JTAG pos. A is selected during start-up, an internal pull-up device will hold this pin high when nothing is driving it.  If DAP pos. 0 is selected during start-up, an internal pull-down device will hold this pin low when nothing is driving it. |  |

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.  | Туре | Function                                       |  |

|-----|-------------------|--------|------|------------------------------------------------|--|

| 38  | P10.0             | O0 / I | St/B | Bit 0 of Port 10, General Purpose Input/Output |  |

|     | U0C1_DOUT         | 01     | St/B | USIC0 Channel 1 Shift Data Output              |  |

|     | CCU60_CC6         | O2     | St/B | CCU60 Channel 0 Output                         |  |

|     | CCU60_CC6<br>0INA | I      | St/B | CCU60 Channel 0 Input                          |  |

|     | ESR1_2            | I      | St/B | ESR1 Trigger Input 2                           |  |

|     | U0C0_DX0A         | I      | St/B | USIC0 Channel 0 Shift Data Input               |  |

|     | U0C1_DX0A         | I      | St/B | USIC0 Channel 1 Shift Data Input               |  |

| 39  | P10.1             | O0 / I | St/B | Bit 1 of Port 10, General Purpose Input/Output |  |

|     | U0C0_DOUT         | 01     | St/B | USIC0 Channel 0 Shift Data Output              |  |

|     | CCU60_CC6         | O2     | St/B | CCU60 Channel 1 Output                         |  |

|     | CCU60_CC6<br>1INA | I      | St/B | CCU60 Channel 1 Input                          |  |

|     | U0C0_DX1A         | I      | St/B | USIC0 Channel 0 Shift Clock Input              |  |

|     | U0C0_DX0B         | I      | St/B | USIC0 Channel 0 Shift Data Input               |  |

| 40  | P10.2             | O0 / I | St/B | Bit 2 of Port 10, General Purpose Input/Output |  |

|     | U0C0_SCLK<br>OUT  | O1     | St/B | USIC0 Channel 0 Shift Clock Output             |  |

|     | CCU60_CC6         | O2     | St/B | CCU60 Channel 2 Output                         |  |

|     | CCU60_CC6<br>2INA | I      | St/B | CCU60 Channel 2 Input                          |  |

|     | U0C0_DX1B         | I      | St/B | USIC0 Channel 0 Shift Clock Input              |  |

| 42  | P2.10             | O0 / I | St/B | Bit 10 of Port 2, General Purpose Input/Output |  |

|     | U0C1_DOUT         | 01     | St/B | USIC0 Channel 1 Shift Data Output              |  |

|     | U0C0_SELO<br>3    | O2     | St/B | USIC0 Channel 0 Select/Control 3 Output        |  |

|     | CC2_CC23          | O3 / I | St/B | CAPCOM2 CC23IO Capture Inp./ Compare Out.      |  |

|     | U0C1_DX0E         | I      | St/B | USIC0 Channel 1 Shift Data Input               |  |

|     | CAPINA            | I      | St/B | GPT12E Register CAPREL Capture Input           |  |

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.  | Туре | Function                                       |  |

|-----|------------------|--------|------|------------------------------------------------|--|

| 43  | P10.3            | O0 / I | St/B | Bit 3 of Port 10, General Purpose Input/Output |  |

|     | CCU60_COU<br>T60 | O2     | St/B | CCU60 Channel 0 Output                         |  |

|     | U0C0_DX2A        | I      | St/B | USIC0 Channel 0 Shift Control Input            |  |

|     | U0C1_DX2A        | I      | St/B | USIC0 Channel 1 Shift Control Input            |  |

| 44  | P10.4            | O0 / I | St/B | Bit 4 of Port 10, General Purpose Input/Output |  |

|     | U0C0_SELO<br>3   | O1     | St/B | USIC0 Channel 0 Select/Control 3 Output        |  |

|     | CCU60_COU<br>T61 | O2     | St/B | CCU60 Channel 1 Output                         |  |

|     | U0C0_DX2B        | I      | St/B | USIC0 Channel 0 Shift Control Input            |  |

|     | U0C1_DX2B        | I      | St/B | USIC0 Channel 1 Shift Control Input            |  |

|     | ESR1_9           | I      | St/B | ESR1 Trigger Input 9                           |  |

| 45  | P10.5            | O0 / I | St/B | Bit 5 of Port 10, General Purpose Input/Output |  |

|     | U0C1_SCLK<br>OUT | O1     | St/B | USIC0 Channel 1 Shift Clock Output             |  |

|     | CCU60_COU<br>T62 | O2     | St/B | CCU60 Channel 2 Output                         |  |

|     | U0C1_DX1B        | I      | St/B | USIC0 Channel 1 Shift Clock Input              |  |

| 46  | P10.6            | O0 / I | St/B | Bit 6 of Port 10, General Purpose Input/Output |  |

|     | U0C0_DOUT        | 01     | St/B | USIC0 Channel 0 Shift Data Output              |  |

|     | U1C0_SELO<br>0   | О3     | St/B | USIC1 Channel 0 Select/Control 0 Output        |  |

|     | U0C0_DX0C        | I      | St/B | USIC0 Channel 0 Shift Data Input               |  |

|     | U1C0_DX2D        | I      | St/B | USIC1 Channel 0 Shift Control Input            |  |

|     | CCU60_CTR<br>APA | I      | St/B | CCU60 Emergency Trap Input                     |  |

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                    |  |  |

|-----|-------------------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 47  | P10.7             | O0 / I | St/B | Bit 7 of Port 10, General Purpose Input/Output                                                                                                                                                                                                                              |  |  |

|     | U0C1_DOUT         | 01     | St/B | USIC0 Channel 1 Shift Data Output                                                                                                                                                                                                                                           |  |  |

|     | CCU60_COU<br>T63  | O2     | St/B | CCU60 Channel 3 Output                                                                                                                                                                                                                                                      |  |  |

|     | U0C1_DX0B         | I      | St/B | USIC0 Channel 1 Shift Data Input                                                                                                                                                                                                                                            |  |  |

|     | CCU60_CCP<br>OS0A | I      | St/B | CCU60 Position Input 0                                                                                                                                                                                                                                                      |  |  |

|     | T4INB             | I      | St/B | GPT12E Timer T4 Count/Gate Input                                                                                                                                                                                                                                            |  |  |

| 51  | P10.8             | O0 / I | St/B | Bit 8 of Port 10, General Purpose Input/Output                                                                                                                                                                                                                              |  |  |

|     | U0C0_MCLK<br>OUT  | O1     | St/B | USIC0 Channel 0 Master Clock Output                                                                                                                                                                                                                                         |  |  |

|     | U0C1_SELO<br>0    | O2     | St/B | USIC0 Channel 1 Select/Control 0 Output                                                                                                                                                                                                                                     |  |  |

|     | CCU60_CCP<br>OS1A | I      | St/B | CCU60 Position Input 1                                                                                                                                                                                                                                                      |  |  |

|     | U0C0_DX1C         | I      | St/B | USIC0 Channel 0 Shift Clock Input                                                                                                                                                                                                                                           |  |  |

|     | BRKIN_B           | I      | St/B | OCDS Break Signal Input                                                                                                                                                                                                                                                     |  |  |

|     | T3EUDB            | I      | St/B | GPT12E Timer T3 External Up/Down Control Input                                                                                                                                                                                                                              |  |  |

| 52  | P10.9             | O0 / I | St/B | Bit 9 of Port 10, General Purpose Input/Output                                                                                                                                                                                                                              |  |  |

|     | U0C0_SELO<br>4    | O1     | St/B | USIC0 Channel 0 Select/Control 4 Output                                                                                                                                                                                                                                     |  |  |

|     | U0C1_MCLK<br>OUT  | O2     | St/B | USIC0 Channel 1 Master Clock Output                                                                                                                                                                                                                                         |  |  |

|     | CCU60_CCP<br>OS2A | I      | St/B | CCU60 Position Input 2                                                                                                                                                                                                                                                      |  |  |

|     | TCK_B             | IH     | St/B | DAP0/JTAG Clock Input If JTAG pos. B is selected during start-up, an internal pull-up device will hold this pin high when nothing is driving it. If DAP pos. 1 is selected during start-up, an internal pull-down device will hold this pin low when nothing is driving it. |  |  |

|     | T3INB             | I      | St/B | GPT12E Timer T3 Count/Gate Input                                                                                                                                                                                                                                            |  |  |

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.      | Туре | Function                                                                                                                                                             |  |

|-----|------------------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 53  | P10.10           | O0 / I     | St/B | Bit 10 of Port 10, General Purpose Input/Output                                                                                                                      |  |

|     | U0C0_SELO<br>0   | O1         | St/B | USIC0 Channel 0 Select/Control 0 Output                                                                                                                              |  |

|     | CCU60_COU<br>T63 | O2         | St/B | CCU60 Channel 3 Output                                                                                                                                               |  |

|     | U0C0_DX2C        | I          | St/B | USIC0 Channel 0 Shift Control Input                                                                                                                                  |  |

|     | U0C1_DX1A        | I          | St/B | USIC0 Channel 1 Shift Clock Input                                                                                                                                    |  |

|     | TDI_B            | IH         | St/B | JTAG Test Data Input If JTAG pos. B is selected during start-up, an internal pull-up device will hold this pin high when nothing is driving it.                      |  |

| 54  | P10.11           | O0 / I     | St/B | Bit 11 of Port 10, General Purpose Input/Output                                                                                                                      |  |

|     | U1C0_SCLK<br>OUT | O1         | St/B | USIC1 Channel 0 Shift Clock Output                                                                                                                                   |  |

|     | BRKOUT           | O2         | St/B | OCDS Break Signal Output                                                                                                                                             |  |

|     | U1C0_DX1D        | I          | St/B | USIC1 Channel 0 Shift Clock Input                                                                                                                                    |  |

|     | TMS_B            | IH         | St/B | JTAG Test Mode Selection Input If JTAG pos. B is selected during start-up, an internal pull-up device will hold this pin high when nothing is driving it.            |  |

| 55  | P10.12           | O0 / I     | St/B | Bit 12 of Port 10, General Purpose Input/Output                                                                                                                      |  |

|     | U1C0_DOUT        | 01         | St/B | USIC1 Channel 0 Shift Data Output                                                                                                                                    |  |

|     | TDO_B            | OH /<br>IH | St/B | JTAG Test Data Output / DAP1 Input/Output If DAP pos. 1 is selected during start-up, an internal pull-down device will hold this pin low when nothing is driving it. |  |

|     | U1C0_DX0C        | I          | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                     |  |

|     | U1C0_DX1E        | I          | St/B | USIC1 Channel 0 Shift Clock Input                                                                                                                                    |  |

| 56  | P10.13           | O0 / I     | St/B | Bit 13 of Port 10, General Purpose Input/Output                                                                                                                      |  |

|     | U1C0_DOUT        | 01         | St/B | USIC1 Channel 0 Shift Data Output                                                                                                                                    |  |

|     | U1C0_SELO<br>3   | О3         | St/B | USIC1 Channel 0 Select/Control 3 Output                                                                                                                              |  |

|     | U1C0_DX0D        | 1          | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                     |  |

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol         | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                                             |  |  |

|-----|----------------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 58  | P10.14         | O0 / I | St/B | Bit 14 of Port 10, General Purpose Input/Output                                                                                                                                                                                                                                                                      |  |  |

|     | U1C0_SELO<br>1 | O1     | St/B | USIC1 Channel 0 Select/Control 1 Output                                                                                                                                                                                                                                                                              |  |  |

|     | U0C1_DOUT      | O2     | St/B | USIC0 Channel 1 Shift Data Output                                                                                                                                                                                                                                                                                    |  |  |

|     | ESR2_2         | I      | St/B | ESR2 Trigger Input 2                                                                                                                                                                                                                                                                                                 |  |  |

|     | U0C1_DX0C      | I      | St/B | USIC0 Channel 1 Shift Data Input                                                                                                                                                                                                                                                                                     |  |  |

| 59  | P10.15         | O0 / I | St/B | Bit 15 of Port 10, General Purpose Input/Output                                                                                                                                                                                                                                                                      |  |  |

|     | U1C0_SELO<br>2 | O1     | St/B | USIC1 Channel 0 Select/Control 2 Output                                                                                                                                                                                                                                                                              |  |  |

|     | U0C1_DOUT      | O2     | St/B | USIC0 Channel 1 Shift Data Output                                                                                                                                                                                                                                                                                    |  |  |

|     | U1C0_DOUT      | О3     | St/B | USIC1 Channel 0 Shift Data Output                                                                                                                                                                                                                                                                                    |  |  |

|     | U0C1_DX1C      | I      | St/B | USIC0 Channel 1 Shift Clock Input                                                                                                                                                                                                                                                                                    |  |  |

| 60  | XTAL2          | 0      | Sp/M | Crystal Oscillator Amplifier Output                                                                                                                                                                                                                                                                                  |  |  |

| 61  | XTAL1          | I      | Sp/M | Crystal Oscillator Amplifier Input To clock the device from an external source, drive XTAL1, while leaving XTAL2 unconnected. Voltages on XTAL1 must comply to the core supply voltage $V_{\rm DDIM}$ .                                                                                                              |  |  |

|     | ESR2_9         | I      | St/B | ESR2 Trigger Input 9                                                                                                                                                                                                                                                                                                 |  |  |

| 62  | PORST          | I      | In/B | Power On Reset Input A low level at this pin resets the XC2336B completely. A spike filter suppresses input pulses <10 ns. Input pulses >100 ns safely pass the filter. The minimum duration for a safe recognition should be 120 ns. An internal pull-up device will hold this pin high when nothing is driving it. |  |  |

| 63  | ESR0           | O0 / I | St/B | External Service Request 0 After power-up, ESR0 operates as open-drain bidirectional reset with a weak pull-up.                                                                                                                                                                                                      |  |  |

|     | U1C0_DX0E      | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                                                                                     |  |  |

|     | U1C0_DX2B      | I      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                                                                                                                                                  |  |  |

Table 6 Pin Definitions and Functions (cont'd)

| Pin                                                | Symbol          | Ctrl. | Туре | Function                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|----------------------------------------------------|-----------------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 6                                                  | $V_{DDIM}$      | -     | PS/M | Digital Core Supply Voltage for Domain M Decouple with a ceramic capacitor, see Data Sheet for details.                                                                                                                                                                                                                                                                     |  |  |  |

| 24,<br>41,<br>57                                   | $V_{DDI1}$      | -     | PS/1 | Digital Core Supply Voltage for Domain 1 Decouple with a ceramic capacitor, see Data Sheet for details. All V <sub>DDI1</sub> pins must be connected to each other.                                                                                                                                                                                                         |  |  |  |

| 9                                                  | $V_{DDPA}$      | -     | PS/A | Digital Pad Supply Voltage for Domain A Connect decoupling capacitors to adjacent $V_{\rm DDP}/V_{\rm SS}$ pin pairs as close as possible to the pir Note: The A/D_Converters and ports P5, P6 at P15 are fed from supply voltage $V_{\rm DDPA}$ .                                                                                                                          |  |  |  |

| 2,<br>16,<br>18,<br>32,<br>34,<br>48,<br>50,<br>64 | $V_{DDPB}$      | -     | PS/B | Digital Pad Supply Voltage for Domain B Connect decoupling capacitors to adjacent $V_{\rm DDP}/V_{\rm SS}$ pin pairs as close as possible to the pins Note: The on-chip voltage regulators and all ponexcept P5, P6 and P15 are fed from supply voltage $V_{\rm DDPB}$ .                                                                                                    |  |  |  |

| 1,<br>17,<br>33,<br>49                             | V <sub>SS</sub> | -     | PS/  | Digital Ground All $V_{\rm SS}$ pins must be connected to the ground-line or ground-plane. Note: Also the exposed pad is connected internally to $V_{\rm SS}$ . To improve the EMC behavior, it is recommended to connect the exposed pad to the board ground. For thermal aspects, please refer to the Data Sheet. Board layout examples are given in an application note. |  |  |  |

## 2.2 Identification Registers

The identification registers describe the current version of the XC2336B and of its modules.

Table 7 XC2336B Identification Registers

| Short Name  | Value                  | Address              | Notes                   |

|-------------|------------------------|----------------------|-------------------------|

| SCU_IDMANUF | 1820 <sub>H</sub>      | 00'F07E <sub>H</sub> |                         |

| SCU_IDCHIP  | 3001 <sub>H</sub>      | 00'F07C <sub>H</sub> | marking EES-AA or ES-AA |

|             | 3002 <sub>H</sub>      | 00'F07C <sub>H</sub> | marking AA, AB          |

| SCU_IDMEM   | 304F <sub>H</sub>      | 00'F07A <sub>H</sub> |                         |

| SCU_IDPROG  | 1313 <sub>H</sub>      | 00'F078 <sub>H</sub> |                         |

| JTAG_ID     | 0018'B083 <sub>H</sub> |                      | marking EES-AA or ES-AA |

|             | 1018'B083 <sub>H</sub> |                      | marking AA, AB          |

#### **Functional Description**

## 3 Functional Description

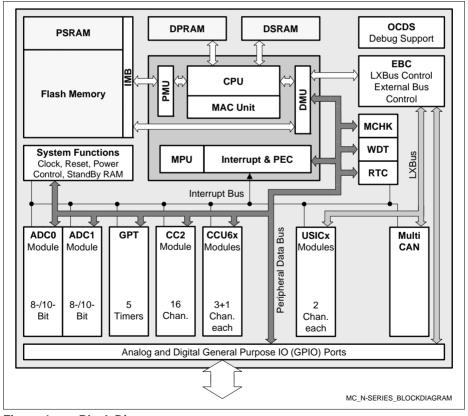

The architecture of the XC2336B combines advantages of RISC, CISC, and DSP processors with an advanced peripheral subsystem in a well-balanced design. On-chip memory blocks allow the design of compact systems-on-silicon with maximum performance suited for computing, control, and communication.

The on-chip memory blocks (program code memory and SRAM, dual-port RAM, data SRAM) and the generic peripherals are connected to the CPU by separate high-speed buses. Another bus, the LXBus, connects additional on-chip resources and external resources. This bus structure enhances overall system performance by enabling the concurrent operation of several subsystems of the XC2336B.

The block diagram gives an overview of the on-chip components and the advanced internal bus structure of the XC2336B.

Figure 4 Block Diagram

#### **Functional Description**

## 3.1 Memory Subsystem and Organization

The memory space of the XC2336B is configured in the von Neumann architecture. In this architecture all internal and external resources, including code memory, data memory, registers and I/O ports, are organized in the same linear address space.

Table 8 XC2336B Memory Map 1)

| Address Area             | Start Loc.           | End Loc.             | Area Size <sup>2)</sup>  | Notes               |

|--------------------------|----------------------|----------------------|--------------------------|---------------------|

| IMB register space       | FF'FF00 <sub>H</sub> | FF'FFFF <sub>H</sub> | 256 Bytes                |                     |

| Reserved                 | F0'0000 <sub>H</sub> | FF'FEFF <sub>H</sub> | < 1 Mbyte                | Minus IMB registers |

| Reserved for EPSRAM      | E8'4000 <sub>H</sub> | EF'FFFF <sub>H</sub> | 496 Kbytes               | Mirrors EPSRAM      |

| Emulated PSRAM           | E8'0000 <sub>H</sub> | E8'3FFF <sub>H</sub> | up to<br>16 Kbytes       | With Flash timing   |

| Reserved for PSRAM       | E0'4000 <sub>H</sub> | E7'FFFF <sub>H</sub> | 496 Kbytes               | Mirrors PSRAM       |

| PSRAM                    | E0'0000 <sub>H</sub> | E0'3FFF <sub>H</sub> | up to<br>16 Kbytes       | Program SRAM        |

| Reserved for Flash       | C5'0000 <sub>H</sub> | DF'FFFF <sub>H</sub> | 1,728 Kbytes             |                     |

| Flash 1                  | C4'0000 <sub>H</sub> | C4'FFFF <sub>H</sub> | 64 Kbytes                |                     |

| Flash 0                  | C0'0000 <sub>H</sub> | C3'FFFF <sub>H</sub> | 256 Kbytes <sup>3)</sup> | Minus res. seg.     |

| External memory area     | 40'0000 <sub>H</sub> | BF'FFFF <sub>H</sub> | 8 Mbytes                 |                     |

| External IO area4)       | 21'0000 <sub>H</sub> | 3F'FFFF <sub>H</sub> | 1,984 Kbytes             |                     |

| Reserved                 | 20'BC00 <sub>H</sub> | 20'FFFF <sub>H</sub> | 17 Kbytes                |                     |

| USIC0–2 alternate regs.  | 20'B000 <sub>H</sub> | 20'BBFF <sub>H</sub> | 3 Kbytes                 | Accessed via EBC    |

| MultiCAN alternate regs. | 20'8000 <sub>H</sub> | 20'AFFF <sub>H</sub> | 12 Kbytes                | Accessed via EBC    |

| Reserved                 | 20'5800 <sub>H</sub> | 20'7FFF <sub>H</sub> | 10 Kbytes                |                     |

| USIC0-2 registers        | 20'4000 <sub>H</sub> | 20'57FF <sub>H</sub> | 6 Kbytes                 | Accessed via EBC    |

| Reserved                 | 20'6800 <sub>H</sub> | 20'7FFF <sub>H</sub> | 6 Kbytes                 |                     |

| MultiCAN registers       | 20'0000 <sub>H</sub> | 20'3FFF <sub>H</sub> | 16 Kbytes                | Accessed via EBC    |

| External memory area     | 01'0000 <sub>H</sub> | 1F'FFFF <sub>H</sub> | 1984 Kbytes              |                     |

| SFR area                 | 00'FE00 <sub>H</sub> | 00'FFFF <sub>H</sub> | 0.5 Kbytes               |                     |

| Dualport RAM (DPRAM)     | 00'F600 <sub>H</sub> | 00'FDFF <sub>H</sub> | 2 Kbytes                 |                     |

| Reserved for DPRAM       | 00'F200 <sub>H</sub> | 00'F5FF <sub>H</sub> | 1 Kbytes                 |                     |

| ESFR area                | 00'F000 <sub>H</sub> | 00'F1FF <sub>H</sub> | 0.5 Kbytes               |                     |

| XSFR area                | 00'E000 <sub>H</sub> | 00'EFFF <sub>H</sub> | 4 Kbytes                 |                     |

| Data SRAM (DSRAM)        | 00'A000 <sub>H</sub> | 00'DFFF <sub>H</sub> | 16 Kbytes                |                     |

## XC2336B XC2000 Family / Value Line

#### **Functional Description**

## Table 8 XC2336B Memory Map (cont'd)<sup>1)</sup>

| Address Area         | Start Loc.           | End Loc.             | Area Size <sup>2)</sup> | Notes |

|----------------------|----------------------|----------------------|-------------------------|-------|

| Reserved for DSRAM   | 00'8000 <sub>H</sub> | 00'9FFF <sub>H</sub> | 8 Kbytes                |       |

| External memory area | 00'0000 <sub>H</sub> | 00'7FFF <sub>H</sub> | 32 Kbytes               |       |

- Accesses to the shaded areas are reserved. In devices with external bus interface these accesses generate external bus accesses.

- 2) The areas marked with "<" are slightly smaller than indicated, see column "Notes".

- 3) The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

- 4) Several pipeline optimizations are not active within the external IO area. This is necessary to control external peripherals properly.

This common memory space consists of 16 Mbytes organized as 256 segments of 64 Kbytes; each segment contains four data pages of 16 Kbytes. The entire memory space can be accessed bytewise or wordwise. Portions of the on-chip DPRAM and the register spaces (ESFR/SFR) additionally are directly bit addressable.

The internal data memory areas and the Special Function Register areas (SFR and ESFR) are mapped into segment 0, the system segment.

The Program Management Unit (PMU) handles all code fetches and, therefore, controls access to the program memories such as Flash memory and PSRAM.

The Data Management Unit (DMU) handles all data transfers and, therefore, controls access to the DSRAM and the on-chip peripherals.

Both units (PMU and DMU) are connected to the high-speed system bus so that they can exchange data. This is required if operands are read from program memory, code or data is written to the PSRAM, code is fetched from external memory, or data is read from or written to external resources. These include peripherals on the LXBus such as USIC or MultiCAN. The system bus allows concurrent two-way communication for maximum transfer performance.

**Up to 16 Kbytes of on-chip Program SRAM (PSRAM)** are provided to store user code or data. The PSRAM is accessed via the PMU and is optimized for code fetches. A section of the PSRAM with programmable size can be write-protected.

Note: The actual size of the PSRAM depends on the quoted device type.

# XC2336B XC2000 Family / Value Line

#### **Functional Description**

**Up to 16 Kbytes of on-chip Data SRAM (DSRAM)** are used for storage of general user data. The DSRAM is accessed via a separate interface and is optimized for data access.

Note: The actual size of the DSRAM depends on the quoted device type.

**2** Kbytes of on-chip Dual-Port RAM (DPRAM) provide storage for user-defined variables, for the system stack, and for general purpose register banks. A register bank can consist of up to 16 word-wide (R0 to R15) and/or byte-wide (RL0, RH0, ..., RL7, RH7) General Purpose Registers (GPRs).

The upper 256 bytes of the DPRAM are directly bit addressable. When used by a GPR, any location in the DPRAM is bit addressable.

**8 Kbytes of on-chip Stand-By SRAM (SBRAM)** provide storage for system-relevant user data that must be preserved while the major part of the device is powered down. The SBRAM is accessed via a specific interface and is powered in domain M.

**1024 bytes (2**  $\times$  **512 bytes)** of the address space are reserved for the Special Function Register areas (SFR space and ESFR space). SFRs are word-wide registers which are used to control and monitor functions of the different on-chip units. Unused SFR addresses are reserved for future members of the XC2000 Family. In order to ensure upward compatibility they should either not be accessed or written with zeros.

In order to meet the requirements of designs where more memory is required than is available on chip, up to 12 Mbytes (approximately, see **Table 8**) of external RAM and/or ROM can be connected to the microcontroller. The External Bus Interface also provides access to external peripherals.

**The on-chip Flash memory** stores code, constant data, and control data. The 320 Kbytes of on-chip Flash memory consist of 1 module of 64 Kbytes (preferably for data storage) and 1 module of 256 Kbytes. Each module is organized in 4-Kbyte sectors. The uppermost 4-Kbyte sector of segment 0 (located in Flash module 0) is used internally to store operation control parameters and protection information.

Note: The actual size of the Flash memory depends on the chosen device type.

Each sector can be separately write protected<sup>1)</sup>, erased and programmed (in blocks of 128 Bytes). The complete Flash area can be read-protected. A user-defined password sequence temporarily unlocks protected areas. The Flash modules combine 128-bit read access with protected and efficient writing algorithms for programming and erasing. Dynamic error correction provides extremely high read data security for all read access operations. Access to different Flash modules can be executed in parallel. For Flash parameters, please see **Section 4.6**.

To save control bits, sectors are clustered for protection purposes, they remain separate for programming/erasing.

# XC2336B XC2000 Family / Value Line

#### **Functional Description**

#### **Memory Content Protection**

The contents of on-chip memories can be protected against soft errors (induced e.g. by radiation) by activating the parity mechanism or the Error Correction Code (ECC).

The parity mechanism can detect a single-bit error and prevent the software from using incorrect data or executing incorrect instructions.

The ECC mechanism can detect and automatically correct single-bit errors. This supports the stable operation of the system.

It is strongly recommended to activate the ECC mechanism wherever possible because this dramatically increases the robustness of an application against such soft errors.

#### **Functional Description**

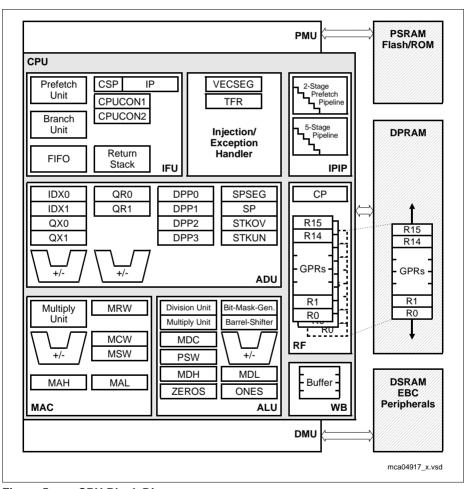

## 3.2 Central Processing Unit (CPU)

The core of the CPU consists of a 5-stage execution pipeline with a 2-stage instruction-fetch pipeline, a 16-bit arithmetic and logic unit (ALU), a 32-bit/40-bit multiply and accumulate unit (MAC), a register-file providing three register banks, and dedicated SFRs. The ALU features a multiply-and-divide unit, a bit-mask generator, and a barrel shifter.

Figure 5 CPU Block Diagram

# XC2336B XC2000 Family / Value Line

#### **Functional Description**

With this hardware most XC2336B instructions are executed in a single machine cycle of 12.5 ns @ 80-MHz CPU clock. For example, shift and rotate instructions are always processed during one machine cycle, no matter how many bits are shifted. Also, multiplication and most MAC instructions execute in one cycle. All multiple-cycle instructions have been optimized so that they can be executed very fast; for example, a 32-/16-bit division is started within 4 cycles while the remaining cycles are executed in the background. Another pipeline optimization, the branch target prediction, eliminates the execution time of branch instructions if the prediction was correct.

The CPU has a register context consisting of up to three register banks with 16 word-wide GPRs each at its disposal. One of these register banks is physically allocated within the on-chip DPRAM area. A Context Pointer (CP) register determines the base address of the active register bank accessed by the CPU at any time. The number of these register bank copies is only restricted by the available internal RAM space. For easy parameter passing, a register bank may overlap others.

A system stack of up to 32 Kwords is provided for storage of temporary data. The system stack can be allocated to any location within the address space (preferably in the on-chip RAM area); it is accessed by the CPU with the stack pointer (SP) register. Two separate SFRs, STKOV and STKUN, are implicitly compared with the stack pointer value during each stack access to detect stack overflow or underflow.

The high performance of the CPU hardware implementation can be best utilized by the programmer with the highly efficient XC2336B instruction set. This includes the following instruction classes:

- Standard Arithmetic Instructions

- · DSP-Oriented Arithmetic Instructions

- Logical Instructions

- Boolean Bit Manipulation Instructions

- Compare and Loop Control Instructions

- Shift and Rotate Instructions

- Prioritize Instruction

- Data Movement Instructions

- System Stack Instructions

- Jump and Call Instructions

- Return Instructions

- System Control Instructions

- Miscellaneous Instructions

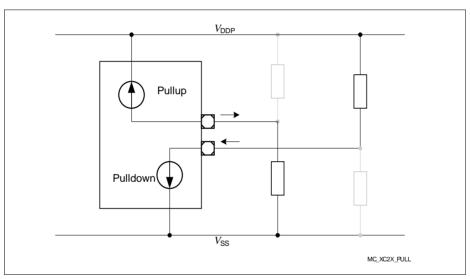

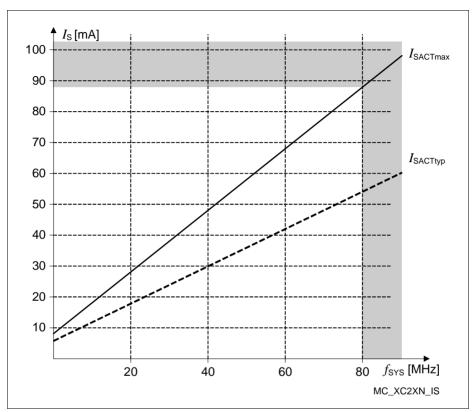

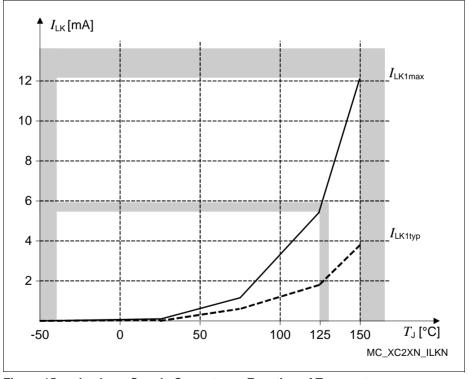

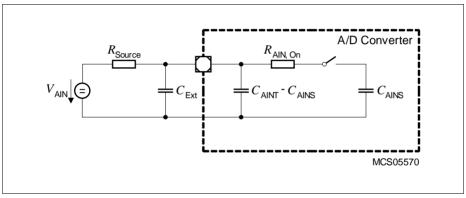

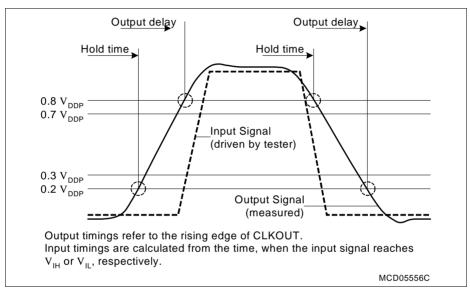

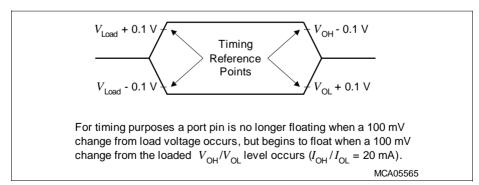

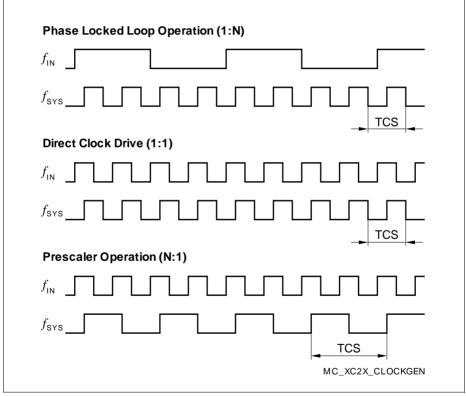

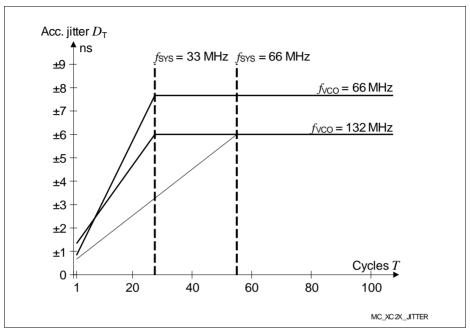

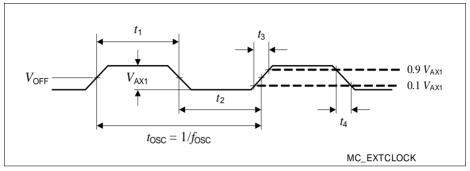

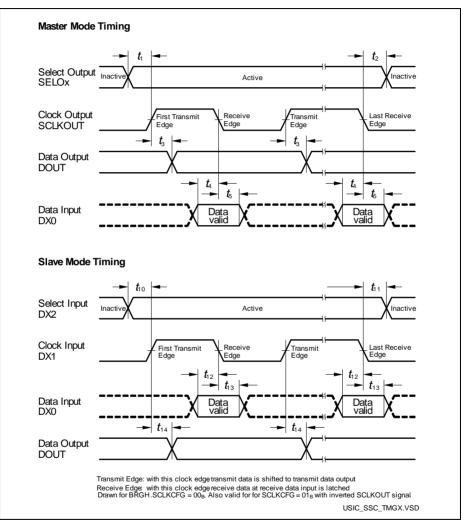

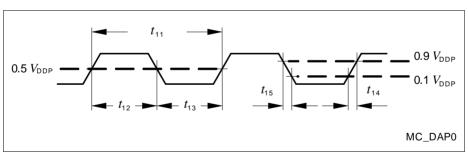

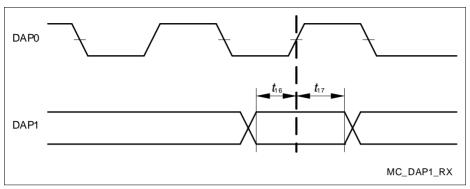

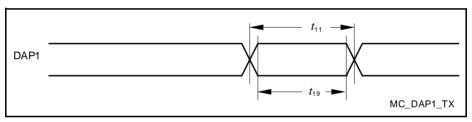

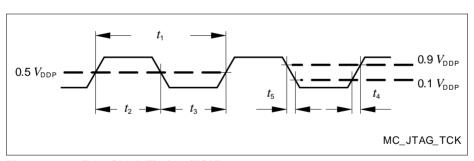

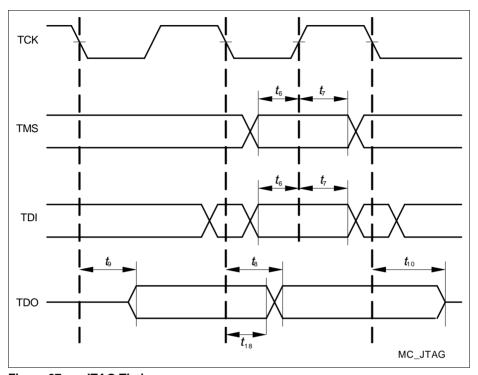

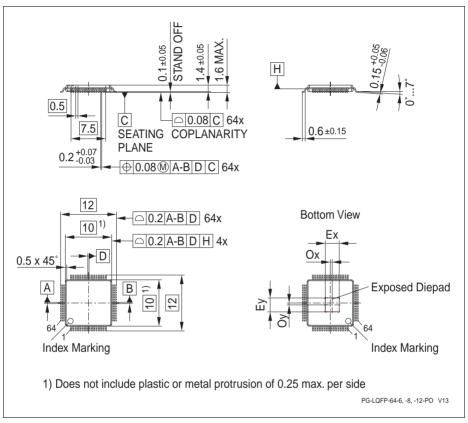

The basic instruction length is either 2 or 4 bytes. Possible operand types are bits, bytes and words. A variety of direct, indirect or immediate addressing modes are provided to specify the required operands.