Authors: Steiner Alois

Di Domenico Francesco

Catly Johnald Stückler Franz

**Application Note**

### About this document

#### Scope and purpose

The present 600 W Evaluation Board is a great example of a full Infineon solution, including high voltage and low voltage power devices, controllers and drivers in order to demonstrate the most flexible and effective way to design the High Voltage DC/DC stage of a Server PSU fulfilling the 80Plus® Titanium Standard.

Furthermore the reader will get additional information how the 600 V CoolMOS™ C7 behaves in this LLC board and what benefits will be achieved.

#### Intended audience

This document is intended for design engineers who want to improve their high voltage power conversion applications.

# **Table of Contents**

| 1     | Introduction                                     | 3                       |

|-------|--------------------------------------------------|-------------------------|

| 2     | HB LLC Converter Design Considerations           | 4                       |

| 2.1   | Principle of operation                           |                         |

| 2.2   | Input design data                                | 5                       |

| 2.3   | Selection of the inductance factor m             |                         |

| 2.4   | Gain curve                                       |                         |

| 2.5   | Resonant components calculation                  | 6                       |

| 2.6   | The ZVS behavior: energy and time considerations |                         |

| 2.6.1 | Energy related equations                         |                         |

| 2.6.2 | Time related equations                           |                         |

| 2.7   | The main transformer design                      |                         |

| 2.8   | The resonant choke design                        |                         |

| 2.9   | The Synchronous Rectification Stage              |                         |

| 3     | Board description                                | 12                      |

| 3.1   | General overview                                 |                         |

| 3.2   | Infineon BOM                                     |                         |

| 3.2.1 | Primary HV MOSFETs CoolMOS™ IPP60R180C7          |                         |

|       | 1                                                | Davision 1 2 2015 00 24 |

| Introdu | ction                                                  |    |

|---------|--------------------------------------------------------|----|

| 3.2.2   | LLC analog controller ICE2HS01G                        | 13 |

| 3.2.3   | Half Bridge Gate Drive 2EDL05N06PF                     | 13 |

| 3.2.4   | Advanced dual-channel Gate Drive 2EDN7524F             | 14 |

| 3.2.5   | Bias QR Flyback controller ICE2QR2280Z                 | 15 |

| 3.2.6   | Synchronous Rectification MOSFETs OptiMOS™ BSC010N04LS | 15 |

| 3.3     | Board schematic                                        | 16 |

| 3.3.1   | Mainboard schematic                                    | 16 |

| 3.3.2   | Control board schematic                                | 17 |

| 3.3.3   | Biasboard schematic                                    | 18 |

| 4       | Typical characteristics with 600 V CoolMOS™ C7         | 20 |

| 4.1     | Critical LLC operation - hard commutation              | 20 |

| 4.2     | Full ZVS area                                          | 21 |

| 4.3     | Burstmode operation                                    | 21 |

| 4.4     | Efficiency                                             | 22 |

| 4.4.1   | Titanium Efficiency                                    | 22 |

| 4.4.2   | Efficiency comparison in resonant LLC Half Bridge      | 23 |

| 5       | Test/powerup procedure                                 | 24 |

| 6       | Useful material and links                              | 26 |

| 7       | References                                             | 27 |

| 8       | List of abbreviations                                  | 28 |

Introduction

## 1 Introduction

The opportunity to significantly reduce the size of power converters by increasing the switching frequency created by the MOSFET technology has recently focused topology development and optimization on the reduction of switching losses of the semiconductor devices, which are perceived as the major obstacle to maximizing the switching frequency of PWM converters.

This has triggered studies on the resonant power conversion, which allows minimizing the switching losses through the achievement of zero-voltage (ZVS) or zero-current (ZCS) switching behavior.

An important example of resonant power conversion is provided by the LLC topology, which is able to address the requirements of high efficiency and power density through the achievement of a true Zero Voltage Switching. Last but not least, its bill of material is significantly reduced compared to the other very popular soft switching topology, the phase shift Full Bridge. These arguments bring the LLC resonant converter more and more in usage in the server/telecom market.

This document will describe an analog controlled 600 W Half Bridge (HB) LLC converter designed using Infineon products. Order information for ISAR: **EVAL\_600W\_12V\_LLC\_C7**

**HB LLC Converter Design Considerations**

## 2 HB LLC Converter Design Considerations

In the present chapter the most relevant design decisions are explained and documented with related calculations.

#### 2.1 Principle of operation

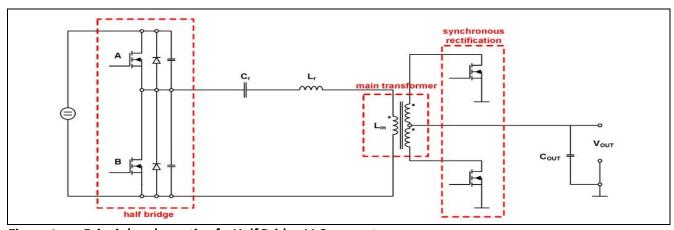

The principle schematic of a Half Bridge LLC converter is shown in the Figure 1. C<sub>r</sub>, L<sub>r</sub> and L<sub>m</sub> represent the so called "resonant tank": together with the main transformer they are the key components in the LLC design. The primary Half Bridge and the secondary synchronous rectification are the other two stages to be defined.

Figure 1 Principle schematic of a Half Bridge LLC converter

The LLC is a resonant converter that means it operates with frequency modulation, instead of the Pulse Width Modulation (PWM), traditional approach to power conversion.

Starting point in a resonant converter design is the definition of an energy transfer function, which can be seen as a voltage gain function, so a mathematical relationship between input and output voltages of the converter. Trying to get this function in an "exact" way involves several nonlinear circuital behaviors governed by complex equations. However, under the assumption that the LLC operates in the vicinity of the series resonant frequency important simplifications can be introduced.

In fact, under this assumption, the current circulating in the resonant tank can be considered purely sinusoidal, ignoring all higher order harmonics: this is the so called First Harmonic Approximation Method (FHA), which is the most common approach to the design of a LLC converter.

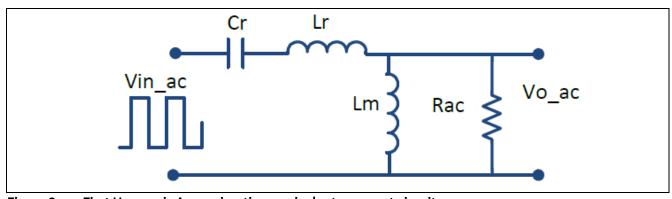

In the FHA the voltage gain is calculated with reference to the following equivalent resonant circuit, shown in Figure 2.

Figure 2 First Harmonic Approximation equivalent resonant circuit

#### **HB LLC Converter Design Considerations**

The mathematical expression of the gain K is:

$$K(Q, m, Fx) = \left| \frac{V_{o_{a}}c(s)}{V_{in_{a}}c(s)} \right| = \frac{F_{x^{2}}(m-1)}{\sqrt{(m \cdot F_{x^{2}}-1)^{2} + F_{x^{2}} \cdot (F_{x^{2}}-1)^{2} \cdot (m-1)^{2} \cdot Q^{2}}}$$

(1)

where:

$$m = \frac{L_r + L_m}{L_r}; \qquad f_r = \frac{1}{\sqrt{L_r \cdot C_r}}; \qquad F_x = \frac{f_s}{f_r}; \qquad R_{ac} = \frac{8}{\pi^2} \cdot \frac{N_p^2}{N_s^2} \cdot R_o; \qquad Q = \frac{\sqrt{\frac{L_r}{C_r}}}{R_{ac}}; \qquad (2)$$

So the resonant tank gain K can be plotted in function of the normalized switching frequency  $f_x$  for different values of the Quality factor Q and any single value of the inductance factor m.

In this chapter it will be shown a design procedure for the selection of the main LLC parameters, with the goal to achieve the best performance while fulfilling input and output regulation requirements.

At same time, Zero Voltage Switching operation of the primary Half Bridge MOSFETs must be ensured, in order to get full benefits out of the soft switching behavior, especially at light load.

## 2.2 Input design data

In Table 1 an overview of the major design parameter is displayed.

Table 1 Design parameters

| Description                        | Minimum              | Nominal             | Maximum                 |

|------------------------------------|----------------------|---------------------|-------------------------|

| Input Voltage                      | 350 V <sub>DC</sub>  | 380 V <sub>DC</sub> | 410 V <sub>DC</sub>     |

| Output Voltage                     | 11.9 V <sub>DC</sub> | 12 V <sub>DC</sub>  | 12.1 V <sub>DC</sub>    |

| Output Power                       |                      |                     | 600 W                   |

| Efficiency at 50% P <sub>max</sub> | 97.5%                |                     |                         |

| Switching Frequency                | 90 kHz               | 150 kHz             | 250 kHz                 |

| Dynamic Output Voltage regulation  |                      |                     | Max. overshoot = 0.1 V  |

| (0-90% Load step)                  |                      |                     | Max. undershoot= 0.3 V  |

| $V_{\text{out\_ripple}}$           |                      |                     | 150 mV <sub>pk-pk</sub> |

From the table above, the first important design parameters can be derived:

Main transformer turn ratio

$$n = \frac{N_p}{N_s} = \frac{V_{in\_nom}}{2 \cdot V_{out\_nom}} \approx 16$$

(3)

Minimum needed Gain

$$K \min(Q, m, F_x) = \frac{n \cdot V_{o_- \min}}{V_{in_- \max}/2} \approx 0.95$$

(4)

Maximum needed Gain

$$K_{\max}(Q, m, F_x) = \frac{n \cdot V_{o_{\max}}}{V_{in_{\min}}/2} \approx 1.08$$

(5)

#### **HB LLC Converter Design Considerations**

#### 2.3 Selection of the inductance factor m

The inductance factor (Equation 2) has an important impact on the converter operation. Lower values of m achieve higher boost gain and narrower range of the frequency modulation, that means more flexible control and regulation, which is valuable in applications with very wide input voltage range.

On the other hand, this means also smaller values of  $L_m$  which leads into significantly high magnetizing current circulating in the primary side: this current doesn't contribute to the power transferred, but mainly generates conduction losses on the primary side.

In other words, there is a trade-off between flexible regulation and overall efficiency requirements, especially at light load.

In the case of our demo board, main goal is to achieve high efficiency, so relatively high m is selected, also because the input range is relatively narrow and in any case we rely in the bulk capacitor in case of specific hold up time requirement at the complete AC/DC SMPS level - so in our case m≈12.

#### 2.4 Gain curve

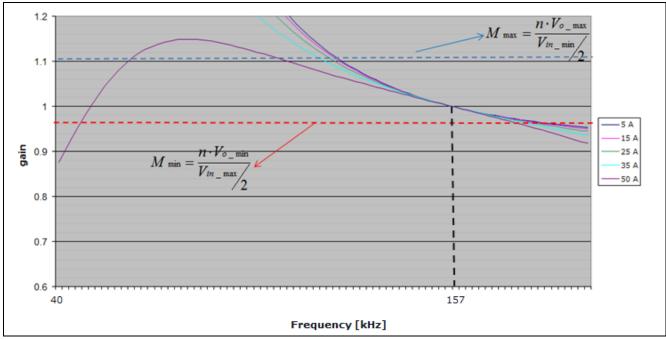

The resulting gain curves, Figure 3, for loads between 10% and 100% P<sub>max</sub> are in the following plot:

Figure 3 Gain curve

Both the  $M_{min}$  and  $M_{max}$  limits cross all the gain curves of our LLC converter: that means the regulation is fully achieved in the specified ranges.

## 2.5 Resonant components calculation

Combining equations (1) and (2), we get a system where the unknown are  $L_r$ ,  $C_r$  and  $L_m$ . Solving it, the following values are set for the LLC converter:

$$n = \frac{N_p}{N_s} = \frac{V_{in\_nom}}{2 \cdot V_{out\_nom}} \approx 16 \Rightarrow Np = 16; Ns = 1$$

(6)

**HB LLC Converter Design Considerations**

$$m = \frac{L_r + L_m}{L_r} \approx 12 \Longrightarrow L_m = 195 \,\mu\text{H}; L_r = 17 \,\mu\text{H}$$

(7)

$$Cr = 66nF \tag{8}$$

$$fr = \frac{1}{2\pi \cdot \sqrt{Lr \cdot Cr}} \approx 150KHz \tag{9}$$

#### 2.6 The ZVS behavior: energy and time considerations

The ZVS calculations involve two kind of analysis, the one in the energy domain and the other in the time domain. The goal is to have enough energy in the resonant tank able to discharge the output capacitance of the primary MOSFET, but also an appropriate dead time between the turn-off of each device and the corresponding turn-on of the one at the other side of the Half Bridge.

$C_{o(er)}$  is the  $C_{oss}$  energy related component of the used High Voltage MOSFET, in our case IPP60R180C7.  $Q_{oss}$  is the charge stored in  $C_{oss}$  at  $V_{in(nom)}$ =380  $V_{DC}$

#### 2.6.1 Energy related equations

$$\operatorname{Im} ag_{-\min} = \frac{2 \cdot \sqrt{2}}{\pi} \cdot \frac{n \cdot V_o}{2\pi \cdot f_{sw_{-\max}} \cdot L_m} = 0.672A \tag{10}$$

$$Enres\_\min = \frac{1}{2} \cdot (L_m + L_r) \cdot I^2 mag\_\min = 95.1 \mu J \tag{11}$$

$$Encap_{\text{max}} = \frac{1}{2} \cdot (2Co(er)) \cdot V^2 DS_{\text{max}} \approx 9 \mu J$$

(12)

$$\Rightarrow Enres\_\min > Encap\_\max \tag{13}$$

## 2.6.2 Time related equations

It can be demonstrated that:

$$tdead = \frac{tecs}{2} + \frac{2 \cdot Qoss @ \text{Vin\_nom}}{\text{Im},pk} = \frac{tecs}{2} + \frac{2 \cdot Co(tr) @ \text{Vin\_nom} * \text{Vin\_nom}}{\text{Im},pk}$$

(14)

where  $t_{dead}$  is the dead time set between the conduction time of the two HB devices and  $t_{ecs}$  is the time when the channel of each MOSFET is still in conduction after turning it off (linear mode operation), which is function of device parameters like  $V_{gs(th)}$ ,  $R_{g(tot)}$  and  $C_{gs}/C_{gd}$ .

Using that equation, together with the min and max values of the magnetizing current:

$$\operatorname{Im} ag \_ \min = \frac{2 \cdot \sqrt{2}}{\pi} \cdot \frac{n \cdot Vo}{2\pi \cdot fsw \_ \max Lm} = 0.672 A \tag{10}$$

#### **HB LLC Converter Design Considerations**

$$\operatorname{Im} ag \_ \max = \frac{2 \cdot \sqrt{2}}{\pi} \cdot \frac{n \cdot Vo}{2\pi \cdot fsw \_ \min \cdot Lm} = 1.66 A \tag{11}$$

$$tdead, \min = \frac{tecs}{2} + \frac{2 \cdot Qoss, @400V}{Im, ag, \max} \approx 130 \, ns$$

(14)

$$tdead$$

,  $max = \frac{tecs}{2} + \frac{2 \cdot Qoss, @ 400V}{Im ag, min} \approx 311 ns$  (15)

### 2.7 The main transformer design

As explained more in details in the chapter 2.6 of the present document, the target efficiency of this design is fixed by the 80PLUS® Titanium Standard; that means fixing certain minimum requirements for the High Voltage DC/DC stage at 10%, 20%, 50%, 100% load conditions.

The most critical condition for the main transformer is the full load, mainly due to thermal reasons. The selection of the core size and material is done according to this condition along with the power density (thus switching frequency) target and the available airflow.

Keeping a margin in the design, the minimum efficiency requirement at full load is fixed for the Half Bridge LLC converter to 97%, which means our goal is to keep the total dissipated power in that condition below 18 W.

In order to guarantee a balanced spread of power and heating, a good rule in the design of the LLC Converter is to keep the total power dissipated on the main transformer below 1/6 of the total dissipated power, which means the max allowed power on it shall be below 3 W. This is our first important design input.

The max operating temperature is 55°C, as in typical server applications. Due to transformer safety insulation approvals, the max operating temperature of the transformer must be lower than 110°C, thereof:

$$\Delta T_{trafo\_MAX} = (110 - 55)^{\circ} C = 55^{\circ} C$$

(16)

From (16) and (17) the max thermal resistance of the core shape can be easily derived:

$$R_{th\_trafo\_MAX} = \frac{\Delta T_{trafo\_MAX}}{P_{trafo\_MAX}} = \frac{55}{3} \, {}^{\circ}C_{W} = 18.3 \, {}^{\circ}C_{W}$$

$$(17)$$

So our selected core shape must have thermal resistance lower than 18.3°C/W.

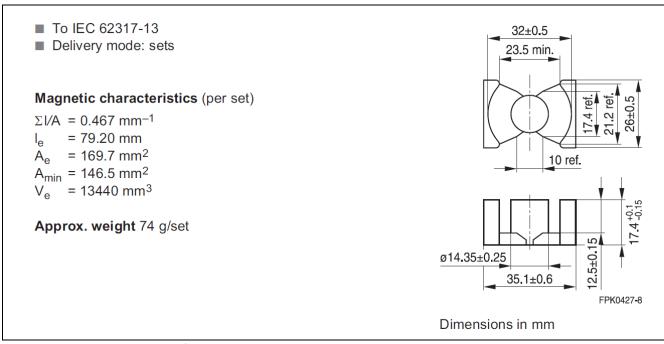

This requirement can be fulfilled with different choices: the preferred will allow maximizing the ratio between available winding area and effective volume, of course compatibly with the eq. (18). Also considering the power density target (in the range of 20 W/inch³), the most suitable selection is PQ 35/35, shown in Figure 4.

The related coil form shows a minimum winding area of 1.58 cm<sup>2</sup> and a thermal resistance of 16.5°C/W, thus able to dissipate up to 3.33 W by keeping the  $\Delta T_{MAX}$  <55°C.

Once verified that the thermal equations are fulfilled, we can proceed with the design of the primary and secondary windings and the core material selection, with some important goals:

- Fitting the geometry/overall dimensions of the core

- Fulfilling the condition (16)

- Try to split as much equally as possible the losses between core and windings: ideally "fifty-fifty" should be achieved at full load, but any percentage close to it would be acceptable.

#### **HB LLC Converter Design Considerations**

Figure 4 TDK-Epcos PQ35/35 core

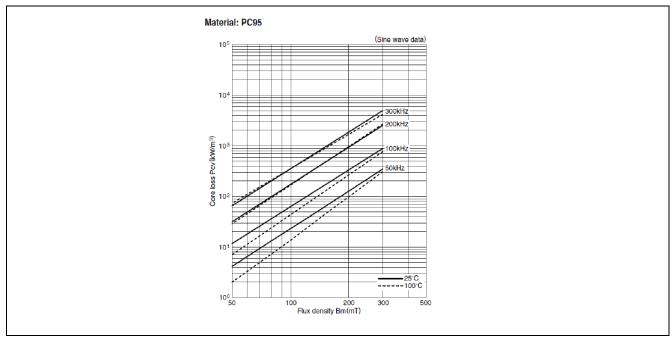

The selected core material is the ferrite TDK PC95, showing a very interesting plot of Core Losses (PCV) vs. Flux Density vs. frequency (see Figure 5 below):

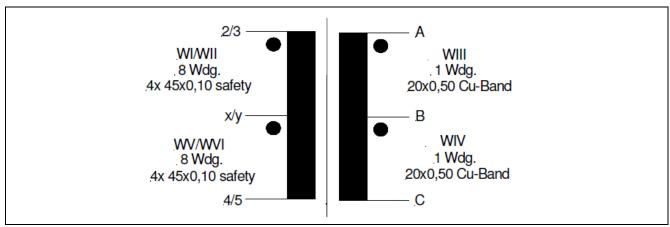

The final structure of the main transformer is reported in Figure 6 below. This has been developed in cooperation with the partner company Kaschke Components GmbH, Göttingen – Germany. So the primary is realized in a "sandwich" technique using 16 turns of 4 layers of litz wire 45 strands 0.1 mm diam. This allows minimizing the AC losses due to skin and proximity effect. The secondary is done with copper band 20x0.5 mm.

Figure 5 Ferrite core material TDK PC95

#### **HB LLC Converter Design Considerations**

With this choice, at full load condition the total copper losses will be (primary + secondary, DC+AC components) are 1.1 W, the core losses are 1.8 W, so overall:

$$P_{trafo} = P_{copper} + P_{core} = 2.9W < P_{trafo\_MAX}$$

(18)

In other words, the equation (18) fulfils the thermal equation (17).

Figure 6 Winding structure of the PQ 35/35 LLC transformer (Kaschke Components GmbH)

An important transformer parameter involved in the LLC design is the primary or magnetizing inductance  $L_m$ , which, according to eq. (7) must be 195  $\mu$ H. This value is obtained with distributed air-gap on the side legs of the PQ core: this construction is preferred since it minimizes the effect of the so called "fringing flux" which generates additional losses in the windings close to the inner limb.

## 2.8 The resonant choke design

In LLC designs with stringent power density requirements, the resonant choke is typically embedded in the transformer, in the sense that the leakage inductance is utilized according this purpose. This technique has the big advantage to save space and the cost of an additional magnetic component, but also some drawbacks, like the not easy controllability of the  $L_r$  value in mass production.

In the case of the present design, it has been decided to use an external Lr. This is due to the fact that the demo board is intended to be primarily used for test and benchmarking and therefore high power density is not in the main focus: having the resonant inductance externally allows to change the resonant tank in a more flexible way.

According to equation (7), the overall value of  $L_r$  shall be 17  $\mu$ H, including the contribution of the transformer leakage inductance + the external resonant choke.

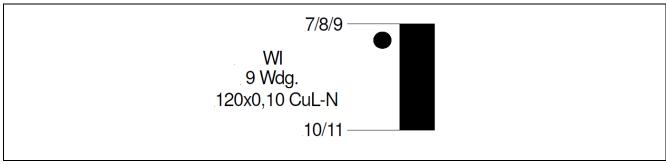

The external resonant choke is realized using a RM-12 core and a winding construction illustrated in Figure 7 below and implemented by the partner company Kaschke Components GmbH, Göttingen - Germany.

Figure 7 Winding structure of the RM 12 resonant choke (Kaschke Components GmbH)

#### **HB LLC Converter Design Considerations**

### 2.9 The Synchronous Rectification Stage

In applications that target high efficiency both at low and high loads –such as 80PLUS® Titanium- while often requiring high power densities, it is critical to select for the Synchronous Rectification Stage MOSFETs that combine multiple key characteristics.

First of all, these Sync Rec MOSFETs should exhibit very low R<sub>DS(on)</sub>. Indeed, due to the low voltages observed on the secondary side of server power supplies, large currents flow through the Sync Rec MOSFETs. Moreover, compared with hard switching topologies such as ZVS PS FB (Zero Voltage Switching Phase-Shifted Full Bridge), using LLC topology leads not only to increased peak currents for the Sync Rec MOSFETs, but also higher root-mean-square currents I<sub>RMS</sub>.

Since the conduction losses P<sub>cond,SR</sub> of each Sync Rec MOSFET are defined by:

$$P_{cond\_SR} = R_{DS, on} \cdot (I_{RMS})^2 \tag{19}$$

These losses can only be mitigated through the use of a part with very low R<sub>DS(on)</sub>.

Secondly, it is critical for these Sync Rec MOSFETs to exhibit low gate charges Qg:

At lower loads, the switching losses of the Sync Rec MOSFETs predominate over the already mentioned conduction losses. In the case of LLC topology, the main contributor of these switching losses is related to  $Q_{\rm g}$ .

Most of the time, a driving voltage of 12 V is applied to Sync Rec MOSFETs. Although 12 V is not necessary the optimized driving voltage for Sync Rec MOSFETs (more on this below), this driving voltage is very popular in server PSUs because it is readily available: there is no need to derive it from another voltage rail. Therefore, we decided to follow this trend for this demo board by driving the Sync Rec MOSFETs with 12 V. This requirement for low  $Q_g$  puts extra-strain on MOSFET manufacturers, especially considering that Sync Rec MOSFETs need to exhibit at the same time a very low  $R_{DS(on)}$ . Such a feat was however possible for Infineon thanks to the new Infineon OptiMOS<sup>TM</sup> 40 V generation, whose gate charges have been significantly reduced in comparison with the previous generation.

Thirdly, the paralleled Sync Rec MOSFETs should turn on almost simultaneously.

This can be achieved thanks to a tightening of the threshold voltage  $V_{GS(th)}$  range. In the case new OptiMOS<sup>TM</sup> 40 V generation, its datasheet guarantees a very narrow  $V_{GS(th)}$  range, with min and max values equal to 1.2 V and 2.0 V respectively.

Finally, the MOSFET package is critical for a variety of reasons.

The package should exhibit low parasitic inductances in order to confine its contribution to the  $V_{DS}$  overshoot to a strict minimum. This is even more critical in server applications using LLC topology, due to the limited headroom for the  $V_{DS}$  overshoot between the transformer secondary voltage (25 V) and the 90% derating (36  $V_{max}$ ) or even 80% derating (32  $V_{max}$ ) applied to the  $V_{DS}$  of the Sync Rec MOSFETs; Moreover, due to the conflicting requirements for high power density and high current capability, the package should combine a minimum footprint with good power dissipation.

Because of the high current densities arising at the source pins, which can lead to electro-migration and thereafter destruction of the Sync Rec MOSFETs, the package should provide an enlarged source connection. While the first two sub-items are tackled by standard SuperSO8 packages, it is the addition of source fused leads implemented in the new Infineon OptiMOS<sup>™</sup> 40 V generation that reduces the high current densities above mentioned.

**Board description**

## 3 Board description

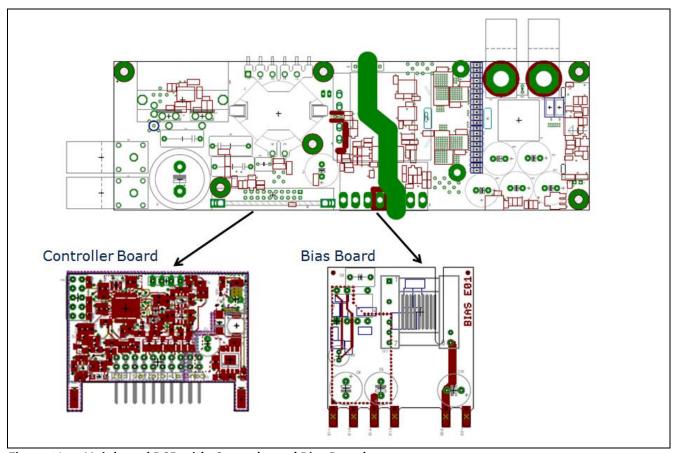

#### 3.1 General overview

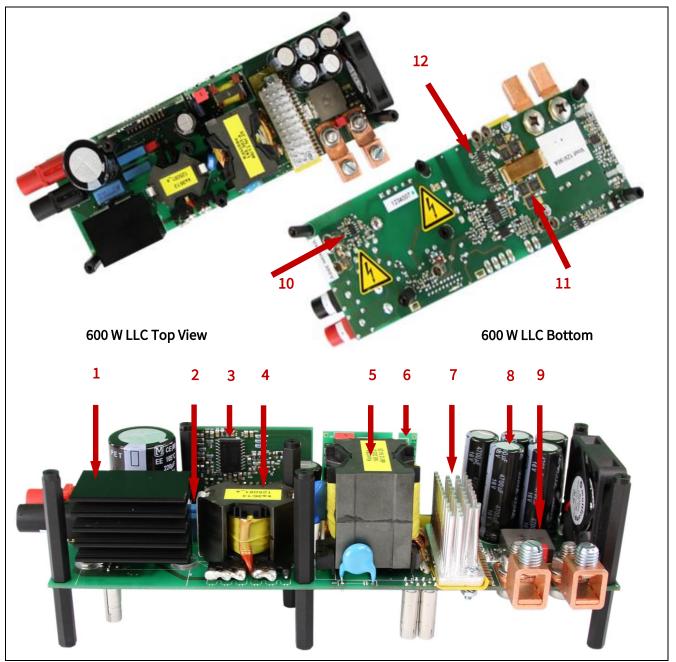

Figure 1 is the top view, bottom view and the assembly of 600W Half Bridge LLC evaluation board. Key components are: (1) heat sink with the assembly of primary side switches IPP60R180C7 (2) Resonant capacitor (3) LLC analog controller ICE2HS01G (4) Resonant inductor (5) Main DC-DC transformer (6) PCB assembly of the auxiliary circuit with bias QR Flyback controller ICE2QR2280Z (7) Heat sink assembly for cooling the synchronous rectifier (8) Output capacitor (9) Output inductor (10) Half Bridge MOSFET gate driver 2EDL05N06PF and (11) Synchronous rectifier OptiMOS™ BSC010N04LS (12) Advanced dual-channel Gate Drive 2EDN7524F.

Figure 8 IFX 600W LLC Evaluation Board

#### **Board description**

#### 3.2 Infineon BOM

This HB LLC 600 W demonstration board is a full Infineon solution, meeting the highest efficiency standard 80PLUS® Titanium using the following parts:

### 3.2.1 Primary HV MOSFETs CoolMOS™ IPP60R180C7

The 600 V CoolMOS™ C7 is the next step of Silicon improvement based on the 650 V CoolMOS™ C7. It stays with the strategy to increased switching performance in order to enable highest efficiency in any kind of target applications as for boost topologies like PFC's (power factor correction) and high voltage DC/DC stages like LLC's (DC/DC stage with resonant tank in order to maintain zero voltage switching). Although the 600 V CoolMOS™ offers very fast switching, it also kept the ease of use level (how easy to control the switch) of the 650 V C7 "parent technology". Therefore the 600 V CoolMOS™ C7 is optimized device for highest efficiency SMPS (switched mode power supply). The 600 V C7 represents the new standard of SJ MOSFET.

In LLC application, converter is in resonant operation with guaranteed ZVS even at a very light load condition. Switching loss caused by  $E_{oss}$  during turn-on can be considered negligible in this topology. With this consideration,  $CoolMOS^{TM}$  C7 family of parts offers superior price/performance ratio with low FOMs ( $R_{on}^*Q_g$  and  $R_{on}^*Q_{oss}$ ), which means that MOSFET switching transitions can happen in a shorter dead time period. This will result to a lower turn-off losses pushing further the efficiency. The following are the additional features and benefits of  $CoolMOS^{TM}$  C7 making it suitable and advantageous for resonant switching topologies like LLC:

- Suitable for hard and soft switching (PFC and high performance LLC)

- Increased MOSFET dv/dt ruggedness to 120 V/ns

- Increased efficiency due to Best-in-Class FOM R<sub>DS(on)</sub>\*E<sub>oss</sub> and R<sub>DS(on)</sub>\*Q<sub>g</sub>

- Best-in-class R<sub>DS(on)</sub>/package

- Qualified for industrial grade applications according to JEDEC (J-STD20 and JESD22)

### 3.2.2 LLC analog controller ICE2HS01G

ICE2HS01G is Infineon's 2<sup>nd</sup> generation HalfBridge LLC controller designed especially for high efficiency Half Bridge or FullBridge LLC resonant converter with synchronous rectification (SR) control for the secondary side. With its new driving techniques, the synchronous rectification can be realized for LLC converter operated with secondary switching current in both CCM and DCM conditions. No special synchronous rectification controller IC is needed at the secondary side. The maximum switching frequency is supported up to 1 MHz. Apart from the patented SR driving techniques, this IC provides very flexible design and integrates full protection functions as well. It is adjustable for maximum/minimum switching frequency, soft-start time, frequency, dead time between primary switches, turn-on and turn-off delay for secondary SR MOSFETs. The integrated protections include input voltage brownout, primary three-levels over current, secondary over load protection and no-load regulation. It also includes a burst mode function which offers an operation with low quiescent current maintaining high efficiency at low output load while keeping output ripple voltage low.

## 3.2.3 Half Bridge Gate Drive 2EDL05N06PF

2EDL05N06PF is one of the drivers from Infineon's 2EDL EiceDRIVER™ Compact 600V Half Bridge gate driver IC family with monolithic integrated low-ohmic and ultrafast bootstrap diode. Its level-shift SOI technology supports higher efficiency and smaller form factors of applications. Based on the used SOI-technology there is an excellent ruggedness on transient voltages. No parasitic thyristor structures are present in the device. Hence, no parasitic latch up may occur at all temperature and voltage conditions. The two independent

#### **Board description**

drivers outputs are controlled at the low-side using two different CMOS resp. LSTTL compatible signals, down up to 3.3 V logic. The device includes an under-voltage detection unit with hysteresis characteristic which are optimised either for IGBT or MOSFET. 2EDL05N06PF (DSO-8) and 2EDL05N06PJ (DSO-14) are driver ICs with undervoltage-lockout for MOSFETs. These two parts are recommended for server/telecom, low-voltage drives, e-bike, battery charger and Half Bridge based switch mode power supply topologies.

- Individual control circuits for both outputs

- Filtered detection of under voltage supply

- All inputs clamped by diodes

- Off line gate clamping function

- Asymmetric undervoltage lockout thresholds for high side and low side

- Insensitivity of the bridge output to negative transient voltages up to -50 V given by SOI-technology

- Ultra fast bootstrap diode

#### 3.2.4 Advanced dual-channel Gate Drive 2EDN7524F

The Fast Dual Channel 5 A Low-Side Gate Driver is an advanced dual-channel driver optimized for driving both Standard and Superjunction MOSFETs, as well as GaN Power devices, in all applications in which they are commonly used. The input signals are TTL compatible (CMOS 3.3 V) with an input voltage range from 3 V to +20 V. The ability to operate with -10  $V_{DC}$  at the input pins protects the device against ground bounce conditions. Each of the two outputs is able to sink and source a 5 A current utilizing a true rail-to-rail stage, that ensures very low impedances of 0.7  $\Omega$  up to the positive and 0.55  $\Omega$  down to the negative rail respectively. Very low channel to channel delay matching, typ. 1 ns, enables the double source and sink capability of 10 A, by paralleling both channels. Different logic input/output configurations guarantee high flexibility in all applications; e.g. with two paralleled switches in a boost configuration (see Figure below). The gate driver is available in the three package options: A standard PG-DSO-8, a thin PG-WSON-8-1 and PG-TSSOP-8-1 (minimized DSO 8 package).

#### Main Features

- Industry-Standard Pinout

- Two Independent Low-Side Gate Drivers

- 5 A Peak Sink/Source Output Driver at V<sub>DD</sub> = 12 V

- -10 V<sub>DC</sub> Negative Input Capability against GND-Bouncing

- Enhanced operating robustness due to High Reverse Current Capability

- True Low-Impedance Rail-To-Rail Output (0.7  $\Omega$  and 0.55  $\Omega$ )

- Very Low Propagation Delay (19 ns)

- Typ. 1 ns Channel to Channel Delay Matching

- Wide Input and Output Voltage Range up to 20 V

- Active Low Output Driver even on Low Power or Disabled Driver

- High Flexibility through Different Logic Input Configurations (LVTTL and CMOS 3.3 V)

- PG-DSO-8, PG-WSON-8-1 and PG-TSSOP-8-1 Package

- Extended Operation from -40 °C to 150 °C (Junction Temperature)

- Particularly Well-Suited for Driving Standard, Superjunction MOSFETs, IGBTs or GaN Power Devices

#### **Board description**

#### **Typical Applications**

- SMPS

- DC/DC Converters

- Motor Control

- Solar Power, Industrial Applications

### 3.2.5 Bias QR Flyback controller ICE2QR2280Z

ICE2QRxxxx is a second generation quasi-resonant PWM CoolSET™ with power MOSFET and startup cell in a single package optimized for off-line power supply applications such as LCD TV, notebook adapter and auxiliary/housekeeping converter in SMPS. The digital frequency reduction with decreasing load enables a quasi-resonant operation till very low load. As a result, the system average efficiency is significantly improved compared to conventional solutions. The active burst mode operation enables ultra-low power consumption at standby mode operation and low output voltage ripple. The numerous protection functions give a full protection of the power supply system in failure situation. Main features of ICE2QR2280Z which make it suitable as an auxiliary converter of this LLC demonstration board are:

- High voltage (650 V/800 V) avalanche rugged CoolMOS™ with startup cell

- Quasi-resonant operation

- Load dependent digital frequency reduction

- Active burst mode for light load operation

- Built-in high voltage startup cell

- Built-in digital soft-start

- Cycle-by-cycle peak current limitation with built-in leading edge blanking time

- Foldback Point Correction with digitalized sensing and control circuits

- V<sub>CC</sub> undervoltage and overvoltage protection with Autorestart mode

- Over Load /open loop Protection with Autorestart mode

- Built-in Over temperature protection with Autorestart mode

- Adjustable output overvoltage protection with Latch mode

- Short-winding protection with Latch mode

- Maximum on time limitation

- Maximum switching period limitation

## 3.2.6 Synchronous Rectification MOSFETs OptiMOS™ BSC010N04LS

For the synchronous rectification stage the selected device is BSC010N04LS, from the latest OptiMOS™ 40 V family. SR is in fact naturally the best choice in high efficiency designs of low output voltage and high output current LLC, as in our case. In applications that target high efficiency both at light and heavy loads – such as 80PLUS® Titanium- while often requiring high power densities, it is critical to select SR MOSFETs that combine following key characteristics:

- Very low  $R_{DS(on)}$ : BSC010N04LS provides the industry's first  $1m\Omega$  40 V product in SuperSO8 package.

- Low gate charge Q<sub>g</sub>, which is important in order to minimize driving losses, with benefits on light load efficiency

- Very tight V<sub>GS(th)</sub> range: in fact, in case of paralleling this allows the MOSFETs to turn-on almost simultaneously. Selected OptiMOS<sup>™</sup> offer very close min and max of V<sub>GS(th)</sub>, respectively 1.2 and 2 V.

#### **Board description**

- Monolithically integrated Schottky like diode, in order to minimize the conduction losses on it.

- Package; BSC010N04LS in SuperSO8 with source fused leads is able to address all the typical crucial requirements for a suitable SR MOSFET package:

- Minimizing parasitic inductances

- Combining compact footprint with good power dissipation

- Enlarged source connection in order to minimize electro-migration occurrence.

## 3.3 Board schematic

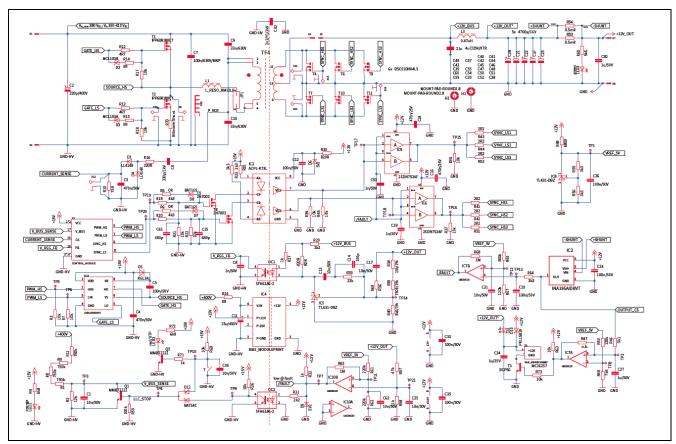

## 3.3.1 Mainboard schematic

Figure 9 Mainboard schematic

## **Board description**

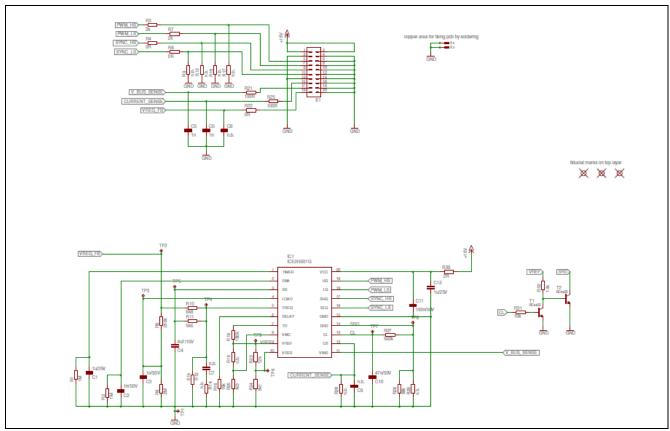

## 3.3.2 Control board schematic

Figure 10 Control board schematic

## **Board description**

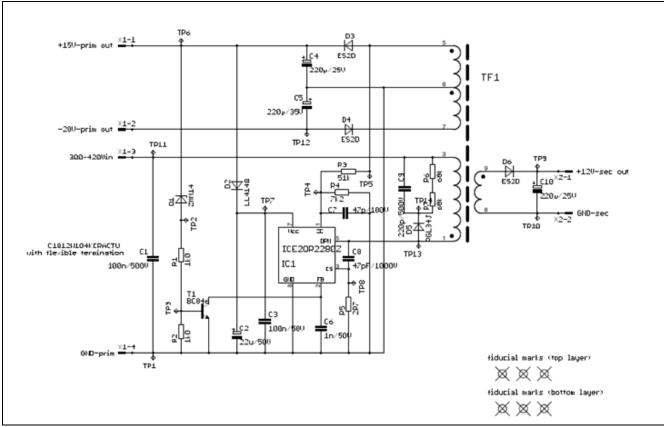

## 3.3.3 Biasboard schematic

Figure 11 Biasboard schematic

## **Board description**

Figure 12 Mainboard PCB with Control – and Bias Board

Typical characteristics with 600 V CoolMOS™ C7

# 4 Typical characteristics with 600 V CoolMOS™ C7

#### 4.1 Critical LLC operation - hard commutation

In LLC converter, hard commutation of the body diode normally only occurs during the start-up, burst mode, overload and short circuit condition. These conditions can be minimized if not avoided in the design using an analog controller with proper selection of resonant components and properly setting of the minimum and maximum operating frequency. Hard commutation happens in LLC during the commutation period of the body diode. During this time, resonant inductor current is flowing through body diode of the MOSFET creating ZVS condition upon this MOSFET's turn-on. When the current is not able to change its direction prior to the turn-on of the other MOSFET, more charges will remain in the P-N junction of that MOSFET. When the other MOSFET turns on, a large shoot-through current will flow due to the reverse-recovery current of the body diode. This results to a high reverse recovery peak current IRRM and high reverse recovery dv/dt which sometimes could result to a MOSFET breakdown.

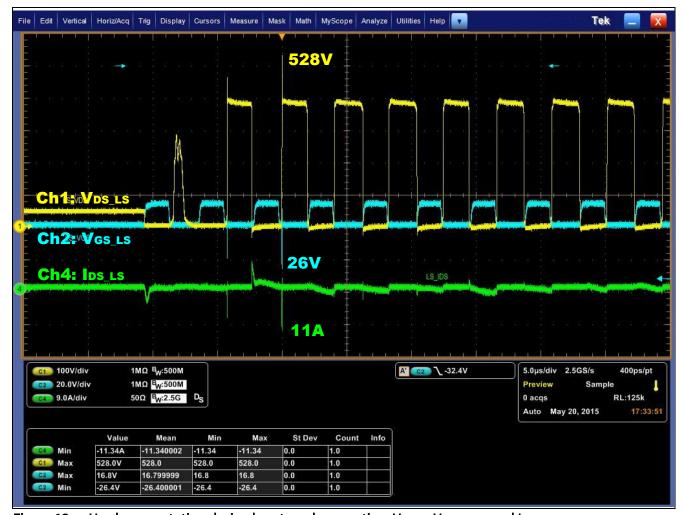

In this 600 W LLC analog controlled demonstration board, only the burst mode condition has the tendency of undergoing hard commutation. In Figure 13, hard commutation at burst mode is minimal that IPP60R180C7 was able to withstand without any problem.

Figure 13 Hard commutation during burst mode operation, VDS\_pk, VGS\_max/min and IRMM

#### Typical characteristics with 600 V CoolMOS™ C7

The voltage spike on the gate  $V_{GS}$  and drain  $V_{DS}$  can be influenced by varying both turn-on and turn-off gate resistors up to 10 ohm without affecting the efficiency, thanks to the switching behavior of the C7 technology.

Thanks to the very carefully design and control loop on this 600 W Analog LLC Demonstration board, there is neither during start-up nor for short-circuit condition any hard commutation observed.

#### 4.2 Full ZVS area

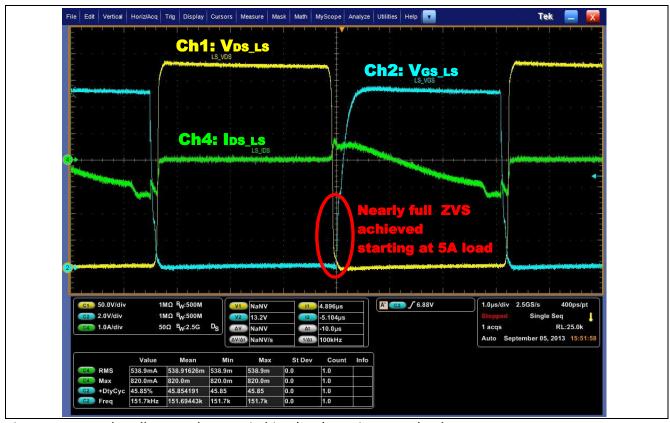

Nearly full ZVS is achieved on the entire output load range as shown in Figure 14.

Figure 14 Nearly Full Zero Voltage Switching (ZVS) starting at 5 A load

## 4.3 Burstmode operation

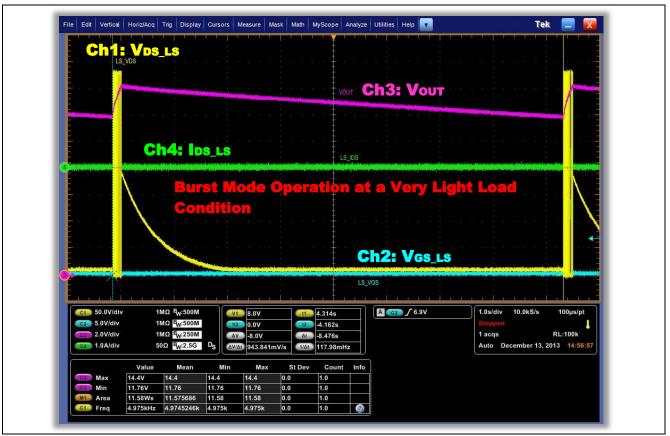

At no load or a very light load condition, LLC controller provides frequency approaching to its maximum setting. In this condition, in order to still achieve full ZVS, magnetizing current should be high enough to discharge the output capacitances. Due to magnetizing current limitation, switching loss especially turn-off loss is relatively high if the devices will continue to switch at the highest frequency. In order to overcome this phenomenon, burst mode function is enabled and implemented. This results to an effective lower switching losses and driving losses because of the low burst frequency. Additionally, this helps to achieve regulation even at no load condition. In Figure 15 one can see the waveform of Burst Mode Operation at no-load and/or very light load condition

Typical characteristics with 600 V CoolMOS™ C7

Figure 15 Burst Mode Operation at no-load and/or very light load condition

## 4.4 Efficiency

### 4.4.1 Titanium Efficiency

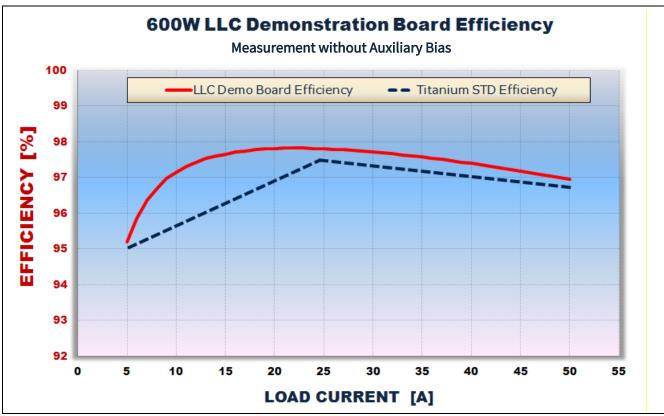

Figure 16 shows the efficiency comparison of this 600 W LLC evaluation board in relation to the Titanium Efficiency Standard. At the most important efficiency point (50% load), this LLC board offers 0.3 % efficiency benefit compared to the Titanium Efficiency Line.

Typical characteristics with 600 V CoolMOS™ C7

Figure 16 IFX 600 W LLC Demonstration Board Efficiency vs Titanium STD Efficiency

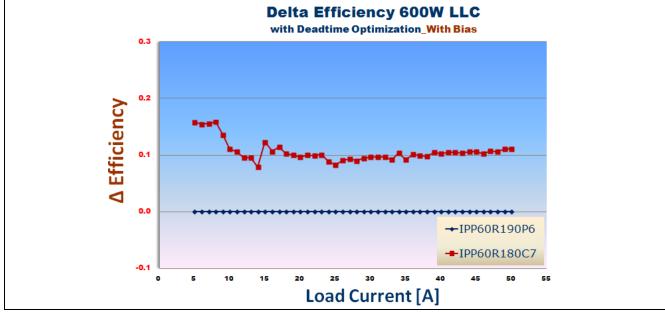

### 4.4.2 Efficiency comparison in resonant LLC Half Bridge

Figure 17 shows the efficiency comparison in a 600 W LLC circuit,  $V_{in}$ =380 V,  $V_{o}$ =12 V, running at resonant frequency  $f_{o}$ =157 kHz. The 0.1 % improvement across the load range is mostly related to the low turn off losses and the low  $C_{oss}$  dissipation, since other switching losses are minimal when operating at the resonant frequency. Furthermore, it's expected to gain more efficiency benefit when operating above the resonant frequency, where turn off losses start to engage.

Figure 17 Efficiency comparison in 600W LLC Half Bridge

Test/powerup procedure

# 5 Test/powerup procedure

Table 2 Test/Powerup procedure

| Test                                       | Test procedure                                                                                         | Condition                                      |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------|

| 1. Auxiliary Circuit Turn-On               | Apply 30 V <sub>DC</sub> on the input.                                                                 | V <sub>in</sub> : ~30 V <sub>DC</sub>          |

|                                            |                                                                                                        | Orange LED will light up                       |

| 2. LLC Converter Turn-On                   | Apply 350 V <sub>DC</sub> . Converter will give Vout =12 V <sub>DC</sub> .                             | V <sub>in</sub> : 350 V <sub>DC</sub>          |

|                                            |                                                                                                        | V <sub>out</sub> :12 V                         |

| 3. Operational switching frequency         | Using voltage probe, monitor switching frequency at following test conditions:                         | V <sub>in</sub> :380 V <sub>DC</sub>           |

|                                            |                                                                                                        | V <sub>out</sub> :12 V                         |

|                                            | @5 A Output Load 10%Load - ~<br>155 kHz*                                                               | lout: 5 A                                      |

|                                            | @25 A Output Load 50%Load - ~<br>142 kHz*                                                              | I <sub>out</sub> : 25 A                        |

|                                            | @50 A Output Load 100%Load - ~<br>132 kHz*                                                             | I <sub>out</sub> : 50 A                        |

|                                            | (*measure freq. at "Pri_LS_VGS"-connector)                                                             |                                                |

|                                            | [* +/-10 kHz]                                                                                          |                                                |

| 4. Fan enable                              | Switch the load from 50 A to 5 A.                                                                      | V <sub>in</sub> =380 V <sub>DC</sub>           |

|                                            | Increase the output load current from 11-14 A, fan should turn on.                                     | I <sub>out</sub> = 5 A                         |

|                                            |                                                                                                        | ÞFan is off                                    |

|                                            |                                                                                                        | V <sub>in</sub> =380 V <sub>DC</sub>           |

|                                            |                                                                                                        | I <sub>out</sub> = 11-14 A                     |

|                                            |                                                                                                        | ÞFan is on                                     |

| 5. Switch off Input Start-up at No         | Switch off the Input                                                                                   | V <sub>in</sub> = 0 V <sub>DC</sub>            |

| load                                       |                                                                                                        | I <sub>out</sub> = 0 A                         |

|                                            | Switch at 380 V <sub>DC</sub> on <b>no load output</b> . Operation should be in burst mode.            | V <sub>in</sub> =380 V <sub>DC</sub>           |

|                                            |                                                                                                        | I <sub>out</sub> = 0 A                         |

|                                            |                                                                                                        | V <sub>out</sub> = 11,5 – 12,5                 |

| 6. Switch off Input; Start-up at Full      | Switch off the Input                                                                                   | V <sub>in</sub> = 0 V <sub>DC</sub>            |

| load                                       |                                                                                                        | I <sub>out</sub> = 0A                          |

|                                            | Apply 380 V <sub>DC</sub> with full load @50 A                                                         | V <sub>in</sub> =380 V <sub>DC</sub>           |

|                                            | output. V <sub>out</sub> is in between 11.8 – 12.2 V <sub>DC</sub> * (*measure on the board-connector) | V <sub>out</sub> : 11,8 – 12,3 V <sub>DC</sub> |

|                                            |                                                                                                        | I <sub>out</sub> = 50 A                        |

| 7. Running No Load -> Output Short Circuit | Switch off load from $380  V_{DC}  50  A$ to $380  V_{DC}  0  A$ .                                     | $V_{in} = 380 V_{DC}$                          |

|                                            | Short circuit the load using the                                                                       | (after short circuit) $V_{out} = 0 V_{DC}$     |

|                                            | short circuit function of the eload. <b>Converter should latch.</b>                                    | I <sub>out</sub> = 0 A                         |

## Test/powerup procedure

| Test                                               | Test procedure                                                                                                                                                                                        | Condition                                                 |  |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|

| 8. Switch off Input & remove short circuit         | Switch off the Input.                                                                                                                                                                                 | V <sub>in</sub> = 0 V <sub>DC</sub>                       |  |

| 9. Running Full Load -> Over<br>Current Protection | Remove short circuit function on the load.                                                                                                                                                            | I <sub>out</sub> = 0 A                                    |  |

|                                                    | Apply 380 V <sub>DC</sub> 50 A with full load output. Increase the current on the output 1 A each step until the converter goes into protection starting from 50 A. OCP occurs between 55 A and 62 A. | V <sub>in</sub> =380 V <sub>DC</sub>                      |  |

|                                                    |                                                                                                                                                                                                       | I <sub>out</sub> = 50 A                                   |  |

|                                                    |                                                                                                                                                                                                       | OCP = between 55 A - 62 A                                 |  |

| 10. Running Full Load -> Output                    | Apply 380 V <sub>DC</sub> 50 A with full load                                                                                                                                                         | I <sub>out</sub> = 0 A                                    |  |

| Short Circuit                                      | output. Short circuit the load                                                                                                                                                                        | V <sub>in</sub> =380 V <sub>DC</sub>                      |  |

|                                                    | using the short circuit functions of the load. Converter should latch.                                                                                                                                | I <sub>out</sub> = 50 A                                   |  |

|                                                    | the load. Converter should tatch.                                                                                                                                                                     | (after short circuit) V <sub>out</sub> =0 V <sub>DC</sub> |  |

| 11. Switch off Input; Start- Up ->                 | Switch off the Input.                                                                                                                                                                                 | V <sub>in</sub> = 0 V <sub>DC</sub>                       |  |

| Output Short Circuit                               |                                                                                                                                                                                                       | I <sub>out</sub> = 0 A                                    |  |

|                                                    | Apply 380 V <sub>DC</sub> with output load short circuit. <i>Converter should be in hiccup/latch mode.</i>                                                                                            | V <sub>in</sub> =380 V <sub>DC</sub>                      |  |

|                                                    |                                                                                                                                                                                                       | I <sub>out</sub> = short circuit                          |  |

|                                                    |                                                                                                                                                                                                       | V <sub>out</sub> = 0 V short circuit<br>(hiccup/latch)    |  |

| 12. Switch off Input & remove short                | Switch off the Input.                                                                                                                                                                                 | V <sub>in</sub> = 0 V <sub>DC</sub>                       |  |

| circuit                                            | Remove short circuit function on the load.                                                                                                                                                            | I <sub>out</sub> = 0 A                                    |  |

| 13. Dynamic Loading                                | Apply 380 V <sub>DC</sub> . Set the electronic load to dynamic loading mode with the following settings:                                                                                              | $V_{in} = 380 V_{DC}$                                     |  |

|                                                    | CCDH1: lout 5 A                                                                                                                                                                                       | I <sub>out</sub> = 5 A50 A                                |  |

|                                                    | CCDH2: lout 50 A                                                                                                                                                                                      | $V_{out} = 11,5 - 12,5 V_{DC}$                            |  |

|                                                    | Dwell time: 10 ms                                                                                                                                                                                     |                                                           |  |

|                                                    | Load slew rate: 1 A/μS                                                                                                                                                                                |                                                           |  |

Useful material and links

## 6 Useful material and links

With the following links you can find more detailed information about the used devices from Infineon and the magnetic components.

Primary HV MOSFETs CoolMOS™ IPP60R180C7:

http://www.infineon.com/dgdl/Infineon-IPP60R180C7DS-v02 00-EN.pdf?fileId=5546d4624cb7f111014d483fe4ba707b

LLC Analog Controller ICE2HS01G

http://www.infineon.com/dgdl/ICE2HS01G PDS v2.1 20110524 Public.pdf?folderId=db3a304412b4079 50112b408e8c90004&fileId=db3a30432a40a650012a458289712b4c

Advanced Dual-Channel Gate Drive 2EDN7524F

http://www.infineon.com/dgdl/Infineon-2EDN752x 2EDN852x-DS-v01 00-EN.pdf?fileId=5546d4624cb7f111014d672f9fbb5142

Bias QR Flyback Controller ICE2QR2280Z

http://www.infineon.com/dgdl/Datasheet\_ICE2QR2280Z\_v21\_20110830.pdf?folderId=db3a304412b4079 50112b408e8c90004&fileId=db3a30432a7fedfc012a8d8038e00473

SR MOSFETs OptiMOS<sup>™</sup> BSC010N04LS

$\frac{http://www.infineon.com/dgdl/BSC010N04LS\ rev2.0.pdf?folderId=db3a304313b8b5a60113cee8763b02\ d7\&fileId=db3a3043353fdc16013552c1c63647c4$

• Main Transformer and Resonant Choke Ferrite Cores

http://en.tdk.eu/blob/519704/download/2/ferrites-and-accessories-data-book-130501.pdf

Half Bridge Gate Drive 2EDL05N06PF

http://www.infineon.com/cms/en/product/power/gate-driver/eicedrivershigh-voltage-gate-driver-ics-and-boards/gate-driver-ic-eicedriver-compact/2EDL05N06PF/power/gate-driver/2EDL05N06PF/power/gate-

driver/2EDL05N06PF/productType.html?productType=db3a30443e36c802013e3c260fb915fd

#### References

## 7 References

- [1] T. Fujihira: "Theory of Semiconductor Superjunction Devices", Jpn. J. Appl. Phys., Vol.36, pp. 6254-6262, 1997

- [2] Francesco Di Domenico and others: "Design of 600 W HB LLC Demo Board using 600 V CoolMOS™ P6", Infineon Technologies AN 2015

- [3] Lawrence Lin, Gary Chang: "Consideration of Primary side MOSFET Selection for LLC topology", Infineon Technologies AN 2014

- [4] Anders Lind: "LLC Converter Design Note", Infineon Technologies AN 2013-03

- [5] Liu Jianwei, Li Dong: "Design Guide for LLC Converter with ICE2HS01G", Infineon Technologies AN V1.0, July 2011

- [6] F. Stückler, S. Abdel-Rahman, K. Siu: "600 V CoolMOS™ C7 Design Guide", Infineon Technologies

List of abbreviations

# 8 List of abbreviations

#### Table 3 Abbreviation and symbols used

| Con                                   | internal gate drain capacitance C <sub>GD</sub> =C <sub>rss</sub>              |

|---------------------------------------|--------------------------------------------------------------------------------|

|                                       | input capacitance $C_{iss} = C_{GS} + C_{GD}$                                  |

|                                       | effective output capacitance                                                   |

|                                       | resonant capacitance                                                           |

| ·                                     | steepness of current slope at turn off / turn on                               |

|                                       | device under test                                                              |

|                                       | steepness of voltage slope at turn off / turn on                               |

|                                       | power loss during switch off                                                   |

| <del></del>                           | power loss during switch on                                                    |

|                                       | energy in output capacitance (C <sub>oss</sub> ) at typ. V <sub>DS</sub> =400V |

|                                       | First Harmonic Approximation Method                                            |

|                                       | Figures of Merit                                                               |

|                                       | resonand frequency                                                             |

| •                                     | drain current                                                                  |

| <del>-</del>                          | effective root mean square current                                             |

|                                       | magnatizing current                                                            |

|                                       | peak current                                                                   |

| 4                                     | gain factor                                                                    |

|                                       | resonant inductance                                                            |

| •                                     | magnatizing inductance                                                         |

| · · · · · · · · · · · · · · · · · · · | voltage gain                                                                   |

|                                       | primary winding                                                                |

| r                                     | secondary winding                                                              |

| •                                     | transformer turn ratio                                                         |

|                                       | metal oxide semiconductor field effect transistor                              |

|                                       | synchronos conduction losses                                                   |

|                                       | power factor correction                                                        |

|                                       | bipolar transistor type (pnp vs. npn)                                          |

|                                       | Charge stored in the Coss                                                      |

| Q                                     | quality factor                                                                 |

|                                       | total equivalent resistor                                                      |

| R <sub>DS(on)</sub>                   | drain-source on-state resistance                                               |

| R <sub>g,tot</sub>                    | total gate resistor                                                            |

| R <sub>o</sub>                        | output resistor                                                                |

| R <sub>th</sub>                       | thermal resistor                                                               |

|                                       | dead time                                                                      |

| t <sub>ecs</sub>                      | early channel shut down time                                                   |

| V <sub>DS</sub>                       | drain to source voltage, drain to source voltage                               |

| V <sub>gsth</sub>                     | drain to source threshold voltage                                              |

| V <sub>O_AC</sub>                     | output voltage, alternating current                                            |

| V <sub>In_AC</sub>                    | input voltage, alternating current                                             |

|                                       |                                                                                |

#### List of abbreviations

| V <sub>In_nom</sub>  | nominale input voltage |

|----------------------|------------------------|

| V <sub>out_nom</sub> | nominale output        |

| zcs                  | zero current switching |

| ZVS                  | zero voltage switching |

# **Revision History**

## Major changes since the last revision

| Page or Reference | Description of change          |

|-------------------|--------------------------------|

|                   | First Release                  |

| Revision 1.1      | Update on Layout and Structure |

| Revision 1.2      | Update on Section 3.2.4        |

|                   |                                |

#### **Trademarks of Infineon Technologies AG**

AURIX™, C166™, CanPAK™, CIPOS™, CIPURSE™, CoolGan™, CoolMOS™, CoolSet™, CoolSic™, CORECONTROL™, CROSSAVE™, DAVE™, DI-POL™, DrBLADE™, EasyPIM™, EconoBRIDGE™, EconoDUAL™, EconoPACK™, EconoPIM™, EiceDRIVER™, eupec™, FCOS™, HITFET™, HybridPACK™, ISOFACE™, IsoPACK™, i-Wafer™, MIPAQ™, ModSTACK™, my-d™, NovalithIC™, OmniTune™, OPTIGA™, OptiMOS™, ORIGA™, POWERCODE™, PRIMARION™, PrimePACK™, PrimeSTACK™, PROFET™, PRO-SIL™, RASIC™, REAL3™, ReverSave™, SatRIC™, SIEGET™, SIPMOS™, SmartLEWIS™, SOLID FLASH™, SPOC™, TEMPFET™, thinQ!™, TRENCHSTOP™, TriCore™.

#### Other Trademarks

Other Trademarks

Advance Design System™ (ADS) of Agilent Technologies, AMBA™, ARM™, MULTI-ICE™, KEIL™, PRIMECELL™, REALVIEW™, THUMB™, µVision™ of ARM Limited, UK. ANSI™ of American National Standards Institute. AUTOSAR™ of AUTOSAR development partnership. Bluetooth™ of Bluetooth SIG Inc. CATiq™ of DECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO™ of Microsoft Corporation. HYPERTERMINAL™ of Hilgraeve Incorporated. MCS™ of Intel Corp. IEC™ of Commission Electrotechnique Internationale. IrDA™ of Infrared Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC™, NUCLEUS™ of Mentor Graphics Corporation. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of OmniVision Technologies, Inc. Openwave™ of Openwave Systems Inc. RED HAT™ of Red Hat, Inc. RFMD™ of RF Micro Devices, Inc. SIRIUS™ of Sirius Satellite Radio Inc. SOLARIS™ of Sun Microsystems, Inc. SPANSION™ of Spansion LLC Ltd. Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas Instruments Incorporated. VXWORKS™, WIND RIVER™ of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes Zetex Limited.

Last Trademarks Update 2014-07-17

#### www.infineon.com

Edition 2015-05-01 Published by Infineon Technologies AG 81726 Munich, Germany

© 2015 Infineon Technologies AG. All Rights Reserved.

Do you have a question about any aspect of this document?

Email: erratum@infineon.com

Document reference AN\_201411\_PL52\_007

#### Legal Disclaimer

THE INFORMATION GIVEN IN THIS APPLICATION NOTE (INCLUDING BUT NOT LIMITED TO CONTENTS OF REFERENCED WEBSITES) IS GIVEN AS A HINT FOR THE IMPLEMENTATION OF THE INFINEON TECHNOLOGIES COMPONENT ONLY AND SHALL NOT BE REGARDED AS ANY DESCRIPTION OR WARRANTY OF A CERTAIN FUNCTIONALITY, CONDITION OR QUALITY OF THE INFINEON TECHNOLOGIES COMPONENT. THE RECIPIENT OF THIS APPLICATION NOTE MUST VERIFY ANY FUNCTION DESCRIBED HEREIN IN THE VERIFY ANY FUNCTION DESCRIBED HEREIN IN THE

REAL APPLICATION. INFINEON TECHNOLOGIES

HEREBY DISCLAIMS ANY AND ALL WARRANTIES

AND LIABILITIES OF ANY KIND (INCLUDING

WITHOUT LIMITATION WARRANTIES OF NONINFRINGEMENT OF INTELLECTUAL PROPERTY

RIGHTS OF ANY THIRD PARTY) WITH RESPECT TO ANY AND ALL INFORMATION GIVEN IN THIS APPLICATION NOTE.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office. Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# 单击下面可查看定价,库存,交付和生命周期等信息

>>Infineon(英飞凌)