Sensors

#### **Edition 2009-09**

Published by Infineon Technologies AG, Am Campeon 1-12, 85579 Neubiberg, Germany © Infineon Technologies AG 2009. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### **Warnings**

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| Revision History: 2 |          | 2009-09                               | Rev 1.1 |

|---------------------|----------|---------------------------------------|---------|

| Previous V          | ersion:  | Data Sheet Rev 1.0                    |         |

| Page                | Subjects | (major changes since last revision)   |         |

| Page 13             | Table 4: | Footnote 3) adapted                   |         |

| Page 15             | Table 5: | Sensitivity drift description adapted |         |

| Page 15             | Table 5: | Footnote 3) adapted                   |         |

| Page 25             | Table 14 | Footnote 1) and 2) adapted            |         |

| General             | Package  | nomenclature changed to PG-SSO-3-92   |         |

|                     |          |                                       |         |

|                     |          |                                       |         |

|                     |          |                                       |         |

|                     |          |                                       |         |

|                     |          |                                       |         |

# **We Listen to Your Comments**

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

sensors@infineon.com

| <b>1</b><br>1.1<br>1.2<br>1.3        | Overview          Features          Target Applications          Pin Configuration                                               | . 6<br>. 7           |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------|

| <b>2</b><br>2.1<br>2.2<br>2.3<br>2.4 | General Block Diagram Functional Description Principle of Operation Transfer Functions                                           | . 8<br>. 8<br>. 9    |

| 3                                    | Maximum Ratings                                                                                                                  | 11                   |

| 4                                    | Operating Range                                                                                                                  | 12                   |

| 5                                    | Electrical, Thermal, and Magnetic Parameters                                                                                     | 15                   |

| 6                                    | Signal Processing                                                                                                                | 17                   |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5      | Magnetic Field Ranges Gain Setting Offset Setting DSP Input Low-Pass Filter Clamping                                             | 18<br>19<br>19<br>20 |

| <b>7</b><br>7.1<br>7.2               | Error Detection                                                                                                                  | 24                   |

| <b>8</b><br>8.1                      | Temperature Compensation                                                                                                         |                      |

| 9<br>9.1<br>9.2<br>9.3<br>9.4        | Calibration Calibration Data Memory Programming Interface Data Transfer Protocol Programming of Sensors with Common Supply Lines | 28<br>29<br>29       |

| 10                                   | Application Circuit                                                                                                              | 30                   |

| 11                                   | PG-SSO-3-92 Package Outlines                                                                                                     | 31                   |

| <b>12</b><br>12.1<br>12.2<br>12.3    | SPC Output Definition  Basic SPC Protocol Definition  Unit Time Setup  Master Pulse Requirements                                 | 32<br>34             |

| 12.4 | Synchronous Transmission                           | 37 |

|------|----------------------------------------------------|----|

| 12.5 | Synchronous Transmission Including Range Selection | 37 |

| 12.6 | Synchronous Mode with ID Selection                 | 38 |

| 12.7 | Checksum Nibble Details                            | 41 |

Data Sheet 5 Rev 1.1, 2009-09

### **Programmable Linear Hall Sensor**

#### **TLE4998C3C**

### 1 Overview

### 1.1 Features

- SPC (Short PWM Code) protocol with enhanced interface features based on SENT (Single Edge Nibble Transmission, defined by SAE J2716)

- 20-bit Digital Signal Processing (DSP)

- Digital temperature compensation

- 16-bit overall resolution

- Operates within automotive temperature range

- Low drift of output signal over temperature and lifetime

- Programmable parameters stored in EEPROM with single-bit error correction:

- SPC protocol modes: synchronous transmission, dynamic range selection, ID selection mode

- SPC unit time

- Magnetic range and sensitivity (gain), polarity of the output slope

- Offset

- Bandwidth

- Clamping levels

- Customer temperature compensation coefficients

- Memory lock

- Re-programmable until memory lock

- Supply voltage 4.5 5.5 V (4.1 16 V extended range)

- Operation between -200 mT and +200 mT within three ranges

- Reverse-polarity and overvoltage protection for all pins

- Output short-circuit protection

- On-board diagnostics (overvoltage, EEPROM error, start up)

- Output of internal magnetic field values and temperature

- Programming and operation of multiple sensors with common power supply

- Two-point calibration of magnetic transfer function without iteration steps

- High immunity against mechanical stress, EMC, ESD

- Package with two capacitors: 47nF (VDD to GND) and 4.7nF (OUT to GND)

| Туре       | Marking | Ordering Code | Package     |

|------------|---------|---------------|-------------|

| TLE4998C3C | 98C3C   | SP000481482   | PG-SSO-3-92 |

Overview

### 1.2 Target Applications

- Robust replacement of potentiometers

- No mechanical abrasion

- Resistant to humidity, temperature, pollution and vibration

- Linear and angular position sensing in automotive applications such as pedal position, suspension control, throttle position, headlight levelling, and steering torque sensing

- Sensing of high current for battery management, motor control, and electronic fuses

### 1.3 Pin Configuration

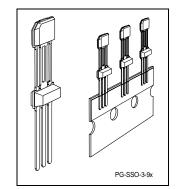

**Figure 1** shows the location of the Hall element in the chip and the distance between Hall probe and the surface of the package.

Figure 1 TLE4998x3C Pin Configuration and Hall Cell Location

Table 1 TLE4998C3C Pin Definitions and Functions

| Pin No. | Symbol | Function                               |

|---------|--------|----------------------------------------|

| 1       | VDD    | Supply voltage / programming interface |

| 2       | GND    | Ground                                 |

| 3       | OUT    | Output / programming interface         |

Data Sheet 7 Rev 1.1, 2009-09

General

### 2 General

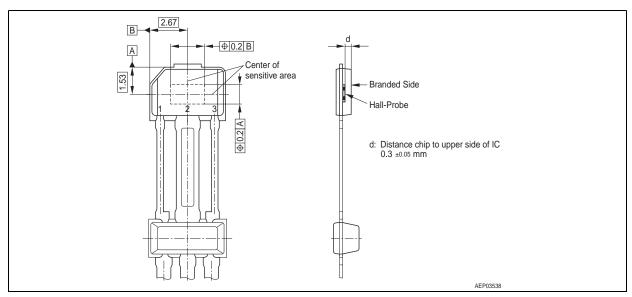

### 2.1 Block Diagram

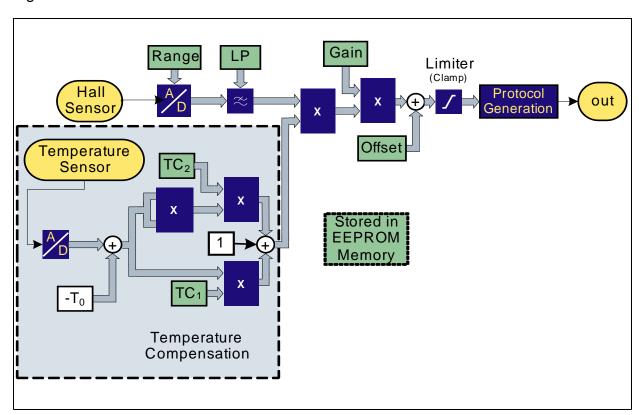

Figure 2 shows a simplified block diagram.

Figure 2 Block diagramm

# 2.2 Functional Description

The linear Hall IC TLE4998C3C has been designed specifically to meet the requirements of highly accurate angle and position detection as well as for current measurement applications. Two capacitors are integrated on the lead frame, making this sensor especially suitable for applications with demanding EMC requirements.

The sensor provides a digital SPC (Short PWM Code) signal, based on the standardized SENT (Single Edge Nibble Transmission, SAE J2716) protocol. The SPC protocol allows transmissions initiated by the ECU. Two further operation modes are available:

- "range selection" for dynamical switching of the measurement range during operation

- "ID selection" to build a bus system with up to 4 ICs on a single output line and a common supply, which can be individually accessed by the ECU.

Each transmission sequence contains an adjustable number of nibbles representing the magnetic field, the temperature value and a status information of the sensor. The

#### General

interface is further described in **Chapter 12**. The output stage is an open-drain driver pulling the output pin to low only. Therefore, the high level needs to be obtained by an external pull-up resistor. This output type has the advantage that the receiver may use an even lower supply voltage (e.g. 3.3 V). In this case the pull-up resistor must be connected to the given receiver supply.

The IC is produced in BiCMOS technology with high voltage capability, and it also has reverse-polarity protection.

Digital signal processing using a 16-bit DSP architecture together with digital temperature compensation guarantee excellent long-time stability compared to analog compensation methods.

While the overall resolution is 16 bits, some internal stages work with resolutions up to 20 bits.

### 2.3 Principle of Operation

- A magnetic flux is measured by a Hall-effect cell

- The output signal from the Hall-effect cell is converted from analog to digital

- The chopped Hall-effect cell and continuous-time A/D conversion ensure a very low and stable magnetic offset

- · A programmable low-pass filter to reduce noise

- The temperature is measured and A/D converted, too

- Temperature compensation is done digitally using a second-order function

- Digital processing of output value is based on zero field and sensitivity value

- The output value range can be clamped by digital limiters

- · The final output value is represented by the data nibbles of the SPC protocol

Data Sheet 9 Rev 1.1, 2009-09

General

#### 2.4 Transfer Functions

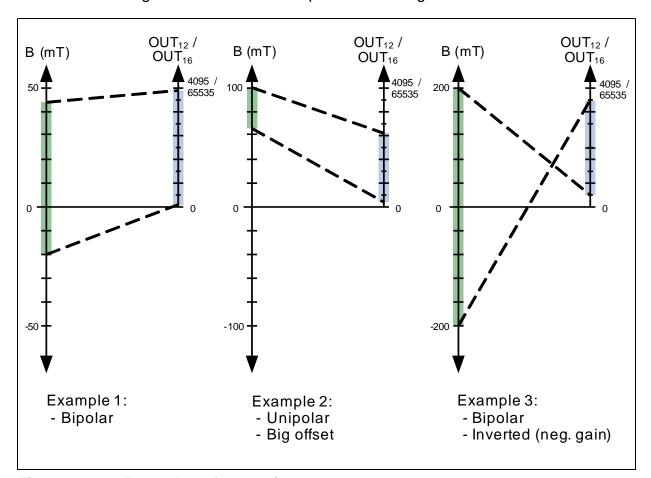

The examples in **Figure 3** show how different magnetic field ranges can be mapped to the desired output value ranges.

- Polarity Mode:

- Bipolar: Magnetic fields can be measured in both orientations. The limit points do not necessarily have to be symmetrical around the zero field point

- Unipolar: Only north- or south-oriented magnetic fields are measured

- Inversion: The gain can be set to both positive and negative values

Figure 3 Examples of Operation

Data Sheet 10 Rev 1.1, 2009-09

### **Maximum Ratings**

# 3 Maximum Ratings

Table 2 Absolute Maximum Ratings

| Parameter                                                                                                     | Symbol             | Limit            | Values            | Unit | Notes                                        |

|---------------------------------------------------------------------------------------------------------------|--------------------|------------------|-------------------|------|----------------------------------------------|

|                                                                                                               |                    | min.             | max.              |      |                                              |

| Storage temperature                                                                                           | $T_{ST}$           | - 40             | 150               | °C   |                                              |

| Junction temperature                                                                                          | $T_{J}$            | - 40             | 170 <sup>1)</sup> | °C   |                                              |

| $\begin{tabular}{lll} \hline & Voltage on $V_{\rm DD}$ pin with \\ respect to ground \\ \hline \end{tabular}$ | $V_{\mathrm{DD}}$  | -18              | 18                | V    | 2)                                           |

| Supply current  @ overvoltage V <sub>DD</sub> max.                                                            | I <sub>DDov</sub>  | -                | 15                | mA   |                                              |

| Reverse supply current @ V <sub>DD</sub> min.                                                                 | I <sub>DDrev</sub> | -1               | 0                 | mA   |                                              |

| Voltage on output pin with respect to ground                                                                  | V <sub>OUT</sub>   | -1 <sup>3)</sup> | 18 <sup>4)</sup>  | V    |                                              |

| Magnetic field                                                                                                | B <sub>MAX</sub>   | -                | unlimited         | Т    |                                              |

| ESD protection                                                                                                | V <sub>ESD</sub>   | -                | 8                 | kV   | According HBM<br>JESD22-A114-B <sup>5)</sup> |

<sup>1)</sup> For limited time of 96 h. Depends on customer temperature lifetime cycles. Please ask for support by Infineon

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>&</sup>lt;sup>2)</sup> Higher voltage stress than absolute maximum rating, e.g. 150% in latch-up tests is not applicable. In such cases,  $R_{\text{series}} \ge 100 \Omega$  for current limitation is required

<sup>3)</sup> I<sub>DD</sub> can exceed 10 mA when the voltage on OUT is pulled below -1 V (-5 V at room temperature)

<sup>4)</sup>  $V_{DD} = 5 \text{ V}$ , open drain permanent low, for max. 10 minutes

<sup>&</sup>lt;sup>5)</sup> 100 pF and 1.5 k $\Omega$

### **Operating Range**

# 4 Operating Range

The following operating conditions must not be exceeded in order to ensure correct operation of the TLE4998C3C. All parameters specified in the following sections refer to these operating conditions, unless otherwise indicated.

Table 3 Operating Range

| Parameter                            | Symbol               | Limit Values      |                          | Unit | Notes                                 |  |

|--------------------------------------|----------------------|-------------------|--------------------------|------|---------------------------------------|--|

|                                      |                      | min.              | min. max.                |      |                                       |  |

| Supply voltage                       | $V_{\mathrm{DD}}$    | 4.5               | 5.5                      | V    |                                       |  |

|                                      |                      | 4.1 <sup>1)</sup> | 16 <sup>2)</sup>         | V    | Extended range                        |  |

| Output pull-up voltage <sup>3)</sup> | V <sub>pull-up</sub> | -                 | 18                       | V    |                                       |  |

| Load resistance <sup>3)</sup>        | $R_{L}$              | 1                 | -                        | kΩ   |                                       |  |

| Output current <sup>3)</sup>         | I <sub>OUT</sub>     | 0                 | 5                        | mA   |                                       |  |

| Junction temperature                 | T <sub>J</sub>       | - 40              | 125<br>150 <sup>4)</sup> | °C   | For 5000 h<br>For 1000 h not additive |  |

<sup>1)</sup> For reduced output accuracy

Keeping signal levels within the limits specified in this table ensures operation without overload conditions.

Data Sheet 12 Rev 1.1, 2009-09

$<sup>^{2)}~</sup>$  For supply voltages > 12 V, a series resistance  $R_{series} \geq$  100  $\Omega$  is recommended

<sup>&</sup>lt;sup>3)</sup> Output protocol characteristics depend on these parameters, R<sub>L</sub> must be according to max. output current

<sup>4)</sup> For reduced magnetic accuracy; extended limits are taken for characteristics

# 5 Electrical, Thermal, and Magnetic Parameters

Table 4 Electrical Characteristics

| Parameter                                    | Symbol               | Limit | Value      | es         | Unit              | Notes                                                          |

|----------------------------------------------|----------------------|-------|------------|------------|-------------------|----------------------------------------------------------------|

|                                              |                      | min.  | typ.       | max.       |                   |                                                                |

| VDD-GND capacitor                            | $C_{VDD}$            | -     | 47         | -          | nF                | Ceramic                                                        |

| OUT-GND capacitor                            | $C_{L}$              | -     | 4.7        | -          | nF                | Ceramic                                                        |

| SPC transmission time                        | t <sub>SPC</sub>     | -     | -          | 1          | ms                | Unit time 3µs <sup>1)</sup>                                    |

| Supply current                               | I <sub>DD</sub>      | 3     | 6          | 8          | mA                |                                                                |

| Output current @ OUT shorted to supply lines | I <sub>OUTsh</sub>   | -     | 95         | -          | mA                | V <sub>OUT</sub> = 5 V, max. 10 minutes                        |

| Thermal resistance                           | $R_{thJA}$           | -     | 190        | -          | K/W               | Junction to air                                                |

|                                              | $R_{thJC}$           | -     | 41         | -          | K/W               | Junction to case                                               |

| Power-on time <sup>2)</sup>                  | t <sub>Pon</sub>     | -     | 0.7<br>15  | 2<br>20    | ms                | ≤ ± 5% target out value<br>≤ ± 1% target out value             |

| Power-on reset level                         | $V_{DDpon}$          | -     | 3.6        | 4          | V                 |                                                                |

| Output impedance                             | $Z_{OUT}$            | 20    | 40         | 70         | kΩ                | 3)                                                             |

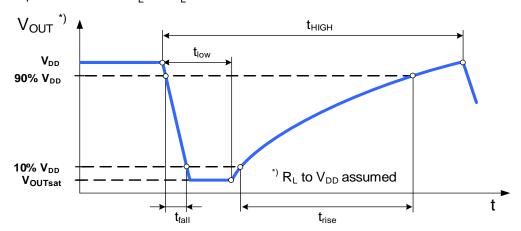

| Output fall time                             | $t_{fall}$           | 2     | -          | 4          | μs                | V <sub>OUT</sub> 4.5 V to 0.5 V <sup>4)</sup>                  |

| Output rise time                             | $t_{rise}$           | -     | 20         | -          | μs                | V <sub>OUT</sub> 0.5 V to 4.5 V <sup>4)5)</sup>                |

| Output low saturation voltage                | V <sub>OUTsat</sub>  | -     | 0.3<br>0.2 | 0.6<br>0.4 | V                 | $I_{OUTsink} = 5 \text{ mA}$<br>$I_{OUTsink} = 2.2 \text{ mA}$ |

| Output noise (rms)                           | OUT <sub>noise</sub> | -     | 1          | 2.5        | LSB <sub>12</sub> | 6)                                                             |

<sup>1)</sup> Transmission time depends on the data values being sent and on int. RC oscillator frequ. variation of +/- 20%

Data Sheet 13 Rev 1.1, 2009-09

Response time to set up output data at power on when a constant field is applied. The first value given has a ± 5% error, the second value has a ± 1% error. Measured with 640-Hz low-pass filter

<sup>3)</sup> Output impedance is measured  $\Delta V_{OUT}/\Delta I_{OUT}$  ( $\Delta V_{OUT}=12V$  ... 2.6V) at  $V_{DD}$  = 5V, open-drain high state

<sup>&</sup>lt;sup>4)</sup> For  $V_{DD}$  = 5 V,  $R_L$  = 2.2 k $\Omega$ ,  $C_L$  = 4.7 nF (in package), at room temperature, not considering condensator tolerance or influence of external circuitry

$^{5)}\,$  Depends on external R  $_L$  and C  $_L$

$^{6)}$  Range 100 mT, Gain 2.23, internal LP filter 244 Hz, B = 0 mT, T = 25 °C

Data Sheet 14 Rev 1.1, 2009-09

### **Calculation of the Junction Temperature**

The internal power dissipation  $P_{TOT}$  of the sensor increases the chip junction temperature above the ambient temperature.

The power multiplied by the total thermal resistance  $R_{thJA}$  (Junction to Ambient) added to  $T_A$  leads to the final junction temperature.  $R_{thJA}$  is the sum of the addition of the two components, *Junction to Case* and *Case to Ambient*.

$$\begin{split} R_{\text{thJA}} &= R_{\text{thJC}} + R_{\text{thCA}} \\ T_{\text{J}} &= T_{\text{A}} + \varDelta T \\ \varDelta T &= R_{\text{thJA}} \times \mathsf{P}_{\text{TOT}} = R_{\text{thJA}} \times (\ V_{\text{DD}} \times I_{\text{DD}} + V_{\text{OUT}} \times I_{\text{OUT}}) \\ &= I_{DD}, I_{OUT} > 0, \textit{if direction is into IC} \end{split}$$

Example (assuming no load on Vout):

- $V_{DD} = 5 \text{ V}$

- $-I_{DD} = 8 \text{ mA}$

- $\Delta T = 190 \text{ [K/W] x (5 [V] x 0.008 [A] + 0 [VA] )} = 7.6 \text{ K}$

For moulded sensors, the calculation with R<sub>th,IC</sub> is more adequate.

### **Magnetic Parameters**

Table 5

Magnetic Characteristics

| Parameter             | Symbol           | Limit ' | Values              |       | Unit                      | Notes                      |

|-----------------------|------------------|---------|---------------------|-------|---------------------------|----------------------------|

|                       |                  | min.    | typ.                | max.  |                           |                            |

| Sensitivity           | $S^{I)}$         | ± 8.2   | -                   | ± 245 | LSB <sub>12</sub> /<br>mT | Programmable <sup>2)</sup> |

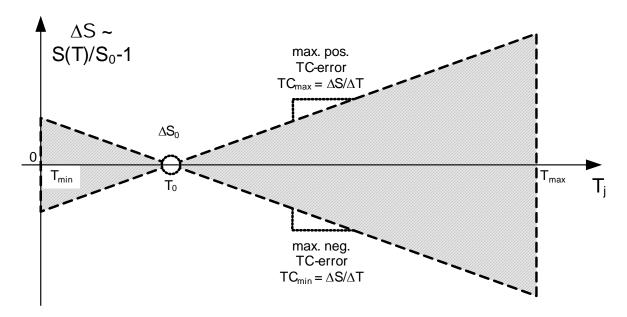

| Sensitivity drift     | $\Delta S$       | -       | ± 80                | ± 150 | ppm/                      | 3)                         |

|                       |                  |         |                     |       | °C                        | See Figure 4               |

| Magnetic field range  | MFR              | ± 50    | ± 100 <sup>4)</sup> | ± 200 | mT                        | Programmable <sup>5)</sup> |

| Integral nonlinearity | INL              | -       | ± 0.05              | ± 0.1 | %MFR                      | 6)8)                       |

| Magnetic offset       | Bos              | -       | -                   | ± 400 | μΤ                        | 7)8)                       |

| Magnetic offset drift | $\Delta B_{OS}$  | -       | ± 1                 | ± 5   | μT / °C                   | Error band <sup>8)</sup>   |

| Magnetic hysteresis   | B <sub>HYS</sub> | -       | -                   | 10    | μΤ                        | 9)                         |

<sup>1)</sup> Defined as ΔOUT / ΔB

Data Sheet 15 Rev 1.1, 2009-09

<sup>2)</sup> Programmable in steps of 0.024%

<sup>&</sup>lt;sup>3)</sup> For any 1<sup>st</sup> and 2<sup>nd</sup> order polynomial, coefficient within definition in Chapter 8. Valid for characterization at 0h

- 4) This range is also used for temperature and offset pre-calibration of the IC

- 5) Depending on offset and gain settings, the output may already be saturated at lower fields

- 6) Gain setup is 1.0

- 7) In operating temperature range and over lifetime

- 8) Measured at ± 100 mT range

- 9) Measured in 100 mT range, Gain = 1, room temperature

Figure 4 Sensitivity drift

Data Sheet 16 Rev 1.1, 2009-09

# 6 Signal Processing

The signal flow diagram in **Figure 5** shows the signal path and data-processing algorithm.

Figure 5 Signal Processing Flow

## **Magnetic Field Path**

- The analog output signal of the chopped Hall-effect cell is converted to a digital signal

in the continuous-time A/D converter. The range of the chopped A/D converter can be

set in several steps either by EEPROM settings or dynamically by the master in the

dynamic range mode (see Table 6). This gives a suitable level for the A/D converter

- After the A/D conversion, a digital low-pass filter reduces the bandwidth (Table 10)

- A multiplier amplifies the value depending on the gain (see Table 8) and temperature compensation settings

- The offset value is added (see Table 9)

- A limiter reduces the resulting signal to 16 bits (see Chapter 12) and feeds the Protocol Generation stage

#### **Temperature Compensation**

(Details are listed in Chapter 8)

The output signal of the temperature cell is also A/D converted

- The temperature is normalized by subtraction of the reference temperature T<sub>0</sub> value (zero point of the quadratic function)

- The linear path is multiplied with the TC<sub>1</sub> value

- In the quadratic path, the temperature difference to T<sub>0</sub> is squared and multiplied with the TC<sub>2</sub> value

- Both path outputs are added together and multiplied with the Gain value from the EEPROM

## 6.1 Magnetic Field Ranges

The working range of the magnetic field defines the input range of the A/D converter. It is always symmetrical around the zero field point. Any two points in the magnetic field range can be selected to be the end points of the output value. The output value is represented within the range between the two points.

In the case of fields higher than the range values, the output signal may be distorted. In case of synchronous mode and ID selection mode the range must be set accordingly (R=0/1/3) before the calibration of offset and gain.

Table 6 Range Setting

| Range | Range in mT <sup>1)</sup> | Parameter R     |

|-------|---------------------------|-----------------|

| Low   | ± 50                      | 3               |

| Mid   | ± 100                     | 1 <sup>2)</sup> |

| High  | ± 200                     | 0               |

<sup>1)</sup> Ranges do not have a guaranteed absolute accuracy. The temperature pre-calibration is performed in the mid range (100 mT)

Table 7 Range

| Parameter     | Symbol | Limit Values |      | Unit | Notes |

|---------------|--------|--------------|------|------|-------|

|               |        | min.         | max. |      |       |

| Register size | R      |              | 2    | bit  |       |

Data Sheet 18 Rev 1.1, 2009-09

<sup>2)</sup> Setting R = 2 is not used, internally changed to R = 1

### 6.2 Gain Setting

The overall sensitivity is defined by the range and the gain setting. The output of the ADC is multiplied with the Gain value.

Table 8 Gain

| Parameter               | Symbol | Limit Values |        | Unit | Notes                  |  |

|-------------------------|--------|--------------|--------|------|------------------------|--|

|                         |        | min.         | max.   |      |                        |  |

| Register size           | G      | 15           |        | bit  | Unsigned integer value |  |

| Gain range              | Gain   | - 4.0        | 3.9998 | -    | 1)2)                   |  |

| Gain quantization steps | ΔGain  | 244.14       |        | ppm  | Corresponds to 1/4096  |  |

<sup>1)</sup> For Gain values between - 0.5 and + 0.5, the numerical accuracy decreases

To obtain a flatter output curve, it is advisable to select a higher range setting

The Gain value can be calculated by:

$$Gain = \frac{(G - 16384)}{4096}$$

# 6.3 Offset Setting

The offset value corresponds to an output value with zero field at the sensor.

Table 9 Offset

| Parameter                 | Symbol            | Limit Values |       | Unit              | Notes                  |

|---------------------------|-------------------|--------------|-------|-------------------|------------------------|

|                           |                   | min.         | max.  |                   |                        |

| Register size             | OS                |              | 15    | bit               | Unsigned integer value |

| Offset range              | $OUT_{OS}$        | -16384       | 16383 | LSB <sub>12</sub> | 1)                     |

| Offset quantization steps | $\Delta OUT_{OS}$ |              | 1     | LSB <sub>12</sub> |                        |

<sup>1)</sup> Infineon pre-calibrates the samples at zero field to 50% output value (100 mT range), but does not guarantee the value. Therefore it is crucial to do a final calibration of each IC within the application

The offset value can be calculated by:

$$OUT_{OS} = OS - 16384$$

<sup>&</sup>lt;sup>2)</sup> A gain value of +1.0 corresponds to typical 32 LSB<sub>12</sub>/mT sensitivity (100 mT range, not guaranteed). It is crucial to do a final calibration of each IC within the application using the Gain/OUT<sub>OS</sub> value

# 6.4 DSP Input Low-Pass Filter

A digital low-pass filter is placed between the Hall A/D converter and the DSP, and can be used to reduce the noise level. The low-pass filter has a constant DC amplification of 0 dB (Gain of 1), which means that its setting has no influence on the internal Hall ADC value.

The bandwidth can be set to any of 8 values.

Table 10 Low Pass Filter Setting

| Note: Parameter LP | Cutoff frequency in Hz (-3dB point) <sup>1)</sup> |

|--------------------|---------------------------------------------------|

| 0                  | 80                                                |

| 1                  | 240                                               |

| 2                  | 440                                               |

| 3                  | 640                                               |

| 4                  | 860                                               |

| 5                  | 1100                                              |

| 6                  | 1390                                              |

| 7                  | off                                               |

<sup>1)</sup> As this is a digital filter running with an RC-based oscillator, the cutoff frequency may vary within ±20%

Table 11 Low-Pass Filter

| Parameter                  | Symbol     | Limit Values |      | Unit | Notes |

|----------------------------|------------|--------------|------|------|-------|

|                            |            | min.         | max. |      |       |

| Register size              | LP         |              | 3    | bit  |       |

| Corner frequency variation | $\Delta f$ | - 20         | + 20 | %    |       |

Note: In range 7 (filter off), the output noise increases.

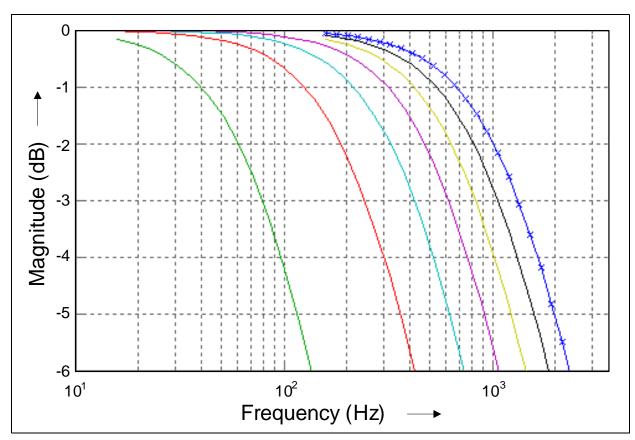

**Figure 6** shows the filter characteristics as a magnitude plot (the highest setting is marked). The "off" position would be a flat 0 dB line. The update rate after the low-pass filter is 16 kHz.

Figure 6 DSP Input Filter (Magnitude Plot)

Data Sheet 21 Rev 1.1, 2009-09

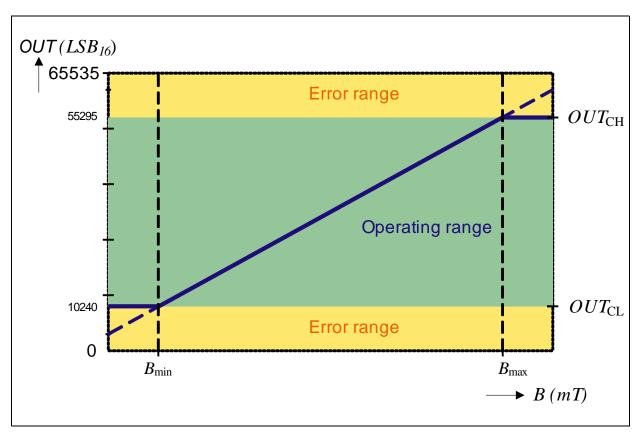

### 6.5 Clamping

The clamping function is useful for separating the output range into an operating range and error ranges. If the magnetic field is exceeding the selected measurement range, the output value OUT is limited to the clamping values. Any value in the error range is interpreted as an error by the sensor counterpart.

Table 12 Clamping

| Parameter                   | Symbol             | Limit Values |       | Unit              | Notes |

|-----------------------------|--------------------|--------------|-------|-------------------|-------|

|                             |                    | min.         | max.  |                   |       |

| Register size               | CL,CH              | 2            | 2 x 6 | bit               | (063) |

| Clamping value low          | $OUT_{CL}$         | 0            | 64512 | LSB <sub>16</sub> | 1)    |

| Clamping value high         | $OUT_{CH}$         | 1023         | 65535 | LSB <sub>16</sub> | 1) 2) |

| Clamping quantization steps | △OUT <sub>Cx</sub> | 1024         |       | LSB <sub>16</sub> | 3)    |

<sup>1)</sup> For CL = 0 and CH = 63 the clamping function is disabled

The clamping values are calculated by:

Clamping value low (deactivated if CL=0):

$$OUT_{CL} = CL \cdot 64 \cdot 16$$

Clamping value high (deactivated if CH=63):

$$OUT_{\rm CH} = (\rm CH + 1) \cdot 64 \cdot 16 - 1$$

<sup>2)</sup> OUT<sub>CL</sub> < OUT<sub>CH</sub> mandatory

$<sup>^{3)}</sup>$  Quantization starts for CL at 0 LSB<sub>16</sub> and for CH at 65535 LSB<sub>16</sub>

**Figure 7** shows an example in which the magnetic field range between  $B_{\rm min}$  and  $B_{\rm max}$  is mapped to output values between 10240 LSB<sub>16</sub> and 55295 LSB<sub>16</sub>.

Figure 7 Clamping Example

Note: The clamping high value must be above the low value.

Data Sheet 23 Rev 1.1, 2009-09

#### **Error Detection**

### 7 Error Detection

Different error cases can be detected by the On-Board Diagnostics (OBD) and reported to the microcontroller in the status nibble (see **Chapter 12**).

### 7.1 Voltages Outside the Operating Range

The output signals an error condition if  $V_{\rm DD}$  crosses the overvoltage threshold level.

Table 13 Overvoltage

| Parameter             | Symbol     | Limit Values |      |       | Unit | Notes |

|-----------------------|------------|--------------|------|-------|------|-------|

|                       |            | min.         | typ. | max.  |      |       |

| Overvoltage threshold | $V_{DDov}$ | 16.65        | 17.5 | 18.35 | V    | 1)    |

<sup>1)</sup> Overvoltage bit activated in status nibble, output stays in "off" state (high ohmic)

#### 7.2 EEPROM Error Correction

The parity method is able to correct a single bit in the EEPROM line. One other single bit error in another EEPROM line can also be detected, but not corrected. In an uncorrectable EEPROM failure, the open drain stage is disabled and kept in the off state permanently (high ohmic/sensor defect).

Data Sheet 24 Rev 1.1, 2009-09

### **Temperature Compensation**

# **8** Temperature Compensation

The magnetic field strength of a magnet depends on the temperature. This material constant is specific for the different magnet types. Therefore, the TLE4998C3C offers a second-order temperature compensation polynomial, by which the Hall signal output is multiplied in the DSP. There are three parameters for the compensation:

- Reference temperature T<sub>0</sub>

- A linear part (1<sup>st</sup> order) TC<sub>1</sub>

- A quadratic part (2<sup>nd</sup> order) TC<sub>2</sub>

The following formula describes the sensitivity dependent on the temperature in relation to the sensitivity at the reference temperature  $T_0$ :

$$S_{\text{TC}}(T) = 1 + TC_1 \times (T - T_0) + TC_2 \times (T - T_0)^2$$

For more information, please refer to the signal processing flow in Figure 5.

The full temperature compensation of the complete system is done in two steps:

#### 1. Pre-calibration in the Infineon final test

The parameters TC1, TC2, T0 are set to maximally flat temperature characteristics with respect to the Hall probe and internal analog processing parts.

#### 2. Overall system calibration

The typical coefficients TC1, TC2, T0 of the magnetic circuitry are programmed. This can be done deterministically, as the algorithm of the DSP is fully reproducible. The final setting of the TC1, TC2, T0 values depend on the pre-calibrated values.

**Table 14** Temperature Compensation

| Parameter                                | Symbol  | Limit Values |      | Unit     | Notes                   |

|------------------------------------------|---------|--------------|------|----------|-------------------------|

|                                          |         | min.         | max. |          |                         |

| Register size TC <sub>1</sub>            | TL      | -            | 9    | bit      | Unsigned integer values |

| $1^{st}$ order coefficient $TC_1$        | $TC_1$  | -1000        | 2500 | ppm/ °C  | 1)                      |

| Quantization steps of TC <sub>1</sub>    | $qTC_1$ | 15.26        |      | ppm/ °C  |                         |

| Register size TC <sub>2</sub>            | TQ      | -            | 8    | bit      | Unsigned integer values |

| $2^{\text{nd}}$ order coefficient $TC_2$ | $TC_2$  | - 4          | 4    | ppm/ °C² | 2)                      |

| Quantization steps of $TC_2$             | $qTC_2$ | 0.1          | 19   | ppm/ °C2 |                         |

| Reference temp.                          | $T_0$   | - 48         | 64   | °C       |                         |

| Quantization steps of $T_0$              | $qT_0$  | ,            | 1    | °C       | 3)                      |

<sup>1)</sup> Relative range to Infineon TC1 temperature pre-calibration, the maximum adjustable range is limited by the register-size and depends on specific pre-calibrated TL setting, full adjustable range: -2441 to +5355 ppm/°C

Data Sheet 25 Rev 1.1, 2009-09

<sup>&</sup>lt;sup>2)</sup> Relative range to Infineon TC2 temperature pre-calibration, the maximum adjustable range is limited by the register-size and depends on specific pre-calibrated TQ setting, full adjustable range: -15 to +15 ppm/°C<sup>2</sup>

### **Temperature Compensation**

3) Handled by algorithm only (see Application Note)

### 8.1 Parameter Calculation

The parameters TC<sub>1</sub> and TC<sub>2</sub> may be calculated by:

$$TC_1 = \frac{TL - 160}{65536} \times 1000000$$

$$TC_2 = \frac{TQ - 128}{8388608} \times 1000000$$

Now the digital output for a given field  $B_{IN}$  at a specific temperature can be calculated by:

$$OUT = 2 \cdot \left(\frac{B_{\text{IN}}}{B_{\text{FSR}}} \times S_{\text{TC}} \times S_{\text{TCHall}} \times S_0 \times 4096\right) + OUT_{\text{OS}}$$

$B_{FSR}$  is the full-range magnetic field. It is dependent on the range setting (e.g 100 mT).  $S_0$  is the nominal sensitivity of the Hall probe times the Gain factor set in the EEPROM.  $S_{TC}$  is the temperature-dependent sensitivity factor calculated by the DSP.

S<sub>TCHall</sub> is the temperature behavior of the Hall probe.

The pre-calibration at Infineon is performed such that the following condition is met:

$$S_{\text{TC}}(T_{\text{J}} - T_{0}) \times S_{\text{TCHall}}(T_{\text{J}}) \approx 1$$

Within the application, an additional factor  $B_{\rm IN}({\rm T})$  /  $B_{\rm IN}({\rm T}_0)$  is given due to the magnetic system.  $S_{\rm TC}$  then needs to be modified to  $S_{\rm TCnew}$  so that the following condition is satisfied:

$$\frac{B_{\rm IN}(T)}{B_{\rm IN}(T_0)} \times S_{\rm TCnew}(T) \times S_{\rm TCHall}(T) \approx S_{\rm TC}(T) \times S_{\rm TCHall}(T) \approx 1$$

Therefore, the new sensitivity parameters  $S_{\mathsf{TCnew}}$  can be calculated from the precalibrated setup  $S_{\mathsf{TC}}$  using the relationship:

$$\frac{B_{\rm IN}(T)}{B_{\rm IN}(T_0)} \times S_{\rm TCnew}(T) \approx S_{\rm TC}(T)$$

Data Sheet 26 Rev 1.1, 2009-09

#### Calibration

### 9 Calibration

For the calibration of the sensor, a special hardware interface to a PC is required. All calibration and setting bits can be temporarily written into a Random Access Memory (RAM). This allows the EEPROM to remain untouched during the entire calibration process, since the number of the EEPROM programming cycles is limited. Therefore, this temporary setup (using the RAM only) does not stress the EEPROM.

The digital signal processing is completely deterministic. This allows a two-point calibration to be performed in one step without iterations. After measuring the Hall output signal for the two end points, the signal processing parameters Gain and Offset can be calculated.

**Table 15** Calibration Characteristics

| Parameter                          | Symbol               | Limit Values |      | Limit Values      |            | Unit | Notes |

|------------------------------------|----------------------|--------------|------|-------------------|------------|------|-------|

|                                    |                      | min.         | max. |                   |            |      |       |

| Ambient temperature at calibration | $T_{CAL}$            | 10           | 30   | °C                |            |      |       |

| 2 point Calibration                | △OUT <sub>CAL1</sub> | -8           | 8    | LSB <sub>12</sub> | Position 1 |      |       |

| accuracy <sup>1)</sup>             | △OUT <sub>CAL2</sub> | -8           | 8    | LSB <sub>12</sub> | Position 2 |      |       |

<sup>1)</sup> Corresponds to  $\pm$  0.2% accuracy in each position

#### Calibration

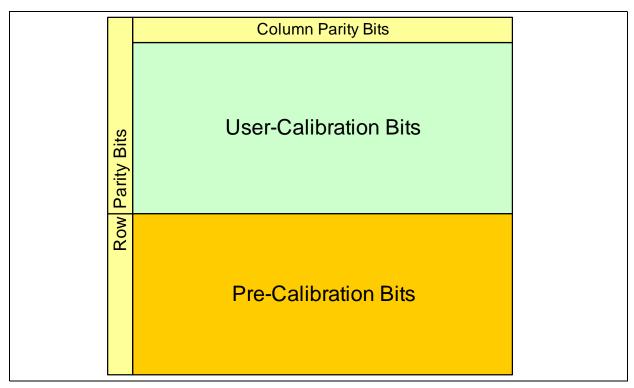

### 9.1 Calibration Data Memory

When the MEMLOCK bits are programmed (two redundant bits), the memory content is frozen and may no longer be changed. Furthermore, the programming interface is locked out and the chip remains in application mode only, preventing accidental programming due to environmental influences.

Figure 8 EEPROM Map

A matrix parity architecture allows automatic correction of any single-bit error. Each row is protected by a row parity bit. The sum of bits set (including this bit) must be an odd number (ODD PARITY). Each column is additionally protected by a column parity bit. Each bit in the even positions (0, 2, etc.) of all lines must sum up to an even number (EVEN PARITY), and each bit in the odd positions (1, 3, etc.) must have an odd sum (ODD PARITY). The parity column must have an even sum (EVEN PARITY).

This system of different parity calculations also protects against many block errors (such as erasing a full line or even the whole EEPROM).

When modifying the application bits (such as Gain, Offset, TC, etc.), the parity bits must be updated. As for the column bits, the pre-calibration area must be read out and considered for correct parity generation as well.

Note: A specific programming algorithm must be followed to ensure data retention.

A detailed separate programming specification is available on request.

#### **Calibration**

**Table 16** Programming Characteristics

| Parameter                           | Symbol           | Limit Values |      | Unit                 | Notes                                         |  |

|-------------------------------------|------------------|--------------|------|----------------------|-----------------------------------------------|--|

|                                     |                  | min.         | max. |                      |                                               |  |

| Number of EEPROM programming cycles | $N_{PRG}$        | -            | 10   | Cycles <sup>1)</sup> | Programming allowed only at start of lifetime |  |

| Ambient temperature at programming  | $T_{PRG}$        | 10           | 30   | °C                   |                                               |  |

| Programming time                    | t <sub>PRG</sub> | 100          | -    | ms                   | For complete memory <sup>2)</sup>             |  |

| Calibration memory                  | -                | 150          |      | Bit                  | All active EEPROM bits                        |  |

| Error Correction                    | -                | 26           |      | Bit                  | All parity EEPROM bits                        |  |

<sup>1) 1</sup> cycle is the simultaneous change of  $\geq$  1 bit

### 9.2 Programming Interface

The VDD pin and the OUT pin are used as a two-wire interface to transmit the EEPROM data to and from the sensor.

#### This allows:

- Communication with high data reliability, parity protected

- The bus-type connection of several sensors and separate programming via the OUT pin

#### 9.3 Data Transfer Protocol

The data transfer protocol is described in a separate document (User Programming Description), available on request.

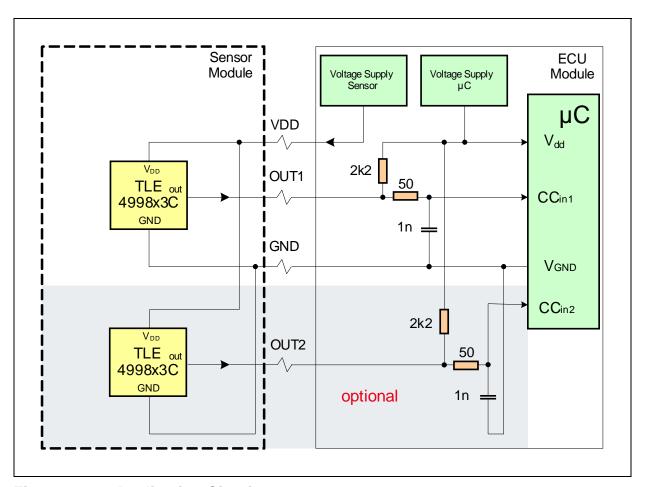

# 9.4 Programming of Sensors with Common Supply Lines

In many automotive applications, two sensors are used to measure the same parameter.

This redundancy makes it possible to continue operation in an emergency mode. If both sensors use the same power supply lines, they can be programmed together in parallel.

<sup>&</sup>lt;sup>2)</sup> Depending on clock frequency at V<sub>DD</sub>, write pulse 10 ms ±1%, erase pulse 80 ms ±1%

### **Application Circuit**

# 10 Application Circuit

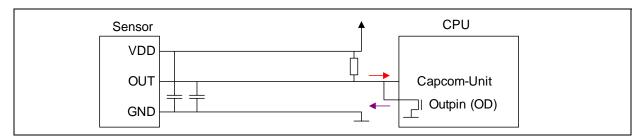

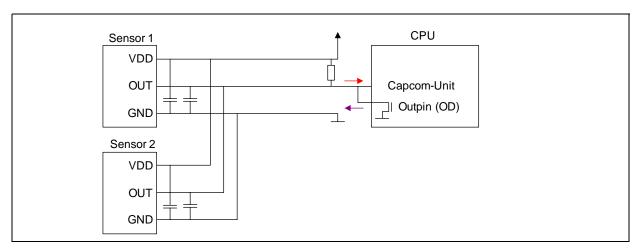

Figure 9 shows the connection of multiple sensors to a microcontroller.

Figure 9 Application Circuit

Note: For calibration and programming, the interface has to be connected directly to the OUT pin.

The application circuit shown should be regarded as an example only. It will need to be adapted to meet the requirements of other specific applications. Further information is given in **Chapter 12**.

Data Sheet 30 Rev 1.1, 2009-09

# **PG-SSO-3-92 Package Outlines**

# 11 PG-SSO-3-92 Package Outlines

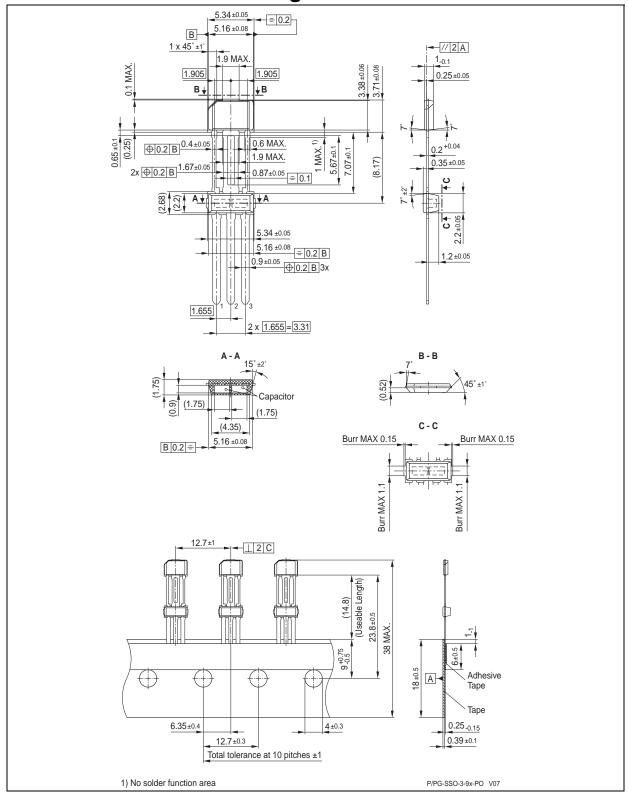

Figure 10 PG-SSO-3-92 (Plastic Green Single Small Outline Package)

# 12 SPC Output Definition

The sensor supports a SPC (Short PWM Code) protocol, which enhances the standardized SENT protocol (Single Edge Nibble Transmission) defined by SAE J2716. SPC enables the use of enhanced protocol functionality due to the ability to select between "synchronous", "range selection" and "ID selection" protocol mode. The following tables give an overview of relevant registers to chose the appropriate SPC mode.

Table 17 SPC Mode Registers

| Parameter         | Symbol | Limit Values |      | Limit Values |    | Unit | Notes |

|-------------------|--------|--------------|------|--------------|----|------|-------|

|                   |        | min.         | max. |              |    |      |       |

| Protocol register | P      |              | 2    | bit          |    |      |       |

| ID register       | ID     |              | 2    | bit          | 1) |      |       |

<sup>1)</sup> The ID register is only actively used in ID selection mode.

Table 18 SPC Mode Selection

| Mode                    | Parameter P <sub>MSB</sub> | Parameter P <sub>LSB</sub> | Explanation  |

|-------------------------|----------------------------|----------------------------|--------------|

| Synchronous             | 0                          | No effect                  | Section 12.4 |

| Dynamic range selection | 1                          | 0                          | Section 12.5 |

| ID selection            | 1                          | 1                          | Section 12.6 |

### 12.1 Basic SPC Protocol Definition

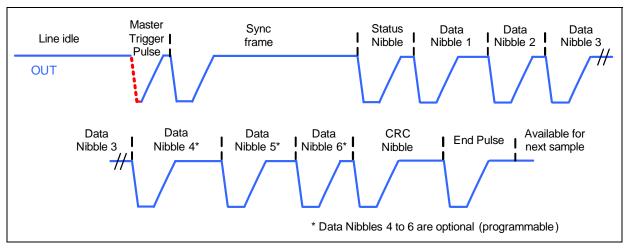

As in SENT, the time between two consecutive falling edges defines the value of a four bit nibble, thus representing numbers between 0 and 15. The transmission time therefore depends on the transmitted data values. The single edge is defined by a 3 unit time (UT) low pulse on the output, followed by the high time defined in the protocol (nominal values, may vary by tolerance of internal RC oscillator, not including analog delay of the open drain output and influence by external circuitry, unit time programming see Section 12.2). All values are multiples of a unit time frame concept. A transfer consists of the following parts, depicted in Figure 11:

- A trigger pulse by the master, which initiates the data transmission

- A synchronization period of 56 UT (in parallel, a new sample is calculated)

- A status nibble of 12-27 UT

- Between 3 and 6 data nibbles of 12-27 UT each (number is programmable, see Table 20), representing the Hall value and temperature information

- A CRC nibble of 12-27 UT

- An end pulse to terminate the SPC transmission.

Figure 11 SPC Frame

The CRC checksum includes the status nibble and the data nibbles and can be used to check the validity of the decoded data. The sensor is available for the next sample 90µs after the falling edge of the end pulse. The sampling time (when values are taken for temperature compensation) is always defined as the beginning of the synchronization period. During this period, the resulting data is always calculated from scratch.

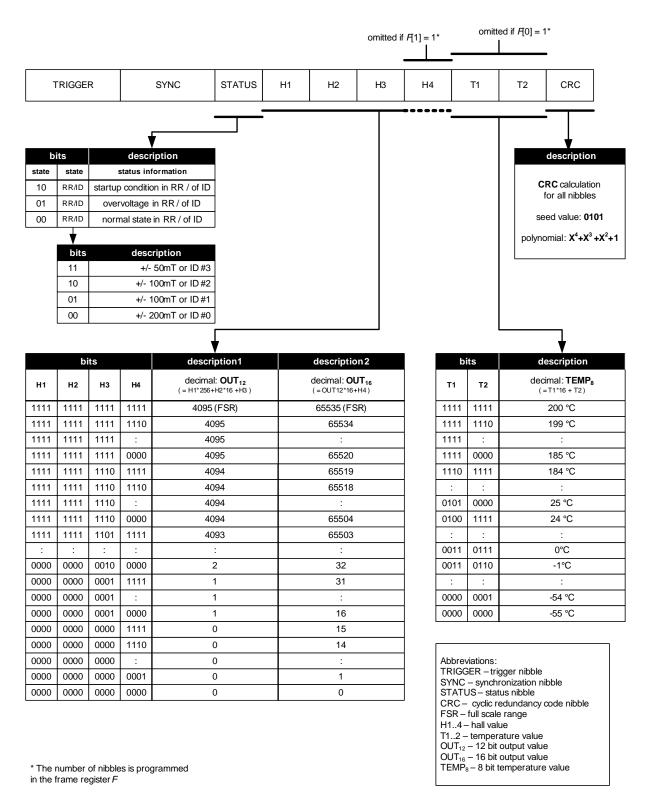

The number of transmitted SPC nibbles is programmable to customize the amount of information sent by the sensor. The frame contains a 16bit Hall value and an 8bit temperature value in the full configuration.

Table 19 Frame Register

| Parameter      | Symbol | Limit Values |      | Limit Values |  | Unit | Notes |

|----------------|--------|--------------|------|--------------|--|------|-------|

|                |        | min.         | max. |              |  |      |       |

| Frame register | F      |              | 2    | bit          |  |      |       |

Table 20 Frame Selection

| Frame Type                   | Parameter F | Data Nibbles |

|------------------------------|-------------|--------------|

| 16bit Hall, 8bit temperature | 0           | 6 nibbles    |

| 16bit Hall                   | 1           | 4 nibbles    |

| 12bit Hall, 8bit temperature | 2           | 5 nibbles    |

| 12bit Hall                   | 3           | 3 nibbles    |

The temperature is coded as an 8bit value. The value is transferred in unsigned integer format and corresponds to the range between -55°C and +200°C, so a transferred value of 55 corresponds to 0°C. The temperature is additional information and although it is not

Data Sheet 33 Rev 1.1, 2009-09

calibrated, may be used for a plausibility check, for example. **Table 21** shows the mapping between junction temperature and the transmitted value in the SPC frame.

Table 21 Mapping of Temperature Value

| Junction Temperature | Typ. Decimal Value from Sensor | Note                                  |

|----------------------|--------------------------------|---------------------------------------|

| - 55°C               | 0                              | Theoretical lower limit <sup>1)</sup> |

| 0°C                  | 55                             |                                       |

| 25°C                 | 80                             |                                       |

| 200°C                | 255                            | Theoretical upper limit <sup>1)</sup> |

<sup>1)</sup> Theoretical range of temperature values, not operating temperature range

The status nibble allows to check internal states and conditions of the sensor.

- Depending on the selected SPC mode, the first two bits of the status nibble contain either the selected magnetic range or the ID of the sensor and allow therefore an easy interpretation of the received data.

- The third bit is set to "1" for the first transmission after the sensor returns from an overvoltage operation with disabled open drain stage to regular operation (see Chapter 7.1).

- The fourth bit is switched to "1" for the first data package transferred after a reset. This allows the detection of low-voltage situations or EMC problems of the sensor.

# 12.2 Unit Time Setup

The basic SPC protocol unit time granularity is defined as  $3 \mu s$ . Every timing is a multiple of this basic time unit. To achieve more flexibility, trimming of the unit time can be used to:

- Allow a calibration trim within a timing error of less than 20% clock error (as given in SAE standard)

- Allow a modification of the unit time for small speed adjustments

This enables a setup of different unit times, even if the internal RC oscillator varies by ±20%. Of course, timing values that are too low could clash with timing requirements of the application and should therefore be avoided, but in principle it is possible to adjust the timer unit for a more precise protocol timing. The output characteristic depends on the external load, the wiring, as well on the pull-up voltage and the temperature. Furthermore, sufficient driving capability of the sensor counterpart (ECU) is mandatory,

Data Sheet 34 Rev 1.1, 2009-09

in order to be able to maintain the herein given master pulse requirements. All these parameters have considerable influence to find the proper unit time setup.

Table 22 Predivider Setting

| Parameter     | Symbol        | Limit Values |      | Unit | Notes                                   |

|---------------|---------------|--------------|------|------|-----------------------------------------|

|               |               | min.         | max. |      |                                         |

| Register size | Prediv        |              | 4    | bit  | Predivider <sup>1)</sup>                |

| Unit time     | $t_{ m UNIT}$ | 2.0          | 3.88 | μs   | Clk <sub>UNIT</sub> =8MHz <sup>2)</sup> |

<sup>1)</sup> Prediv default is decimal = 8 for 3 µs nominal SPC unit time

The nominal unit time is calculated by:

$$t_{\text{UNIT}} = (Prediv + 16) / Clk_{\text{UNIT}}$$

$Clk_{\text{UNIT}} = 8\text{MHz} \pm 20\%$

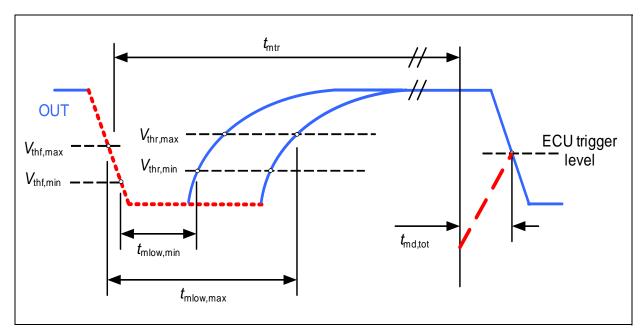

### 12.3 Master Pulse Requirements

An SPC transmission is initiated by a Master pulse on the OUT pin. To detect a low level on the OUT pin, the voltage must be below a threshold  $V_{\rm thf}$ . The sensor detects that the OUT line has been released as soon as  $V_{\rm thr}$  is crossed. Figure 12 shows the timing definitions for the master pulse. The master low time  $t_{\rm mlow}$  as well as the total trigger time  $t_{\rm mtr}$  are individual for the different SPC modes and are given in the subsequent sections. It is recommended to chose the typical master low time exactly between the minimum and the maximum possible time:  $t_{\rm mlow,typ} = (t_{\rm mlow,min} + t_{\rm mlow,max}) / 2$ . Although the allowed timing windows are larger for longer low times, the master should use a quarz clock source to provide a high timing accuracy (approx. 1%). For improved robustness, the master pulse can be adopted by the master once the effective unit time is known through the sensor's synchronisation period length. If the master low time exceeds the maximum low time, the sensor does not respond and is available for a next triggering

Data Sheet 35 Rev 1.1, 2009-09

<sup>2)</sup> RC oscillator frequency variation +/- 20%

30 $\mu$ s after the master pulse crosses  $V_{\text{thr}}$ .  $t_{\text{md,tot}}$  is the delay between internal triggering of the falling edge in the sensor and the triggering of the ECU.

**Table 23** Master Pulse Parameters

| Parameter              | Symbol              | Limit Values |      |      | Unit | Notes                             |

|------------------------|---------------------|--------------|------|------|------|-----------------------------------|

|                        |                     | min.         | typ. | max. |      |                                   |

| Falling edge threshold | $V_{\rm thf}$       | 1.1          | 1.3  | 1.7  | V    |                                   |

| Rising edge threshold  | $V_{\rm thr}$       | 1.25         | 1.43 | 1.8  | V    |                                   |

| Total trigger time     | t <sub>mtr</sub>    | 10.8         | 13   | 16.3 | UT   | Synchronous mode <sup>1)2)</sup>  |

|                        |                     | 46.6         | 56   | 70   | UT   | Dyn. range mode <sup>1)2)</sup>   |

|                        |                     | 75           | 90   | 113  | UT   | ID selection mode <sup>1)2)</sup> |

| Master delay time      | t <sub>md,tot</sub> | 3.7          | 5.8  | 7.9  | μs   | 3)                                |

<sup>1)</sup> UT = Programmed nominal SPC unit time

<sup>&</sup>lt;sup>3)</sup> For  $V_{DD}$  = 5 V,  $R_L$  = 2.2 k $\Omega$ ,  $C_L$  = 4.7 nF (in package), ECU trigger level  $V_{th,ECU}$  = 2V

Figure 12 SPC Master Pulse Timing

Data Sheet 36 Rev 1.1, 2009-09

<sup>&</sup>lt;sup>2)</sup> Trigger time in the sensor is fixed to the number of unit times specified in the "typ." column, but the effective trigger time varies due to the sensor's clock variation

## 12.4 Synchronous Transmission

In the "synchronous" mode, the sensor (slave) starts to transfer a complete data frame only after a low pulse is forced by the master on the OUT pin. This means that the data line is bidirectional - an open drain output of the microcontroller (master) sends the trigger pulse. The sensor then initiates a sync pulse and starts to calculate the new output data value. After the synchronization period, the data follows in form of a standard SENT frame, starting with the status, data and CRC nibbles. At the end, an end pulse allows the CRC nibble decoding and indicates that the data line is idle again. The timing diagram in Figure 11 visualizes a synchronous transmission.

Table 24 Master Pulse Timing Requirements for Synchronous Mode

| Parameter       | Symbol            | Limit Values |      |      | Unit <sup>1)</sup> | Notes |

|-----------------|-------------------|--------------|------|------|--------------------|-------|

|                 |                   | min.         | typ. | max. |                    |       |

| Master low time | t <sub>mlow</sub> | 1.5          | 2.75 | 4    | UT                 |       |

<sup>1)</sup> UT = Programmed nominal SPC unit time

Figure 13 Bidirectional Communication in Synchronous Mode

# 12.5 Synchronous Transmission Including Range Selection

The low time duration of the master can be used to select the magnetic range of the sensor in SPC dynamic range selection mode.

Table 25 Master Pulse Timing Requirements for Dynamic Range Mode

| Parameter       | Symbol            | Limit Values |      |      | Unit <sup>1)</sup> | Notes                        |

|-----------------|-------------------|--------------|------|------|--------------------|------------------------------|

|                 |                   | min.         | typ. | max. |                    |                              |

| Master low time | t <sub>mlow</sub> | 1.5          | 3.25 | 5    | UT                 | Range = 200mT ( <i>R</i> =0) |

|                 |                   | 9            | 12   | 15   | UT                 | Range = 100mT ( <i>R</i> =1) |

|                 |                   | 24           | 31.5 | 39   | UT                 | Range = 50mT ( <i>R</i> =3)  |

<sup>1)</sup> UT = Programmed nominal SPC unit time

Data Sheet 37 Rev 1.1, 2009-09

The range information in the status bit can be used to determine whether the range has been properly identified. Changing the range takes some time due to the settling time of internal circuitry. The first sample after a range switch therefore still displays a value sampled with the old range setting, and the second transmission after changing the range displays the new range with reduced accuracy.

### 12.6 Synchronous Mode with ID Selection

This functionality is similar to the previous mode, but instead of switching the range of one sensor, one of up to four sensors are selectable on a bus (bus mode, 1 master with up to 4 slaves). This allows parallel connection of up to 4 sensors using only three lines (VDD, GND, OUT), as illustrated in Figure 14.

Figure 14 Bidirectional Communication with ID Selection

In this mode, the sensor starts to transfer complete packages only after receiving a master low pulse with an ID that is equivalent to the programmed value in its *ID* register. The mapping between master low time and ID is given in **Table 26**. A proper addressing requires the different sensors on a same bus to be programmed with the same nominal

Data Sheet 38 Rev 1.1, 2009-09

SPC unit time. Alternatively, the sensors can be trimmed using the predivider settings to further reduce their relative unit time difference for more robustness.

Table 26 Master Pulse Timing Requirements for ID Selection Mode

| Parameter       | Symbol            | Limit Values |      |      | Unit <sup>1)</sup> | Notes  |

|-----------------|-------------------|--------------|------|------|--------------------|--------|

|                 |                   | min.         | typ. | max. |                    |        |

| Master low time | t <sub>mlow</sub> | 9            | 10.5 | 12   | UT                 | ID = 0 |

|                 |                   | 19           | 21   | 23   | UT                 | ID = 1 |

|                 |                   | 35.5         | 38   | 40.5 | UT                 | ID = 2 |

|                 |                   | 61.5         | 64.5 | 67.5 | UT                 | ID = 3 |

<sup>1)</sup> UT = Programmed nominal SPC unit time

Data Sheet 39 Rev 1.1, 2009-09

Table 27 Content of a SPC Data Frame (5-8 Nibbles)

Data Sheet 40 Rev 1.1, 2009-09

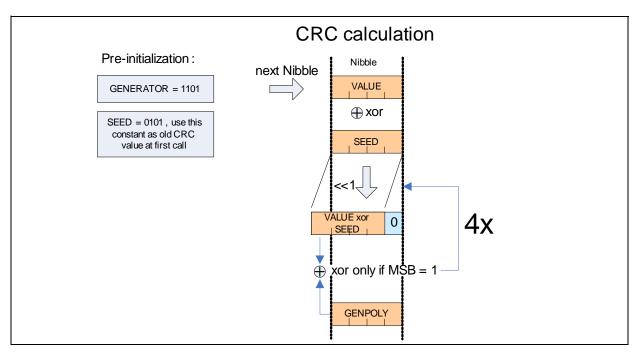

#### 12.7 Checksum Nibble Details

The Checksum nibble is a 4-bit CRC of the data nibbles including the status nibble. The CRC is calculated using a polynomial  $x^4 + x^3 + x^2 + 1$  with a seed value of 0101.

In the TLE4998C3C it is implemented as a series of XOR and shift operations as shown in the following flowchart:

Figure 15 CRC Calculation

A microcontroller implementation may use an XOR command plus a small 4-bit lookup table to calculate the CRC for each nibble.

```

// Fast way for any \muC with low memory and compute capabilities char Data[8] = {...}; // contains the input data (status nibble, 6 data nibble, CRC) // required variables and LUT char CheckSum, i; char CrcLookup[16] = {0, 13, 7, 10, 14, 3, 9, 4, 1, 12, 6, 11, 15, 2, 8, 5}; CheckSum= 5; // initialize checksum with seed "0101" for (i=0; i<7; i++) { CheckSum = CheckSum ^ Data[i]; CheckSum = CrcLookup[CheckSum]; } ; // finally check if Data [7] is equal to CheckSum

```

Figure 16 Example Code for CRC Generation

www.infineon.com

Published by Infineon Technologies AG

# 单击下面可查看定价,库存,交付和生命周期等信息

>>Infineon(英飞凌)