# IR3596

## **FEATURES**

- Ultra Low Power single loop PWM Controller with 3 PWMs configurable as 1, 2, 3 phase systems

- Compliant with Intel VR12.5 Rev 1.3/VR12.6 Rev1.0 specifications

- Intel® VR12.5/VR12.6 SVID or I2C controlled regulation

- Optimized for 3 phase DDR memory solution when paired with IR3548 and IR355x PowIRstage

- ~50mW @ Maximum Performance

- Compatible with Active Tri Level (ATL) Industry Standard Tri-state Drivers

- Dynamic Phase Control and Automatic Power State Switching with Active Diode Emulation for Very Light Loads

- I2C system interface for telemetry of Temperature, Voltage, Input and Output Current & Power

- Fault Protection: Output OVP, UVP, OC Warn, OCP, OT Warn, OTP

- IR Adaptive Transient Algorithm (ATA) minimizes output bulk capacitors and system cost

- 8 Time Programming (MTP) with integrated charge pump for easy custom configuration

- 200kHz to 2MHz switching frequency per phase

- +3.3V supply voltage; -40°C to 85°C ambient operation

- Pb-Free, RoHS, 4x4mm, 28-pin, 0.4mm pitch QFN

## DESCRIPTION

The IR3596 is a flexible single loop digital multi-phase buck controller that can be configured as a 1, 2 or 3 phase system when combined with IR Dual 6x8mm IR3548 or IR355x powIRstages.

Power consumption is minimized while maintaining full digital capability and flexibility. Digital non-linear transient control allows lower frequency operation to achieve the highest efficiency possible while providing minimal all ceramic output capacitor solutions. The IR3596 includes IR's Efficiency Shaping Technology to automatically deliver exceptional efficiency at minimum cost across the entire load range and can be configured to enter 1-phase operation and active diode emulation mode automatically or by command. The IR3596 may also shut down connected drivers/PowIRstage to minimize the quiescent current consumption in the system to maximize battery life on next gen VR12.5/VR12.6 notebooks/Ultrabooks.

IR's unique Adaptive Transient Algorithm (ATA), based on proprietary non-linear digital PWM algorithms, minimizes output bulk capacitors, and improves transient response and form factor.

Device configuration and fault parameters are easily defined using the IR Digital Power Design Center (DPDC) GUI and stored in on-chip MTP. MTP storage saves pins and enables a small package size. Fault protection includes output OV, UV and OC protection, thermistor or NTC based OT protection sensing with a VRHOT signal output and a Over Current warning flag.

### APPLICATIONS

- DDR3/LV DDR3/ DDR4 Memory Controller

- VR12.5/VR12.6 Mobile Controller

| Base Part<br>Number | Package Type    | Standard Pack |          | Orderable                   | Brogromming            |

|---------------------|-----------------|---------------|----------|-----------------------------|------------------------|

|                     |                 | Form          | Quantity | Part Number                 | Programming            |

| IR3596              | QFN 4 mm x 4 mm | Tape and Reel | 3000     | IR3596MTRPBF                | Default                |

| <u>IR3596</u>       | QFN 4 mm x 4 mm | Tape and Reel | 3000     | IR3596MxxyyTRP <sup>1</sup> | Customer Configuration |

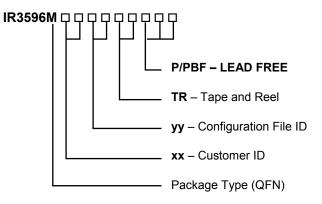

### **ORDERING INFORMATION**

1. Customer Specific Configuration File, where xx = Customer ID and yy = Configuration File (Codes assigned by IR Marketing).

# IR3596

## **ORDERING INFORMATION**

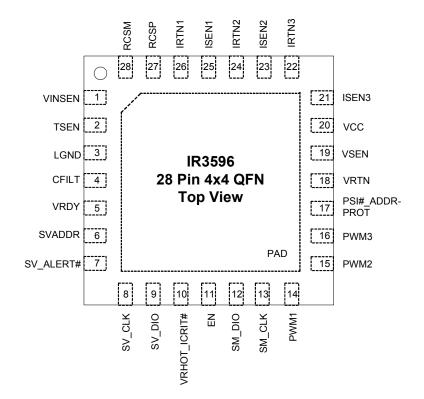

## **PIN DIAGRAM**

#### Figure 1: IR3596 Pin Diagram<sup>1</sup>

#### Notes:

2

1. Center pad is electrically isolated. Pad should be always connected to ground.

单击下面可查看定价,库存,交付和生命周期等信息

>>Infineon Technologies(英飞凌)