**IGBT**

TRENCHSTOP<sup>TM</sup> IGBT4 Medium Power Chip IGC99T120T8RM

**Data Sheet**

Industrial Power Control

Downloaded From Oneyac.com

### **Table of Contents**

| Features and Applications             | 3 |

|---------------------------------------|---|

|                                       |   |

| Mechanical Parameters                 | 3 |

| Maximum Ratings                       | 4 |

| Static and Electrical Characteristics | 4 |

| Further Electrical Characteristics    |   |

| Further Electrical Characteristics    | 5 |

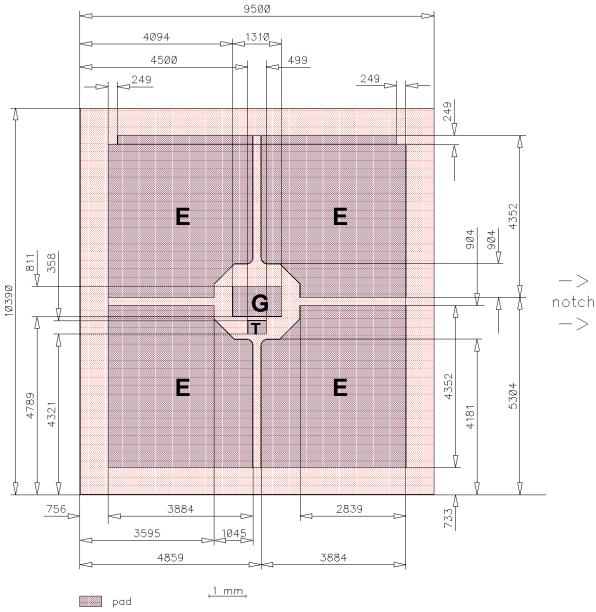

| Chip Drawing                          | 6 |

| Revision History                      | 7 |

| Relevant Application Notes            | 7 |

| Legal Disclaimer                      | 8 |

### TRENCHSTOP<sup>TM</sup> IGBT4 Medium Power Chip

#### Features:

- 1200V trench & field stop technology

- Low switching losses

- Soft turn off

- Positive temperature coefficient

- Easy paralleling

#### Recommended for:

Medium power modules

### **Applications:**

• Medium power drives

| Chip Type     | V <sub>CE</sub> | <i>I</i> <sub>Cn</sub> <sup>1</sup> | Die Size        | Package      |

|---------------|-----------------|-------------------------------------|-----------------|--------------|

| IGC99T120T8RM | 1200V           | 100A                                | 9.5mm x 10.39mm | Sawn on foil |

### **Mechanical Parameters**

| Die size                                               |                                  | 9.5 x 10.39                                                                                                                                         |                      |  |  |

|--------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|

| Emitter pad size                                       |                                  | See chip drawing                                                                                                                                    | 2                    |  |  |

| Gate pad size                                          |                                  | 1.31 x 0.811                                                                                                                                        | mm <sup>2</sup>      |  |  |

| Area total                                             |                                  | 98.71                                                                                                                                               |                      |  |  |

| Thickness                                              |                                  | 120                                                                                                                                                 | μm                   |  |  |

| Wafer size                                             |                                  | 200                                                                                                                                                 | mm                   |  |  |

| Maximum possible ch                                    | ips per wafer                    | 258                                                                                                                                                 |                      |  |  |

| Passivation frontside                                  |                                  | Photoimide                                                                                                                                          |                      |  |  |

| Pad metal 3200nm AlSiCu                                |                                  |                                                                                                                                                     |                      |  |  |

| Backside metal                                         |                                  | Ni Ag – system  To achieve a reliable solder connection it is strongly recommended not to consume the Ni layer completely during production process |                      |  |  |

| Die bond Electrically conductive epoxy glue and soft s |                                  |                                                                                                                                                     | lder                 |  |  |

| Wire bond                                              |                                  | Al, ≤500μm                                                                                                                                          |                      |  |  |

| Reject ink dot size                                    |                                  | Ø 0.65mm; max. 1.2mm                                                                                                                                | Ø 0.65mm; max. 1.2mm |  |  |

| Storago environment                                    | for original and sealed MBB bags | Ambient atmosphere air, temperature 17°C – 25°0 <6 months                                                                                           |                      |  |  |

| Storage environment                                    | for open MBB bags                | Acc. to IEC62258-3: atmosphere >99% Nitrogen or inchange humidity <25%RH, temperature 17°C – 25°C, <6 mg                                            |                      |  |  |

L7683O, L7683U 3 Rev. 2.1, 20.08.2015

<sup>&</sup>lt;sup>1</sup> Nominal collector current at  $T_C$ =100°C for chip packaged in power modules, see application example cited on page 5.

### **Maximum Ratings**

| Parameter                                                                  | Symbol              | Value    | Unit |

|----------------------------------------------------------------------------|---------------------|----------|------|

| Collector-emitter voltage, T <sub>vj</sub> =25°C                           | V <sub>CE</sub>     | 1200     | V    |

| DC collector current, limited by $T_{\rm vj\;max}^{\;\;2}$                 | I <sub>C</sub>      | -        | Α    |

| Pulsed collector current, $t_p$ limited by $T_{vj \max}$ 3                 | I <sub>C,puls</sub> | 300      | Α    |

| Gate-emitter voltage                                                       | $V_{GE}$            | ±20      | V    |

| Operating junction temperature                                             | $T_{vj}$            | -40 +175 | °C   |

| Short circuit data $^{3/4}$ $V_{GE}$ =15V, $V_{CC}$ =800V, $T_{vj}$ =150°C | t <sub>sc</sub>     | 10       | μs   |

### Static Characteristics (tested on wafer), T<sub>vi</sub>=25°C

| Parameter                            | Symbol Conditions    |                                                               | Value |      |      | Unit |

|--------------------------------------|----------------------|---------------------------------------------------------------|-------|------|------|------|

| rai ailletei                         | Symbol               | Conditions                                                    | min.  | typ. | max. | •    |

| Collector-emitter breakdown voltage  | V <sub>(BR)CES</sub> | $V_{\text{GE}}$ =0V, $I_{\text{C}}$ =3.8mA                    | 1200  | -    | -    |      |

| Collector-emitter saturation voltage | V <sub>CEsat</sub>   | V <sub>GE</sub> =15V, I <sub>C</sub> =100A                    | 1.53  | 1.75 | 1.97 | V    |

| Gate-emitter threshold voltage       | $V_{\rm GE(th)}$     | $I_{\rm C}$ =3.8mA, $V_{\rm GE}$ = $V_{\rm CE}$               | 5.1   | 5.8  | 6.4  |      |

| Zero gate voltage collector current  | I <sub>CES</sub>     | $V_{\text{CE}} = 1200 \text{V}, \ V_{\text{GE}} = 0 \text{V}$ | -     | -    | 1.3  | μA   |

| Gate-emitter leakage current         | I <sub>GES</sub>     | $V_{CE} = 0V, V_{GE} = 20V$                                   | ı     | ı    | 120  | nA   |

| Integrated gate resistor             | r <sub>G</sub>       |                                                               |       | 7.5  |      | Ω    |

### **Electrical Characteristics** <sup>3</sup>

| Parameter                            | Symbol Conditions |                                                                    | Value |      |      | Unit |

|--------------------------------------|-------------------|--------------------------------------------------------------------|-------|------|------|------|

| raiametei                            | Symbol            | Conditions                                                         | min.  | typ. | max. | Onit |

| Collector-emitter saturation voltage | $V_{CEsat}$       | $V_{\text{GE}}$ =15V, $I_{\text{C}}$ =100A, $T_{\text{vj}}$ =150°C | -     | 2.05 | -    | ٧    |

| Input capacitance                    | C <sub>ies</sub>  | V <sub>CE</sub> =25V,                                              | -     | 6300 | 1    | ςE   |

| Reverse transfer capacitance         | C <sub>res</sub>  | $V_{\text{GE}}$ =0V, $f$ =1MHz<br>$T_{\text{vj}}$ =25°C            | -     | 270  | -    | pF   |

<sup>&</sup>lt;sup>2</sup> Depending on thermal properties of assembly.

<sup>&</sup>lt;sup>3</sup> Not subject to production test - verified by design/characterization.

<sup>&</sup>lt;sup>4</sup> Allowed number of short circuits: <1000; time between short circuits: >1s.

### **Further Electrical Characteristics**

Switching characteristics and thermal properties are depending strongly on module design and mounting technology and can therefore not be specified for a bare die.

| Application example | IFS100B12N3E4_B31 | Rev. 2.0 |

|---------------------|-------------------|----------|

|---------------------|-------------------|----------|

### **Chip Drawing**

**E** = Emitter

**G** = Gate

T = Test pad do not contact

### **Bare Die Product Specifics**

Test coverage at wafer level cannot cover all application conditions. Therefore it is recommended to test all characteristics which are relevant for the application at package level, including RBSOA and SCSOA.

### **Description**

AQL 0.65 for visual inspection according to failure catalogue

Electrostatic Discharge Sensitive Device according to MIL-STD 883

### **Revision History**

| Revision | Subjects (major changes since last revision) | Date       |

|----------|----------------------------------------------|------------|

| 2.0      | Final data sheet                             | 18.02.2015 |

| 2.1      | Update disclaimer                            | 20.08.2015 |

|          |                                              |            |

| Relevant App | lication Notes |

|--------------|----------------|

|              |                |

Published by Infineon Technologies AG 81726 München, Germany © Infineon Technologies AG 2015. All Rights Reserved.

#### **IMPORTANT NOTICE**

The information given in this document shall in <u>no event</u> be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

Please note that this product is <u>not</u> qualified according to the AEC Q100 or AEC Q101 documents of the Automotive Electronics Council.

#### **WARNINGS**

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may <u>not</u> be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.

$w\ w\ w\ .\ i\ n\ f\ i\ n\ e\ o\ n\ .\ c\ o\ m$

Published by Infineon Technologies AG

单击下面可查看定价,库存,交付和生命周期等信息

>>Infineon Technologies(英飞凌)