# EiceDRIVER™

High voltage gate driver IC with reinforced isolation

# 1EDS-SRC family

Real-time adjustable gate current control IC 1EDS20I12SV 1EDU20I12SV 1EDI20I12SV

EiceDRIVER™

# Final datasheet

<Revision 2.1>, 22.10.2018

# Industrial Power Control

Edition 22.10.2018

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2018 Infineon Technologies AG

All Rights Reserved.

## IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

Please note that this product is not qualified according to the AEC Q100 or AEC Q101 documents of the Automotive Electronics Council.

#### **WARNINGS**

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.

| <b>Revision Histo</b>        | Revision History                                 |  |  |  |  |  |

|------------------------------|--------------------------------------------------|--|--|--|--|--|

| Page or Item                 | Subjects (major changes since previous revision) |  |  |  |  |  |

| <revision 2.1=""></revision> | <revision 2.1="">, 22.10.2018</revision>         |  |  |  |  |  |

| all                          | Changed document status for final datasheet      |  |  |  |  |  |

|                              |                                                  |  |  |  |  |  |

|                              |                                                  |  |  |  |  |  |

|                              |                                                  |  |  |  |  |  |

|                              |                                                  |  |  |  |  |  |

|                              |                                                  |  |  |  |  |  |

|                              |                                                  |  |  |  |  |  |

|                              |                                                  |  |  |  |  |  |

|                              |                                                  |  |  |  |  |  |

|                              |                                                  |  |  |  |  |  |

|                              |                                                  |  |  |  |  |  |

|                              |                                                  |  |  |  |  |  |

|                              |                                                  |  |  |  |  |  |

## **Trademarks of Infineon Technologies AG**

AURIX™, BlueMoon™, C166™, CanPAK™, CIPOS™, CIPURSE™, COMNEON™, EconoPACK™, CoolMOS™, CoolSET™, CORECONTROL™, CROSSAVE™, DAVE™, EasyPIM™, EconoBRIDGE™, EconoDUAL™, EconoPIM™, EiceDRIVER™, eupec™, FCOS™, HITFET™, HybridPACK™, I²RF™, ISOFACE™, IsoPACK™, MIPAQ™, ModSTACK™, my-d™, NovalithIC™, OmniTune™, OptiMOS™, ORIGA™, PRIMARION™, PrimePACK™, PrimeSTACK™, PRO-SIL™, PROFET™, RASIC™, ReverSave™, SatRIC™, SIEGET™, SINDRION™, SIPMOS™, SMARTi™, SmartLEWIS™, SOLID FLASH™, TEMPFET™, thinQ!™, TRENCHSTOP™, TriCore™, X-GOLD™, X-PMU™, XMM™, XPOSYS™.

## **Other Trademarks**

Advance Design System™ (ADS) of Agilent Technologies, AMBA™, ARM™, MULTI-ICE™, KEIL™, PRIMECELL™, REALVIEW™, THUMB™, µVision™ of ARM Limited, UK. AUTOSAR™ is licensed by AUTOSAR development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of DECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO™ of Microsoft Corporation. FlexRay™ is licensed by FlexRay Consortium. HYPERTERMINAL™ of Hilgraeve Incorporated. IEC™ of Commission Electrotechnique Internationale. IrDA™ of Infrared Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC™, NUCLEUS™ of Mentor Graphics Corporation. Mifare™ of NXP. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of OmniVision Technologies, Inc. Openwave™ Openwave Systems Inc. RED HAT™ Red Hat, Inc. RFMD™ RF Micro Devices, Inc. SIRIUS™ of Sirius Satellite Radio Inc. SOLARIS™ of Sun Microsystems, Inc. SPANSION™ of Spansion LLC Ltd. Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas Instruments Incorporated. VXWORKS™, WIND RIVER™ of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes Zetex Limited.

Last Trademarks Update 2010-10-26

## **Table of Contents**

| 1              | Block diagram                                                                      | 7  |

|----------------|------------------------------------------------------------------------------------|----|

| 2              | Pin configuration, description, and functionality                                  | 8  |

| 2.1            | Terminal configuration                                                             |    |

| 2.2            | Terminal functionality                                                             | 9  |

| 3              | Functional description                                                             | 13 |

| 3.1            | Introduction                                                                       |    |

| 3.2            | IC Supply                                                                          |    |

| 3.2.1          | Input side                                                                         |    |

| 3.2.2          | Output side                                                                        |    |

| 3.3            | Non-inverting and inverting input terminals INP and INN                            |    |

| 3.4            | Driver output terminal ON                                                          |    |

| 3.5            | SPEED setting                                                                      |    |

| 3.6            | Preboost setting                                                                   |    |

| 3.7            | Gate turn-off terminal OFF                                                         |    |

| 3.8            | Terminal EN                                                                        |    |

| 3.9            | Protection and diagnosis features                                                  |    |

| 3.9.1          | Undervoltage lockout (UVLO)                                                        |    |

| 3.9.2          | Ready and status output terminals                                                  |    |

| 3.9.3          | Fault indication (terminal /FLT)                                                   |    |

| 3.9.4<br>3.9.5 | Watchdog                                                                           |    |

| 3.9.6          | Two-level turn-off (TLTO)                                                          |    |

| 3.9.7          | Desaturation shut down protection                                                  |    |

| 3.9.8          | IGBT overcurrent detection                                                         |    |

| 3.9.9          | Overcurrent protection ON/OFF                                                      |    |

| 3.9.10         | Soft turn-off                                                                      |    |

| 4              | Electrical parameters                                                              | 21 |

| 4.1            | Absolute maximum ratings                                                           |    |

| 4.2            | Operating range                                                                    |    |

| 4.3            | Electrical characteristics                                                         |    |

| 4.3.1          | Voltage supply                                                                     |    |

| 4.3.2          | Logic input and output                                                             |    |

| 4.3.3          | Gate driver                                                                        | 24 |

| 4.3.4          | Desaturation protection                                                            |    |

| 4.3.5          | Overcurrent protection disable                                                     |    |

| 4.3.6          | Current sense                                                                      |    |

| 4.3.7          | Two-level turn-off                                                                 | 27 |

| 5              | Insulation characteristics                                                         | 28 |

| 5.1            | Reinforced insulation requirements according to VDE 0884-10 (Certificate 40043864, |    |

|                | 1EDS20I12SV only)                                                                  |    |

| 5.2            | Recognized under UL 1577 (File E311313, 1EDS20I12SV and 1EDU20I12SV only)          | 28 |

| 6              | Timing diagrams                                                                    | 29 |

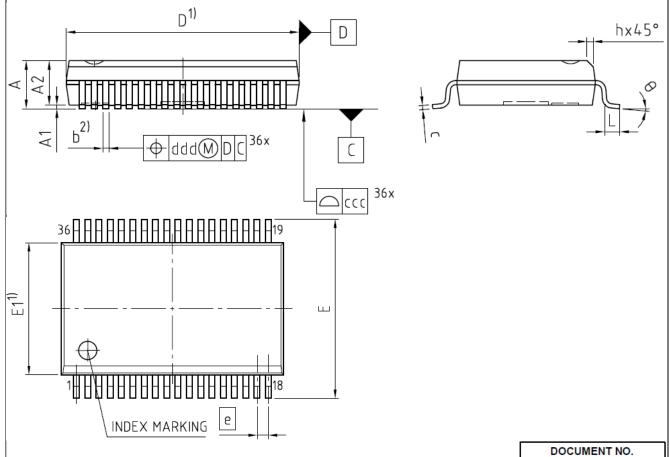

| 7              | Package                                                                            | 32 |

| 7.1            | PG-DSO-36-64                                                                       |    |

# **List of Figures**

| Figure 1  | Block diagram for the 1EDS-SRC family                                                                                    | 7     |

|-----------|--------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 2  | Terminal configuration of the 1EDS-SRC family (Top View)                                                                 | 8     |

| Figure 3  | Typical application                                                                                                      |       |

| Figure 4  | Timing diagram for turn-on                                                                                               | .15   |

| Figure 5  | External circuit for setting of preboost current (left: unipolar supply; right: bipolar supply)                          | .16   |

| Figure 6  | I/O signature check                                                                                                      | .18   |

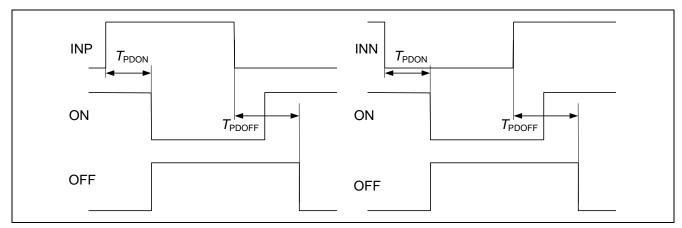

| Figure 7  | Timing of turn-on and turn-off propagation delay without two-level turn-off mode                                         | .29   |

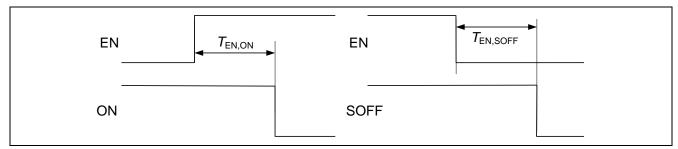

| Figure 8  | Timing of EN turn-on and shut down propagation delay                                                                     | .29   |

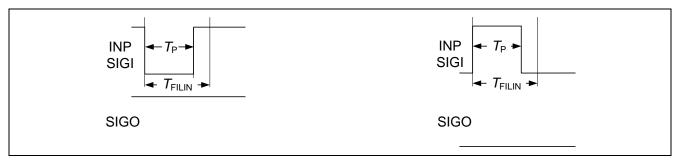

| Figure 9  | Timing of short pulse suppression terminal INP and SIGI (TP < TFILIN)                                                    | .29   |

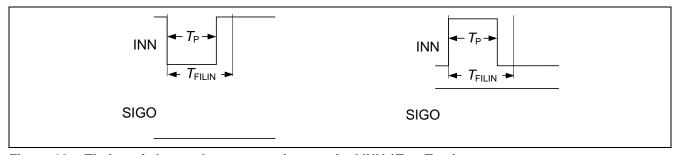

| Figure 10 | Timing of short pulse suppression terminal INN ( $T_P < T_{FILIN}$ )                                                     | .29   |

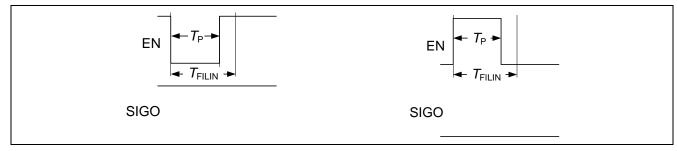

| Figure 11 | Timing of short pulse suppression terminal EN ( $T_P < T_{FILIN}$ )                                                      | .30   |

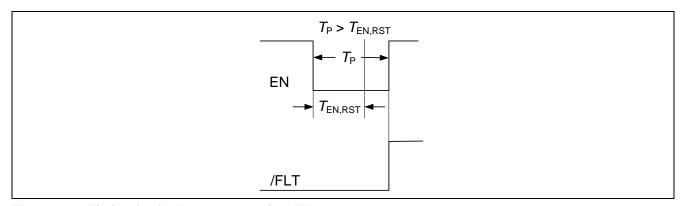

| Figure 12 | Timing for fault reset at terminal EN                                                                                    | .30   |

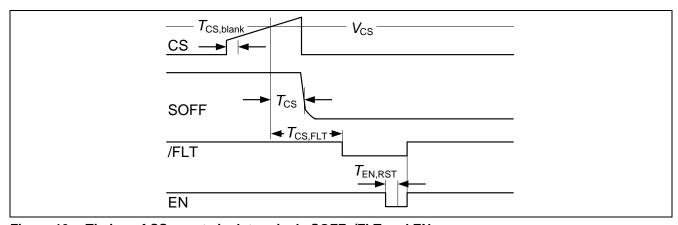

| Figure 13 | Timing of CS events incl. terminals SOFF, /FLT and EN                                                                    | .30   |

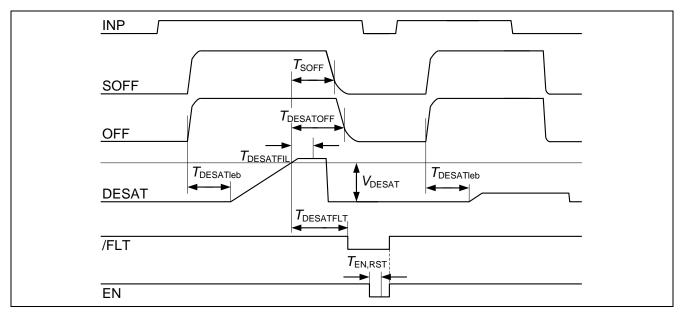

| Figure 14 | Timing for DESAT events incl. terminals SOFF, /FLT and EN (timing is same for related INN input                          | t     |

|           | signal)                                                                                                                  |       |

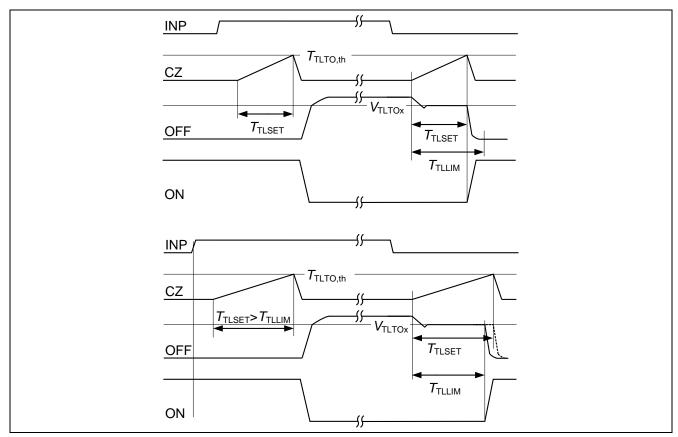

| Figure 15 | Timing for two-level turn-off incl. terminals CZ and OFF (top: $T_{TLSET} < T_{TLLIM}$ , bottom: $T_{TLSET} > T_{TLLIM}$ | ıм)31 |

| Figure 16 | Package drawing                                                                                                          | .32   |

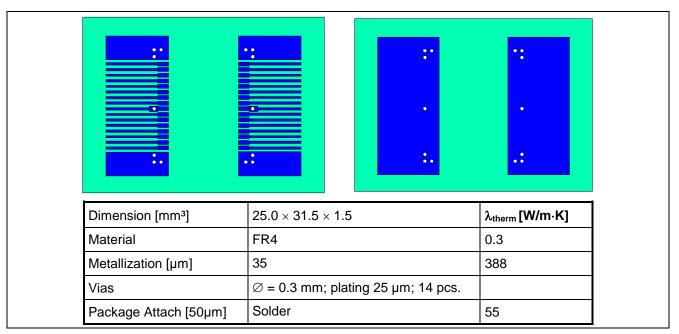

| Figure 17 | PCB reference layout (left: top layer, right: bottom layer)                                                              | .33   |

|           |                                                                                                                          |       |

## **List of Tables**

| Table 1  | Terminal Description                                     | 8  |

|----------|----------------------------------------------------------|----|

| Table 2  | Switching speed levels on input and output side          | 16 |

| Table 3  | Driver IC status for EN, INP, and INN                    | 17 |

| Table 4  | Driver IC status UVLO at VCC1, VCC2 and PADP (EN = high) | 18 |

| Table 5  | Abs. maximum ratings                                     | 21 |

| Table 6  | Operating parameters                                     | 22 |

| Table 7  | Voltage supply                                           | 23 |

| Table 8  | Logic input and output                                   | 24 |

| Table 9  | Gate driver                                              | 24 |

| Table 10 | Desaturation protection                                  | 26 |

| Table 11 | Overcurrent protection disable                           | 26 |

| Table 12 | Current sense                                            |    |

| Table 13 | Two-level turn-off                                       |    |

| Table 14 | Insulation characteristics                               | 28 |

| Table 15 | Reinforced isolation limits                              | 28 |

| Table 16 | Recognized under UL 1577                                 | 28 |

## **EiceDRIVER™**

## Real-time adjustable gate current control IC

#### Main features

- · Single-channel isolated IGBT Driver

- Supports IGBT up to 1200 V

- IGBT off-state: 2 A pull down to rail

- Overcurrent protection for sense IGBTs and conventional IGBTs

- Desaturation detection

- Soft turn-off shut down: 1 A pull down to rail

- Two-level turn-off

- Operation at high ambient temperature up to 105°C

- Compatible PWM inputs for 3.3 V, 5 V, and 15 V logic voltages

# PG-DSO36

1EDS20I12SV 1EDU20I12SV

## **Product highlights**

- Optimized short circuit control for 3-level inverters

- Online adjustable current source slew rate control during IGBT turn-on

- Reinforced isolation according VDE 0884-10 (V<sub>IORM</sub> = 1420 V, 1EDS20I12SV only)

- UL certification according UL1577 (Viso = 5 kV, 1EDS20I12SV and 1EDU20I12SV only)

## Potential applications

- · AC and brushless DC motor drives

- High-voltage DC/DC converters

- UPS systems

- Welding

- Servo drives

### Description

The 1EDS20I12SV is a single-channel IGBT driver in a PG-DSO-36-64 package with a reinforced galvanically isolated barrier according to VDE0884-10 and UL1577. The driver IC controls up to three external p-channel MOSFET as a controlled current source during turn-on. The IC is therefore able to control precisely the turn-on process in order to avoid excessive  $dv_{CE}/dt$  or  $di_C/dt$  transients. The IC has a peak sinking capability of 2 A for turning off the IGBT. An external PNP transistor can be used to support IGBT with currents ratings higher than 75 A.

The 1EDU20I12SV offers the same set of function including a galvanically isolated barrier according to UL1577.

The 1EDI20I12SV offers the same set of functions including the unique slew rate control with the exception that its isolation barrier offers functional isolation.

All three devices together are the 1EDS-SRC family.

The logic input pins of the 1EDS-SRC family are 3.3 V, 5 V, and 15 V CMOS-compatible. The data transfer across the galvanic isolation barrier is accomplished with the integrated coreless transformer technology. The 1EDS-SRC family provides several protection features such as IGBT desaturation shut down protection for IGBT, overcurrent protection for sense IGBT, soft turn-off shut down, and two-level turn-off.

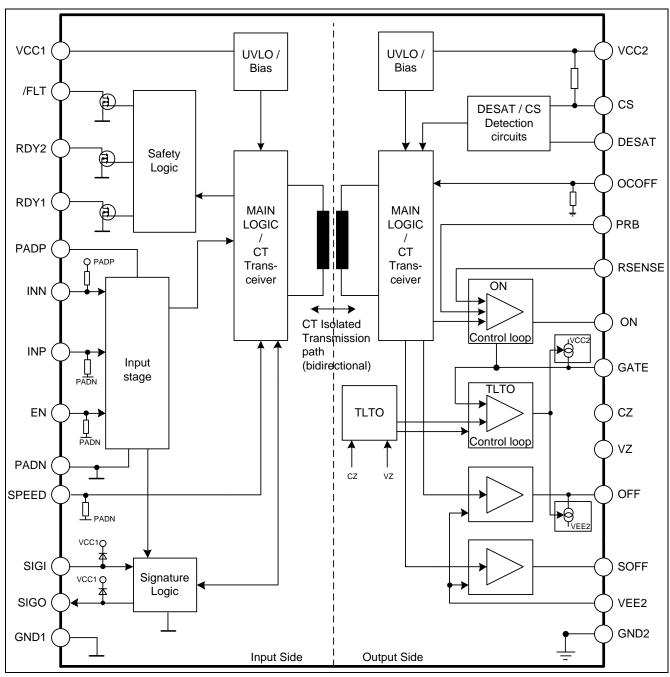

## 1 Block diagram

Figure 1 Block diagram for the 1EDS-SRC family

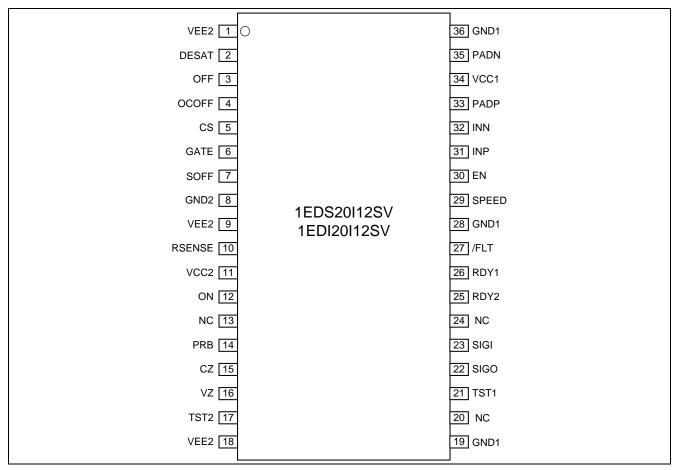

## 2 Pin configuration, description, and functionality

## 2.1 Terminal configuration

Figure 2 Terminal configuration of the 1EDS-SRC family (Top View)

Table 1 Terminal Description

| Terminal number | Terminal<br>name | Description                        |

|-----------------|------------------|------------------------------------|

| 1               | VEE2             | Negative power supply, output side |

| 2               | DESAT            | Desaturation shut down protection  |

| 3               | OFF              | Gate turn-off                      |

| 4               | OCOFF            | Overcurrent protection on/off      |

| 5               | CS               | Sense IGBT overcurrent             |

| 6               | GATE             | Gate voltage sense                 |

| 7               | SOFF             | Gate soft turn-off                 |

| 8               | GND2             | Signal ground, output side         |

| 9               | VEE2             | Negative power supply, output side |

| 10              | RSENSE           | Sense resistor input               |

| 11              | VCC2             | Positive power supply, output side |

Table 1 Terminal Description

| Terminal number | Terminal<br>name | Description                                   |

|-----------------|------------------|-----------------------------------------------|

| 12              | ON               | Gate control for external p-channel MOSFET    |

| 13              | NC               | Not connected, connection to GND2 recommended |

| 14              | PRB              | Preboost current adjustment                   |

| 15              | CZ               | Two-level turn-off time set                   |

| 16              | VZ               | Two-level turn-off voltage set                |

| 17              | TST2             | Reserved terminal, to be connected to VEE2    |

| 18              | VEE2             | Negative power supply, output side            |

| 19              | GND1             | Ground, input side                            |

| 20              | NC               | Not connected, connection to GND1 recommended |

| 21              | TST1             | Reserved terminal, to be connected to GND1    |

| 22              | SIGO             | Signature test output                         |

| 23              | SIGI             | Signature test input                          |

| 24              | NC               | Not connected, connection to GND1 recommended |

| 25              | RDY2             | Ready signal, monitoring the output side      |

| 26              | RDY1             | Ready signal, monitoring the input side       |

| 27              | /FLT             | Fault output                                  |

| 28              | GND1             | Ground, input side                            |

| 29              | SPEED            | Setting of IGBT gate current level (analog)   |

| 30              | EN               | Enable, shutdown, and fault reset input       |

| 31              | INP              | Non-inverting driver input                    |

| 32              | INN              | Inverting driver input                        |

| 33              | PADP             | Input side logic reference voltage            |

| 34              | VCC1             | Positive power supply, input side             |

| 35              | PADN             | Input side logic reference ground             |

| 36              | GND1             | Ground, input side                            |

## 2.2 Terminal functionality

## GND1

Logic ground terminal of the input side.

## **PADN**

Input side logic reference ground. Direct connection to GND1 is required.

## VCC1

5 V power supply for the input side.

The reference terminal for VCC1 is GND1.

## **PADP**

3.3 V, 5 V or 15 V input side logic reference voltage.

The reference terminal for PADP is PADN.

## INN inverting driver input

INN control signal for the driver output while INP is set to high. The IGBT is turned on, if INN is set to low, and is turned off, if INN is set to high, respectively. A minimum pulse width is required to prevent from glitches while controlling the IGBT. An internal pull-up resistor ensures that the IGBT is kept in off-state, if terminal INN is left unconnected.

The reference terminal for INN is PADN.

## INP non-inverting driver input

INP control signal for the driver output while INN is set to low. The IGBT is turned on, if INP is set to high, and is turned off, if INP is set to low, respectively. A minimum pulse width is required to suppress glitches while controlling the IGBT. An internal pull-down resistor ensures that the IGBT is kept in off-state, if terminal INP is left unconnected.

The reference terminal for INP is PADN.

## **EN** input

Terminal EN needs to be set high for INP and INN to control the IGBT switching.

The EN input terminal serves two purposes:

**Feature 1**: Enable / shutdown of the output side. The IGBT is turned off by a soft turn-off, if terminal EN is set to low. A minimum pulse width is defined to help suppress glitches on terminal EN.

The IGBT is switched on without preboost on the rising edge of terminal EN, if terminal INP is set high and terminal INN is set low before activating EN.

**Feature 2**: Resets the desaturation or overcurrent condition signaled on terminal /FLT, if terminal EN is set to low for more than 870 ns. A reset of signal /FLT is asserted at the rising edge of terminal EN.

The reference terminal for EN is PADN.

#### **SPEED**

IGBT on-state gate current setting sent from input side. This is an analog input terminal. The reference voltage of the internal ADC is PADP. The reference terminal for SPEED is PADN.

## /FLT fault output

Open-drain output terminal to signal desaturation of conventional IGBTs or overcurrent of sense IGBTs. Terminal /FLT is set low, if desaturation or overcurrent occurs. The /FLT terminal has to be connected via a pull-up resistor to PADP.

The reference terminal for /FLT is GND1.

## RDY1 ready status

Open-drain output to signal the proper operation of the input side. RDY1 is set to high if the input side terminals VCC1 and PADP are above their respective undervoltage thresholds. The RDY1 terminal should be connected a via pull-up resistor to PADP.

The reference ground terminal for RDY1 is GND1.

#### **RDY2** ready status

Open-drain output to signal the proper operation of the output side. RDY2 is set to high, if the output side supply is above the UVLO2 level and the internal chip data transmission is operating properly. The RDY2 terminal should be connected via a pull-up resistor to PADP.

The reference ground terminal for RDY2 is GND1.

#### SIGI

I/O signature check input terminal.

The reference terminal for SIGI is GND1.

#### **SIGO**

I/O signature check output terminal The reference terminal for SIGO is GND1.

## TST1

Terminal TST1 is a reserved terminal and has to be connected to GND1.

#### TST2

TST2 is a reserved terminal and has to be connected to VEE2.

#### VEE2

Negative power supply terminal for the output side: All VEE2 terminals must be connected to GND2, if no separate negative supply voltage is used.

## **DESAT**

Monitoring of the IGBT saturation voltage  $V_{\text{CE(sat)}}$  to detect desaturation caused by a short: The IGBT is shut down by activating soft turn-off, if the voltage at this pin is above a given threshold. Two additional filters provide a large robustness against noise and coupling effects. One of these filters is adjustable in terms of the filter time. The reference terminal for DESAT is GND2.

### **OFF**

Gate turn-off terminal in normal operation mode The reference terminal for OFF is VEE2.

## **OCOFF**

Input terminal to inhibit the automatic turn-off of the IGBT in case of a desaturation or current sense failure. The fault status continues to be signaled on terminal /FLT. This feature is deactivated by an internal pull-down resistor to GND2, if the terminal is left open.

The reference terminal for OCOFF is GND2

## CS

Current sense comparator input terminal for sense IGBTs or standard IGBTs with external emitter shunts. The reference terminal for CS is GND2. This feature is deactivated, if terminal CS is connected to GND2.

## **GATE**

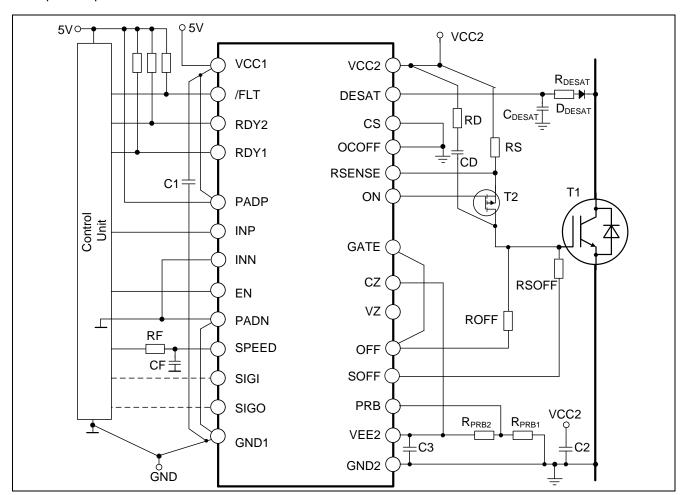

Input terminal for sensing the gate voltage at resistor ROFF, for example according to Figure 3.

The reference terminal for GATE is GND2.

## **PRB**

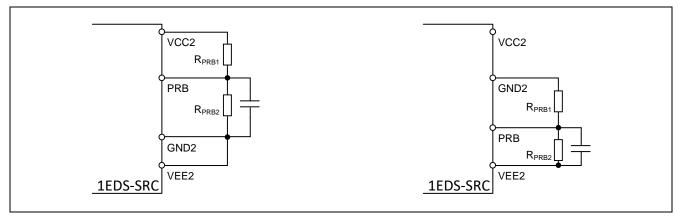

The preboost current is adjusted by means of a voltage divider between GND2 and VEE2 for a bipolar supply. The voltage divider is connected to VCC2 and VEE2 for unipolar supply.

The reference terminal for PRB is VEE2.

#### **SOFF**

Output terminal for IGBT soft turn-off in case of short circuit or overcurrent events. The reference terminal for SOFF is VEE2.

## GND2

Reference ground terminal of the output side.

### **RSENSE**

Current sense feedback input of the turn-on gate current control loop.

The reference terminal for RSENSE is VCC2.

## VCC2

Positive power supply terminal of the output side.

#### ON

Terminal for the connection to the gate terminal of an external p-channel MOSFET, such as OptiMOS™ BSD314SPE. This transistor is used to control the IGBT turn-on gate current.

The reference terminal for ON is VCC2.

#### CZ

This terminal sets the two-level turn-off timing via an external capacitor against VEE2. A short between terminals CZ and VEE2 deactivates the two-level turn-off.

The reference terminal for CZ is VEE2.

### ٧Z

Voltage adjustment terminal for the two-level turn-off feature: This terminal can be connected to VEE2 via a resistor of 27 k $\Omega$  ( $V_{\rm TLTO}$  = 9.3 V), shorted against VEE2 ( $V_{\rm TLTO}$  = 11.4 V), or left floating ( $V_{\rm TLTO}$  = 10.3 V). The reference terminal for VZ is VEE2.

## 3 Functional description

### 3.1 Introduction

The 1EDS-SRC family is an advanced IGBT gate driver family with various control and protection features to allow the design of highly reliable systems. The integrated circuit consists of two galvanically isolated sides, called input side and output side. The input side is typically interfaced with a CMOS-compatible DSP or a microcontroller. The galvanically isolated output side is connected to the high voltage domain. The adjustable gate current source allows the tuning of the IGBT turn-on slew rate to control the EMI of power electronic systems.

The turn-off process is accomplished with an internal MOSFET stage capable of driving 2 A. An internal MOSFET switch capable of driving 1 A could be connected to an external gate resistor with higher resistance to prevent from an overvoltage at the IGBT in case of a short circuit or an overcurrent shut down.

The driver also includes IGBT desaturation protection for conventional IGBTs and overcurrent protection for sense IGBTs with the fault status signal at the input side. Two ready status output terminals indicate whether the driver is properly supplied and operates normally. A two-level turn-off feature with adjustable delay protects against excessive overvoltage at turn-off in case of an overcurrent or a short. The same delay is applied at turn-on to prevent pulse width distortions.

Figure 3 Typical application

## 3.2 IC Supply

There are three supply voltage domains available having individual undervoltage lockout levels. The IC is in a safe state during undervoltage lockout of any domain under all circumstances, meaning that the gate drive outputs are never activated before each part of the IC is ready to operate.

Final datasheet 13 < Revision 2.1>, 22.10.2018

## 3.2.1 Input side

The driver is supplied with 5 V between terminals VCC1 to GND1. This supply voltage manages the basic functions of the input side. The input side contains a second voltage domain for the logic input signals INP, INN, and EN. This special voltage domain is supplied by the terminals PADP and PADN and can range from 3.3V over 5V to 15V. It is mandatory to connect directly the terminals PADN and GND1. It is important to note, that the voltage domains VCC1 and PADP have independent undervoltage lockout levels and both domains must be supplied appropriately for operation.

VCC1 can be shorted to GND1 in order to deactivate the driver. No turn-on signals will be transmitted from the input to the output side even if terminal VCC1 is left floating. Therefore, the IGBT won't be turned on.

## 3.2.2 Output side

The EiceDRIVER™ 1EDS-SRC family is designed to support both bipolar and unipolar power supply configurations. The driver IC is typically supplied with a positive voltage of 15 V on terminal VCC2 and a negative voltage of -8 V on terminal VEE2, if configured for bipolar supply. The driver IC is typically supplied with a positive voltage of 15 V on terminal VCC2 for a unipolar supply configuration. VEE2 and GND2 have to be connected together as short as possible for unipolar supply.

## 3.3 Non-inverting and inverting input terminals INP and INN

There are two input modes to control the IGBT. In non-inverting mode, terminal INP controls the driver output while terminal INN is set to low. In inverting mode, terminal INN controls the driver output while terminal INP is set to high. A low signal at terminal INN will activate the output ON. A minimum input pulse width is defined to suppress potential glitches.

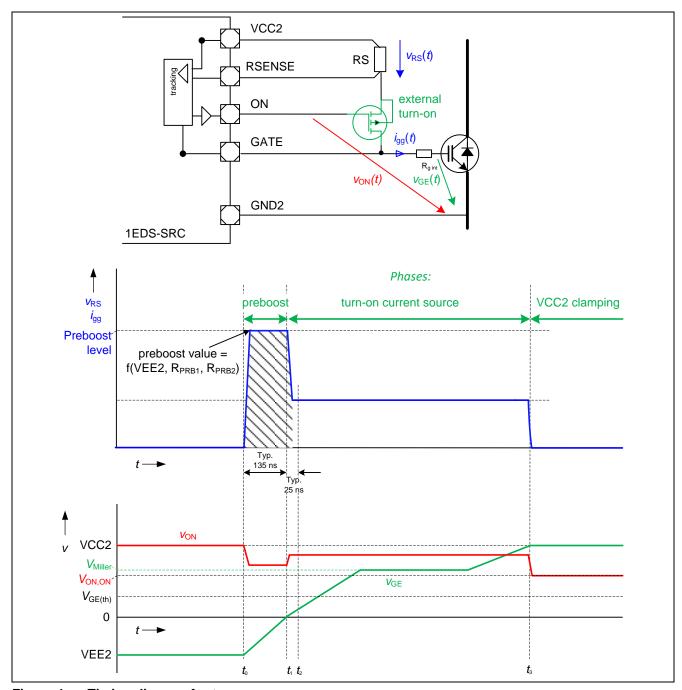

## 3.4 Driver output terminal ON

The output side contains an integrated feedback control for the IGBT gate current. The gate current control is completed by the external current sense resistor and a p-channel MOSFET. Several resistors and MOSFETs can be placed in parallel in order to limit the individual power dissipation. The recommended P-channel transistor is BSD314SPE (OptiMOS $^{TM}$ -P 3, 30 V, 140 m $\Omega$ ).

The entire turn-on procedure of an IGBT is separated into three phases according to Figure 4: the preboost, the turn-on, and the VCC2 clamping phase.

The preboost phase controls a high current to drive the gate of the IGBT. The gate voltage is increased from its starting point to a voltage lower than the gate-emitter threshold voltage of the IGBT, i.e.  $V_{GATE} < V_{GE(th)}$ , within a period of typ. 135 ns. It is important that the IGBT is not turned on during the preboost phase. The value of the preboost current  $I_{PRB}$  is proportional to the voltage  $V_{PRB}$  at terminal PRB. The preboost current  $I_{PRB}$  is defined as:

$$I_{PRB} = \left| \frac{2 \cdot V_{PRB}}{3 \cdot RS} \right| \tag{1}$$

The change from the preboost phase into the turn-on phase needs less than typically 25 ns. This time must be considered for the setting of the preboost current amplitude in order not to overcharge the gate during the preboost phase.

The gate current during the turn-on phase can be selected out of 11 levels for the proper adjustment of the turn-on transition. The fine granularity between levels 1 and 10 allows accurate slope control. It behaves similar as a traditional driver at level 11. The driver controls the voltage drop across the sense resistor RS. The corresponding gate current  $I_{gg}$  is

$$I_{gg} = \frac{V_{RSENSE}}{R_{SENSE}} \tag{2}$$

The selection of the gate current for the turn-on phase is accomplished with terminal SPEED on the input side. Terminal SPEED is an input terminal with voltage levels between 0 V and 3.3 V. The lowest voltage at terminal SPEED corresponds with the highest gate current level, e.g. by connecting SPEED to GND1.

Figure 4 Timing diagram for turn-on

Finally, the IGBT gate voltage saturates at VCC2 in the VCC2 clamping phase. The driver clamps the gate voltage of the external P-channel transistor 6 V below VCC2 according to Figure 4. This provides a low-resistive connection between the gate of the IGBT and terminal VCC2

It is good board layout engineering to keep tightest proximity of the control loop consisting of driver IC, sense resistor, p-channel MOSFET, and the VCC2 / VEE2 blocking capacitors to avoid oscillations.

## 3.5 SPEED setting

The 11 levels of gate current can be selected by applying an analog voltage  $V_{\text{SPEED}}$  at terminal SPEED according to the table below.

| I UDIC Z | Owntoning special levels on input and output side |                                |                                     |  |  |  |

|----------|---------------------------------------------------|--------------------------------|-------------------------------------|--|--|--|

|          | Voltage at terminal SPEED                         | Typ. reference $V_{ m RSENSE}$ | % of turn-on gate current amplitude |  |  |  |

| Level 1  | 3.3 V                                             | V <sub>VCC2</sub> -0.197       | 20%                                 |  |  |  |

| Level 2  | 2.91 V                                            | V <sub>VCC2</sub> -0.287       | 29%                                 |  |  |  |

| Level 3  | 2.63 V                                            | V <sub>VCC2</sub> -0.376       | 38%                                 |  |  |  |

| Level 4  | 2.35 V                                            | V <sub>VCC2</sub> -0.466       | 46%                                 |  |  |  |

| Level 5  | 2.08 V                                            | V <sub>VCC2</sub> -0.556       | 56%                                 |  |  |  |

| Level 6  | 1.80 V                                            | V <sub>VCC2</sub> -0.645       | 64%                                 |  |  |  |

| Level 7  | 1.52 V                                            | V <sub>VCC2</sub> -0.735       | 73%                                 |  |  |  |

| Level 8  | 1.25 V                                            | V <sub>VCC2</sub> -0.825       | 82%                                 |  |  |  |

| Level 9  | 0.97 V                                            | V <sub>VCC2</sub> -0.912       | 91%                                 |  |  |  |

| Level 10 | 0.69 V                                            | V <sub>VCC2</sub> -1.003       | 100%                                |  |  |  |

| Level 11 | 0                                                 | V <sub>VCC2</sub> -1.543       | 154%                                |  |  |  |

Table 2 Switching speed levels on input and output side

## 3.6 Preboost setting

The preboost control is always active, both in bipolar or unipolar power supply configuration. The only exception is, if the IGBT is turned on via EN according to section 3.8

The preboost current may be set by a simple voltage divider for bipolar gate supply as well as for unipolar supply. In case of bipolar power supply, connect the voltage divider between GND2, PRB, and VEE2. In case of a unipolar power supply, use VCC2, PRB, and VEE2 according to Figure 5.

Figure 5 External circuit for setting of preboost current (left: unipolar supply; right: bipolar supply)

The selected preboost current amplitude should charge the IGBT gate from the negative voltage VEE2 to a value between 0 V and  $V_{\text{GE(th)}}$  of the IGBT within 135 ns. The corresponding IGBT gate charge curves should be consulted for the various collector-emitter voltages  $V_{\text{CE}}$  for best accuracy.

## 3.7 Gate turn-off terminal OFF

The driver IC is able to sink a minimum gate current of 2 A peak. The closed loop controlled sink MOSFET establishes the two-level turn-off function according to section 3.9.6 by controlling the second level during the turn-off process for an adjustable time period  $T_{\text{TLSET}}$ . An external turn-off boost transistor is recommended for larger sink current capability.

## 3.8 Terminal EN

Terminal EN is used to enable the input side for normal operation. A soft turn-off is initiated, when the signal at terminal EN is logic low regardless of the status of signals at terminals INP and INN. The status of EN is dominant over all communications over the insulation barrier. If therefore a shutdown is initiated via terminal EN during normal operation and an overcurrent is detected simultaneously, the IGBT is turned off via soft turn-off. However, /FLT is not activated as the chip is already being reset. /FLT will be activated after IC enable, if the overcurrent still exists on the next IGBT turn-on command.

Signals on terminal EN have also priority over INN and INP. The signals at terminal EN have to pass a noise filter. The EN signal is suppressed, if the pulse duration is shorter than the filter time and the driver reacts as described in Table 3.

Table 3 Driver IC status for EN, INP, and INN

| EN     | INP    | INN   | Result                       |

|--------|--------|-------|------------------------------|

| high   | high   | high  | regular turn-off / soft off* |

| high   | low    | low   | regular turn-off / soft off* |

| high   | high ↑ | low   | turn-on                      |

| high   | high   | low ↓ | turn-on                      |

| high ↑ | high   | low   | turn-on without preboost     |

| low↓   | high   | low   | Soft off                     |

<sup>\*</sup> soft turn-off only in case of simultaneous CS / DESAT event

A second function of the EN terminal is to reset the driver IC after an overcurrent event, which was triggered by the DESAT or CS function. The IC is reset by holding EN low. The fault indication at terminal /FLT follows on the next rising edge of signal EN

## 3.9 Protection and diagnosis features

## 3.9.1 Undervoltage lockout (UVLO)

The device is equipped with a system of defined undervoltage lockout (UVLO) levels on both the input and output side to ensure proper operation of the IGBT.

Any triggering of UVLO will turn-off the IGBT by means of the soft turn-off function. All signals at INP and INN are ignored until the voltage at terminals VCC1 recovers above  $V_{\rm UVLOH1}$  at terminals VCC1 and  $V_{\rm UVLOH3}$  at terminal PADP.

The IGBT is switched off via terminal OFF in case of an UVLO event at pin VCC2. Signals from the input side are ignored until VCC2 recovers to the power-up level of  $V_{\rm UVLOH2}$ . The IC will perform an immediate turn-on after recovery of VCC2 according to Table 4.

## 3.9.2 Ready and status output terminals

The ready signal RDY1 for the input side covers the following conditions:

- UVLO status of the input side supply voltage domains at terminals VCC1 and PADP

- Establishment of correct signal transmission from input side to output side across the insulation barrier

The ready signal RDY2 for the output side indicates after a short delay:

- UVLO status of the output side supply voltage VCC2

- Establishment of bidirectional signal transmission across the insulation barrier

Both signals are monitoring signals only and need not to be reset actively.

| Tubic 4 | Diliver 10 Sta | tus oveo at | 1001, 1002 | and the (E | ·· – ···g·· <i>)</i>                   |

|---------|----------------|-------------|------------|------------|----------------------------------------|

| VCC1    | VCC2           | PADP        | RDY1       | RDY2       | Result                                 |

| UVLO↓   | good           | good        | low        | X          | SOFF and 5µs watchdog                  |

| UVLO ↑  | good           | good        | high       | high       | acc. INP / INN (turn-on with preboost) |

| UVLO ↑  | good           | UVLO        | low        | high       | OFF                                    |

| good    | UVLO↓          | good        | high       | low        | activate OFF and SOFF simultaneously   |

| good    | UVLO ↑         | good        | high       | high       | acc. INP / INN (turn-on with preboost) |

| UVLO    | UVLO ↑         | good        | low        | high       | OFF                                    |

| X       | Х              | UVLO ↓      | low        | high       | SOFF and 5µs watchdog                  |

| good    | good           | UVLO ↑      | high       | high       | acc. INP / INN (turn-on with preboost) |

Table 4 Driver IC status UVLO at VCC1, VCC2 and PADP (EN = high)

## 3.9.3 Fault indication (terminal /FLT)

Terminal /FLT is the indicator for a triggered DESAT or CS event. It is pulled low by an internal FET. The /FLT function is reset by means of a low signal at terminal EN.

## 3.9.4 Watchdog

The bidirectional signal transmission across the insulation barrier is monitored by watchdogs on the input and output side. These are the most important ones:

- The IGBT is switched off via terminal SOFF and additionally switched off via terminal OFF, if the transmission fails for a given duration.

- A watchdog activates the terminal OFF after typically 5 µs in any case of a soft turn-off event.

## 3.9.5 I/O signature check

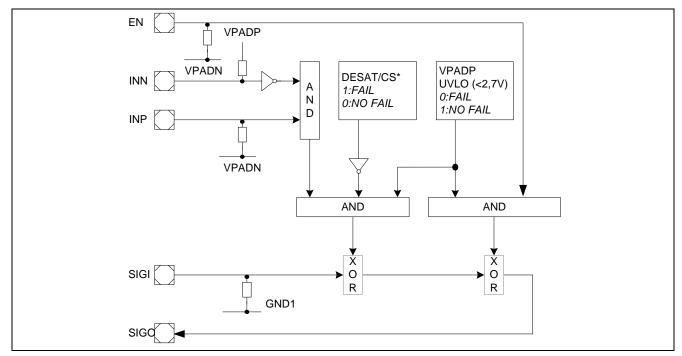

The I/O signature check is a feature that allows the confirmation of switching commands sent by the microcontroller to the driver IC. The SIGO output terminal is an exclusive-or (XOR) combination of the terminals INN, INP, and EN according to Figure 6. The desaturation status on terminal DESAT and the correct voltage at terminal PADP are also monitored.

Figure 6 I/O signature check

18

To save PCB space, the SIGI and SIGO terminals of a series of drivers can be interconnected via a daisy chain. In this case, terminal SIGI of the first driver in the daisy chain should be connected to VCC1 or GND1. Terminal SIGI of the next driver should be connected to terminal SIGO of the previous driver. Terminal SIGO of the last driver in the daisy chain should be connected to the microcontroller.

The I/O signature check does not monitor the status of the IGBT.

#### Monitored status

- INN / INP and EN

- DESAT

- PADP undervoltage

The reference terminals are VCC1 and GND1.

## 3.9.6 Two-level turn-off (TLTO)

The TLTO function is activated, if a capacitor is applied between terminal CZ and terminal VEE2. It affects any turn-on and turn-off process, which is either initiated by the input signals INP, INN or EN or by any protection function on the output side. Connecting terminal CZ with terminal VEE2 will deactivate the two-level turn-off function.

The two-level turn-off introduces a second (lower) gate voltage level during the turn-off process according to Figure 15This additional level ensures lower collector-emitter voltage overshoots during turn-off. The second gate voltage level reduces the collector current of the IGBT when reaching this level. The obtained dic/dt is therefore slower and generates less induced overvoltage. The required timing, which can be adjusted by the capacitance value at terminal CZ, depends on stray inductance and overcurrent at the beginning of the two-level turn-off period.

Three voltage levels are available:

- The voltage level is set to 11.4 V, if terminal VZ is connected to VEE2,

- the voltage level is set to 10.3 V, if terminal VZ is floating,

- the voltage level is set to 9.3 V, if terminal VZ is connected to VEE2 via a 27 kΩ resistor

The second voltage level is set in a way that turn-off losses are the same as during normal turn-off for nominal current values. The turn-on signal is delayed by the duration of the two-level turn-off in order to achieve identical pulse lengths.

The duration of the plateau is set by the capacitor connected between terminals CZ and VEE2.

The IC starts charging the capacitance on CZ for obtaining the two-level set time  $T_{TLSET}$ , when a turn-on signal is given. The IC starts the turn-on sequence and resets the capacitor at terminal CZ as soon as the voltage at terminal CZ exceeds 2.5 V.

The IC activates additionally a soft turn-off sequence, if a turn-off is initiated due to a desaturation condition on terminal DESAT.

## 3.9.7 Desaturation shut down protection

Desaturation protection ensures the protection of the IGBT in case of a short. When the desaturation voltage on terminal DESAT rises and reaches 9 V, the output is driven low by soft turn-off and the /FLT output terminal is activated. The blanking time is determined by the combination of the highly precise internal current source and an external capacitor. Desaturation protection is only set active at  $T_{\rm DESATleb} = 400$ ns after the preboost phase.

## 3.9.8 IGBT overcurrent detection

The IGBT overcurrent detection is a protection feature that senses the emitter current on current-sense IGBTs or standard IGBTs via using an emitter shunt resistor. The voltage is measured by a comparator that triggers at 0.35 V. The current sense signal at terminal CS is ignored while the IGBT is off. An external blanking circuit is necessary to prevent false tripping during turn-on. With non-sensing IGBT types, a low resistance shunt is used to sense the emitter current. When a short is detected, the IGBT is switched off by a soft turn-off. Both the desaturation and the current sense features can be used at the same time. This function is therefore not limited to current sensing. It can be used for any shut down condition as well. The fault status is signaled on terminal

/FLT. The fault status has to be reset via terminal EN. IGBT overcurrent detection is only active 400ns after the preboost phase.

## 3.9.9 Overcurrent protection ON/OFF

The IGBT is switched off via a soft turn-off in case of a CS or DESAT event, if terminal OCOFF is connected to GND2 or left unconnected. If terminal OCOFF is connected to VCC2, the IGBT is not switched off in such cases. However, the signaling of CS or DESAT events to output /FLT is done in any case. The IGBT can be turned off externally instead, e.g. via control input EN.

## 3.9.10 Soft turn-off

The IGBT can be turned off smoothly via an external higher-ohmic gate resistor attached to terminal SOFF. The soft turn-off speed can be adjusted by selecting the appropriate resistor value. The soft turn-off reduces the voltage overshoot considerably and may be used in combination with the two-level turn-off function of the IC. The regular turn-off function at terminal OFF supports the soft turn-off as soon as the voltage between terminals GATE and VEE2 drops below 3 V. An additional safety feature is installed by means of a watchdog timer, which starts at the same time the soft turn-off is triggered. The watchdog turns off the IGBT in any case via terminal OFF after 5 µs. If the soft-off function is not used, both the terminals SOFF and OFF can be combined to increase the turn-off current capability of the IC.

## Trigger conditions for a soft turn-off:

- Desaturation condition at terminal DESAT

- Overcurrent condition at terminal CS

- Driver Enable OFF (EN equals GND1)

- UVLO1 of the input side supply VCC1

- UVLO of the input side logic reference PADP

- · Internal signal transmission error

## 4 Electrical parameters

## 4.1 Absolute maximum ratings

Note: Absolute maximum ratings are defined as ratings, which may lead to destruction of the integrated circuit when being exceeded. Unless otherwise noted all parameters refer to GND1 and to  $T_A = 25$ °C.

Table 5 Abs. maximum ratings

| Table 5 Abs. maximum ratings                                                                | _                        |            |                     |      |

|---------------------------------------------------------------------------------------------|--------------------------|------------|---------------------|------|

| Parameter                                                                                   | Symbol                   | Min.       | Max.                | Unit |

| Offset voltage V <sub>GND1</sub> – V <sub>VEE2</sub> 1EDI20I12SV and 1EDU20I12SV only       | $V_{ m OFFSET}$          | -1200      | 1200                | V    |

| Positive power supply input side                                                            | V <sub>VCC1</sub>        | -0.3       | 6.5                 |      |

| PADP voltage                                                                                | $V_{\mathrm{PADP}}$      | -0.3       | 16.05               |      |

| PADN voltage                                                                                | $V_{ m PADN}$            | -0.3       | 0.3                 |      |

| Positive power supply output side <sup>1</sup>                                              | $V_{ m VCC2}$            | -0.3       | 20.3                |      |

| Negative power supply output side <sup>1</sup>                                              | $V_{ m VEE2}$            | -12        | 0.3                 |      |

| Maximum power supply voltage output side ( $V_{ m VCC2}$ - $V_{ m VEE2}$ )                  | $V_{ m max2}$            | _          | 28                  |      |

| Voltage at terminals INN, INP, EN, RDY1, RDY2, /FLT                                         | $V_{\mathrm{TERMINAL}}$  | -0.3       | $V_{\mathrm{PADP}}$ |      |

| Voltage at terminals SIGI, SIGO, SPEED                                                      |                          | -0.3       | $V_{ m VCC1}$       |      |

| Voltage at terminal DESAT <sup>1</sup>                                                      |                          | -5         | $V_{ m VCC2}$       |      |

| Voltage at terminals OCOFF 1, GATE 2, OFF 2, SOFF 2                                         |                          | -0.3       | $V_{ m VCC2}$       |      |

| Voltage at terminal GATE <sup>3</sup>                                                       |                          | -0.3       | 5.5                 |      |

| Voltage at terminals CS <sup>1</sup> , VZ <sup>2</sup> , CZ <sup>2</sup> , PRB <sup>2</sup> |                          | -0.3       | 5.5                 |      |

| Voltage at terminal RSENSE, ON <sup>4</sup>                                                 |                          | -7         | $V_{ m VCC2}$       |      |

| Open drain output current (/FLT, RDY2, RDY1)                                                | $I_{ m OD}$              | _          | 10                  | mA   |

| Output current at terminals SIGO                                                            | $I_{ m SIGO}$            | -6         | 6                   |      |

| DC output current at terminal ON ( $V_{VCC2}$ - $V_{VEE2}$ = 20 V)                          | $I_{ m ON,DC}$           | _          | 10                  |      |

| Peak output current at terminal OFF ( $t_p = 2 \mu s$ , $f = 20 \text{ kHz}$ )              | $I_{ m OFF}$             | _          | 2.4                 | А    |

| Peak output current at terminal SOFF ( $t_p = 2 \mu s$ , $f = 20 \text{ kHz}$ )             | $I_{\mathrm{SOFF}}$      | _          | 1.05                |      |

| Junction temperature 1EDS20I12SV 1EDI20I12SV                                                | $T_{ m J}$               | -40<br>-40 | 125<br>150          | °C   |

| Storage temperature                                                                         | $T_{\mathrm{S}}$         | -55        | 125                 |      |

| Total power dissipation <sup>5</sup>                                                        | $P_{ m D,tot}$           | _          | 980                 | mW   |

| Thermal resistance (Both chips active), $T_A$ = 25 °C                                       | $R_{\text{th(j-a)}}$     | _          | 102                 | K/W  |

| $\Psi$ value                                                                                | $\Psi_{	ext{th(j-top)}}$ | _          | 6.69                |      |

|                                                                                             | •                        | •          |                     |      |

<sup>&</sup>lt;sup>1</sup> with respect to terminal GND2

Final datasheet 21 < Revision 2.1>, 22.10.2018

<sup>&</sup>lt;sup>2</sup> with respect to terminal VEE2

<sup>&</sup>lt;sup>3</sup> with respect to terminal OFF

<sup>&</sup>lt;sup>4</sup> with respect to terminal VCC2

<sup>&</sup>lt;sup>5</sup> Power dissipation is derated linearly with 9.8 mW/°C above an ambient temperature of  $T_A = 25$ °C. See Figure 17 for reference layouts for these thermal data. Thermal performance may change significantly with layout and heat dissipation of components in close proximity.

Table 5 Abs. maximum ratings

| Parameter                      |                | Symbol              | Min. | Max. | Unit  |

|--------------------------------|----------------|---------------------|------|------|-------|

| ESD Capability HBN             | M <sup>1</sup> | $V_{ m ESD}$        | _    | 750  | V     |

| CDI                            | M <sup>2</sup> |                     |      | 1000 |       |

| Common mode transient immunity |                | $ dV_{\rm ISO}/dt $ | ı    | 50   | kV/μs |

## 4.2 Operating range

Note: The IC operates as described in the functional description within the operating range. Unless otherwise noted all parameters refer to terminal GND1 and  $T_A = 25$ °C.

Table 6 Operating parameters

| Parameter                                                                           | Symbol                 | Min.                       | Тур. | Max.                        | Unit |

|-------------------------------------------------------------------------------------|------------------------|----------------------------|------|-----------------------------|------|

| Positive power supply input side                                                    | V <sub>VCC1</sub>      | 4.85                       | 5    | 5.5                         | V    |

| Input side logic reference voltage ranges $V_{\mathrm{PADP}}$ - $V_{\mathrm{PADN}}$ | $\Delta V_{ m PAD}$    | 3                          | 3.3  | 5.5                         |      |

|                                                                                     |                        | 7                          | 15   | 15.75                       |      |

| Control voltage by terminal SPEED at terminal RSENSE                                | V <sub>IN,RSENSE</sub> | V <sub>VCC2</sub> -<br>1.7 | -    | V <sub>VCC2</sub> -<br>0.2V |      |

| Voltage at terminal SPEED <sup>3</sup>                                              | $V_{ m SPEED}$         | 0                          | _    | 3.3                         |      |

| Positive power supply output side <sup>4</sup>                                      | V <sub>VCC2</sub>      | 0                          | 15   | 20                          |      |

| Negative power supply output side <sup>4</sup>                                      | $V_{ m VEE2}$          | -12                        | -8   | 0                           |      |

| Power supply voltage output side $(V_{VCC2} - V_{VEE2})$                            | $V_{ m max2}$          | _                          | -    | 25                          |      |

| Output current at terminal SIGO                                                     | $I_{ m SIGO}$          | -3                         | _    | 3                           | mA   |

| Ambient temperature                                                                 | $T_{\rm A}$            | -40                        | _    | 105                         | °C   |

<sup>&</sup>lt;sup>1</sup> According to EIA/JESD22-A114-B

<sup>&</sup>lt;sup>2</sup> According to EIA/JESD22-C101

$<sup>^3</sup>$  With respect to voltage  $V_{\mathrm{PADN}}$

$<sup>^4</sup>$  With respect to voltage  $V_{

m GND2}$

## 4.3 Electrical characteristics

Note: The electrical characteristics given below include the spread of values for the junction temperature range of  $-40^{\circ}\text{C} \le T_{\text{J}} \le 125^{\circ}\text{C}$ . All values refer to the supply condition of  $V_{\text{VCC1}} = V_{\text{PADP}} = 5 \text{ V}$ ,  $V_{\text{PADN}} = V_{\text{GND1}} = 0 \text{ V}$ ,  $V_{\text{VCC2}} = 15 \text{ V}$ ,  $V_{\text{VEE2}} = -8 \text{ V}$  and the given test conditions. Typical values represent the median values at  $T_{\text{A}} = 25^{\circ}\text{C}$  under the above mentioned supply conditions. Unless otherwise noted all voltages are given with respect to their respective reference terminal (GND1 for terminals 19 to 36, GND2 for terminals 1 to 18).

## 4.3.1 Voltage supply

Table 7 Voltage supply

| Parameter                            |                                   | Symbol             |      | Value | s    | Unit | Test condition                                                                                                                                                                              |

|--------------------------------------|-----------------------------------|--------------------|------|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      |                                   |                    | Min. | Тур.  | Max. |      |                                                                                                                                                                                             |

| UVLO threshold for VCC1              | power up                          | $V_{ m UVLOH1}$    | _    | 4.63  | 4.85 | V    |                                                                                                                                                                                             |

|                                      | power down                        | $V_{ m UVLOL1}$    | 3.5  | 4.47  | _    |      |                                                                                                                                                                                             |

| UVLO hysteresis VCC1 ( $V_{ m UV}$   | $V_{\rm LOH1}$ - $V_{\rm UVLOL1}$ | $V_{ m UVLO1,hys}$ | 0.08 | _     | _    |      |                                                                                                                                                                                             |

| UVLO threshold VCC2                  | power up                          | $V_{ m UVLOH2}$    | _    | 11.9  | 12.6 |      |                                                                                                                                                                                             |

|                                      | power down                        | $V_{ m UVLOL2}$    | 10.4 | 11.0  | _    |      |                                                                                                                                                                                             |

| UVLO hysteresis VCC2 (V <sub>U</sub> | $_{ m VLOH2}$ - $V_{ m UVLOL2}$ ) | $V_{ m UV,hys2}$   | 0.3  | -     | -    |      |                                                                                                                                                                                             |

| UVLO threshold for PADP              | power up                          | $V_{ m UVLOH3}$    | _    | _     | 2.95 |      |                                                                                                                                                                                             |

|                                      | power down                        | $V_{ m UVLOL3}$    | 1.6  | _     | _    |      |                                                                                                                                                                                             |

| Quiescent current input side \       | /CC1                              | $I_{\mathrm{Q1}}$  | -    | 9.6   | 13   | mA   | $V_{\mathrm{INP}} = V_{\mathrm{PADP}}, V_{\mathrm{INN}}$<br>$V_{\mathrm{PADN}}$<br>$V_{\mathrm{RDY1}} = V_{\mathrm{RDY2}} = V_{\mathrm{F}}$<br>$= V_{\mathrm{PADP}}$                        |

| Quiescent current input side \       | /CC1                              |                    | _    | 9.6   | 13   |      | $V_{\text{INP}} = V_{\text{PADP}} = 15$ $V_{\text{FLT}} = V_{\text{RDY1}} = V_{\text{RI}}$ $= 5 \text{ V}, V_{\text{INN}} = V_{\text{PAD}}$                                                 |

| Quiescent current output side        | VCC2                              | $I_{\mathrm{Q2}}$  | -    | 7.3   | 9.5  |      | $V_{\mathrm{INP}} = V_{\mathrm{PADP}}, V_{\mathrm{INN}}$ $V_{\mathrm{PADN}}$ $V_{\mathrm{RDY1}} = V_{\mathrm{RDY2}} = V_{\mathrm{F}}$ $= V_{\mathrm{PADP}}$                                 |

| Quiescent current output side mode   | in UVLO                           | $I_{ m Q2,UVLO}$   | _    | 4.5   | 6    |      | $V_{\rm VCC2}$ = 10.4 V                                                                                                                                                                     |

| Quiescent current output side        | VEE2                              | $I_{\mathrm{Q3}}$  | -    | 4.7   | _    |      | $egin{aligned} V_{\mathrm{INP}} &= V_{\mathrm{PADP}},  V_{\mathrm{INN}} \ V_{\mathrm{PADN}} \ V_{\mathrm{RDY1}} &= V_{\mathrm{RDY2}} = V_{\mathrm{F}} \ &= V_{\mathrm{PADP}} \end{aligned}$ |

| Quiescent current PADP               |                                   | $I_{\mathrm{Q4}}$  | -    | 1     | _    |      | $V_{\mathrm{INP}} = V_{\mathrm{PADP}}, \ V_{\mathrm{INN}}$ $V_{\mathrm{PADN}}$ $V_{\mathrm{RDY1}} = V_{\mathrm{RDY2}} = 5$ $V_{\mathrm{FLT}} = 5 \ \mathrm{V}$                              |

## 4.3.2 Logic input and output

Table 8 Logic input and output

| Parameter                                         | Symbol                             |               | Value | s             | Unit | Test condition                                         |

|---------------------------------------------------|------------------------------------|---------------|-------|---------------|------|--------------------------------------------------------|

|                                                   |                                    | Min.          | Тур.  | Max.          |      |                                                        |

| Low level input voltage terminals INP, INN, EN    | $V_{ m IL}$                        | 1.5           | _     | _             | V    |                                                        |

| High level input voltage terminals INP, INN, EN   | $V_{ m IH}$                        | _             | _     | 3.5           |      |                                                        |

| Low level input voltage terminal SIGI             | $V_{ m IL,SIGI}$                   | 1.5           | _     | _             |      |                                                        |

| High level input voltage terminal SIGI            | $V_{ m IH,SIGI}$                   | _             | _     | 3.5           |      |                                                        |

| Low level output voltage terminal SIGO            | $V_{ m OL,SIGO}$                   | $V_{ m GND1}$ | 0.1   | 0.3           |      | $I_{\rm IL,SIGO} = 3 \text{ mA}$                       |

| High level output voltage terminal SIGO           | $V_{ m OH,SIGO}$                   | 4.3           | 4.7   | $V_{ m VCC1}$ |      | $I_{\rm IH,SIGO}$ = - 3 mA                             |

| Low level output voltage terminal /FLT            | $V_{ m OL,FLT}$                    | _             | 0.08  | 0.3           |      | $I_{\rm IL,pin}$ = 3 mA                                |

| Low level output voltage terminals RDY1, RDY2     | $V_{ m OL,RDY1}, \ V_{ m OL,RDY2}$ | _             | 0.1   | 0.3           |      | $I_{\rm IL,pin}$ = 3 mA                                |

| Input bias current INP                            | $I_{ m IH,INP}$                    | 30            | 60    | 100           | μΑ   | $V_{\rm INP}$ = 5 V                                    |

| Input bias current EN                             | $I_{ m IH,EN}$                     | 30            | 60    | 100           |      | $V_{\rm EN}$ = 5 V                                     |

| Input bias current INN                            | $I_{ m IL,INN}$                    | -1200         | -700  | -350          |      | $V_{\mathrm{INN}} = OV$                                |

| Input bias current SPEED                          | $I_{ m IH,SPEED}$                  | 6             | 10    | 16            |      | $V_{\text{SPEED}} = 5 \text{ V}$                       |

| Input filter time terminals INP, INN, SIGI        | $T_{ m FILIN}$                     | 22            | _     | _             | ns   | $V_{\text{TERMINAL}} = 5 \text{ V}$                    |

| Input filter time terminal EN                     | $T_{ m FILEN}$                     | 45            | _     | _             |      | $V_{\rm EN}$ = 5 V                                     |

| Fault reset duration terminal EN                  | $T_{ m EN,RST}$                    | 870           | _     | _             |      | $V_{\rm EN} = 0 \text{V}, \ V_{\rm VEE2} = 0 \text{V}$ |

| Propagation delay EN to ON (Turn-On)              | $T_{ m EN,ON}$                     | _             | 530   | _             |      |                                                        |

| Shut down propagation delay EN to SOFF (Turn-Off) | $T_{ m EN,SOFF}$                   | _             | 530   | 680           |      | $V_{ m VEE2}$ = 0 V                                    |

## 4.3.3 Gate driver

Table 9 Gate driver

| Parameter                                                       | Symbol          | Values                       |                              |                                  | Unit | Test condition                      |

|-----------------------------------------------------------------|-----------------|------------------------------|------------------------------|----------------------------------|------|-------------------------------------|

|                                                                 |                 | Min.                         | Тур.                         | Max.                             |      |                                     |

| Voltage of sense resistor for gate current level 1              | $V_{ m RSENSE}$ | V <sub>VCC2</sub> -<br>0.165 | V <sub>VCC2</sub> -<br>0.197 | V <sub>VCC2</sub> -<br>0.230     | V    | $V_{\text{SPEED}} = 3.3 \text{ V}$  |

| Voltage of sense resistor for gate current level 2              |                 | V <sub>VCC2</sub> -<br>0.250 | V <sub>VCC2</sub> -<br>0.287 | V <sub>VCC2</sub> -<br>0.324     |      | $V_{\text{SPEED}}$ = 2.91 V         |

| Voltage of sense resistor for gate current level 3              |                 | V <sub>VCC2</sub> -<br>0.340 | V <sub>VCC2</sub> -<br>0.376 | V <sub>VCC2</sub> -<br>0.413     |      | $V_{\text{SPEED}} = 2.63 \text{ V}$ |

| Voltage of sense resistor for gate current level 4 <sup>1</sup> |                 | V <sub>VCC2</sub> -<br>0.420 | V <sub>VCC2</sub> -<br>0.466 | <i>V</i> <sub>VCC2</sub> - 0.512 |      | $V_{\text{SPEED}} = 2.35 \text{ V}$ |

| Voltage of sense resistor for gate current level 5              |                 | V <sub>VCC2</sub> -<br>0.510 | V <sub>VCC2</sub> -<br>0.556 | V <sub>VCC2</sub> -<br>0.601     |      | $V_{\text{SPEED}} = 2.08 \text{ V}$ |

$<sup>^{\</sup>rm 1}$  Default state after power on ( $V_{\rm VCC1}$  >  $V_{\rm UVLOH1})$

| Voltage of sense resistor for gate current level 6                | $V_{ m RSENSE}$    | V <sub>VCC2</sub> -<br>0.600     | V <sub>VCC2</sub> -<br>0.645     | V <sub>VCC2</sub> -<br>0.691     | V  | V <sub>SPEED</sub> = 1.80 V                      |

|-------------------------------------------------------------------|--------------------|----------------------------------|----------------------------------|----------------------------------|----|--------------------------------------------------|

| Voltage of sense resistor for gate current level 7                |                    | V <sub>VCC2</sub> -<br>0.680     | V <sub>VCC2</sub> -<br>0.735     | V <sub>VCC2</sub> -<br>0.790     |    | V <sub>SPEED</sub> = 1.52 V                      |

| Voltage of sense resistor for gate current level 8                |                    | V <sub>VCC2</sub> -<br>0.770     | V <sub>VCC2</sub> -<br>0.825     | V <sub>VCC2</sub> -<br>0.880     |    | V <sub>SPEED</sub> = 1.25 V                      |

| Voltage of sense resistor for gate current level 9                |                    | V <sub>VCC2</sub> -<br>0.825     | V <sub>VCC2</sub> -<br>0.912     | V <sub>VCC2</sub> -<br>0.999     |    | $V_{\rm SPEED}$ = 0.97 V                         |

| Voltage of sense resistor for gate current level 10               |                    | V <sub>VCC2</sub> -<br>0.910     | V <sub>VCC2</sub> -1.003         | V <sub>VCC2</sub> -<br>1.095     |    | $V_{\text{SPEED}} = 0.69 \text{ V}$              |

| Voltage of sense resistor for gate current level 11               |                    | <i>V</i> <sub>VCC2</sub> - 1.420 | <i>V</i> <sub>VCC2</sub> - 1.543 | <i>V</i> <sub>VCC2</sub> - 1.667 |    | $V_{\text{SPEED}} = 0 \text{ V}$                 |

| $V_{ m SPEED}$ hysteresis                                         | $V_{ m SPEED,hys}$ | _                                | _                                | 60                               | mV |                                                  |

| Low level output voltage terminal OFF                             | $V_{ m OFFL}$      | _                                | V <sub>VEE2</sub> +0.03          | V <sub>VEE2</sub> + 0.09         | V  | $I_{\rm OFFL}$ = 20 mA                           |

|                                                                   |                    | _                                | V <sub>VEE2</sub> +0.3           | V <sub>VEE2</sub> + 0.85         |    | $I_{\mathrm{OFFL}} = 200 \; \mathrm{mA}$         |

|                                                                   |                    | _                                | V <sub>VEE2</sub> +2.3           | V <sub>VEE2</sub> + 6            |    | I <sub>OFFL</sub> = 1 A                          |

|                                                                   |                    | _                                | V <sub>VEE2</sub> + 7.6          | _                                |    | I <sub>OFFL</sub> = 2 A <sup>1</sup>             |

| Low level output voltage terminal SOFF                            | $V_{ m SOFFL}$     | _                                | V <sub>VEE2</sub> +0.06          | V <sub>VEE2</sub> + 0.18         |    | I <sub>SOFFL</sub> = 20 mA                       |

|                                                                   |                    | _                                | V <sub>VEE2</sub> +0.6           | V <sub>VEE2</sub> + 1.7          |    | I <sub>SOFFL</sub> = 200 mA                      |

|                                                                   |                    | _                                | V <sub>VEE2</sub> +1.9           | V <sub>VEE2</sub> + 4.9          |    | $I_{\rm SOFFL} = 500 \text{ mA}$                 |

|                                                                   |                    | _                                | V <sub>VEE2</sub> +7.2           | _                                |    | $I_{\rm SOFFL}=1$ A <sup>1</sup>                 |

| Turn-on clamping voltage terminal ON                              | V <sub>ON,ON</sub> | _                                | V <sub>VCC2</sub> - 6.5          | V <sub>VCC2</sub> - 5.0          |    |                                                  |

| Turn-off threshold voltage terminal GATE <sup>2</sup>             | $V_{ m GATE,th}$   | _                                | 3                                | _                                |    |                                                  |

| Active Shut Down Voltage (VCC2 open)                              | $V_{ m ACTSD}$     | _                                | 1.4                              | 2.4                              |    | $I_{\rm OFF}$ = 200 mA,<br>$V_{\rm VEE2}$ = 0 V, |

| Output current of terminal ON                                     | $I_{\mathrm{ON+}}$ | 50                               | _                                | _                                | mA | <i>t</i> <sub>p</sub> =2 µs                      |

| Output current of terminal ON                                     | $I_{ m ON	ext{-}}$ | _                                | _                                | -50                              |    |                                                  |

| Preboost time                                                     | $T_{\mathrm{PRB}}$ | _                                | 135                              | 180                              | ns |                                                  |

| Speed setting propagation delay <sup>1</sup>                      | $T_{ m SPEED}$     | _                                | _                                | 120                              | μs | IGBT is turn on                                  |

| Fall time <sup>1</sup>                                            | $T_{ m FALL}$      |                                  | 8                                | -                                | ns | C <sub>LOAD</sub> = 1 nF                         |

| Turn-on propagation delay without PMOS                            | $T_{ m PDON}$      | _                                | 500                              | 540                              |    | $T_{\rm A}$ =25°C, $V_{\rm VEE2}$ =0V            |

| Turn-on propagation delay over junction temperature <sup>1</sup>  | $T_{ m PDONt}$     | _                                |                                  | 570                              |    | $V_{ m VEE2}$ = 0V                               |

| Turn-off propagation delay                                        | $T_{ m PDOFF}$     | _                                | 485                              | 535                              |    | T <sub>A</sub> =25°C, V <sub>VEE2</sub> =0V      |

| Turn-off propagation delay over junction temperature <sup>1</sup> | $T_{ m PDOFFt}$    | _                                | _                                | 565                              |    | $V_{ m VEE2}$ = 0 V                              |

| Matching delay (T <sub>PDON</sub> - T <sub>PDOFF</sub> )          | MT                 | _                                | 15                               | 30                               |    | $V_{ m VEE2}$ = 0 V                              |

|                                                                   |                    |                                  |                                  |                                  |    | <u> </u>                                         |

$<sup>^{\</sup>rm 1}$  The Parameter is not subject to production test - verified by design / characterization

$<sup>^{2}</sup>$  Reference to  $V_{

m VEE2}$

## 4.3.4 Desaturation protection

Table 10 Desaturation protection

| Parameter                                            | Symbol            |      | Values |      | Unit | Test condition                     |