## Dual 6 A H-Bridge With SPI

#### **Overview**

#### **Features**

- R<sub>DSon</sub> of 100 mW per switch typ. at Tj = 25 °C

- Logic inputs 3.3 V and 5.0 V TTL / CMOS-compatible

- Low standby current

- Chopper current limitation

- · Short circuit shut down with latch behavior

- · Overtemperature shut down with latch behavior

- V<sub>s</sub> undervoltage shutdown

- · Open load detection in ON and OFF state

- · Detailed SPI diagnosis or simple error flag

- Green product (RoHS compliant)

- AEC qualified

## **Description**

The TLE9202ED contains two independent general purpose 6 A H-Bridges in one Package. It is designed for (but not limited to) the control of DC motors or other inductive loads in automotive applications. The outputs can be pulse width modulated at frequencies up to 20 kHz. PWM/DIR control reduces the number of PWM capable pins needed on the microcontroller side.

For load currents above the current limitation threshold (8 A typ.) the H-Bridge goes into chopper current limitation mode. It is protected against short circuits and overtemperature and provides extensive diagnosis via SPI or basic error feedback via error flag. Open load can be detected when the bridge is disabled or during PWM operation of inductive loads.

| Туре      | Package      | Marking   |

|-----------|--------------|-----------|

| TLE9202ED | PG-DSO-36-72 | TLE9202ED |

# TLE9202ED Dual 6 A H-Bridge With SPI

## **Table of Contents**

| 1                  | Pin Configuration                 | . 3 |

|--------------------|-----------------------------------|-----|

| 1.1                | Pin Assignment                    |     |

| 1.2                | Pin Definitions and Functions     |     |

| 1.3                | Terms                             | 5   |

| 2                  | Block Diagram                     |     |

| 3                  | Block Description                 | . 7 |

| 3.1                | Power Supply                      | 7   |

| 3.2                | Sleep Mode                        | 7   |

| 3.3                | Output Stages                     | 8   |

| 3.4                | Protection and Diagnostics        |     |

| 3.5                | Current Limitation                |     |

| 3.6                | Short Circuit Detection           |     |

| 3.7                | Short Circuit to Battery          |     |

| 3.8                | Short Circuit over Load           |     |

| 3.9                | Overtemperature                   |     |

| 3.10               | Undervoltage Shut-Down            |     |

| 3.11               | Open Load Detection               |     |

| 3.11.1             | Open Load Detection in OFF state  |     |

| 3.11.2             | Open Load Detection in ON state   |     |

| 3.12               | Serial Peripheral Interface (SPI) |     |

| 3.12.1             | Error Flag                        |     |

| 3.12.2<br>3.12.2.1 | SPI Register Description          |     |

| 3.12.2.1           | Control Register                  |     |

| 3.12.2.2           | Revision Register                 |     |

|                    | •                                 |     |

| 4                  | General Product Characteristics   |     |

| 4.1<br>4.2         | Absolute Maximum Ratings          |     |

| 4.2<br>4.3         | Thermal Resistance                |     |

|                    |                                   |     |

| 5                  | Electrical Characteristics        | 19  |

| 6                  | Application Information           | 23  |

| 7                  | Package Outlines                  | 26  |

| 8                  | Revision History                  | 27  |

#### **Pin Configuration** 1

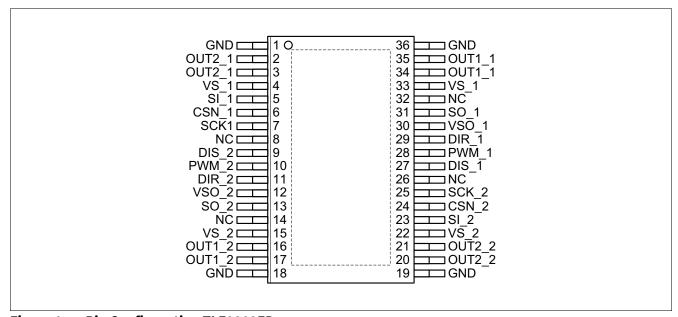

#### **Pin Assignment** 1.1

Figure 1 **Pin Configuration TLE9202ED**

#### **Pin Definitions and Functions** 1.2

Table 1 **Pin Defintions and Functions**

| Pin | Symbol            | Description                                                                                        |  |  |  |  |

|-----|-------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|

| 1   | GND <sup>1)</sup> | Ground                                                                                             |  |  |  |  |

| 2   | OUT2_1            | Output 2 of H-Bridge 1. Connect to Pin 3                                                           |  |  |  |  |

| 3   | OUT2_1            | Output 2 of H-Bridge 1. Connect to Pin 2                                                           |  |  |  |  |

| 4   | VS_1              | Supply voltage of H-Bridge 1. Connect to Pin 33                                                    |  |  |  |  |

| 5   | SI_1              | SPI serial input of H-Bridge 1                                                                     |  |  |  |  |

| 6   | CSN_1             | SPI chip select (low active) of H-Bridge 1                                                         |  |  |  |  |

| 7   | SCK_1             | SPI clock input of H-Bridge 1                                                                      |  |  |  |  |

| 8   | NC                | Not connected                                                                                      |  |  |  |  |

| 9   | DIS_2             | Disable. Disables the output (all MOSFETs off) of H-Bridge 2                                       |  |  |  |  |

| 10  | PWM_2             | Pulse width modulation input of H-Bridge 2                                                         |  |  |  |  |

| 11  | DIR_2             | Direction input to define direction of the motor current of H-Bridge 2                             |  |  |  |  |

| 12  | VSO_2             | Supply pin for SO output of H-Bridge 2<br>Connect to 5 V or 3.3 V depending on desired logic level |  |  |  |  |

| 13  | SO_2              | SPI serial output of H-bridge 2                                                                    |  |  |  |  |

| 14  | NC                | Not connected                                                                                      |  |  |  |  |

| 15  | VS_2              | Supply voltage of H-Bridge 2. Connect to Pin 22                                                    |  |  |  |  |

| 16  | OUT1_2            | Output 1 of H-Bridge 2. Connect to Pin 17                                                          |  |  |  |  |

## **Dual 6 A H-Bridge With SPI**

## **Pin Configuration**

Table 1 **Pin Defintions and Functions**

| Pin | Symbol            | Description                                                                                         |

|-----|-------------------|-----------------------------------------------------------------------------------------------------|

| 17  | OUT1_2            | Output 1 of H-Bridge 2. Connect to Pin 16                                                           |

| 18  | GND <sup>1)</sup> | Ground                                                                                              |

| 19  | GND <sup>1)</sup> | Ground                                                                                              |

| 20  | OUT2_2            | Output 2 of H-Bridge 2. Connect to Pin 21                                                           |

| 21  | OUT2_2            | Output 2 of H-Bridge 2. Connect to Pin 20                                                           |

| 22  | VS_2              | Supply voltage of H-Bridge 2. Connect to Pin 15                                                     |

| 23  | SI_2              | SPI serial input of H-Bridge 2                                                                      |

| 24  | CSN_2             | SPI chip select (low active) of H-bridge 2                                                          |

| 25  | SCK_2             | SPI clock input of H-Bridge 2                                                                       |

| 26  | NC                | Not connected                                                                                       |

| 27  | DIS_1             | Disable. Disables the output (all MOSFETS off) of H-Bridge 1                                        |

| 28  | PWM_1             | Pulse width modulation input of H-Bridge 1                                                          |

| 29  | DIR_1             | Direction input to define direction of the motor current of H-Bridge 1                              |

| 30  | VSO_1             | Supply pin for SO output of H-Bridge 1.<br>Connect to 5 V or 3.3 V depending on desired logic level |

| 31  | SO_1              | SPI serial output of H-Bridge 1                                                                     |

| 32  | NC                | Not connected                                                                                       |

| 33  | VS_1              | Supply voltage of H-Bridge 1, Connect to Pin 4                                                      |

| 34  | OUT1_1            | Output 1 of H-Bridge 1. Connect to Pin 35                                                           |

| 35  | OUT1_1            | Output 1 of H-Bridge 1. Connect to Pin 34                                                           |

| 36  | GND <sup>1)</sup> | Ground                                                                                              |

<sup>1)</sup> All ground pins (GND) have to be connected via a low ohmic, low inductive connection (e.g. a ground plane)

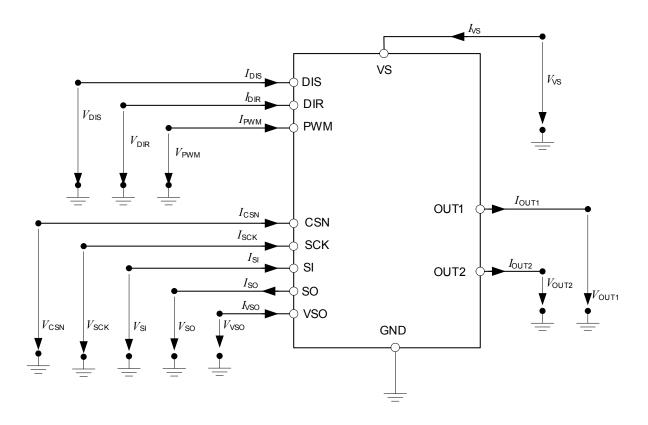

#### **Pin Configuration**

#### 1.3 Terms

Please note: For the sake of simplicity all following diagrams and parameters are describing one single H-Bridge only. To distuinguish between the two H-Bridges according to the pin assignment, the index "\_1" has to be added for H-Bridge 1 and index "\_2" has to be added for H-Bridge 2.

Figure 2 Terms TLE9202ED (Single H-Bridge)

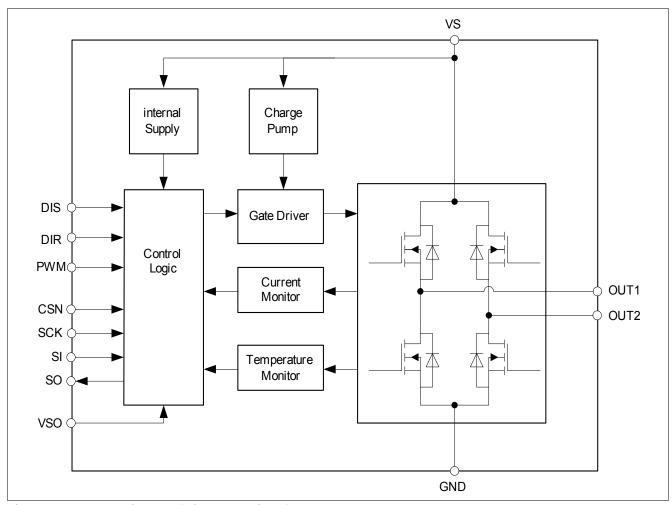

**Block Diagram**

#### **Block Diagram** 2

Block Diagram (Single H-Bridge) Figure 3

#### 3.1 **Power Supply**

All internal supply voltages are derived from the pin VS. A charge pump provides the gate voltage for the high side switches. The charge pump does not require an external capacitor.

The output buffer of the digital output SO is supplied by the pin VSO. Therefore the output level at SO can be easily configured for 3.3 V or 5 V logic by connecting VSO to the respective voltage.

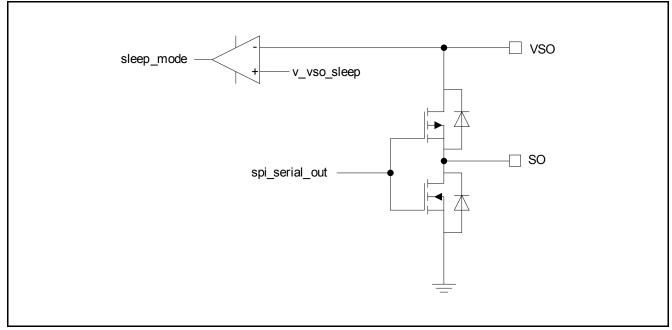

#### 3.2 **Sleep Mode**

In order to minimize current consumption during inactive phases the device can be put into sleep mode by pulling the VSO pin to GND. This functionality can also be used to provide a second switch off path for the outputs similar to an enable pin, simply by driving VSO directly from a microcontroller output.

Since VSO is supplying also the output buffer of the SO signal it has to be ensured that the microcontroller output can provide sufficient current. Alternatively an external mosfet or a driver stage could be used to switch the VSO supply voltage. To account for dynamic switching currents it might be advisable to buffer VSO with a small capacitor (see Figure 13 "Application Example VSO as Enable Input" on Page 25).

Please note that the push pull stage of the SO output provides a current return path to VSO via the bulk diode of the highside mosfet. Therefore it has to be ensured that the voltage at SO never exceeds the voltage at VSO by more than 0.3 V.

Figure 4 **SO** output buffer

#### 3.3 Output Stages

The output stages consist of four n-channel mosfets in H-bridge configuration. The outputs are protected against short circuits and over temperature.

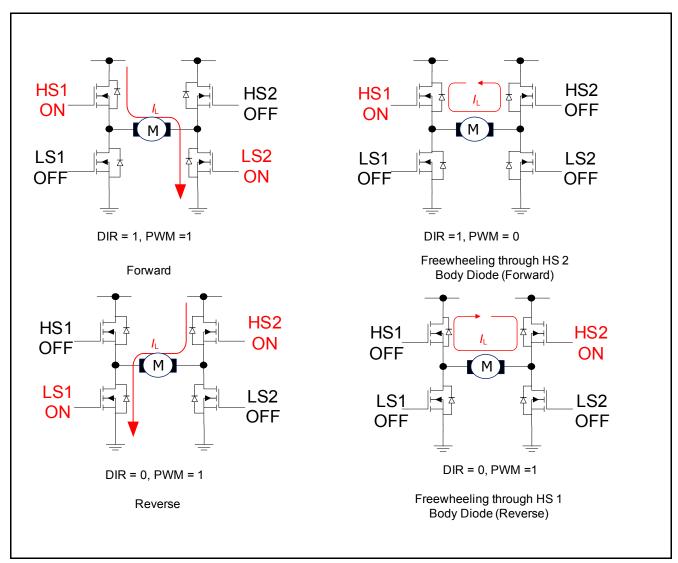

The bridge is controlled using the inputs PWM and DIR. The signal at DIR is defining the direction of the driven DC motor whereas the PWM signal sets the duty cycle.

The outputs can be set tristate (i.e. high side and low side switches are turned off) by setting DIS to high level.

Figure 5 Operation Modes

Table 2 Output Truth Table

| DIS | PWM | DIR | OUT1 | OUT2 | Comment                      |

|-----|-----|-----|------|------|------------------------------|

| 1   | Х   | Х   | Z    | Z    | disabled, outputs tristate   |

| 0   | 1   | 1   | Н    | L    | forward / clockwise          |

| 0   | 1   | 0   | L    | Н    | reverse / counterclockwise   |

| 0   | 0   | 1   | Н    | Z    | freewheeling in HS (forward) |

| 0   | 0   | 0   | Z    | Н    | freewheeling in HS (reverse) |

#### 3.4 Protection and Diagnostics

Both output stages of the TLE9202ED are equipped with fault diagnostic functions:

- Short to battery voltage (SCB)

- · Short to ground (SCG)

- Open load (OL)

- Over-temperature (OT)

#### 3.5 Current Limitation

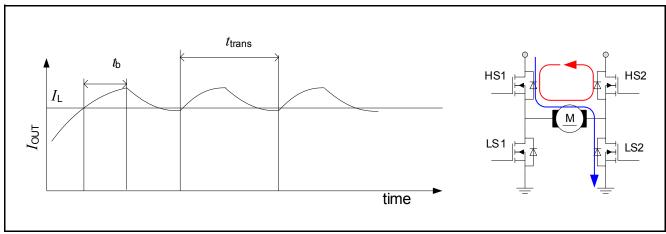

To limit the output current a chopper current limitation is integrated. Current measurement for current limitation is done in the high side path.

Figure 6 Chopper Current Limitation

**Figure 6** shows the behavior of the current limitation for over current detection in HS1. It applies accordingly also for HS2.

When the current in high-side switch of OUT1 (HS1) exceeds the limit  $I_L$  longer than the blanking time  $t_b$ , the low side switch of OUT2 (LS2) is switched off, independent of the input signal at PWM. This leads to freewheeling through the bulk diode of HS2 and therefore to a decrease of the load current. As soon as the current falls below  $I_L$ , OUT2 is switched back to normal operation, i.e. the outputs follow the inputs according to the truth table. To avoid high switching frequencies in case of low inductive loads the minimum time between two transitions is limited to  $t_{\rm trans}$ .

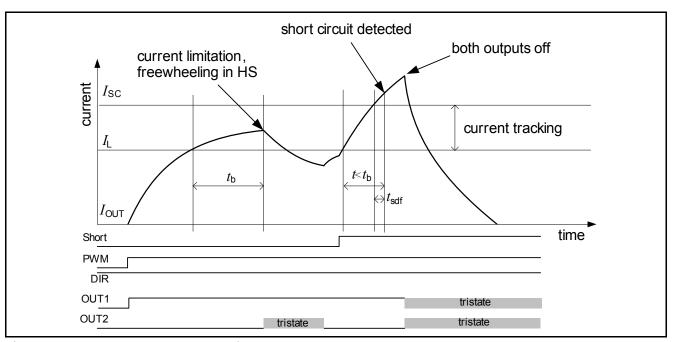

#### **Short Circuit Detection** 3.6

Figure 7 **Short to Ground Detection**

The short circuit to ground detection is activated when the current through one of the high side switches rises over the threshold  $I_{SC}$  and remains higher than  $I_{SC}$  for at least the filter time  $t_{sdf}$  within the blanking time  $t_b$ . Both outputs will be switched off and the failure will be reported in the SPI diagnosis register. The outputs can be re-activated by disabling and enabling the bridge via the disable signal DIS, pulling VSO to GND or by a reset command via SPI.

#### 3.7 **Short Circuit to Battery**

A short circuit to battery is detected in the same way as a short circuit to ground, only in the low side switch instead of the high side switch.

#### **Short Circuit over Load** 3.8

Short circuit over load will trigger the short circuit detection either of the high side or the low side switch (whichever is faster).

#### 3.9 **Overtemperature**

In case of high DC-currents, insufficient cooling or high ambient temperature, the chip temperature may rise above the thermal shut-down temperature  $T_{\rm iSD}$ . In that case, all output transistors are turned off. Overtemperature shutdown is latching.

The outputs can be re-activated as soon as the junction temperature has fallen below the switch-on temperature  $T_{iso}$ .

#### 3.10 Undervoltage Shut-Down

If the supply voltage at the VS pins falls below the undervoltage detection threshold  $V_{\rm UV\_OFF}$ , the outputs are turned off. The undervoltage detection is not latching. That means that as soon as  $V_{\rm S}$  rises above  $V_{\rm UV\_ON}$  again, the device is returning to normal operation.

#### 3.11 Open Load Detection

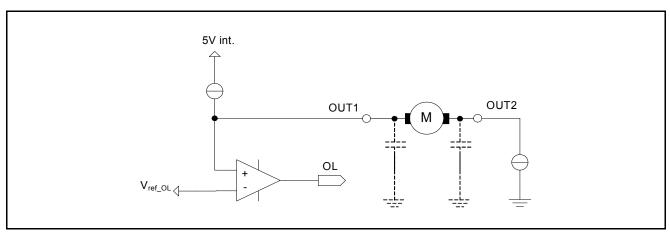

## 3.11.1 Open Load Detection in OFF state

When the bridge is disabled (DIS = high) the open load in OFF detection becomes active. Two diagnostic current sources will then be connected to the outputs, a pull up current source at OUT1 and a pull down current source at OUT2. The pull down current source is stronger than the pull up current source and therefore will pull down OUT1 if a load is present. If no load is present OUT1 will be pulled high by the pull up current source. This is detected by a comparator and reported in the SPI diagnosis register.

Please note that capacitors that might be placed at the outputs for EMC reasons first have to be discharged by the pull down current source at OUT2 for the open load detection to work properly.

Also, if current is flowing through the load at the time of disabling the freewheeling current will force the outputs towards supply voltage  $V_s$ . This may lead to an erroneous reporting of open load.

Therefore the first diagnostic reading after disabling should be discarded and a second reading should be taken after the load is deenergized and the output capacitors are discharged completely.

The open load detection can be disabled by setting the OLDIS bit in the CTRL\_REG register. This will disconnect the diagnostic current sources and suppress the reporting of open load in the DIA\_REG register.

Figure 8 Open Load Detection in OFF state

## 3.11.2 Open Load Detection in ON state

The TLE9202ED contains an open load diagnosis during operation for inductive loads. It evaluates whether freewheeling occurs in the switching phase. In order to avoid inadvertent triggering of the open load diagnosis a failure counter is implemented. There have to be at least 5 occurances of the internal open load signal (i.e. 5 PWM pulses without freewheeling detected) before open load is reported in the SPI diagnosis register.

Depending on the operation conditions and on external circuitry like the output capacitors it is possible that open load is indicated although the load is present. This might be the case for example during a direction change or for small load currents respectively small PWM duty cycles. Therefore it is recommended to evaluate the open load diagnosis only in known suitable operating conditions and to ignore it otherwise.

The open load diagnosis is not latching.

#### 3.12 Serial Peripheral Interface (SPI)

For diagnosis purposes the TLE9202ED is equipped with a "Serial Peripheral Interface" (SPI).

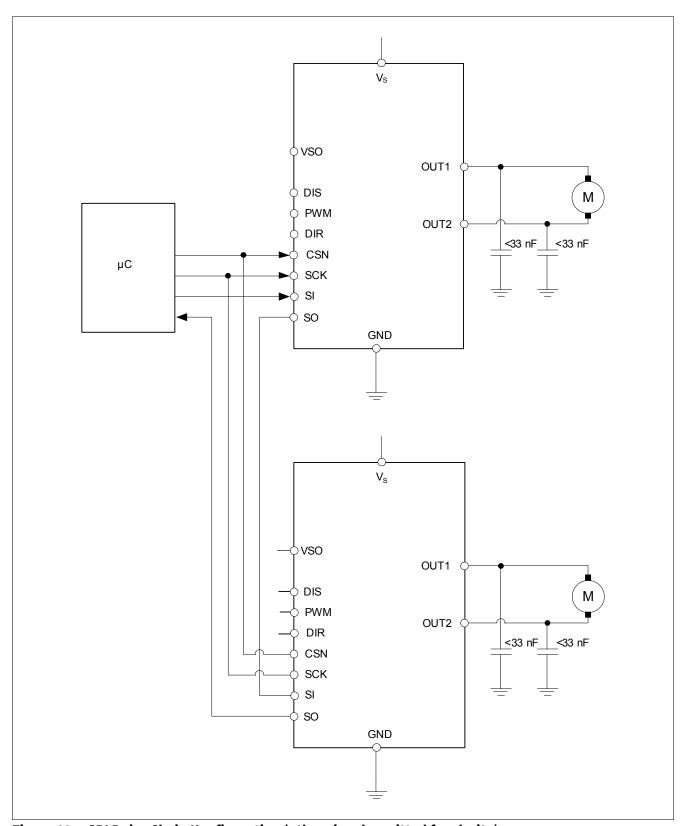

The SPI of several TLE9202EDs can be connected in daisy chain configuration in order to save microcontroller interface pins.

Both channels of the TLE9202ED is configured as a "slave" device. This means that the  $\mu$ C as the master is providing the chip select (CSN) and clock signal (SCK).

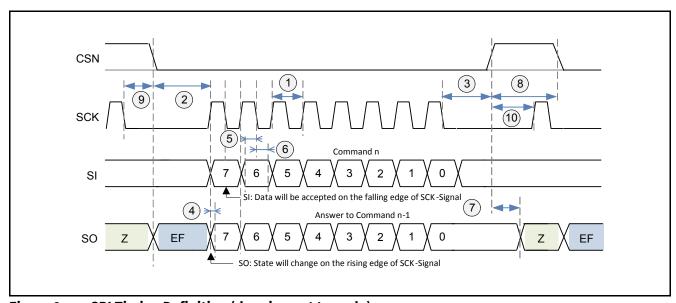

A data transfer on the SPI bus is initiaded with a falling edge on CSN and is terminated by a rising edge on CSN. The data on the serial input pin SI is sampled with the falling edge of SCK, the serial data output at SO is determined by the rising clock edge. The data is transferred "MSB first".

The word length of the SPI is 8 bit. Please note that there is no check for the number of clocks within a SPI frame. Any low pulse at CSN will be regarded as one frame.

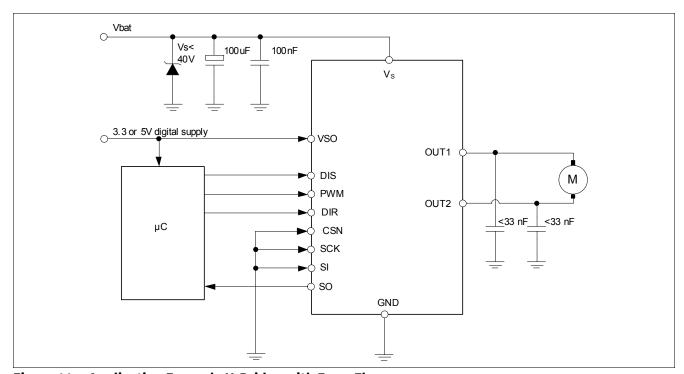

#### 3.12.1 Error Flag

Between the falling edge of CSN and the first rising edge of SCK an additional error flag signal is set asynchronously at the SO pin. The error flag signal set to high whenever the output stages are shut down (tristate) due to a failure or due to disabling of the output stages. Additionally the EF signal is OR'ed with the SI input signal. By connecting the SO of one device to the SI of the next device the EF signal can be routed through similar to a SPI daisy chain configuration.

This flag can be used for simple error feedback without SPI communication by connecting SCK and CSN to GND permanently (see Figure 11 "Application Example H-Bridge with Error Flag" on Page 23).

Figure 9 SPI Timing Definition (drawing not to scale)

## TLE9202ED **Dual 6 A H-Bridge With SPI**

#### **Block Description**

#### **SPI Register Description** 3.12.2

The TLE9202ED provides detailed diagnosis and the option to control the outputs via SPI. Following commands are available (x = don't care, d = data):

**SPI Command Set** Table 3

| Command               | Input Byte | Description                                                                                          |

|-----------------------|------------|------------------------------------------------------------------------------------------------------|

| RD_DIA                | 000x xxxx  | Read Diagnosis Register                                                                              |

| RES_DIA <sup>1)</sup> | 100x xxxx  | Reset Diagnosis Register                                                                             |

| RD_REV                | 001x xxxx  | Read Device Revision Number                                                                          |

| RD_CTRL               | 011x xxxx  | Read Control Register                                                                                |

| WR_CTRL               | 111d dddd  | Write Control - sets and returns Control Register values                                             |

| WR_CTRL_RD_DIA        | 110d dddd  | Write Control and Read Diagnosis- sets Control Register values and returns Diagnosis Register values |

<sup>1)</sup> After a RES\_DIA command, the device will respond with the Diagnosis register value

The first SPI response provided after power up is the device revision number (RD\_REV). For any unspecified commands the device will respond with the content of the diagnosis register (RD\_DIA).

## **Dual 6 A H-Bridge With SPI**

**Block Description**

## 3.12.2.1 Control Register

## **Control Register**

## CTRL\_REG **Control Register**

ResetValue:00<sub>H</sub>

|     | 7 | 6     | 5   | 4   | 3    | 2    | 1  | 0  |

|-----|---|-------|-----|-----|------|------|----|----|

| СМД |   | OLDIS | SIN | SEN | SDIR | SPWM |    |    |

|     |   | rw    |     | rw  | rw   | rw   | rw | rw |

| Field | Bits | Туре | Description                                                                                                                                                                                                                               |

|-------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD   | 7:5  | rw   | Command 011: RD_CTRL 110: WR_CTRL_RD_DIA 111: WR_CTRL                                                                                                                                                                                     |

| OLDIS | 4    | rw   | Open Load Disconnect  1: Open load current source disconnected.                                                                                                                                                                           |

| SIN   | 3    | rw   | SPI control 0: Control outputs via PWM/DIR inputs 1: Control outputs via SPI Note: can only be set if DIS=0 and PWM=0 and DIR=0. Any change of the DIS, PWM or DIR signals will reset this bit and revert to standard control via PWM/DIR |

| SEN   | 2    | rw   | 1: Enable outputs in case of SPI control (SIN=1) 0: Disable outputs in case of SPI control (SIN=1)                                                                                                                                        |

| SDIR  | 1    | rw   | DIR Signal in case of SPI control (SIN=1)                                                                                                                                                                                                 |

| SPWM  | 0    | rw   | PWM Signal in case of SPI control (SIN=1)                                                                                                                                                                                                 |

## **Dual 6 A H-Bridge With SPI**

**Block Description**

## 3.12.2.2 Diagnosis Register

#### **Diagnosis Register**

## DIA\_REG **Diagnosis Register**

Reset Value: DF<sub>H</sub>

| 7  | 6  | 5  | 4  | 3    | 2    | 1    | 0    |

|----|----|----|----|------|------|------|------|

| EN | ОТ | TV | CL | DIA4 | DIA3 | DIA2 | DIA1 |

| r  | r  | r  | r  | r    | r    | r    | r    |

| Field | Bits | Type | Description                                                                                    |

|-------|------|------|------------------------------------------------------------------------------------------------|

| EN    | 7    | r    | 1 = outputs enabled by low signal on pin DIS<br>0 = outputs disabled by high signal on pin DIS |

| ОТ    | 6    | r    | 0 = overtemperature shutdown                                                                   |

| TV    | 5    | r    | Always 0 - used for transmission validation                                                    |

| CL    | 4    | r    | 0 = current limitation active                                                                  |

| DIA4  | 3    | r    | Diagnosis bit 4                                                                                |

| DIA3  | 2    | r    | Diagnosis bit 3                                                                                |

| DIA2  | 1    | r    | Diagnosis bit 2                                                                                |

| DIA1  | 0    | r    | Diagnosis bit 1                                                                                |

#### **Diagnosis Truth Table**

The short circuit and VS undervoltage diagnosis is coded in the DIA bits according to the following truth table. Together with transmission validation bit TV (always 0) it is ensured that there is always at least one 1->0 change at SO during a valid transmission. Therefore a "stuck at" failure of the SO pin can be detected.

Table 4 **Encoding of Diagnosis Bits (sorted by hex value, only listed combinations are valid)**

| Туре                                                        | DIA4 | DIA3 | DIA2 | DIA1 | Hex | Comment        |

|-------------------------------------------------------------|------|------|------|------|-----|----------------|

| No failure                                                  | 1    | 1    | 1    | 1    | 0xF | -              |

| Short to GND at OUT1 (SCG1)                                 | 1    | 1    | 1    | 0    | 0xE | latched        |

| Short to Battery at OUT1 (SCB1)                             | 1    | 1    | 0    | 1    | 0xD | latched        |

| Open Load (OL)                                              | 1    | 1    | 0    | 0    | 0xC | not<br>latched |

| Short to GND at OUT2 (SCG2)                                 | 1    | 0    | 1    | 1    | 0xB | latched        |

| Short to GND at OUT1 and OUT2 (SCG1, SCG2)                  | 1    | 0    | 1    | 0    | 0xA | latched        |

| Short to Bat. at OUT1 and short to GND at OUT2 (SCB1, SCG2) | 1    | 0    | 0    | 1    | 0x9 | latched        |

| Short to Battery at OUT2 (SCB2)                             | 0    | 1    | 1    | 1    | 0x7 | latched        |

| Short to GND at OUT1 and short to Bat. at OUT2 (SCG1, SCB2) | 0    | 1    | 1    | 0    | 0x6 | latched        |

| Short to Battery at OUT1 and OUT2 (SCB1, SCB2)              | 0    | 1    | 0    | 1    | 0x5 | latched        |

| VS Undervoltage (VS_UV)                                     | 0    | 0    | 1    | 1    | 0x3 | not<br>latched |

#### **Dual 6 A H-Bridge With SPI**

#### **Block Description**

#### **Reset Behavior of Diagnosis Register**

The diagnosis register is reset by the following events:

Table 5 Diagnosis Reset Types

| Name | Туре           | Comment                                                                          |

|------|----------------|----------------------------------------------------------------------------------|

| POR  | Power On Reset | Reset due to power up, undervoltage or sleep mode                                |

| ENR  | Enable Reset   | Reset due to disabling/enabling of the outputs by DIS pin or bit SEN in CTRL_REG |

| SPIR | SPI Reset      | Reset by sending the RES_DIA command via SPI                                     |

A change of the DIR signal will lead to a reset of current limitation (CL) or open load in on (OL) error messages. The open load in on failure will also be reset automatically if the open load condition no longer persits, i.e. freewheeling is detected for five or more consecutive pulses.

## 3.12.2.3 Revision Register

The Revision Register contains the device revision corresponding to the mask set.

#### **Revision Register**

#### **REV\_REG**

| Revision Register Reset Value:00 <sub>H</sub> |   |   |   |   |    |    |   |  |  |  |  |

|-----------------------------------------------|---|---|---|---|----|----|---|--|--|--|--|

| 7                                             | 6 | 5 | 4 | 3 | 2  | 1  | 0 |  |  |  |  |

| 0                                             | 0 | 1 | 0 |   | RI | EV |   |  |  |  |  |

| r                                             | r | r | r |   |    | •  | • |  |  |  |  |

| Field | Bits | Туре | Description                               |

|-------|------|------|-------------------------------------------|

| 0     | 7    | r    | fixed to 0                                |

| 0     | 6    | r    | fixed to 0                                |

| 1     | 5    | r    | fixed to 1                                |

| 0     | 4    | r    | fixed to 0                                |

| REV   | 3:0  | r    | Device Revision corresponding to mask set |

#### **General Product Characteristics**

#### 4 General Product Characteristics

#### 4.1 Absolute Maximum Ratings

#### Table 6 Absolute Maximum Ratings<sup>1)</sup>

$T_i = -40^{\circ}\text{C to } +150^{\circ}\text{C};$

| Parameter                                       | Symbol           | Values |      |                       | Unit | Note or                             | Number   |

|-------------------------------------------------|------------------|--------|------|-----------------------|------|-------------------------------------|----------|

|                                                 |                  | Min.   | Тур. | Max.                  |      | <b>Test Condition</b>               |          |

| Junction temperature                            | $T_{J}$          | -40    | _    | 150                   | °C   | _                                   | P_5.1.1  |

|                                                 |                  | 150    |      | 175                   |      | 100 h cumulative                    |          |

| Storage temperature                             | $T_{\rm s}$      | -55    | _    | 150                   | °C   | _                                   | P_5.1.2  |

| Ambient temperature                             | Ta               | -40    | _    | 125                   | °C   | _                                   | P_5.1.3  |

| Supply voltage                                  | $V_{\rm VS}$     | -0.3   | _    | 40                    | V    | _                                   | P_5.1.4  |

| Supply for logic output                         | $V_{\rm VSO}$    | -0.3   | _    | 5.5                   | V    | _                                   | P_5.1.5  |

| Voltage at logic inputs                         | V <sub>IN</sub>  | -0.3   | _    | 5.5                   | V    | -                                   | P_5.1.6  |

| Voltage at logic output SO                      | $V_{SO}$         | -0.3   | -    | V <sub>vso</sub> +0.3 | V    | both conditions<br>must be observed | P_5.1.7  |

|                                                 |                  | -0.3   | _    | 5.5                   |      |                                     |          |

| ESD Susceptibility                              |                  |        | ,    |                       |      |                                     | <u>"</u> |

| ESD Susceptibility to GND acc. HBM              | V <sub>ESD</sub> | -2     | -    | 2                     | kV   | HBM <sup>2)</sup>                   | P_5.1.8  |

| ESD Susceptibility to GND acc. CDM              | V <sub>ESD</sub> | -500   | -    | 500                   | V    | CDM <sup>3)</sup>                   | P_5.1.9  |

| ESD Susceptibility to GND acc. CDM, Corner Pins | V <sub>ESD</sub> | -750   | -    | 750                   | V    | CDM <sup>3)</sup> , Corner Pins     | P_5.1.10 |

<sup>1)</sup> Not subject to production test, specified by design.

#### **Notes**

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

<sup>2)</sup> ESD susceptibility HBM according to EIA/JESD22-A114-B (1.5 k $\Omega$ , 100 pF)

<sup>3)</sup> ESD susceptibility, Charged Device Model "CDM" EIA/JESD22-C101

# infineon

#### **General Product Characteristics**

## 4.2 Functional Range

Table 7 Functional Range<sup>1)</sup>

| Parameter                               | Symbol              |               | Value | S    | Unit | Note or               | Numbe   |

|-----------------------------------------|---------------------|---------------|-------|------|------|-----------------------|---------|

|                                         |                     | Min.          | Тур.  | Max. |      | <b>Test Condition</b> | r       |

| Supply voltage range                    | $V_{S}$             | $V_{UV\_OFF}$ | _     | 28   | V    | -                     | P_5.2.1 |

| V <sub>S</sub> supply voltage slew rate | dV <sub>s</sub> /dt | -10           | -     | 10   | V/µs | -                     | P_5.2.2 |

| SO buffer supply voltage                | $V_{SO}$            | 2.9           | _     | 5.5  | V    | _                     | P_5.2.3 |

| Junction Temperature                    | $T_{\rm j}$         | -40           | _     | 150  | °C   | -                     | P_5.2.4 |

<sup>1)</sup> Not subject to production test, specified by design.

Note:

Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the Electrical Characteristics table.

#### 4.3 Thermal Resistance

Note:

This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to **www.jedec.org**.

Table 8 Thermal Resistance<sup>1)</sup>

| Parameter           | Symbol              | bol Values |      | Unit | Note or Test Condition | Number                               |         |

|---------------------|---------------------|------------|------|------|------------------------|--------------------------------------|---------|

|                     |                     | Min.       | Тур. | Max. |                        |                                      |         |

| Junction to Case    | $R_{\mathrm{thJC}}$ | _          | _    | 1    | K/W                    | 0.5 W on each H-Bridge               | P_5.3.1 |

| Junction to Ambient | $R_{thJA}$          | _          | 23   | _    | K/W                    | 0.5 W on each H-Bridge <sup>2)</sup> | P_5.3.2 |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> Specified  $R_{thJA}$  value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The Product (Chip+Package) was simulated on a 76.2 × 114.3 × 1.5 mm board with 2 inner copper layers (2 × 70 mm Cu, 2 × 35 mm Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

#### **Electrical Characteristics**

#### **Electrical Characteristics** 5

#### **Electrical Characteristics**

$V_{\rm S}$  = 8 V to 28 V;  $V_{\rm VSO}$  = 2.9 V to 5.5 V;  $T_{\rm j}$  = -40°C to +150°C; positive current flowing according to **Figure 2** (unless otherwise specified)

| Parameter                                              | Symbol                  | Values |      |      | Unit | <b>Note or Test Condition</b>                                                                       | Number   |

|--------------------------------------------------------|-------------------------|--------|------|------|------|-----------------------------------------------------------------------------------------------------|----------|

|                                                        |                         | Min.   | Тур. | Max. |      |                                                                                                     |          |

| Supply                                                 |                         |        |      |      |      |                                                                                                     |          |

| Supply Current                                         | I <sub>VS</sub>         | _      | -    | 13   | mA   | $f_{PWM} = 2 \text{ kHz}; I_{OUT} = 0 \text{ A};$<br>$V_{VS} = 13.5 \text{ V}$                      | P_6.0.1  |

| Supply Current Sleep Mode<br>25 °C                     | I <sub>VS</sub>         | -      | 19   | 30   | μΑ   | $V_{VS} = 13.5 \text{ V}; V_{VSO} = 0 \text{ V};$<br>$V_{OUTx} = 0 \text{ V}; T_j = 25 \text{ °C}$  | P_6.0.2  |

| Supply Current Sleep Mode<br>150 °C <sup>1)</sup>      |                         | _      | -    | 50   | μΑ   | $V_{VS} = 13.5 \text{ V}; V_{VSO} = 0 \text{ V},$<br>$V_{OUTx} = 0 \text{ V}; T_j = 150 \text{ °C}$ | P_6.0.3  |

| VSO Sleep Mode Threshold                               | $V_{ m VSO\_sleep}$     | 0.5    | -    | 2.0  | V    | _                                                                                                   | P_6.0.4  |

| VSO Input Current, CSN high                            | I <sub>VSO</sub>        | _      | _    | 100  | μΑ   | $I_{SO} = 0 \text{ A}; V_{CSN} > 2 \text{ V}$                                                       | P_6.0.5  |

| VSO Input Current, CSN low                             | I <sub>VSO</sub>        | _      | _    | 1.0  | mA   | $I_{SO} = 0 \text{ A}; V_{CSN} = 0 \text{ V}$                                                       | P_6.0.6  |

| VS Undervoltage                                        |                         |        |      |      |      |                                                                                                     |          |

| Undervoltage at V <sub>S</sub>                         | $V_{ m UV\_OFF}$        | 3.5    | 4.2  | 5.0  | V    | Switch off threshold                                                                                | P_6.0.7  |

| Undervoltage at V <sub>S</sub>                         | $V_{UV\_ON}$            | 3.6    | 4.4  | 5.2  | V    | Switch on threshold                                                                                 | P_6.0.8  |

| Undervoltage at V <sub>S</sub>                         | $V_{UV\_HY}$            | 0.1    | -    | 0.2  | V    | Hysteresis                                                                                          | P_6.0.9  |

| VS Undervoltage Detection<br>Filter Time <sup>1)</sup> | t <sub>UV</sub>         | _      | 1    | -    | μs   | -                                                                                                   | P_6.0.10 |

| Inputs PWM,DIR,SCK,SI                                  |                         |        |      |      |      |                                                                                                     |          |

| Low level                                              | $V_{\text{input\_L}}$   | _      | -    | 0.8  | V    | _                                                                                                   | P_6.0.11 |

| High level                                             | V <sub>input_H</sub>    | 2.0    | -    | -    | V    | -                                                                                                   | P_6.0.12 |

| Hysteresis                                             | V <sub>input_HYS</sub>  | 0.1    | 0.3  | -    | V    | _                                                                                                   | P_6.0.13 |

| Pull Down Current                                      | I <sub>in_pd</sub>      | 9      | 38   | 85   | μΑ   | V <sub>IN</sub> = 5.5 V                                                                             | P_6.0.14 |

| Input Capacity <sup>1)</sup>                           | C <sub>in</sub>         | _      | _    | 15   | pF   | $V_{\text{bias}} = 2V;$<br>$V_{\text{test}} = 20 \text{mVpp};$<br>f = 1  MHz                        | P_6.0.15 |

| Inputs DIS, CSN                                        |                         |        |      |      |      |                                                                                                     |          |

| Low level                                              | $V_{\text{input}\_L}$   | -      | -    | 0.8  | ٧    | -                                                                                                   | P_6.0.16 |

| High level                                             | V <sub>input_H</sub>    | 2.0    | -    | -    | V    | -                                                                                                   | P_6.0.17 |

| Hysteresis                                             | $V_{\text{input\_HYS}}$ | 0.1    | 0.3  | -    | V    | -                                                                                                   | P_6.0.18 |

| Pull Up Current                                        | I <sub>in_pu</sub>      | 9      | 38   | 85   | μΑ   | _                                                                                                   | P_6.0.19 |

| Input Capacity <sup>1)</sup>                           | C <sub>in</sub>         | -      | _    | 15   | pF   | $V_{\text{bias}}$ = 2 V;<br>$V_{\text{test}}$ = 20 mVpp;<br>f = 1 MHz                               | P_6.0.20 |

## **Dual 6 A H-Bridge With SPI**

#### **Electrical Characteristics**

#### Table 9 **Electrical Characteristics**

$V_{\rm S}$  = 8 V to 28 V;  $V_{\rm VSO}$  = 2.9 V to 5.5 V;  $T_{\rm j}$  = -40°C to +150°C; positive current flowing according to **Figure 2** (unless otherwise specified)

| Parameter                                | Symbol                                        | Values                     |      |               | Unit | <b>Note or Test Condition</b>                                   | Number   |

|------------------------------------------|-----------------------------------------------|----------------------------|------|---------------|------|-----------------------------------------------------------------|----------|

|                                          |                                               | Min.                       | Тур. | Max.          |      |                                                                 |          |

| Output SO                                | <u>'</u>                                      |                            |      |               |      |                                                                 |          |

| Low level                                | $V_{SO_L}$                                    | 0.0                        | -    | 0.4           | V    | I <sub>SO</sub> = -1 mA                                         | P_6.0.21 |

| High level                               | V <sub>SO_H</sub>                             | V <sub>vso</sub> -<br>0.75 | -    | $V_{\rm VSO}$ | V    | I <sub>SO</sub> = 1 mA,<br>2.9 V < V <sub>VSO</sub> < 5.5 V     | P_6.0.22 |

| Tristage Leakage Current                 | I <sub>SO</sub>                               | -5                         | _    | 5             | μΑ   | $0V < V_{SO} < V_{VSO};$<br>$V_{VSO} = 5.5 V$                   | P_6.0.23 |

| Output Capacity <sup>1)</sup>            | C <sub>so</sub>                               | _                          | -    | 19            | pF   | $V_{\rm bias}$ = 2 V;<br>$V_{\rm test}$ = 20 mVpp;<br>f = 1 MHz | P_6.0.24 |

| Power Outputs OUT1, OUT                  | Γ2                                            |                            |      |               |      |                                                                 |          |

| On resistance low side                   | R <sub>OUTL</sub>                             | -                          | 100  | _             | mΩ   | $I_{OUT} = 2 \text{ A}; T_j = 25 \text{ °C}$                    | P_6.0.25 |

|                                          |                                               | -                          | _    | 200           | mΩ   | $I_{OUT} = 2 \text{ A}; T_j = 150 ^{\circ}\text{C}$             |          |

| On resistance high side                  | R <sub>OUTH</sub>                             | -                          | 100  | -             | mΩ   | $I_{OUT} = 2 \text{ A}; T_j = 25 \text{ °C}$                    | P_6.0.26 |

|                                          |                                               | -                          | -    | 200           | mΩ   | $I_{OUT} = 2 \text{ A}; T_j = 150 ^{\circ}\text{C}$             |          |

| Leakage current                          | I <sub>OUT1(off)</sub> I <sub>OUT2(off)</sub> | -25                        | -    | 25            | μΑ   | $V_{VS}$ = 13.5 V; Outputs off; OLDIS High                      | P_6.0.27 |

|                                          |                                               | -100                       |      | 25            |      | $V_{\rm VS}$ = 13.5 V; Sleep mode                               |          |

| Free-wheel diode forward<br>voltage      | U <sub>D</sub>                                | -                          | 0.9  | 1.0           | V    | I <sub>D</sub> = 2 A                                            | P_6.0.28 |

| Output Switching Times <sup>2)</sup>     | <u>'</u>                                      |                            |      |               |      |                                                                 |          |

| Rise time HS                             | t <sub>r (HS)</sub>                           | 5                          | -    | 40            | μs   | $V_{VS} = 13.5 \text{ V};$                                      | P_6.0.29 |

| Fall time HS                             | t <sub>f (HS)</sub>                           | 5                          | -    | 40            | μs   | $R_{\text{Load}} = 6.8 \Omega$                                  | P_6.0.30 |

| Rise time LS                             | t <sub>r (LS)</sub>                           | 1.0                        | -    | 7.0           | μs   |                                                                 | P_6.0.31 |

| Fall time LS                             | $t_{\rm f(LS)}$                               | 1.0                        | _    | 7.0           | μs   |                                                                 | P_6.0.32 |

| PWM Frequency <sup>1)</sup>              | $f_{\sf PWM}$                                 | 0                          | _    | 20            | kHz  | _                                                               | P_6.0.33 |

| Output Delay Times <sup>2)</sup>         |                                               | •                          | •    |               |      |                                                                 |          |

| Output on-delay HS                       | t <sub>d_on(HS)</sub>                         | -                          | -    | 80            | μs   | V <sub>VS</sub> = 13.5 V;                                       | P_6.0.34 |

| Output off-delay HS                      | $t_{d\_off(HS)}$                              | -                          | -    | 80            | μs   | $R_{\text{Load}} = 6.8 \Omega$                                  | P_6.0.35 |

| Output on-delay LS                       | $t_{\sf d\_on(LS)}$                           | -                          | -    | 10            | μs   |                                                                 | P_6.0.36 |

| Output off-delay LS                      | $t_{\rm d\_off(LS)}$                          | -                          | _    | 10            | μs   |                                                                 | P_6.0.37 |

| Disable delay time                       | $t_{\sf d\_dis}$                              | -                          | -    | 80            | μs   |                                                                 | P_6.0.38 |

| Enable delay time                        | $t_{\sf d\_en}$                               | -                          | _    | 80            | μs   |                                                                 | P_6.0.39 |

| Disable/Enable filter time <sup>1)</sup> | $t_{\mathrm{f\_en}}$                          | 0.4                        | -    | 3             | μs   |                                                                 | P_6.0.40 |

| Wake Up delay time <sup>1)</sup>         | $t_{\rm wu}$                                  | -                          | _    | 1             | ms   | VSO high> OUT high                                              | P_6.0.41 |

## **Dual 6 A H-Bridge With SPI**

#### **Electrical Characteristics**

#### Table 9 **Electrical Characteristics**

$V_{\rm S}$  = 8 V to 28 V;  $V_{\rm VSO}$  = 2.9 V to 5.5 V;  $T_{\rm j}$  = -40°C to +150°C; positive current flowing according to **Figure 2** (unless otherwise specified)

| Parameter                                            | Symbol                               | ol Values |         |          | Unit   | <b>Note or Test Condition</b>                     | Number   |

|------------------------------------------------------|--------------------------------------|-----------|---------|----------|--------|---------------------------------------------------|----------|

|                                                      |                                      | Min.      | Тур.    | Max.     |        |                                                   |          |

| <b>Chopper Current Limitation</b>                    | n                                    |           |         | <u> </u> |        | 1                                                 |          |

| Current Limit                                        | / <sub>L</sub>                       | 6.0       | 8.0     | 10.0     | Α      | V <sub>VS</sub> = 13.5 V                          | P_6.0.42 |

| Blanking time <sup>1)</sup>                          | $t_{\rm b}$                          | 5         | 8       | 13       | μs     | -                                                 | P_6.0.43 |

| Minimum transition time <sup>1)</sup>                | $t_{trans}$                          | -         | 95      | -        | μs     | -                                                 | P_6.0.44 |

| Short Circuit Detection                              |                                      |           |         | <u> </u> |        | 1                                                 |          |

| Short circuit detection threshold high side switch   | I <sub>SC_H</sub>                    | 8.0       | 11.5    | 14.5     | А      | V <sub>VS</sub> = 13.5 V                          | P_6.0.45 |

| Short Circuit detection threshold low side switch    | I <sub>SC_L</sub>                    | 8.0       | 11.5    | 14.5     | А      |                                                   | P_6.0.46 |

| Current tracking high side                           | / <sub>SC_H</sub>  - / <sub>L</sub>  | 2.0       | 4.0     | 5.2      | Α      | -                                                 | P_6.0.47 |

| Current tracking low side                            | / <sub>SC_L</sub>  -  / <sub>L</sub> | 1.8       | 3.5     | 5.2      | Α      |                                                   | P_6.0.48 |

| Short Circuit detection filter time <sup>1)</sup>    | $t_{\rm sdf}$                        | -         | 2       | -        | μs     | -                                                 | P_6.0.49 |

| Open Load Detection in OF                            | F State                              |           |         |          |        |                                                   | 1        |

| Pull up Current at OUT1                              | I <sub>OUT1_OL</sub>                 | 60        | 140     | 200      | μΑ     | $V_{VS} = 13.5 \text{ V}; V_{OUT1} = 0 \text{ V}$ | P_6.0.50 |

| Pull down Current at OUT2                            | I <sub>OUT2_OL</sub>                 | -500      | -350    | -200     | μΑ     | $V_{VS} = V_{OUT2} = 13.5 \text{ V}$              | P_6.0.51 |

| Ratio of current sources                             | Ratio_I <sub>OL</sub>                | 1.8       | 2.5     | 3.5      | -      | -                                                 | P_6.0.52 |

| Open load detection in OFF filter time <sup>1)</sup> | $t_{f\_OL}$                          | 40        | -       | -        | μs     | -                                                 | P_6.0.53 |

| SPI Timing (Figure 9 "SPI T                          | iming Defi                           | nition    | (drawir | g not to | scale) | " on Page 12) <sup>1)</sup>                       |          |

| Cycle-time (1)                                       | tcyc                                 | 490       | -       | -        | ns     | Referred to master                                | P_6.0.54 |

| Enable Lead Time (2)                                 | tlead                                | 50        | -       | -        | ns     | Referred to master                                | P_6.0.55 |

| Enable Lag Time (3)                                  | tlag                                 | 150       | -       | -        | ns     | Referred to master                                | P_6.0.56 |

| Data valid (4) <sup>3)</sup>                         | tv                                   | -         | -       | 150      | ns     | CL = 200 pF Referred to<br>TLE9202ED              | P_6.0.57 |

|                                                      |                                      | -         | -       | 230      | ns     | CL = 350 pF Referred to TLE9202ED                 |          |

| Data Setup Time (5)                                  | tsu                                  | 40        | -       | -        | ns     | Referred to master                                | P_6.0.58 |

| Data hold Time (6)                                   | th                                   | 40        | -       | -        | ns     | Referred to master                                | P_6.0.59 |

| Disable Time (7)                                     | tdis                                 | -         | -       | 100      | ns     | Referred to TLE9202ED                             | P_6.0.60 |

| Transfer Delay (8)                                   | tdt                                  | 2         | -       | -        | μs     | Referred to master                                | P_6.0.61 |

| Disable Lead Time(9)                                 | tdld                                 | 250       | -       | -        | ns     | Referred to master                                | P_6.0.62 |

| Disable Lag Time (10)                                | tdlg                                 | 250       | -       | -        | ns     | Referred to master                                | P_6.0.63 |

## **Dual 6 A H-Bridge With SPI**

#### **Electrical Characteristics**

#### **Electrical Characteristics** Table 9

$V_S$  = 8 V to 28 V;  $V_{VSO}$  = 2.9 V to 5.5 V;  $T_j$  = -40°C to +150°C; positive current flowing according to **Figure 2** (unless otherwise specified)

| Parameter                                            | Symbol        | Values |      |      | Unit | <b>Note or Test Condition</b> | Number   |

|------------------------------------------------------|---------------|--------|------|------|------|-------------------------------|----------|

|                                                      |               | Min.   | Тур. | Max. |      |                               |          |

| Thermal Shutdown                                     | 1             |        |      |      |      |                               |          |

| Thermal Shutdown Junction Temperature <sup>1)</sup>  | $T_{\rm jSD}$ | 150    | 175  | -    | °C   | -                             | P_6.0.64 |

| Thermal Switch-On Junction Temperature <sup>1)</sup> | $T_{\rm jSO}$ | 125    | -    | -    | °C   |                               | P_6.0.65 |

- 1) Not subject to production test, specified by design.

- 2) Output switching times are measured between 20% and 80% of the output swing.

- 3)  $V_{SO}$  timing thresholds are 20% / 80% of  $V_{VSO}$  for 4.5 V <  $V_{VSO}$  < 5.5 V and 30% / 70% of  $V_{VSO}$  for 2.9 V <  $V_{VSO}$  < 4.5 V.

## **Application Information**

## **6** Application Information

Note:

The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device. The function of the described circuits must be verified in the real application.

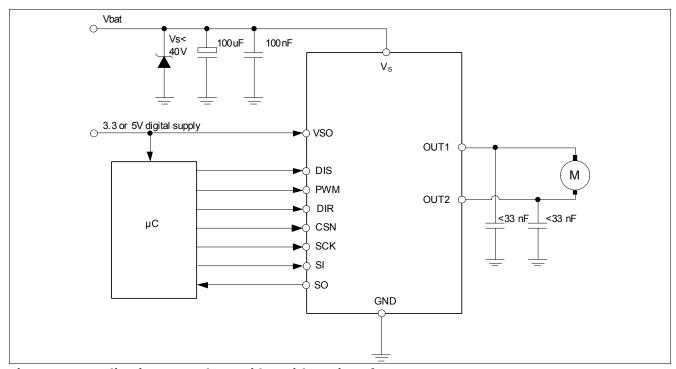

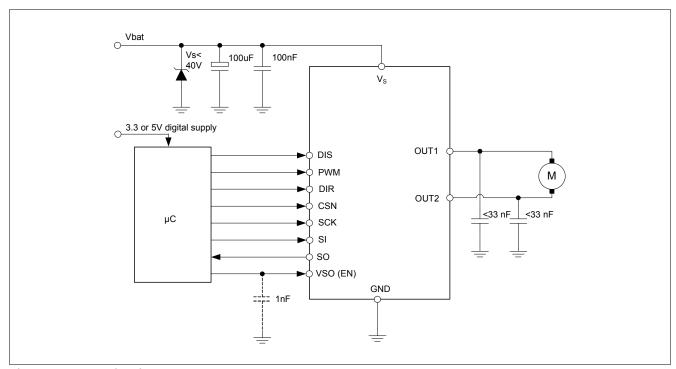

Figure 10 Application Example H-Bridge with SPI interface

Figure 11 Application Example H-Bridge with Error Flag

#### **Application Information**

Figure 12 SPI Daisy Chain Konfiguration (other signals omitted for clarity)

#### **Application Information**

Figure 13 Application Example VSO as Enable Input

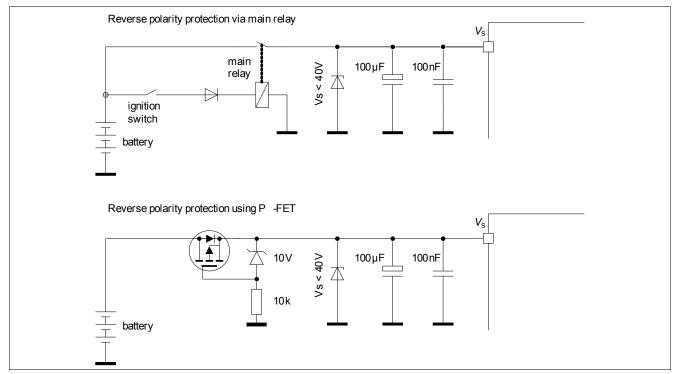

Figure 14 Examples for Reverse Polarity Protection

The TLE9202ED is not protected against reverse polarity. External measures have to be taken to ensure the right polarity of the supply voltage.

#### **Package Outlines**

#### **Package Outlines** 7

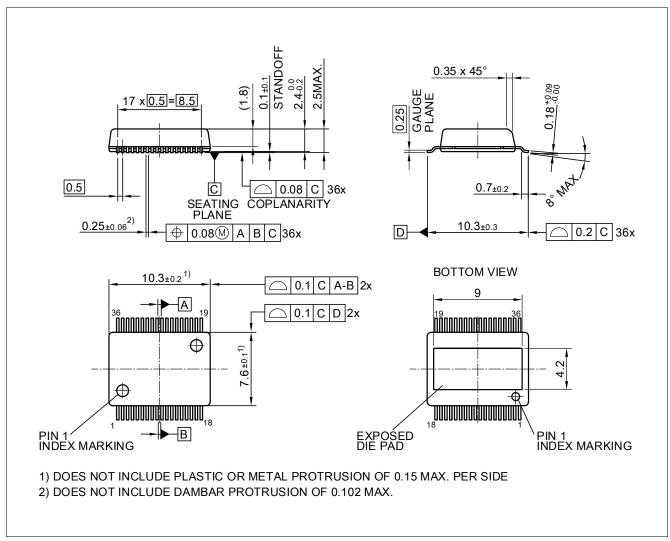

PG-DSO-36-72 Figure 15

**Data Sheet**

#### **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

Rev. 1.0 2016-09-29

## Dual 6 A H-Bridge With SPI

**Revision History**

#### **Revision History** 8

| Revision | Date       | Changes                                                                           |

|----------|------------|-----------------------------------------------------------------------------------|

| 0.1      | 2015-03-04 | Initial Target Data Sheet                                                         |

| 0.2      | 2015-06-25 | Chapter 1: Updated pin assignment                                                 |

| 0.3      | 2016-08-25 | Editorial Changes Chapter 7: Package Outlines                                     |

| 1.0      | 2016-09-29 | Editorial Changes Chapter 4.3 P_5.3.1 P_5.3.2 Chapter 5 P_6.0.1 P_6.0.43 P_6.0.51 |

#### **Trademarks of Infineon Technologies AG**

µHVIC™, µIPM™, µPFC™, AU-ConvertIR™, AURIX™, C166™, Canpak™, CIPOS™, CIPURSE™, CoolDp™, CoolGan™, COOLiR™, CoolMos™, CoolSiC™, DAVE™, DI-POL™, DirectFET™, DrBlade™, EasyPIM™, EconoBRIDGE™, EconoDual™, EconoPack™, EconoPim™, EiceDriver™, eupec™, FCOS™, Ganpowir™, HEXFET™, HITFET™, HybridPack™, iMOTION™, IRAM™, ISOFACE™, IsoPack™, LeDrivir™, LiTiX™, MiPaq™, ModStack™, my-d™, Novalithic™, Optiga™, Optimos™, Origa™, Powirstage™, PrimePack™, PrimeStack™, Profet™, Pro-Sil™, Rasic™, Real3™, SmartLewis™, Solid Flash™, Spoc™, Strongirfet™, Supirbuck™, Tempfet™, Trenchstop™, Tricore™, UHVic™, XHP™, XMc™.

Trademarks updated November 2015

#### **Other Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2016-09-29 Published by Infineon Technologies AG 81726 Munich, Germany

© 2016 Infineon Technologies AG. All Rights Reserved.

Do you have a question about any aspect of this document?

Email: erratum@infineon.com

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.

单击下面可查看定价,库存,交付和生命周期等信息

>>Infineon Technologies(英飞凌)