# **OptiMOS<sup>™</sup>3** Power MOS Transistor Chip

| Туре       | V(BR)DSS | R <sub>DS(on)</sub> | Die size                   | Thickness |

|------------|----------|---------------------|----------------------------|-----------|

| IPC26N12NR | 120 V    | 4.8 m $\Omega^{2)}$ | 6.0 * 4.36 mm <sup>2</sup> | 250 μm    |

## DESCRIPTION

- N-channel enhancement mode

- For additional characteristic and max ratings refer to the datasheet of IPP048N12N3 G<sup>1)</sup>

- AQL 0.65 for visual inspection according to failure catalogue

- Electrostatic Discharge Sensitive Device according to MIL-STD 883C

- Die bond: soldered or glued

- Backside metallization: NiV system

- Frontside metallization: AISi system

- Passivation: nitride (only on edge structure)

### **Electrical Characteristics on Wafer Level**

at  $T_j = 25 \text{ °C}$ , unless otherwise specified.

| Parameter                        | Symbol              | Value |                   |                   | Unit | Conditions                                         |

|----------------------------------|---------------------|-------|-------------------|-------------------|------|----------------------------------------------------|

|                                  |                     | min.  | typ.              | max.              |      |                                                    |

| Drain-source breakdown voltage   | V(BR)DSS            | 120   | -                 | -                 | V    | $V_{GS} = 0V$                                      |

|                                  |                     |       |                   |                   |      | I <sub>D</sub> = 1 mA                              |

| Gate threshold voltage           | V <sub>GS(th)</sub> | 2     | -                 | 4                 | V    | $V_{DS} = V_{GS}$                                  |

|                                  |                     |       |                   |                   |      | I <sub>D</sub> = 230 μA                            |

| Zero gate voltage drain current  | I <sub>DSS</sub>    | -     | 0.1               | 1                 | μA   | $V_{GS} = 0V$                                      |

|                                  |                     |       |                   |                   |      | V <sub>DS</sub> = 100 V                            |

| Gate-source leakage current      | I <sub>GSS</sub>    | -     | 1                 | 100               | nA   | V <sub>GS</sub> = 20 V                             |

|                                  |                     |       |                   |                   |      | $V_{DS} = 0 V$                                     |

| Drain-source on-resistance       | R <sub>DS(on)</sub> | -     | 3.2 <sup>4)</sup> | 100 <sup>3)</sup> | mΩ   | V <sub>GS</sub> = 10 V                             |

|                                  |                     |       |                   |                   |      | I <sub>D</sub> = 2.0 A                             |

| Reverse diode forward on-voltage | V <sub>SD</sub>     | -     | 1.0               | 1.2               | V    | V <sub>GS</sub> =0 V                               |

|                                  |                     |       |                   |                   |      | I <sub>F</sub> = 1 A                               |

| Internal gate resistance         | R <sub>G</sub>      | -     | 2                 | -                 | Ω    |                                                    |

| Additional gate resistor         | R <sub>Gadd</sub>   |       | 16                |                   | Ω    |                                                    |

| Avalanche energy, single pulse   | E <sub>AS</sub>     | -     | 45 <sup>5)</sup>  | -                 | mJ   | I <sub>D</sub> = 30 A, <i>R</i> <sub>GS</sub> =25Ω |

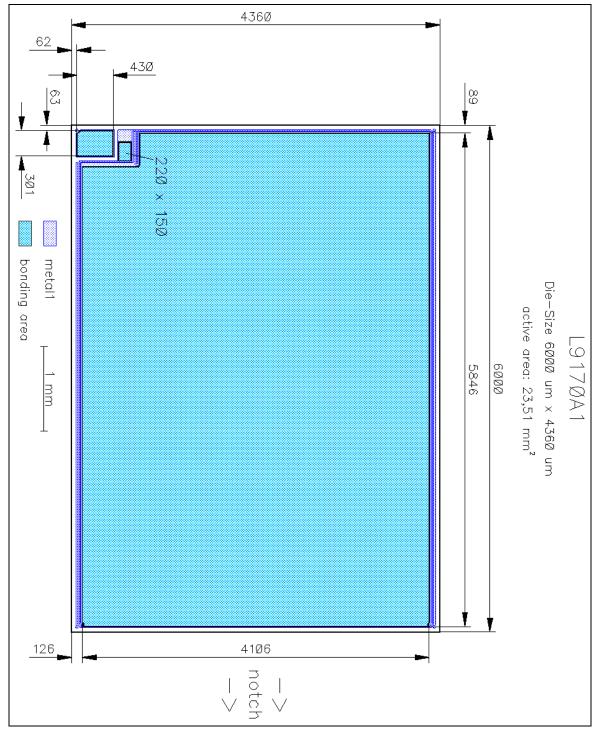

## Chip-Layout:

<sup>1)</sup> IPP048N12N3 G dynamic characterization does not include the internal added Rg

<sup>2)</sup> packaged in a P-TO220-3-1 (see ref. product)

<sup>3)</sup> limited by wafer test-equipment

$^{\rm 4)}$  typical bare die  $R_{\rm DS(on)};\,V_{\rm GS}{=}10V$

<sup>5)</sup> Wafer tested. For general avalanche capability refer to the datasheet of IPP048N12N3 G

Infineon Technologies, IMM PSD Rev. 2.1

Published by Infineon Technologies AG 81726 Munich, Germany © 2009 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

单击下面可查看定价,库存,交付和生命周期等信息

>>Infineon Technologies(英飞凌)