### **USB DCP Control IC**

### **General Description**

The LP102 is a USB Dedicated Charging Port controller. The feature monitors USB D+/D- data line's signal, and automatically adjusts output voltage of power source output to optimize charge time.

The LP102 was supported USB Battery Charging Specification Revision 1.2(BC1.2), DCP apply the 2.7V operation function for Divider 3 mode.

Other features include under-voltage lockout (UVLO). The LP102 is available in a space saving SOT23-6 package.

### **Order Information**

LP102 F: Green

Package Type

B6: SOT-23-6

### **Features**

- ◆ Power consumption below 1mW@5 V

- ◆ Support USB BC1.2

- ◆ Support Short Mode per Chinese Telecommunication Industry Standard YD/T 1591-2009

- ◆ Divide3 DCP, apply D+/D- is 2.7V/2.7V

- ◆ Support USB DCP 1.2V on Data Line

- ◆ Under-Voltage Protection

- ◆ Available in SOT23-6

- ◆ RoHS Compliant and Halogen Free

### **Applications**

- ◆ Battery Charge Port

- ◆ USB Dedicated Charging Port

- ♦ Wall-Adapter

### **Marking Information**

|   | Device                                                       | Marking | Package | Shipping |  |

|---|--------------------------------------------------------------|---------|---------|----------|--|

| ì | LP102                                                        | LP102   | SOT23-6 | 3K/REEL  |  |

|   | INGI OGIIII                                                  | YWX     |         |          |  |

| 3 | Y: Y is year code. W: W is week code. X: X is series number. |         |         |          |  |

LP102-00 Version 0.0 NOV.-2017 Email: marketing@lowpowersemi.com www.lowpowersemi.com Page 1 of 7

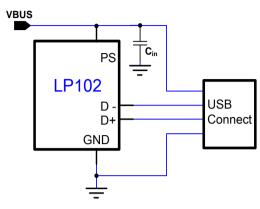

# **Typical Application Circuit**

Figure 1. Typical Application Circuit of LP102 with SOT23-6 Package Type.

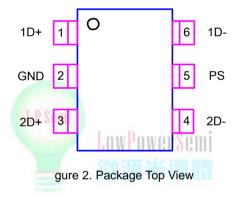

# **Pin Configuration**

LP102-00 Version 0.0 NOV.-2017 Email: <a href="marketing@lowpowersemi.com">marketing@lowpowersemi.com</a> <a href="marketing@lowpowersemi.com">www.lowpowersemi.com</a> Page 2 of 7

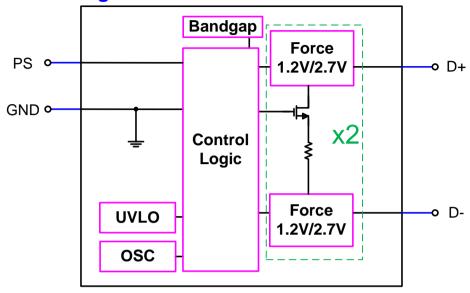

# **Function Block Diagram**

Figure 3. Function Block Diagram

# **Functional Pin Description**

| Pin NO. | SOT23-6 | Description                                                                                                |  |  |  |

|---------|---------|------------------------------------------------------------------------------------------------------------|--|--|--|

| 1D+     | 1       | USB D+ data line port 1.                                                                                   |  |  |  |

| GND     | 2       | Ground.                                                                                                    |  |  |  |

| 2D+     | 3       | USB D+ data line port 2.                                                                                   |  |  |  |

| 2D-     | 4       | USB D- data line port 2.                                                                                   |  |  |  |

| PS      | 5       | Power Source. Connection point for an external bypass capacitor for the internally general supply voltage. |  |  |  |

| 1D-     | 6       | USB D- data line port 1.                                                                                   |  |  |  |

LP102-00 Version 0.0 NOV.-2017 Email: <a href="marketing@lowpowersemi.com">marketing@lowpowersemi.com</a> <a href="marketing@lowpowersemi.com">www.lowpowersemi.com</a> Page 3 of 7

# **Absolute Maximum Ratings** Note2

| $\diamond$ | PS to GND                                              | -0.3V to +6.5V  |

|------------|--------------------------------------------------------|-----------------|

| <b>\$</b>  | 1D+, 1D-, 2D+, 2D- to GND                              | -0.3V to +6.5V  |

| <b></b>    | Operating Junction Temperature Range (T <sub>J</sub> ) | -40°C to 150°C  |

| <b></b>    | Operation Ambient Temperature Range                    | -40°C to +105°C |

| <b>\$</b>  | Storage Temperature Range                              | -65°C to +150°C |

| <b>\$</b>  | Maximum Soldering Temperature (at leads, 10sec)        | +260°C          |

**Note2.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Thermal Information**

♦ Thermal Resistance

LP102-00 Version 0.0 NOV.-2017 Email: marketing@lowpowersemi.com www.lowpowersemi.com Page 4 of 7

### **Electrical Characteristics**

$(V_{BUS} = 5V, T_A = 25^{\circ}C \text{ (Unless Otherwise Specified))}$

| Parameter                                              | Symbol                   | Test Conditions       | Min  | Тур | Max  | Units |

|--------------------------------------------------------|--------------------------|-----------------------|------|-----|------|-------|

| Supply and Reference Function                          |                          |                       |      |     |      |       |

| Power Source UVLO Threshold                            | V <sub>UVLO</sub>        |                       | 3.9  | 4.1 | 4.3  | V     |

| UVLO Threshold Hysteresis                              | V <sub>UVLO _Hys</sub>   |                       |      | 0.1 |      | V     |

| Power Source Current                                   | I <sub>PS</sub>          |                       |      | 150 | 200  | μΑ    |

| Battery Charging Specification Revision 1.2 (BC 1.2)   |                          |                       |      |     |      |       |

| D+ and D- Shorting Resistance                          | R <sub>BC_SHORTx</sub>   | V <sub>D+</sub> =0.8V |      | 150 | 200  | Ω     |

| Resistance between D+/D- and GND                       | R <sub>BC_DISx</sub>     |                       | 350  | 656 | 1150 | kΩ    |

| D+ Low Voltage Detach                                  | V <sub>D+L_DETx</sub>    |                       | 310  | 330 | 350  | mV    |

| D+ Low Voltage Detach Hysteresis                       | V <sub>D+_DETx_Hys</sub> |                       |      | 50  |      | mV    |

| Dedicated Charging Port Divide Mode(DCP Divide 3 mode) |                          |                       |      |     |      |       |

| DCP2.7V Data Line Output Voltage                       | V <sub>DCP2.7V</sub>     |                       | 2.57 | 2.7 | 2.84 | V     |

| DCP2.7V Data Line Output Resistance                    | R <sub>DCP2.7V</sub>     |                       | 24   | 30  | 36   | kΩ    |

| Dedicated Charging Port 1.2V Mode(DCP 1.2V mode)       |                          |                       |      |     |      |       |

| DCP1.2V Data Line Output Voltage                       | V <sub>DCP1.2V</sub>     |                       | 1.12 | 1.2 | 1.28 | V     |

| DCP1.2V Data Line Output Resistance                    | R <sub>DCP1.2V</sub>     | LowPowerSemi          | 80   | 100 | 120  | kΩ    |

微源半導體

LP102-00 Version 0.0 NOV.-2017 Email: <a href="marketing@lowpowersemi.com">marketing@lowpowersemi.com</a> <a href="marketing@lowpowersemi.com">www.lowpowersemi.com</a> Page 5 of 7

### **Application Information**

The LP102 is a USB Dedicated Charging Port controller. It monitors USB D+/D- data line's signal, and automatically adjusts output voltage of power source output to optimize charge time.

#### **Under Voltage Lockout (UVLO)**

The LP102 had an UVLO internal circuit that enable the device once the voltage on the  $V_{\text{PS}}$  voltage exceeds the UVLO threshold voltage.

#### **DCP Mode**

A dedicated charging port (DCP) is a downstream port on a device that outputs power through a USB connector, which generally allows portable devices to fast charge at their maximum rated current. A USB charger is a device with a DCP, such as a power bank or car charger. A DCP is identified by the electrical characteristics of its data lines. The following DCP identification circuits are usually used to meet the handshaking detections of different portable devices.

| Data  | Line | LP102                   |  |

|-------|------|-------------------------|--|

| D+    | D-   | DCP Mode                |  |

| 2.7V  | 2.7V | Divider 3               |  |

| 1.2V  | 1.2V | DCP 1.2V Mode           |  |

| Short |      | BC1.2 and YD/T1591-2009 |  |

The LP102 integrate an auto-detect feature to support divider mode, short mode and 1.2V modes. The device operated D+/D- driver 2.7V output normally. If a BC1.2 compliant device is attached, the LP102 will switches into short mode automatically. If a device compliant with the 1.2V charging scheme is attached, 1.2V is applied on both the D+ pin and the D- pin. DCP auto-detect feature is cost effective, it doesn't need external element.

#### Battery Charging Specification Revision 1.2(BC1.2)

The BC1.2 Specification defines the protocol necessary to allow portable equipment to determine what type of port it is connected to so that it can allot its maximum allowable current drawn.

Simply put, the portable device outputs a nominal 0.6V output to one data line, and detected the other one data line.

#### DCP 1.2V Mode

The LP102 have the auto-detect feature that monitors the D+ and D- line voltages of the USB connector, providing the correct voltage data on the D+ and D-pins for support portable devices to fast charge.

#### **Divider Mode**

There are three charging schemes for divider DCP. They are named after Divider1, Divider2, and Divider3. The Divider 3 charging scheme is used for 12-W adapters, and applies 2.7 V on D+ and D- lines.

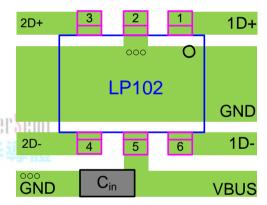

### **Layout Consideration**

The proper PCB layout and component placement are critical for all circuit. Here are some suggestions to the layout of LP102 design.

- 1. Connected all ground together with one uninterrupted ground plane, which include power ground and analog ground.

- 2. The input capacitor should be located as closed as possible to the VPS and ground plane.

Figure 4. Recommended PCB Layout Diagram

LP102-00 Version 0.0 NOV.-2017 Email: marketing@lowpowersemi.com www.lowpowersemi.com Page 6 of 7

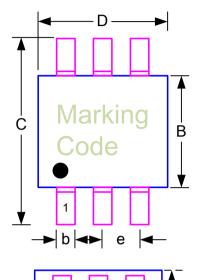

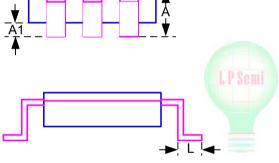

# **Outline Information**

| SYMBOLS | DIMENSION IN MILLIMETER |       |  |  |

|---------|-------------------------|-------|--|--|

| UNIT    | MIN                     | MAX   |  |  |

| А       | 0.700                   | 1.000 |  |  |

| A1      | 0.000                   | 0.100 |  |  |

| В       | 1.397                   | 1.803 |  |  |

| b       | 0.300                   | 0.559 |  |  |

| С       | 2.591                   | 3.000 |  |  |

| D       | 2.692                   | 3.099 |  |  |

| е       | 0.838                   | 1.041 |  |  |

| Н       | 0.080                   | 0.254 |  |  |

| L       | 0.300                   | 0.610 |  |  |

LP102-00 Version 0.0 NOV.-2017 Email: <a href="marketing@lowpowersemi.com">marketing@lowpowersemi.com</a> <a href="marketing@lowpowersemi.com">www.lowpowersemi.com</a> Page 7 of 7

# 单击下面可查看定价,库存,交付和生命周期等信息

# >>LOW POWER(微源半导体)