### **LED Driver with PWM Dimming Control**

### **General Description**

LP3350 is a cost effective LED driver optimized for LCD monitor and LCD TV backlighting application. It provides a high performance LED backlight solution with minimized bill of material count.

The LP3350 contains a PWM boost driver which uses current mode control and fixed frequency operation to regulate the LED current. The LED current is sensed through an external current sense resistor. The voltage across the sensing resistor is compared with reference level of 0.3V, the error amplified to control the pulse width of the power switch thus to regulate the current flowing the LED.

Otherwise, The LP3350 offers external frequency PWM dimming method for a wide range of dimming control.

Other features include over current protection (OCP), output over voltage protection (OVP), and under-voltage lockout (UVLO). The LP3350 is available in a space saving SOP-8 (0.5mm pitch) package.

### **Order Information**

#### **Features**

- ♦ Wide V<sub>IN</sub> Range: 8V to 28V

- ◆ Current-Mode PWM Controller

- ◆ External PWM Dimming Mode

- ◆ Under-Voltage Lockout

- ◆ Over Voltage Protection

- ◆ Over Current Protection

- ◆ Under-Voltage Protection

- ◆ Over-Temperature Protection

- ◆ Available in SOP-8

- ◆ RoHS Compliant and Halogen Free

- ♦ Pb-Free Package

### **Applications**

- ◆ TFT LCD TV

- **◆** TFT LCD Monitor

- ◆ Flat Panel Display

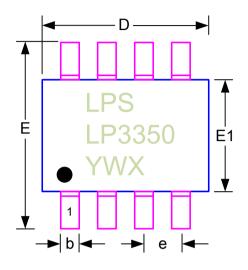

### **Marking Information**

| Device                                                       | Marking | Package | Shipping |

|--------------------------------------------------------------|---------|---------|----------|

| LP3350                                                       | LPS     | SOP-8   | 3K/REEL  |

| 丰學體                                                          | LP3350  |         |          |

|                                                              | YWX     |         |          |

| Y: Y is year code. W: W is week code. X: X is series number. |         |         |          |

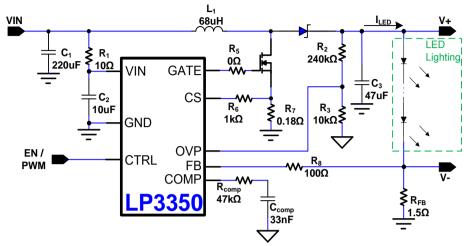

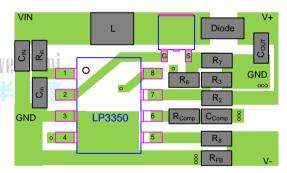

## **Typical Application Circuit**

Figure 1. Typical Application Circuit of LP3350

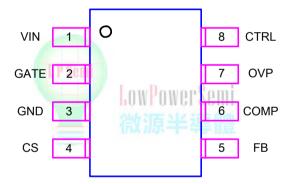

## **Pin Configuration**

Figure 2. SOP-8 Package Top View

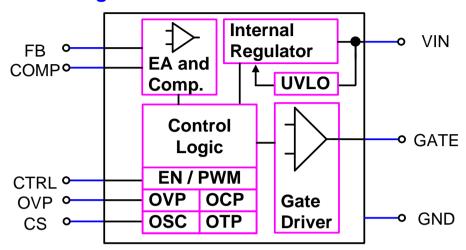

## **Function Block Diagram**

Figure 3. Function Block Diagram

## **Functional Pin Description**

| Pin NO. | Pin Name | Description                                                                                               |  |

|---------|----------|-----------------------------------------------------------------------------------------------------------|--|

| 1       | VIN      | Input Supply Pin. Decouple with 10μF ceramic capacitor close to the pin.                                  |  |

| 2       | GATE     | External NMOS Gate Drive Pin.                                                                             |  |

| 3       | GND      | Ground. OW OWELSEM                                                                                        |  |

| 4       | CS       | Current Sense Input Pin.                                                                                  |  |

| 5       | FB       | Regulator Feedback Input. Connect to an external resistive to set the output current.                     |  |

| 6       | COMP     | Regulator Error Amplifier Compensation Pin.                                                               |  |

| 7       | OVP      | Over Voltage Protection Sense Input. Connect to an external resistive voltage divider from the V+ to GND. |  |

| 8       | CTRL     | Enable and External PWM Dimming Control.                                                                  |  |

## **Preliminary Datasheet**

# **Absolute Maximum Ratings Note 1**

| <b></b>   | VIN to GND                                             | -0.3V to +36V   |

|-----------|--------------------------------------------------------|-----------------|

| <b></b>   | GATE, CS, FB, COMP, OVP, CTRL to GND                   | -0.3V to +20V   |

| <b></b>   | Operating Junction Temperature Range (T <sub>J</sub> ) | −40°C to +150°C |

| <b></b>   | Operation Ambient Temperature Range                    | -40°C to +85°C  |

| <b></b>   | Storage Temperature Range                              | -65°C to +150°C |

| <b></b>   | Maximum Soldering Temperature (at leads, 10sec)        | +260°C          |

| <b>\$</b> | Maximum Junction Temperature                           | +150°C          |

**Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Thermal Information**

♦ Thermal Resistance

LP3350-00 Version 0.3 NOV-2017

Email: marketing@lowpowersemi.com

www.lowpowersemi.com

Page 4 of 7

## **Electrical Characteristics**

(V<sub>IN</sub>=12V, V<sub>CTRL</sub>=5V, T<sub>A</sub>=25°C, unless otherwise specified)

| Parameter                      | Symbol                 | Test Conditions                           | Min   | Тур | Max   | Units |

|--------------------------------|------------------------|-------------------------------------------|-------|-----|-------|-------|

| General                        |                        |                                           |       |     |       |       |

| Input Supply Voltage           | $V_{VLI}$              |                                           | 8     |     | 28    | V     |

| V <sub>IN</sub> Supply Current | 1                      | Sleep Current                             |       | 310 | 400   | uA    |

|                                | IQ                     | Operation Current                         |       | 2.5 | 3     | mA    |

| Input UVLO Threshold           | V <sub>UVLO(VTH)</sub> | V <sub>IN</sub> Rising                    | 6     | 7   | 8     | V     |

| UVLO Threshold Hysteresis      | V <sub>UVLO(HYS)</sub> | Falling Hysteresis                        |       | 500 |       | mV    |

| Soft Start Slope               | T <sub>SS_Slop</sub>   |                                           |       | 400 |       | mV/ms |

| Thermal Shutdown Threshold     | T <sub>SD</sub>        | Temperature Rising                        | 140   | 160 | 180   | °C    |

| Thermal Shutdown Hysteresis    | $\DeltaT_{SD}$         |                                           |       | 30  |       | °C    |

| PWM Control                    | ·                      |                                           |       |     |       |       |

| Internal Oscillator Frequency  | Fosc                   |                                           | 175   | 200 | 225   | kHz   |

| Maximum Duty Cycle             | D <sub>MAX</sub>       |                                           | 93    | 95  | 97    | %     |

| CTRL Threshold Voltage         | V <sub>IH</sub>        | Logic High.                               |       |     | 2.6   | V     |

|                                | I Viceni               | Logic Low                                 | 1     |     |       | V     |

| Pull Down Resistor             | R <sub>Pull_Low</sub>  | LowPowerSemi                              |       | 150 |       | kΩ    |

| Error Amplifier                |                        |                                           |       |     |       |       |

| Reference Voltage              | $V_{REF}$              | Reference voltage at non-inverting input. | 295.5 | 300 | 304.5 | mV    |

| Open Loop Voltage Gain         | Am                     |                                           |       | 70  |       | dB    |

| Transconductance of EA         | Gm                     |                                           | 80    | 100 | 120   | uA/V  |

| GATE Source Current            | I <sub>Source</sub>    |                                           | 24    | 30  | 36    | uA    |

| GATE Sink Current              | I <sub>Sink</sub>      |                                           | 48    | 60  | 72    | uA    |

| Protection Threshold           |                        |                                           |       |     |       |       |

| Over Voltage Protection        | V <sub>OVP</sub>       | Threshold of OVP                          | 1.8   | 2   | 2.2   | V     |

| Over Current Protection        | V <sub>OCP</sub>       | Threshold of OCP                          |       | 330 |       | mV    |

| Fault Trigger Duration         | T <sub>Fault</sub>     |                                           |       | 50  |       | ms    |

| Connect detect time            | T <sub>Dly</sub>       |                                           |       | 1   |       | ms    |

| 00P TI                         | V                      | Normal Operation                          |       | 200 |       | mV    |

| SCP Threshold                  | $V_{OVP\_UV}$          | System Startup                            |       | 100 |       | mV    |

LP3350-00 Version 0.3 NOV-2017

Email: marketing@lowpowersemi.com

### **Application Information**

The LP3350 is designed in a current mode, constant frequency PWM boost converter. It can use dimming input that can by external control signal with a duty ratio of 1%-100% in 100Hz to 1kHz. LP3350 offers protection features to protect the system such as output over voltage protection, boost diode disconnection protection, output short circuit protection and over temperature protection.

#### **Under Voltage Lockout (UVLO)**

The LP3350 had an UVLO internal circuit that enable the device once the voltage on the VIN voltage exceeds the UVLO threshold voltage.

#### **Boost Controller**

The LP3350 uses 200kHz fixed-frequency, current mode architecture to fixed the output current. The output voltage and soft start time can be adjustable by internal register.

#### **Boost Loop Compensation**

The feedback loop can be compensated with an external compensation network consisted of Rcomp, Ccomp (As Figure 1). Choosing Rcomp to set high frequency integrator gain for fast transient response and Ccomp to set the integrator zero to maintain loop stability.

#### **Over Voltage Protection**

The LP3350 converter has an over voltage protection by OVP pin. When the LEDs fail open circuit or LEDs are disconnected from the circuit, the over voltage function will monitor the output voltage through OVP pin to protect the converter. When LP3350 occur OVP, it will latch off until VIN is re-startup or CTRL input is recycled.

#### **LED Current Setting**

The LED current is specified by current sense resistor between the FB pin to ground. In order to have accurate LED current, precision resistors are preferred. The LED current can be programmed by:  $I_{\text{LED}}{=}0.3/R_{\text{FB}}$

### **Dimming Control**

The LED brightness is controlled by the PWM signal at CTRL pin which has different duty cycle. LP3350 can accept an external PWM signal to CTRL pin in the range of 100Hz to 1 kHz.

#### **Over Temperature Protection**

The LP3350 device enters over temperature protection(OTP) if its junction temperature exceeds 160°C (Typ.). During over temperature protection none of the device's functions are available. To resume normal operation the junction temperature need cool down, and the outputs will restart.

#### **Layout Guideline**

The proper PCB layout and component placement are critical for all circuit. The careful attention should be prevent electromagnetic interference (EMI) problems. Here are some suggestions to the layout of LP3350 design.

- 1. Connected all ground together with one uninterrupted ground plane with at least two vias .

- 2. The input capacitor should be located as closed as possible to the VIN and ground plane.

- 3. Minimize the distance of all traces connected to the LX node, that the traces short and wide route to obtain optimum efficiency.

- 4. All output capacitor must be closed to ground plane.

The ground terminal of COUT must be located as closed as possible to ground plane.

5. Radiated noise can be decreased by choosing a shielded inductor.

Figure 4. Recommended PCB Layout Diagram

LP3350-00 Version 0.3 NOV-2017

Email: marketing@lowpowersemi.com

www.lowpowersemi.com

Page 6 of 7

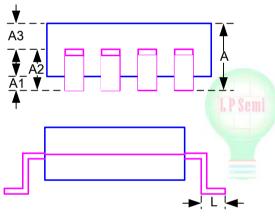

### **Outline Information**

SOP-8 Package (Unit: mm)

| SYMBOLS | DIMENSION IN MILLIMETER |       |       |

|---------|-------------------------|-------|-------|

| UNIT    | MIN                     | NOM   | MAX   |

| Α       |                         |       | 1.750 |

| A1      | 0.100                   |       | 0.225 |

| A2      | 1.300                   | 1.400 | 1.500 |

| А3      | 0.600                   | 0.650 | 0.700 |

| b       | 0.390                   |       | 0.470 |

| D       | 4.800                   | 4.900 | 5.000 |

| E       | 5.800                   | 6.000 | 6.200 |

| E1      | 3.800                   | 3.900 | 4.000 |

| е       | 1.27BSC                 |       |       |

| L       | 0.500                   |       | 0.800 |

## 单击下面可查看定价,库存,交付和生命周期等信息

## >>LOW POWER(微源半导体)